## Testability and Dependability of AI Hardware: Survey, Trends, Challenges, and Perspectives

Fei Su, Chunsheng Liu, Haralampos-G. Stratigopoulos

### ▶ To cite this version:

Fei Su, Chunsheng Liu, Haralampos-G. Stratigopoulos. Testability and Dependability of AI Hardware: Survey, Trends, Challenges, and Perspectives. IEEE Design & Test, 2023, 40 (2), pp.8 - 58. 10.1109/MDAT.2023.3241116 . hal-03961502

HAL Id: hal-03961502

https://hal.science/hal-03961502

Submitted on 29 Jan 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Testability and Dependability of AI Hardware: Survey, Trends, Challenges, and Perspectives

Fei Su\*, Chunsheng Liu<sup>†</sup>, Haralampos-G. Stratigopoulos<sup>‡</sup>

\*Intel Coorporation, USA

<sup>†</sup>Alibaba Inc., USA

<sup>‡</sup>Sorbonne Université, CNRS, LIP6, France

Abstract—In recent years, there has been an expedited trend in embracing bold and radical innovation of computer architectures, aiming at the continuation of computing performance improvement despite the slowed-down physical device scaling. One new frontier in this field focuses on Artificial Intelligence (AI) hardware. While functionality of AI hardware still remains the main focus, testability and dependability of these new architectures need to be addressed before the mainstream adoption. This survey paper covers the state-of-the-art in research and development of dependability and testability solutions for AI hardware including digital or analog implementations of Artificial Neural Networks (ANNs) and Spiking Neural Networks (SNNs), used in accelerators and neuromorphic designs. Trends, challenges and perspectives are also discussed in this paper.

Index Terms—AI hardware accelerators, neuromorphic computing, artificial neural networks, spiking neural networks, fault modeling and simulation, testability, dependability, fault tolerance, functional safety.

### I. Introduction

Artificial Intelligence (AI) and Machine Learning (ML) algorithms have been a subject of interest for several decades now. Although AI and ML have gone through hype cycles of disappointment and enthusiasm, recent algorithmic advancements, in particular Deep Neural Networks (DNNs) [1], as well as the availability of big data and the rapid growth of computing power, have renewed interest leading nowadays to applications in numerous distinct fields, e.g., robotics, medicine, autonomous vehicles, computer vision, speech recognition, natural language processing, gaming, etc.

DNN models are computational intensive with their backpropagation training process taking up a number of operations in the order of millions. Inference on trained models requires a single forward pass, but still the number of operations remains very high. From a hardware perspective, this poses severe challenges of data storage, movement, and processing speed on conventional Central Processing Units (CPUs) with a traditional Von Neumann computer architecture, commonly known as the memory wall problem [2]. To this end, there are intense and on-going efforts nowadays towards designing dedicated and customized processors for AI [3]-[9], referred to as AI hardware accelerators, which belong to the larger family of domain-specific computing paradigms. Widely used AI hardware accelerators today are Graphics Processing Unit (GPUs) and Field-Programmable Gate Arrays (FPGAs), but orders of magnitude of energy-speed improvement can be achieved with Application-Specific Integrated Circuits (ASICs).

Another high incentive for designing AI hardware accelerators is to push the execution of AI algorithms from the cloud closer to the sources of data onto edge devices [10]. This is

driven by energy, bandwidth, speed, availability, and privacy requirements. More specifically, edge computing reduces the data transfer requirement thus saving energy and bandwidth. Saving bandwidth is important given the forecast that several tens of billions of edge devices will be connected to the internet in the near future. Several applications, e.g., autonomous vehicles, require low-latency real-time computation which is slowed down due to the communication with the cloud. Also, several applications require availability, thus they need to be less dependent on the communication with the cloud. Finally, handling data locally offers privacy as opposed to transmitting sensitive data over the cloud. Edge AI is a challenging objective since edge devices have limited resources and are often battery-operated. Typically, AI hardware accelerators embedded on edge devices perform only inference with the DNN model trained in software and uploaded upfront.

Having stressed that AI hardware accelerators are pivotal in the AI world, many would believe that neural networks on hardware inherit the remarkable fault tolerance capabilities of the biological brain. Indeed, biological neural networks are capable of regenerating, rewiring or adapting network elements to make up for damage, which is part of their neuroplasticity ability [11]. This assumption also stems from properties of neural networks, such as their high parallelism and over-provisioning, i.e., there are more neurons available than the minimum required for a certain cognitive task and many neurons end up being ineffective. However, as it will be discussed in more detail in Section IV, recent hardware-level fault injection experiments have shown that this assumption is false. A neural network is likely to be capable of learning even in the presence of a high fault rate; however, the impact on prediction accuracy can be non-negligible or even detrimental if a model is uploaded on a faulty hardware neural network or if a fault occurs during the lifetime of the hardware neural network.

For these reasons, testability and dependability of AI hardware accelerators are important issues that need to be addressed already from the design phase [12]. Inspiration can of course be drawn from known and mature methodologies applied to traditional computer architectures, but the architectural particularities of AI hardware accelerators often make such methodologies prohibitive in terms of cost and quality, requiring the development of new methodologies that are better suited and take full advantage of the said architectural particularities.

The aim of this article is to provide a survey of existing works on testability and dependability methodologies for AI hardware accelerators and discuss trends, challenges, and

1

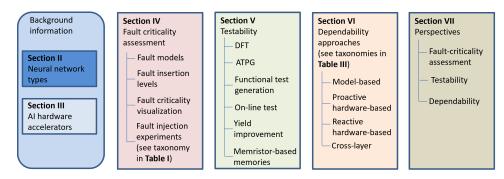

Fig. 1: Structure of article.

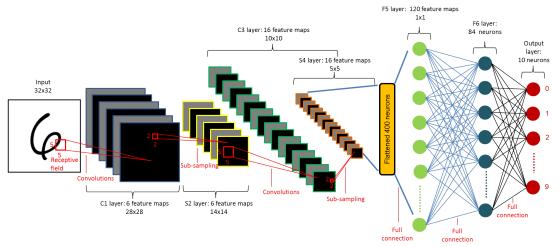

Fig. 2: Architecture of LeNet-5 CNN.

perspectives. The high-level organization of this article into sections and their main subsections is shown in Fig. 1.

### II. NEURAL NETWORK TYPES

We distinguish two types of neural networks, namely the Artificial Neural Networks (ANNs) and the Spiking Neural Networks (SNNs). Both are inspired from the brain structure composed of layers assembled by neurons and synapses interconnecting the different layers. The term "deep" in DNN refers to the number of layers going beyond of just a few, allowing to extract more complex features. The number of layers, the number of neurons within each layer, and synapse connections define a network topology.

There are three main topologies applied to both ANNs and SNNs, namely Fully-Connected (FC) networks, Convolutional Neural Networks (CNNs) [13], and Recurrent Neural Networks (RNNs) [14]. Fig. 2 shows an example CNN with FC layers forming the last layers. In FC networks, the neurons of a new layer are connected via synapses to the outputs of all neurons in the prior layer. In CNNs, a convolutional layer is composed of several feature maps. A feature map is a plane of neurons where each neuron is connected to the outputs of spatially nearby neurons contained in a lower-dimensional plane of the prior layer, referred to as a receptive field. Each neuron has a different receptive field located at different coordinates of the prior layer. In a given feature map, all neurons are constrained to share the same synaptic weights, whereas synaptic weights change from one feature

map to another. Convolutional layers are alternated with subsampling layers which are used to down-sample the output of the preceding convolutional layer. There are different types of sub-sampling, such as max pooling and average pooling. Max pooling captures the maximum value of the receptive field and processes it to the output, whereas average pooling calculates the average value. CNNs allow synapse reuse and reduce the number of synapses compared with a FC network. In RNNs, neurons can additionally receive as input their previous state or the previous state of a neuron in a subsequent layer, thus realizing an internal memory retaining past information to forecast future outputs. RNNs are used for learning on timeseries or sequential data, while FC networks and CNNs are feed-forward and inputs are independent of each other.

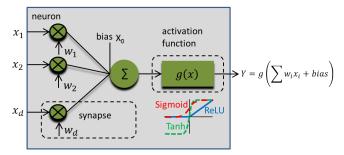

In ANNs, data are represented as static numerical values. Neurons apply a non-linear activation function, such as Rectified Linear Unit (ReLU), sigmoid, and tanh, on the weighted sum of outputs of other neurons, as depicted in Fig. 3. The weights are scalar values and correspond to the synaptic weights.

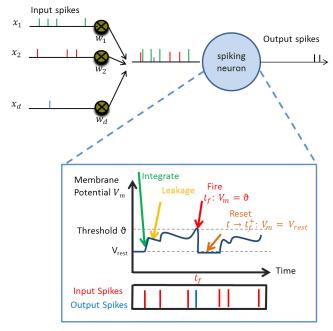

In SNNs, on the other hand, data are represented with spikes processed in a continuous way in time, which is similar to brain operation. Thus, they are more biologically plausible compared with ANNs, bridging the gap between ML and the biological brain in terms of computation speed and power consumption [15]. SNNs form the basis of neuromorphic computing as pioneered by Carver Mead in the 1980s [16]. The most hardware-friendly spiking neuron implementation

Fig. 3: Artificial neuron.

Fig. 4: Spiking neuron.

is the Integrate & Fire (I&F) model [17], depicted in Fig. 4. The neuron integrates the spikes from incoming synapses, and when the potential of its membrane exceeds a threshold it fires a spike of its own that propagates through synapses to other neurons. It also resets the threshold so as to be able to fire again. The neuron has two additional brain-inspired functionalities. It has a refractory period, i.e., it is allowed to fire only if a certain time is elapsed since the last output spike, and a leakage behavior, i.e., the membrane potential decreases between two consecutive input spikes. The synapse operation is different from ANNs and also resembles the biological synapse operation. A synapse receives spikes and in turn stimulates the membrane potential of post-synaptic neurons via a current. The most common information representation in SNNs is rate coding, whereby the information is encoded into the firing rate over an observation period, but other representations have been suggested, including time-to-firstspike and inter-spike interval.

From a hardware perspective, there is a belief that SNNs offer faster inference and lower energy consumption compared with ANNs. This belief stems from two SNN characteristics, namely the real-time asynchronous spike flow and the sparsity of the spike flow which reduces neuron activities. In contrast, ANNs have a frame-based operation, i.e., for a layer to perform

its computation the layer has to wait for the computation of the previous layer to complete and every individual neuron is being evaluated. However, SNNs are harder to train compared with ANNs due to the non-continuity of the spiking neuron's transfer function, as well as the additional parameters a spiking neuron carries, e.g., threshold, leakage rate, refractory period, which could be sensitive. In general, the discussion on the relative performance between ANNs and SNNs is not trivial due to the different input type, i.e., sequence of static frames versus continuous-time event flow. Converting a dataset from frame-based to spiking format and vice versa creates bias in the comparison. In general, the advantage of one neural network type over the other is task-dependent, with the SNNs being ideally suited for processing spatio-temporal event-based sensory data. For an extensive discussion on SNNs and the comparison with their ANN counterparts, the readers are referred to [5], [18], [19].

### III. AI HARDWARE ACCELERATORS

Silicon implementations of neural networks appeared decades ago with early efforts demonstrating few-layers, fewneurons per layer networks [20]. Moving to larger designs for DNN acceleration, the main challenge is the memory wall that limits the throughput and increases power consumption. The design ambition is therefore to overcome the memory wall by distributing the memory within close proximity to the Processing Elements (PEs), e.g., the Multiple-Accumulate (MAC) units, or through interleaving of memory and PEs. Basic architectures include the streaming architecture composed of many cores with the layers mapped among the cores and the single-core architecture, i.e., in the form of a systolic array that parallelizes the storage and computation of the different layers [3]. SNNs typically employ the streaming architecture with a core receiving and transmitting spikes via the Address Event Representation (AER) protocol which essentially implements a Network-on-Chip (NoC) communication scheme [21]. Clearly, efficient mapping of the neural network algorithm onto the hardware becomes of utmost importance and different neural network topologies require different hardware designs to fully take advantage of neuromorphic computing.

Analog and Mixed-Signal (AMS) implementations can offer orders of magnitude lower power consumption compared with their digital counterparts, thus they are better-suited for edge computing being capable of acting directly on sensory data from world-machine interfaces [22], [23]. This is because transistors are operated in the sub-threshold region and the main operations of a neural network, i.e., addition and multiplication, can be performed efficiently in the analog domain. Addition can be performed using Kirchhoff's current law while multiplication can be performed with just a few transistors. However they are less robust due to process variations and noise.

One way to reduce the energy consumption is approximate computing which involves two strategies. The first uses approximate arithmetic units in the PEs [24]. The second is termed network compression or quantization [25]. It reduces the precision of the weights and neuron activation values by

Fig. 5: Memristive crossbar array.

transforming floating point numbers into narrow few-bit integers. At the extreme, this results in Binary Neural Networks (BNNs) that use 1-bit precision [26], further simplifying the network architecture by allowing using XNORs instead of MAC units [27]. BNNs save energy and storage and can serve for implementing deep models in resource-constrained edge devices. Network compression results in accuracy loss but it may be recovered through training.

Another design paradigm with tremendous potential for overcoming the memory wall is in-memory computing where the matrix-vector multiplications are performed within the memory itself [28], [29]. In-memory computing has two main embodiments, namely performing arithmetic and logic operations within the SRAM or using memristive crossbar arrays.

A memristive crossbar array is composed of horizontal and vertical metal lines with a memristive device placed at each cross-point intersection connecting the two metal lines, as shown in Fig. 5. The conductance of the memristive device implements the synapse weight, horizontal lines are driven by the voltage output of pre-synaptic neurons, and vertical lines provide the current input of post-synaptic neurons. Each column implements the dot product  $I_i = \sum_j G_{i,j} \cdot V_j$  and parallelized dot-products across the columns implement efficient *in-situ* matrix-vector multiplication  $I = \mathbf{G} \cdot V$  in analog form, reducing computational complexity from  $\mathcal{O}(n^2)$  to  $\mathcal{O}(1)$ . Each memristive device is augmented with an access device, as shown in the 1-transistor/1-resistor (1T1R) architecture of Fig. 5, that allows selecting a memristive device for programming while not disturbing the stored state of other memristive devices. A memristive crossbar array is accompanied with peripheral circuits (not shown in Fig. 5) if communication between crossbars is implemented in the digital domain. These include Digital-to-Analog Converters (DACs) and Analog-to-Digital Converters (ADCs) which contribute a large fraction of the area and power consumption of the array macro.

There are several emerging Non-Volatile Memory (NVM) devices that can be used to implement the memristive device, including Resistive Random Access Memory (ReRAM), Phase

Fig. 6: Taxonomy of AI hardware accelerators.

Change Memory (PCM), and Spin Transfer Torque Magnetic Random Access Memory (STT-MRAM) [30]. These devices are compact and can perform read and write operations with low power. However, they suffer from several imperfections, such as conductance variations and drifts, which result in poor yield, stability, and endurance. Therefore, enhancing the reliability of crossbar-array computation is a subject of ongoing research.

Finally, 3D integration technologies could offer several advantages such as short interconnections, high parallelism, high bandwidth, and small form factors [31], [32].

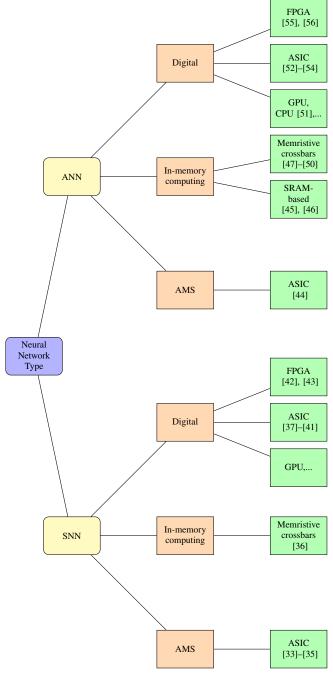

A taxonomy of AI hardware accelerators is illustrated in Fig. 6. The first layer defines the type of neural network, i.e., ANN

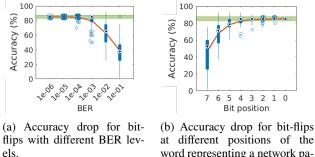

Fig. 7: Fault classification. Images are from [57].

or SNN. The second layer defines different design flavors, i.e., digital or AMS, with in-memory computing inserted as a separate category. The third layer defines the implementation, i.e., ASIC, FPGA, etc., while in-memory computing is further distinguished into digital processing-in-memory, i.e., SRAM-based in-memory computing, and memristive crossbar arrays. In Fig. 6, we provide references to representative designs with a focus on designs that have been demonstrated on silicon. Regarding memristive crossbar-array accelerators, most works present only simulation results up to now. This list of references is not meant to be complete. For recent and thorough surveys on accelerator design for ANNs and SNNs, the readers are referred to [3], [4], [6]–[9] and [5], respectively.

### IV. FAULT CRITICALLY ASSESSMENT

### A. Introduction

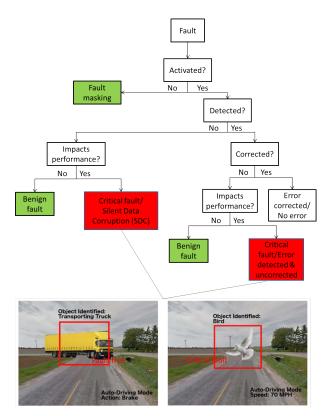

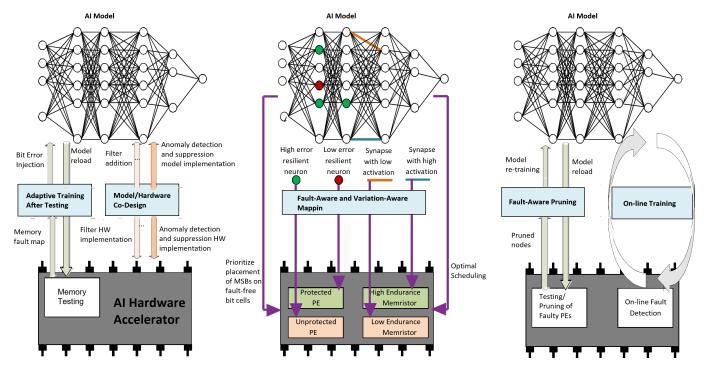

In the context of an AI hardware accelerator many faults turn out to be benign: they are masked before their effect reaches the output or produce an output change that is tolerable, i.e., it does not translate to performance loss. This is thanks to the network sparsity, the over-provisioning, the distributed computing, and the nature and sequence of mathematical computations. Some faults, however, will be critical and will affect the performance. A fault classification is shown in Fig. 7. The ability of quickly assessing the impact of faults on the AI hardware accelerator performance is very valuable for performing early reliability analysis and for guiding the development of efficient and cost-effective fault detection, fault tolerance, and fault repair schemes by placing the focus on targeting the critical faults only.

A network is viewed as a distributed system where neurons and synapses can fail independently [58]. Given the large number of synapses and neurons, the size of the fault space easily explodes, not to mention the rest of the hardware components. On the other hand, the fault impact is typically expressed in terms of accuracy drop on the testing set, which can contain several thousands of samples, while the time for a single inference can be very long. For these reasons, performing fault simulation at the hardware-level can be intractable, thus necessitating fault modeling approaches at a higher abstract level. As a matter of fact, performing exhaustive fault injection even on a higher abstract network representation may still not be feasible, thus necessitating fault sampling.

Another challenge in fault modeling is that the fault impact is determined by the interactions between the network model, the dataset, and the AI hardware accelerator. When analyzing the fault impact, the AI hardware accelerator architecture and the scheduling of network operations on its architectural components cannot be ignored [59].

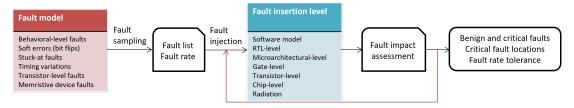

Fig. 8 shows a fault injection experiment flow. Starting with a fault model, a fault list is created as a subset of the fault universe possibly using fault sampling. A single fault assumption or multiple fault scenario with user-specified fault rate can be considered in this step. Then fault injection is performed on the AI hardware accelerator which could be done at different insertion levels, i.e, in a software model, RTL-level, microarchitectural-level, gate-level, transistor-level, on an actual hardware prototype, or with radiation. For every fault scenario the fault impact is assessed and stored. After going trough the complete fault list, a report is produced, for example including the benign and critical faults, the critical fault locations, and the fault rate that can be tolerated.

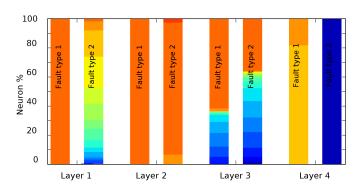

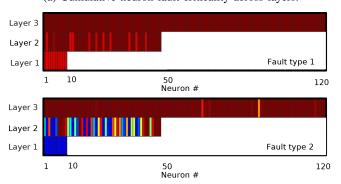

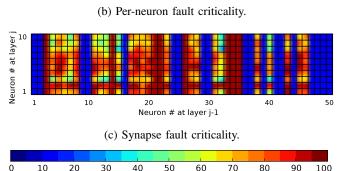

Examples of fault criticality visualizations are shown in Fig. 9. In Fig. 9(a), the x-axis shows the different layers and for each layer there are two columns, each corresponding to a different fault type. A column is a colored bar possibly separated into chunks of different colors. Each chunk of the bar corresponds to a specific classification accuracy according to the color shading shown at the bottom of Fig. 9, and the projection on the y-axis shows the percentage of neurons for which the fault results in this classification accuracy. While Fig. 9(a) shows the cumulative neuron criticality across layers, Fig. 9(b) shows the per-neuron criticality as a heat map with the neuron number in the x-axis and the layer number in the yaxis. Each orthogonal corresponds to one specific neuron, and the color of each orthogonal corresponds to the classification accuracy in the presence of a fault in the neuron according to the color shading in the bottom of Fig. 9. For a given fault type, Fig. 9(c) displays the impact on classification accuracy of synapse faults in the synaptic matrix between two layers. Using such plots, one can label faults as critical or benign and identify critical fault locations across layers and within each layer.

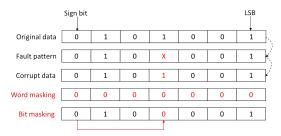

As we will see next, most research works consider bit-flips in the memories and registers storing the network parameters, i.e., synapse weights and neuron activations. For this fault model, examples of reliability assessment are shown in Fig. 10. Bit-flips can be injected with some Bit Error Rate (BER)

Fig. 8: Fault injection experiment flow.

(a) Cumulative neuron fault criticality across layers.

Fig. 9: Fault criticality visualization.

Classification Accuracy %

probability to assess the largest BER that can be tolerated, as shown in Fig. 10(a). The experiment is repeated several times and summary statistics are visualized in Fig. 10(a) using box plots. The bottom and top edges of the box indicate the 25th and 75th percentile, respectively. The whiskers extend to the most extreme data points without considering outliers, and the outliers are plotted individually using the 'o' symbol and are not always aligned vertically for illustration purpose. Fig. 10(a) also illustrates the baseline fault-free accuracy

different positions of the word representing a network pa-

Fig. 10: Reliability assessment using bit-flips as fault model.

shown with the green zone, the median shown with a dotted circle, and the average accuracy across repetitions of the same experiment shown with a red line. Bit-flips can also be injected at individual bit positions as shown in Fig. 10(b) where the network parameter has an 8-bit representation. For example, with the results in Fig. 10(b) we can identify those bits starting from the Least Significant Bit (LSB) that have no impact on the accuracy if they are flipped and can be left unprotected in a fault-tolerance strategy.

In Section IV-B, we survey several works demonstrating fault injection experiments and frameworks. Fig. 11 shows different fault types at different insertion levels. A taxonomy of works is provided in Table I based on the fault insertion level, while memristor crossbar-based architectures are treated as a special category. In Section IV-C we summarize general conclusions from these experiments.

### B. Fault injection experiments

1) Software-level: The software and hardware implementation of a neural network matches closely in terms of component connectivity and data flow, thus allowing performing fault injection in software in a more time-efficient manner. This was noticed in early works [58], [61]-[63] where structural behavioral-level fault models were used in the main software operators that support the network computational task, i.e., neurons and synapses. Behavioral-level fault types included stuck-at nodes, missing or saturated neurons, errors in the summation or the evaluation of the neuron's nonlinear activation function, errors in synaptic multiplication, disabled or saturated weights, errors in learning rules, noisy inputs, etc. These behavioral-level faults can be mapped to physical fault models and root-causes in hardware, i.e., gate-level stuckat faults and soft errors, for both digital and analog circuit implementations of neural networks [64], [65]. In [58], a the-

Fig. 11: Faults models at different insertion levels. The chip image corresponds to an AMS implementation of a FC network used as an on-chip classifier for Built-in Self-Test (BIST) purposes [60].

TABLE I: Taxonomy of fault injection experiments and frameworks.

| Fault injection experiments and frameworks         |  |

|----------------------------------------------------|--|

| Software-level [57], [58], [61]–[63], [66]–[91]    |  |

| RTL-level [92], [93]                               |  |

| Microarchitectural-level [94]                      |  |

| Gate-level [95]–[98]                               |  |

| Transistor-level [99], [100]                       |  |

| Chip-level [101]–[110]                             |  |

| Radiation experiments [81]–[85], [111]–[114]       |  |

| Memristor crossbar-based architectures [115]–[118] |  |

oretical study is presented for Feed-Forward Neural Networks (FFNNs) deducing the number of failing neurons and synapses an FFNN can tolerate.

As there is a large body of works in this direction for modern AI hardware accelerators, we categorize them according to the two neural network types, namely ANNs and SNNs.

a) ANNs: In [57], the fault model used is bit-flips in datapaths and buffers. A wide range of data types are considered and bit flips are injected in different bit positions. Fault injection is carried out in the open-source DNN simulator framework Tiny-CNN written in C++, where each line of code is mapped to the corresponding hardware component so as to pinpoint the impact of the fault injection location in terms of the underlying micro-architectural components. The focus is on CNNs considering different image classification tasks. Four types of Silent Data Corruption (SDC), defined as a mismatch between the output of a faulty and the fault-

free inference execution, or "fault ratings" are proposed taking into consideration that networks may rank predictions based on a confidence score. Some conclusions of this large-scale fault injection study are: (a) different DNNs have different sensitivities to SDCs depending on the topology, the types of layers, the data type used, and the position of the bit flip; (b) Failure in-Time (FIT) rates can exceed the safety standards, e.g. ISO 26262 for automotive, by orders of magnitude; (c) data types that provide more dynamic value range are more vulnerable to SDCs since there are likely to be redundant value ranges that lead to larger-value deviation under faults. This implies that just-enough numeric value-range and precision is advantageous from a reliability point of view; (d) normalization layers reduce the impact of faults by averaging fault values with adjacent correct values.

In [66], the *Ares* framework is proposed that simulates static bit-flips in the memory of the DNN accelerator. *Ares* is built on top of Keras [119], which takes high-level DNN descriptions specified in Python and executes them using either Theano [120] or TensorFlow [121] back ends. Fault injection experiments are performed for several DNN models and datasets to study the classification rate as a function of BER. Fault injection is performed across the whole network, per-layer, and across network components, i.e., weights and activation functions. Main conclusions of this study are: (a) a thresholded behavior is observed where for small BERs the classification error is zero, but there is a BER threshold beyond

which the classification error rises exponentially from zero; (b) there is a largely spread fault sensitivity or resilience across the DNN models, e.g., the threshold varies by two orders of magnitude; (c) the weight quantization impacts resilience, i.e., the larger the range of the possible weight values is the lower the threshold is; (d) fault sensitivity across network layers and components can vary by several orders of magnitude.

In [67], the *FIdelity* DNN resilience analysis framework is proposed where hardware faults are modeled in software, i.e., TensorFlow [121], thereafter high-speed software fault injection is performed. In this way an analysis speedup is achieved while maintaining the level of accuracy of RTL or mixed-mode fault injection techniques. To map hardware faults in software the key insight is that hardware and software operations closely match, and all operations affected by a fault can be systematically derived thanks to well-defined dataflow and scheduling algorithms. Given high-level architecture/hardware information and Flip-Flop (FF) FIT rate, the framework captures the effect of hardware faults to set a faulty output neuron using a reuse factor analysis for FFs. Faulty output neuron values are derived considering that each FF value already corresponds to a software-variable state. A key aspect of the framework is that it can treat logic transient errors in data-path and control FFs and not only memory errors.

In [68], a methodology is proposed to reduce the fault injection space and, thereby, the overhead of an exhaustive fault injection. The underlying observation is that most ML functions in a DNN model, i.e., convolution, ReLu, pooling, normalization, etc., are monotonic. This means that in a word representing a model parameter, there exists a SDC-boundary bit such that bit-flips at higher-order bits would lead to SDCs and bit-flips at lower-order bits would be masked. Based on this observation, the Binary Fault Injection (*BinFI*) fault simulator is proposed that bisects the fault injection space and finds the SDC-boundary bit with a binary-search like algorithm. *BinFI* is built on top of the TensorFlow framework [121] duplicating the graph with customized operators.

In [69], a fault injection framework is proposed that reproduces fault models and event rates extracted from radiation tests. The ultimate goal is to have the flexibility of a software-based fault injector with a reliability assessment precision close to this of an accelerated neutron beam radiation-based fault injection experiment in a realistic harsh environment.

The interested reader is referred to [70]–[85] for more software-based fault injection experiments studying the fault impact for different neural network models, data type representations, layer types, network sizes, pruned networks, compressed versus uncompressed networks, etc. Such experiments are also part of several other works that will be discussed in Sections V and VI and they are used for motivation or for guiding test and dependability solutions. Many of these works develop at the same time an in-house automated fault injection framework. The development of automated, fast, flexible, and accurate fault injection frameworks is an active area of research. Examples include PyTorchFI [86] and TensorFI [87], which are open-source and publicly available, and CLASSES [88]. An interesting research line is the development of ML-based frameworks that based on a small number of fault

injections they estimate the vulnerability for all parameters in the DNN in a short time [89]. Such approaches will be described in more detail in Section IV-B4 for systolic-array DNN architectures at gate-level and in Section IV-B8 for memristor crossbar-array architectures. Another possibility is to use generic fault injection tools, such as SASSIFI [122], NVBitFI [123], and CAROL-FI [124], to emulate fault effects in the hardware platform, i.e., GPU, running the application.

b) SNNs: The fault tolerance characteristics of SNNs trained with different algorithms is studied in [90]. The fault model is synapse fault where a faulty synapse is zeroed out or equivalently removed. Synapses are selected to be faulty at random with different failure rates. Results show that these different algorithms have different resilience characteristics. Resilience can greatly depend on the training algorithm and dataset, and it can also show large variances according to the synapses that are selected to fail. Common conclusion is that for all considered networks resilience drops rapidly as fault rates increase, and SNNs are not inherently resilient as it is frequently cited.

In [91], the behavioral-level fault model proposed in [100] (see Section IV-B5) is used to perform accelerated fault injection in deep SNNs. The fault injection framework is built on top of the SLAYER [125] and PyTorch [126] frameworks by customizing the flow of computations and the faulty SNN is mapped onto a GPU. The general conclusion of this experiment is that saturation neuron faults are the most lethal and can severely affect inference regardless the location of the neuron in the network, and that the impact of all other fault types, i.e., dead neuron faults and timing variations, may be severe only for neurons in the last hidden and output layer. At the extreme, timing variations could result in a dead or saturated neuron. In other words, a neuron that becomes permanently active has a greater effect on inference compared to a neuron that is permanently silenced or presents timing variations in its output spike train.

2) RTL-level: In [92], fault characterization is performed on a RTL design of a typical accelerator. Fault injection is performed into the different registers that latch data during the inference, i.e., input, weights, and intermediate layer computations. The fault model includes permanent stuck-at faults and transient faults occurring in a single random cycle. In each fault injection experiment, a different fault is randomly generated and injected by selecting a random register and set of bits and a random cycle in the case of transient faults. Fault characterization is performed across the different register types, layers, components of fixed-point data representation, i.e., sign, digit, and fraction, number of PEs, and network models. General conclusions are: (a) permanent faults are more critical than transient faults; (b) stuck-at-1 faults are more critical than stuck-at-0 faults due to the sparsity of zeros; (c) registers storing intermediate data are the most vulnerable, whereas input registers are the least vulnerable; (d) permanent faults are more critical in inner layers, i.e., closer to the output, while the opposite is observed for transient faults; (e) sign, digit, and fraction are in this order more vulnerable; (f) for permanent faults the error decreases with the number of PEs, while there is no correlation in the case of transient faults.

In [93], an RTL-level fault injection framework is proposed that drastically reduces the fault simulation time. It makes use of a multi-level structure where on the lower level the inference is split in several blocks corresponding to the neural network layers that run as stand-alone application processes and on the upper level these processes are synchronized.

- 3) Microarchitectural-level: In software fault injection the fault model risks to be unrealistic and faults can be mapped to only a subset of hardware resources. In [94], the concept of a two-level fault injection is adopted to evaluate the effects on CNN execution of faults in the GPU's scheduler and pipeline registers, two microarchitectural components that otherwise would be hidden in an abstract high-level CNN model. Microarchitectural simulation requires a prohibitively high time. To improve efficiency, the two-level fault injection idea is composed of the following steps: (a) perform microarchitectural fault injection, i.e. transient bit-flips; (b) observe the effect on selected CNN tiles (i.e., matrix portions); (c) merge the corrupted tiles' output with the other tiles in the convolution considering their fault-free output to compose the layer's output; and (d) continue the execution of CNN at the softwarelevel to check if the fault is eventually masked or it propagates at the output creating an error. Finally, a feedback analysis can determine the microarchitectural locations causing the observed critical errors that should be targeted for hardening.

- 4) Gate-level: In [95], fault injection experiments are performed on a systolic array-based DNN accelerator. The core of the systolic array is composed of a 256×256 grid of MAC units. Each weight maps to exactly one MAC unit, thus a faulty MAC unit can result in multiple faulty weights. The systolic array is developed in Verilog and synthesized at gate-level. The fault model includes stuck-at faults at gate-level and timing faults created by under-scaling the power supply which essentially emulates process variations. It is demonstrated that training on a faulty systolic array can result in significant classification drop when as few as four MAC units are faulty.

In [96], the impact of timing variations on hardware implementation of ANNs is studied. Timing variations could result from delay defects, process variations, power supply noise, crosstalk, aging, voltage over-scaling or frequency overclocking. Timing variations are modeled at gate-level by introducing an extra delay variation in the range of 10-40% into each gate relative to the nominal gate delay. Results show that ANNs are sensitive to timing variations with the error growing larger as the timing variations worsen. Accuracy loss can be alleviated to a large degree but not fully recovered if the ANN is retrained under timing errors.

In [97], [98], ML-based frameworks are proposed for analyzing the functional criticality of gate-level stuck-at faults in systolic array based AI accelerators. Fault injection targets not only the interface/boundary level of a PE, but also all internal nodes of a PE. The main challenge of such a task is on computation/simulation overhead introduced by a significantly large number of potential fault injection points, e.g., there will be tens of thousands of stuck-at faults for a single 32-bit PE, and billions for a 256x256 PE array. To this end, computationally efficient ML-based methods are proposed to speed up the analysis. The basic idea is based on the use

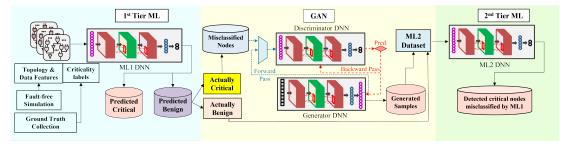

of deep learning to predict fault criticality by utilizing the structural and data flow features. For example, in [98], a twotier DNN-based model is presented, as illustrated in Fig. 12. The first tier DNN is trained on a data set obtained from ground-truth collection. The second tier DNN is trained on a smaller and targeted data set containing the critical faults mis-predicted as benign by the first tier DNN. A Generative Adversarial Network (GAN)-based method is further used to augment the data for the second tier DNN, in order to minimize misclassification (i.e., misclassify critical faults as benign). The transferability of the proposed method is also investigated (i.e., if a fault criticality model trained on a PE can be transferred to evaluate a different PE). The results show that there exists some inherent transferability across PEs in the same array, mainly due to their identical topologies. On the other hand, more model re-training will be needed if transferability is not met.

5) Transistor-level: Transistor-level fault simulations can be performed only at neuron-level or for small-size networks.

In [99], transistor-level short- and open-circuit defects are injected into the fundamental logic operators of a perceptron, i.e., adders and multipliers. Fault injection experiments in a shallow 2-layer classical fully-digital spatial expansion ANN architecture have demonstrated that hidden layers can tolerate defects even for high defect rates. However, depending on the affected bit or neuron, there may be single defects that can influence the inference accuracy. Defects in hidden layers can be silenced out by a re-training operation with the hardware inthe-loop even for high defect rates. In contrast, the output layer is a defect-sensitive layer and defects in this layer cannot be masked by re-training necessitating a dedicated fault tolerance scheme.

In [100], defect simulations and Monte Carlo analysis taking into consideration the technology Process Design Kit (PDK) are performed for a spiking neuron. The different faulty behaviors are collected and grouped so as to generate an abstract behavioral-level fault model for spiking neurons that capture the effects of low-level faults, i.e., transistor-level defects and process variations. Faulty behaviors turn out to be either catastrophic (i.e., dead neurons that are silenced even in the presence of input activity, saturated neurons that fire nonstop even in the absence of input activity, neurons with a stuck output, etc.) or parametric (i.e., timing variations of the output spike train such as variations in the time-to-first-spike and firing rate). This bottom-up behavioral-level fault modeling approach starting from transistor-level simulations can help generating fault models at a higher abstraction level to be used for software fault injection, while still capturing the effect of underlying root-cause transistor-level faults on the neuron's output, independent of its actual hardware implementation. For example, dead and saturated neuron behavior can be modelled in the output spike train, while timing variations can be modelled by varying various neuron parameters, i.e., the neuron's membrane potential threshold.

6) Chip-level: Software-based fault injection is fast and flexible but it ignores the behavior of the AI hardware accelerator. RTL-level, microarchitectural-level, gate-level, and transistor-level fault injection takes into consideration the

Fig. 12: ML-based method for criticality assessment [98].

hardware, but it is slow and inevitably limited on specific hardware blocks.

FPGA-based hardware accelerators offer the possibility to perform realistic fault injection, including faults that would be difficult to model with software simulation, i.e., faults affecting the configuration memory or controlling modules. They offer also the possibility to evaluate both accuracy degradation and system exceptions, such as system stall and running overtime. Fault injection experiments on accelerators implemented on FPGAs are presented in [101]–[108]. In particular, fault injection experiments are performed on the FPGA-based FINN Quantized Neural Network (QNN) accelerator [56] in [101], [103]–[105], for the tinyTPU implemented on an FPGA in [107], for FPGA implementations of custom ANN accelerators in [102], [106], and for neuromorphic FPGA-based hardware supporting SNNs in [108].

In [109], [110], the soft error reliability of CNN models running on microprocessors is investigated, analyzing the results for different components of the microprocessor and precision bitwidth configurations.

7) Radiation experiments: Experiences from radiation experiments on different GPUs running different DNN models are described in [81]-[84]. In [81], FIT rates are scaled to natural terrestrial environment. Main observations are as follows: (a) crashes are more frequent than SDCs but are less critical as they can at least be detected; (b) all reported SDCs rates are higher than the 10 FIT limit imposed by the ISO 26262 safety standard for automotive, thereby reliability of GPU-based AI accelerators is paramount; (c) FIT is dependent on the technology, i.e., for FinFET it is an order of magnitude lower than that of standard CMOS; (d) Error Correction Code (ECC) protection alone is insufficient to ensure high reliability. In [82], the FIT rate is evaluated for different data precisions, showing that it increases with precision since it depends not only on the fault propagation probability but also on the probability of the fault occurrence. In [83], the run-time of the inference is tuned based on the beam flux such that the chip experiences no more than a single bit flip event during each application run. The study shows that with the ECC/parity checking enabled, single bit errors are corrected, no SDCs is observed, and the most stringent ASIL D requirement imposed by ISO 26262 is met. However, vulnerability to permanent faults is observed, which shows that ECC/parity checking must be complemented with periodic structural tests.

Accelerated radiation testing results for DNNs running on FPGAs are reported in [85], [111]–[113]. In [85], it is shown that applying selective Triple Modular Redundancy (TMR) to

only the most vulnerable layers can mask a high percentage of faults. In [111], [112] it is evaluated how reducing the bit-width used for data representation impacts the radiation sensitivity and failure rate. In [113], it is shown that QNNs trained with fault-aware training are more resilient to soft errors.

Finally, results on the reliability to neutrons of Google Coral TPU are reported in [114], considering elementary operations and several CNN models. It turns out that, despite the high error rate, most neutron induced errors only slightly modify the convolution output and do not change the detection or classification of CNNs.

8) Memristor crossbar-based architectures: The work in [115] studies the fault injection effect in memristor crossbars. The fault model includes stuck-at faults in the conductance of memristors after programming. The conductance error is defined as the difference between the final programmed value and the target value. A device with a conductance error higher than a positive threshold is considered to have a stuck-on fault, i.e., it freezes at a high conductance state. Whereas a conductance error below a negative threshold is considered to have a stuck-off fault, i.e., it freezes in a low conductance state. Fault injection experiments show that inference accuracy drops by more than 50% for a stuck-at memristor rate of 20%.

The work in [116] proposes a fault model for SNNs using memristor crossbars for the connection of the layers. Spike Timing Dependent Plasticity (STDP) is used for learning. Some specificities of the SNN design are that the output neurons are implemented with lateral inhibition and synapses are off when there is no activity on their connected neurons. The fault taxonomy is divided into different synapse faults and neuron faults. Synapse faults include dead synapse, degraded plasticity, and synapse stuck-at faults. Neuron faults include dead neurons and delayed spiking, as well as faults specific to this SNN design, i.e., stuck-at or delayed lateral inhibition and delayed synapse activation fault. Fault injection experiments considered only the worst case faults, i.e., dead neuron and dead synapse faults. Results show that a high fault density is required for noticeable decrease in recognition rate. Moreover, for dead neuron faults, learning on a faulty network is more critical than a fault occurring in a fault-free trained network.

In [117], the susceptibility of ReRAM-based crossbar arrays to single event and cumulative radiation damage is investigated. Simulations are performed using an experimentally derived memristor SPICE model. Results for an ANN trained with the MNIST dataset indicate that the system is highly resistant to transient Single Event Effects (SEEs) thanks to

the low cross section of the memristive device. Moreover, the cumulative ionizing dose level corresponding to the inference failure point is very large, thus it is concluded that ReRAM-based accelerators have high radiation tolerance in normal environments.

In [118], it is proposed to train a ML classifier to predict fault criticality in a DNN mapped to memristor crossbars. The considered fault types are stuck-on and stuck-off conductance in the memristor cell. The training set is generated by: (a) random fault injection for which the overwhelming majority of analyzed faults will be benign; and (b) a Misclassification-Driven Training (MDT) algorithm to quickly identify critical faults so as to have a balanced training set. The MDT algorithm runs an optimization where the DNN parameters, i.e., weights, are perturbed towards maximizing the prediction error. In each iteration, the most significant parameter based on gradient value is chosen. A fault is injected in this parameter and is identified as critical fault if all samples in a batch of the dataset are mispredicted. The features from the benign and critical faults used to train the ML classifier are: (a) fault location; (b) fault type; (c) parameter significance; and (d) parameter deviation amount. The fault criticality analysis can be used to develop a fault tolerance solution that targets only critical faults, thus leading to a significant reduction in the redundancy needed for fault tolerance. The proposed criticality-aware fault tolerance scheme used in this work is to introduce spare columns for remapping only columns in the memristor crossbar that include cells with critical faults.

### C. General observations from fault injection experiments

Some common conclusions in the above fault injection experiments are as follows:

- 1) The fault impact depends on the DNN topology, type of layer, and type of activation function used. Moreover, fault sensitivity across layers and across neurons within a layer can vary by several orders of magnitude. Typically, the output layer is a highly-sensitive layer necessitating a dedicated fault tolerance scheme. Convolution and fully-connected layers tend to spread the SDCs, while subsampling layers tend to mask a significant portion of SDCs. Moreover, very frequently a bimodal behavior is encountered: either the accuracy is negligibly impacted by the fault, or the accuracy drops rapidly even approaching random guessing.

- FIT rates of AI hardware accelerators can exceed safety standards, which shows that reliability and error recovery is of paramount concern.

- 3) The accuracy drop is contingent on the dataset, i.e., the application. The same fault can be benign for one dataset but can be critical for another.

- 4) Fault susceptibility depends on the data type used. DNNs using data types of higher dynamic range are more vulnerable. Still, even QNNs with 2-bit precision are shown to be vulnerable. Susceptibility also depends on the affected bit position, with the MSBs being the most critical.

- Stuck-at-1 faults furnish the largest accuracy drop because typically over 99% of model parameters have zeros in their MSBs.

- 6) For systolic array-based accelerators, by increasing the number of layers or the number of neurons per layer the accuracy drop escalates [127]. This is due to the reuse of the systolic array across multiple layers.

- For memristor crossbar-based architectures, single memristor yield and endurance is very low, necessitating yield rescuing methods.

- 8) For SNNs, saturation neuron faults seem to be the most lethal, although dead neuron faults can also cause significant accuracy drop.

### V. TESTABILITY

### A. Introduction

The goal of testability in AI hardware accelerators is no different from traditional hardware: achieving acceptable test quality under manageable cost. It is confronted by the same problems as in traditional test but with new challenges. While some challenges can be handled by existing tools and solutions, many still remain as major problems in today's Design-For-Testability (DFT) applications. Some typical issues seen in industry are discussed below.

Being domain-specific, AI hardware accelerators usually have some unique features that may not be test friendly. The most prominent one is the sea-of-core design, e.g., 1472 cores in Graphcore GC200 [128], 128x128 systolic array in Google's TPU [129], or even more such as 850K cores in CS-2 [130]. While the notion of "core" in different accelerators may be very different in size, cores in one design are usually identical or very similar. From DFT and physical design perspective, these cores may be too small to implement DFT on a percore basis with a reasonable overhead. On the other hand, incorporating many cores in a physical partition could lead to prohibitive cost for DFT or physical implementation and verification, while not taking the advantage of the similarities among cores. Attempting to achieve best test quality with reasonable overhead, there has been plenty of research on low-cost testing of systems with identical cores [131]-[133]. However for today's AI architectures, an optimal solution might be further explored from other angles, i.e., the function structure may help increase DFT test coverage [134], and function patterns may become part of test patterns [135].

AI applications are memory intensive, hence many AI hardware accelerators require embedded memories with much larger sizes than in traditional ASIC designs. Several MBytes are common practices, i.e., 900MB in Graphcore GC200 [128]. While these memories can be extensively tested and repaired using today's Built-In Self-Test (MBIST) tools, they can present major penalties to Power, Performance and Area (PPA) [136]. Recently, many AI hardware research topics have proposed to bring the computation near to the memory or into the memory, or using large external memory such as High Bandwidth Memory (HBM) or wafer-bonding. These solutions bring in new challenges for testing. For instance, in-memory solutions may require understanding and creation

TABLE II: New testability challenges for AI hardware accelerators and possible solutions.

| Challenges                              | Solutions                            |  |  |

|-----------------------------------------|--------------------------------------|--|--|

| DFT efficiency for designs with large   | Test architectures                   |  |  |

| number of cores                         | 1                                    |  |  |

| Physical design issues for large die    | Physical-aware DFT [136]             |  |  |

| size (i.e., routing and timing)         |                                      |  |  |

| DFT overhead                            | Function-aware DFT [134], [135],     |  |  |

|                                         | [145]                                |  |  |

| Complete DFT solutions for large het-   | Functional test generation [127],    |  |  |

| erogeneous systems                      | [146]–[156]                          |  |  |

| Memory-hungry designs                   | On-line test [157]–[165]             |  |  |

| New market demands (i.e., 0 DPPM        | Yield improvement [115], [166]–[169] |  |  |

| for automotive, on-line test)           | İ                                    |  |  |

| New architectures and faults (i.e., in- | Fault modeling and testing of        |  |  |

| memory computing)                       | memristor-based memory technology    |  |  |

|                                         | [170]–[177]                          |  |  |

| New design paradigms (i.e., 2.5D/3D     | 2.5D/3D IC DFT                       |  |  |

| ICs)                                    |                                      |  |  |

|                                         | Automotive-grade DFT                 |  |  |

of new logic and physical fault models [137], while waferbonding necessitates better solutions for test access, test power control, and yield improvement [138].

Besides the issues mentioned above, existing test challenges for traditional ASIC design may also become increasingly intense in AI applications. For example, current large AI hardware accelerators require hierarchical DFT solutions that are scalable with design size. However, since an AI hardware accelerator is often an heterogeneous system, hierarchical DFT needs a comprehensive solution for automatic DFT insertion, verification, debugging and silicon bring up. Another popular difficulty stems from physical design, i.e., large accelerators often use tile-based design where no dedicated routing channels are reserved for global routing. However, complex DFT designs can create hundreds of global signals for scan, MBIST, debug, etc. This presents a huge overhead for top level implementation and verification. New solutions are necessary for both efficient DFT and easy physical implementations [136] [139].

AI hardware accelerators are also facing pressure from new marketing and technical trends. For example, as one of today's popular applications, automotive grade AI hardware accelerators require more stringent screening than before to ensure zero Defective Parts Per Million (DPPM), which has to be reflected in the architectural level of DFT design. Test data analysis and diagnosis are also critical for yield and reliability learning [140]. Another typical new paradigm is 3D IC design, since large AI hardware accelerators are often limited by physical geometry and cost. Chiplet designs based on 2.5D or 3D methodologies can mitigate the challenges from die size, process, cost, etc., but necessitate a complete set of test solutions from die-level, stack-level, to package-level, which is being addressed in the development of new tools and test flows [141]–[144].

Table II categorizes some of these challenges or issues (left) and possible solutions (right), which are discussed in this paper. This taxonomy is not meant to be comprehensive, but can be representative for many testability activities in the AI hardware designs. Table II cites only works specific to AI hardware, but more generic solutions will be discussed, especially on the test architecture side, that are applicable to AI hardware too.

### B. DFT and ATPG

1) Test architecture: Plenty of research has been conducted on DFT solutions for identical cores to minimize test overhead and maintain test quality. The assumptions of these techniques may still be valid for AI hardware accelerators, but new solutions may be needed to handle large AI designs with limited cost.

A straightforward idea is to broadcast the test stimuli to identical cores while compare their test responses for pass/fail. In [131], a Test Access Mechanism (TAM) is designed to implement on-chip comparison of multiple identical cores. It contains multiple stages of pipelines and several configurations so that each core's test can be implemented in different modes. As such, it not only supports comparing test responses from cores for manufacturing test, but also provides diagnosability of a core during silicon bring up and yield ramp up. With on-chip comparison, test data volume can be significantly reduced, and so is test time. However, for large AI designs with many cores, such broadcasting-style solution may encounter increasing difficulty from routing and top integration. It also needs some manipulations of test patterns from standard Automatic Test Pattern Generation (ATPG) tools.

In [132], another form of TAM is proposed supporting similar features. It is a generalized time-multiplexed TAM, where the compressed test and control data streams are serialized before going into the decompressor. At core level, designers can still utilize the regular decompressor/compactor scan architecture. This simplifies the core level scan channel configuration and decouples it from top-level scan pin assignment. The designers can be flexible in architecting a core-level scan scheme without worrying too much about the top-level. This can be a major benefit for large AI hardware accelerator designs with many cores but very limited scan pin resources. Pattern re-targeting, verification and diagnosis flow are also supported, which are also critical for today's large AI hardware designs.

It can be seen that in order to take the advantage of seaof-core design style in AI hardware, on-chip processing of test data may be preferred when implementation is feasible. There are several varieties in this domain. In [133], a TAM design is presented for chips with multiple isolated identical cores. The proposed pipelined architecture relies on forming nonlinear equations on a very limited number of output pins that compress the outputs from the identical cores and solve them off-chip to reproduce the failure information of each core. It uses test resources similar to testing a single core and also supports accurate failure diagnosis. In [178], a TAM based on majority comparison is presented. It also utilizes an on-chip comparator, yet not to compare with an expected value but with other core's test data to determine a majority value. For example, if more than half of cores in the comparison present the same value, this value is a majority value. This value is then compared with Automatic Test Equipment (ATE) data. The test cost is close to that of a single core.

In [179], yield improvement is considered when a multicore system contains spare cores. A comparison-based TAM that is capable of handling multiple spare cores is proposed.

Fig. 13: DFT solutions at different levels for many core AI hardware accelerator designs.

All faulty cores can be identified via low-cost comparison, and if the spare cores are more than the faulty cores, the chip is still usable. Using spare cores is also common practice in accelerators with many cores. Such designs usually provide a configuration with all good cores and several "partial-good" configurations with different numbers or locations of good cores for yield improvement.

It can be seen that for such DFT solutions to be acceptable, several issues have to be resolved. First, we should be able to manipulate the patterns according to the scan architecture, e.g., re-targeting the core-level patterns to top-level without regenerating the pattern. Second, test quality such as coverage should not be compromised and overhead should be minimized. And finally, from engineering perspective, some critical metrics such as single core diagnosability, verification effort, and routing complexity should also be considered. Fortunately, some of these requirements are already supported well by current mainstream DFT tools.

2) Physical-aware DFT: The above works are mostly developed for traditional multi-core designs. As discussed earlier, many AI hardware accelerator designs share certain features that may render these traditional solutions either impractical or not as efficient, especially on physical design. To address these AI specific problems, some new industrial efforts are reported to make DFT solutions more physical-friendly and hence more practical.

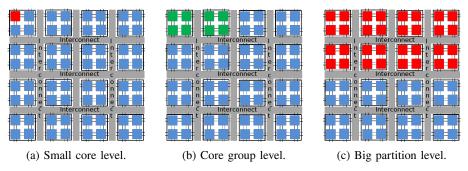

In [136], a comprehensive set of DFT solutions targeting AI hardware accelerators are proposed. In scan test, this work identifies that although accelerators may contain many identical cores, these cores are not as big or as complex as cores in a traditional multi-core system such as a CPU. A typical accelerator for data center applications may contain thousands of "small" cores, as shown in Fig. 13(a). At this core level, any DFT insertion may incur huge PPA penalty, i.e., compression logic, wrapper logic, control logic and routing for DFT signals. It is too small for the DFT overhead to be economical. On the other hand, if we group many small cores together to create a big partition and apply DFT insertion at this level, as seen in Fig. 13(c), the run time, memory requirement, power consumption, pattern count, verification efforts, and other concerns may prevail and render it infeasible, e.g., ATPG or simulation cannot finish in a limited time. Meanwhile, the similarities among cores cannot be effectively exploited.

As a result, in [136] it is proposed to find a "sweet spot" where a suitable number of small cores are viewed as a "core

group" where DFT insertion, verification, pattern generation and other activities are done at this level, as shown in Fig. 13(b). Note that in practice, this usually aligns with physical design requirements, which is probably the most straightforward solution. However, if physical partition is too big or too small, DFT can still make architectural changes to adapt to a suitable size of core group. After this core group is determined, existing technologies such as test data broadcasting, test response on-chip comparison, pattern retargeting, scan channel pin-muxing can be effectively applied.

Note that in practice the logical identical cores may not be physically identical. Synthesis and physical implementations may create various physical instances from the same logic module, converting a homogeneous system to a heterogeneous system from a physical perspective. A feasible DFT solution has to take this into account.

Streaming Scan Network (SSN) [139] is a recently introduced tool that can target these physical challenges. SSN is a bus-based scan data distribution architecture. It contains a scan data bus that travels through all cores in the design, a percore controller (host) with IJTAG support, and regular scan compression logic. The bus is connected to chip-level scan pins and scan data for any core in the system are streamed in through the bus in the form of packets. The concept of packets is different from that in network switching, since SSN packet is a fixed-format data segment that only contains scan data, no address or opcode. The local host in each core is pre-configured through IJTAG to learn how to offload scan data from packets. The expected value can also be streamed in for on-chip comparison. The routing and heterogeneous problems with tile-based designs are also mitigated, since only a single test bus is routed through the entire chip. There is no need to pin-mux the scan channels from various cores to top-level scan pins, and the test bus interface is identical for all cores. Another benefit is that due to the flexibility of packeted test data, any cores can be tested at any time. This can help effectively control test power and improve test channel throughput. With comprehensive considerations of DFT and physical-design requirements, this solution is especially suitable for AI hardware containing many identical cores.

3) Function-aware DFT: Most of the aforementioned technologies are common DFT solutions without in-depth analysis of the function mode of hardware. Many AI hardware accelerator architectures are domain-specific or even application-specific, hence a customized DFT solution designed for a

specific AI architecture is intuitively best for PPA results. To serve this purpose, a DFT architect needs to understand how AI hardware works in function mode such that the DFT design can be optimized accordingly.

In [135], the authors realize that due to the unique architecture of AI hardware, traditional stuck-at and delay tests may not be sufficient. They study test methodologies and DFT requirements specifically for supervised ML systems. Hardware architecture of FIFO-based and scratchpad-based accelerators are analyzed. Test strategies for specific hardware components such as MAC, global buffer, activation functions, etc., are developed. These solutions are more function-like and can help bridge the gap between traditional test patterns and specific AI hardware test requirements. They are also easy for on-line test to ensure product quality.

In [145], post-manufacturing testing of DNN accelerators is discussed. It is argued that the inherent error-tolerance can be leveraged to reduce the fault model size and, thereby, the test time and cost. The idea is that if a fault does not lead to inference accuracy degradation for a given accuracy tolerance margin, then it is non-critical and can be dropped. Only critical faults will be targeted during test application. Two approaches are shown considering a gate-level implementation. The first approach is Boolean Satisfiability (SAT)-based structural testing where a SAT solver exhaustively checks all input combinations to determine the fault criticality and generates a test pattern able to detect it. The second approach is classical functional testing where the actual workload, e.g., images, are used as test inputs.

Function mode operation is also studied in [134] to improve test quality in accelerators with very large number of small cores. As suggested in [136], this scenario can be handled by grouping small cores into a core with a size suitable for both DFT and physical implementations. However it does not exploit the similarity among small cores and test quality may still be impacted if there are interactions between small cores. In typical AI hardware accelerators, there are heavy data traffic between adjacent cores, hence the test coverage on core boundaries is essential. The work in [134] studies intercore connectivity, function data flow, and design homogeneity to derive a C-testable method that can run ATPG for only a single core to reduce test cost and maintain the coverage and diagnosability. By exploring design space, it also presents a hierarchical compaction scheme for on-chip response compaction under reasonable design constraints.

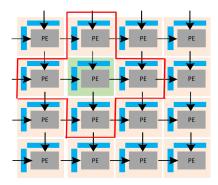

Fig. 14 shows a systolic array example consisting of 16 small cores (or PEs). Dataflow is only from left to right and from top to bottom. Each PE has registers on the input sides but not on the output side. If ATPG is performed at each PE level, coverage will be unacceptable since PE itself is not well wrapped by registers. However, if ATPG run consists of the five adjacent PEs inside the red line, faults in the green PE in the middle will be fully covered. Note that this ATPG pattern can be used to detect faults in all PEs in the same scenario. Since an architecture with small PEs usually contains a large number of them, the overhead of such a scheme is low.

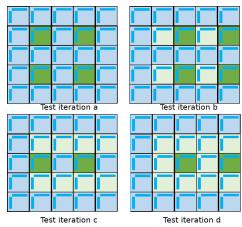

Fig. 15 illustrates the sequence of testing the whole systolic array. ATPG consisting of 5 neighbouring PEs is repeatedly

Fig. 14: Example of a 2D unidirectional pipelined dataflow in 4x4 PE-based systolic array [134].

Fig. 15: Testing 5x5 PE-based systolic array in a checkboard style [134].

used to detect faults in the dark green PEs with high coverage. Each iteration will cover a different set of PEs. Light green PEs are those already covered by previous runs. As a result, for a large systolic array (e.g. 256x256), most PEs can be covered by small ATPG patterns in 4 test runs. The uncovered PEs on the borders can be fully tested in a top-off run.

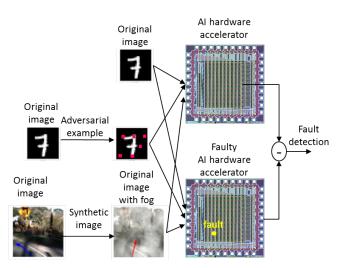

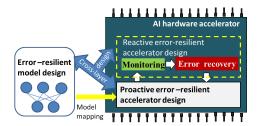

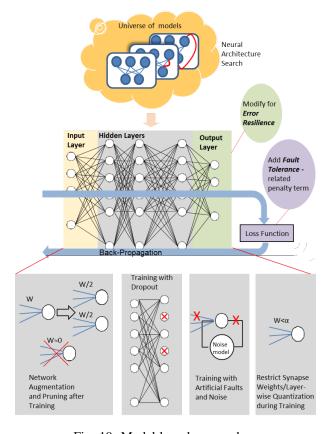

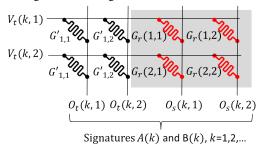

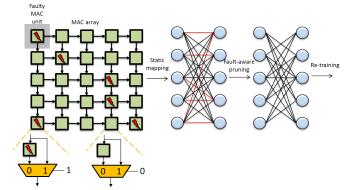

4) Functional test generation: Functional test generation aims at generating inputs, e.g., images, that are capable of sensitizing the fault and propagating its effect to the output, leading to a different prediction with respect to that of the nominal fault-free network. This approach has been demonstrated for ANNs [127], [146]–[149], including memristive crossbar array-based architectures [146], [147], [149], and for SNNs [150], [151]. As shown in Fig. 16, functional tests could be original images from training and testing sets, adversarial examples generated from original images, or synthetic images generated from original images.

More specifically, starting from the available set of input samples, one approach is to select samples that are profoundly similar to other samples belonging to different output classes, i.e., a similarity metric could be average pixel intensity [127]. A second approach is to select samples that have been predicted correctly but with least confidence score [127], [151]. A third approach is to select samples that require more neural network parameter tuning effort during training, where the effort is measured with the change in the loss function in each training step [149]. In [146], [150], it is proposed to

Fig. 16: Functional test generation. The street images are from [154]. The chip image is from [60].

generate adversarial input samples, i.e., perturb available input samples by adding a minimum amount of noise aiming at forcing the predictions of the nominal and faulty network to differ. Another strategy is to craft new samples by attaching watermarks to available input samples [147]. The network is deliberately trained to output a designated classification label for a watermarked input, a technique that is called backdooring. Using the watermarked inputs as validation set, a low validation accuracy indicates a fault. In general, in all aforementioned works, the objective is to use samples that are more vulnerable to misclassification when faults occur. Finally, in [148], a method is proposed for querying a network with a set of specially crafted test inputs, in order to reveal if the model parameters stored in the memory are faulty.

Functional tests can also be employed by the user of the programmed AI hardware accelerator to validate that the embedded DNN model has not undergone any malicious perturbations [152].

A related research direction is generating error-inducing corner test cases for a trained DNN, which thereafter can be used to retrain the DNN and improve its accuracy [153], [154]. These corner test cases are synthetic real-world input images resulting from realistic transformations of seed images and generated in a way such that they activate a large percentage of neurons in the DNN. For example, for DNN models controlling the perception of autonomous cars, these transformations include changing brightness, changing contrast, shearing, rotation, blurring, fog effect, rain effect, etc.

In [155], an alternative functional test generation is proposed, demonstrated for memristive crossbar-array architectures targeting detection of classification accuracy drop due to process variability. This approach is inspired from the alternate analog circuit testing paradigm [180], [181]. First, a compact test set of input images is generated with the maximum possible diversity of responses, and a feature vector is defined at the output of the network. An outlier detector in the form of an one-class classifier is trained in the space of features using as training set instances of the DNN with process

Fig. 17: Functional testing of a biologically-inspired spiking neuron.

variations but with acceptable accuracy. Applying the compact test set, the outlier detector serves as a first screening of nonconforming devices. Devices that pass this test are presented to a regressor which is trained using the same training set to map the features to the DNN classification accuracy. A guard-band is defined around the minimum tolerated accuracy to classify devices as passing, failing or fuzzy, where the fuzzy devices fall within the guard-band and are subject to standard testing using the complete image set to obtain a precise decision. Failing and fuzzy devices found in production testing can be combined in batches with prior training data to retrain the outlier detector and regressor.

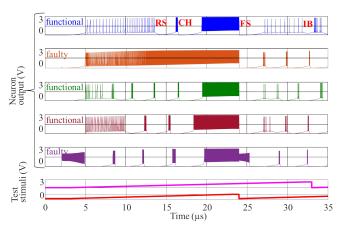

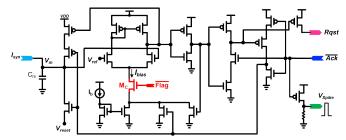

In [156], a functional BIST scheme is proposed for biologically-inspired spiking neurons. The idea is to test that the neuron is capable of producing all the basic firing patterns, i.e., regular spiking (RS), fast spiking (FS), intrinsic bursting (IB), and chattering (CH). The test stimulus is composed of low-resolution ramps applied at the bias nodes of the neuron such that in one pass all firing patterns appear. If one or more firing patterns are missing, then the neuron is declared to be faulty. Examples of functional and faulty neuron responses are illustrated in Fig. 17.

### C. On-line test

1) ATPG and functional testing: Many AI accelerators are used in datacenter applications, where reliability, availability and serviceability requirements demand certain level of online test of memories and logic. However, such tests involve both function mode and test mode, imposing more difficulties to DFT designs.

A recent effort is reported by Amazon AWS in [182], where high-speed serdes I/Os in an AI hardware accelerator are used to transport scan test patterns to test the processing cores. Test patterns are converted to a format compliant with corresponding protocol and transported from PCIe/USB, through standard AXI fabric, to cores. Cores under test will be idled from workload and isolated from the rest of logic. Although the major advantage of this solution is test time reduction, it supports native on-line test capability, which is critical in a cloud scenario.

Returning to the functional test generation methods in [127], [146]–[151] discussed in Section V-B4, as the resultant functional test set is compact, it can be also fed periodically during mission mode in idle times towards functional safety.

In [158], different self-test approaches are proposed for the compute units and control units of an accelerator. For compute units that do not contain complex sequential logic, test patterns based on combinational ATPG are generated. For the control units that contain finite state machines and sequential logic, it is proposed to use functional tests in the form of executing DNN layers with carefully-crafted input and weight values. The methodology is enhanced in [159] to cover both stuck-at and delay fault models for both unit types.

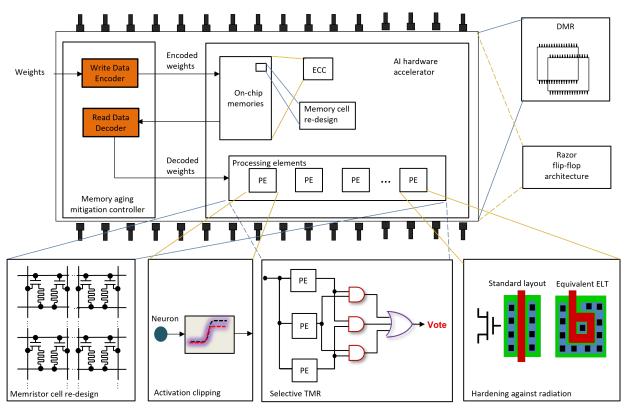

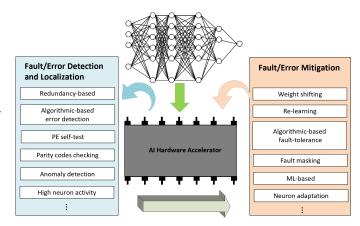

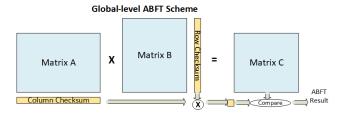

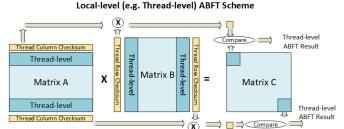

2) Checksums and error codes: The idea here is to build invariants into the accelerator that hold true only in fault-free operation while they are violated in the presence of faults. Thus, checking them concurrently with the operation can point to abnormal operation. Invariants can be built using checksums or error codes.