## Electron emission device made from planar nanowires

Thomas Lerond, Yevheniia Chernukha, Maxime Berthe, Francois Vaurette, D. Deresmes, Dorina Papanastasiou, Daniel Bellet, Laurent Gangloff, Thierry Melin

## ▶ To cite this version:

Thomas Lerond, Yevheniia Chernukha, Maxime Berthe, Francois Vaurette, D. Deresmes, et al.. Electron emission device made from planar nanowires. Journées du GDR Nanosciences with near-field microscopy under ultra high vacuum 2022, Nov 2022, Paris, France. hal-03955837

HAL Id: hal-03955837

https://hal.science/hal-03955837

Submitted on 25 Jan 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Electron emission device made from planar nanowires

Thomas Lerond<sup>1</sup>, Yevheniia Chernukha<sup>1</sup>, <u>Maxime Berthe</u><sup>1</sup>, François Vaurette<sup>1</sup>, Dominique Deresmes<sup>1</sup>, Dorina T. Papanastasiou<sup>2</sup>, Daniel Bellet<sup>2</sup>, Laurent Gangloff<sup>3</sup>, and Thierry Mélin<sup>1</sup>

- 1. IEMN, CNRS-8520, University of Lille, Avenue Poincaré, Cité Scientifique, 59652 Villeneuve d'Ascq, France

- 2. LMGP Phelma Minatec 3 parvis Louis Néel 38016 Grenoble, France

- 3. Laboratoire de Micro et Nano Physique, THALES RESEARCH & TECHNOLOGY, Campus Polytechnique, 1 avenue

Augustin Fresnel, 91767 Palaiseau Cedex, France

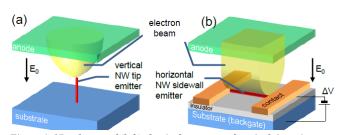

Recently, Thales patented an alternative to tip-plane field emission structure(1) in order to address two main drawbacks: (i) poorly active native apex surface ( $\sim$ R²); (ii) complexity to handle out-of-plane structure fabrication with high control over parameters (physical parameters and geometry). Derived from a general capacitive system, a backgated structure was proposed (Fig.1.b). An insulating layer is placed in between a conductive substrate (backgate) and horizontal top NWs. By applying a voltage difference  $\Delta V$  between NWs and backgate, capacitively induced charges appear on NW sidewalls.

In the ANR PANASSE project, a process has been established to synthesize full-metal-nanowire devices to be characterized in a multiple-probe STM-SEM setup.

Figure 1. 3D schemes of (left) classical structure of vertical tip emitter and (right) new cathode structure based on backgated NW sidewalls field emitter (not to scale).

Under SEM Monitoring, one probe is in contact with the backgate, one probe is set in contact with a flatlying nanowire and a third probe acts as anode at a controlled height above the NW to measure the emitted electrons.

The process and its evolution compared to the experimental results will be presented : process

details and alternative strategies, scheme of measurements, functional results, future developments.

## REFERENCES

1. J.-P. Mazellier and L. Sabaut, Patent reg. 1601057, 07/07/2016.