## Advanced TCAD Simulation of Tunnel Oxide Degradation for EEPROM Applications

F. Matteo, R. Simola, J. Postel-Pellerin, K. Coulie

### ▶ To cite this version:

F. Matteo, R. Simola, J. Postel-Pellerin, K. Coulie. Advanced TCAD Simulation of Tunnel Oxide Degradation for EEPROM Applications. IEEE 4th International Conference on Dielectrics (ICD 2022), Jul 2022, Palerme, Italy. pp.764-768, 10.1109/ICD53806.2022.9863611. hal-03941192

## HAL Id: hal-03941192 https://hal.science/hal-03941192

Submitted on 27 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Advanced TCAD Simulation of Tunnel Oxide Degradation for EEPROM Applications

F. Matteo<sup>1,2</sup>, R. Simola<sup>1</sup>, J. Postel-Pellerin<sup>2</sup>, K. Coulié<sup>2</sup>

<sup>1</sup>STMicroelectronics Rousset ZI de Peynier AV Célestin Coq 13790 Rousset, France

*Abstract-* In this paper we have simulated dynamic Constant Voltage Stress (CVS) and subsequent degradation of MOS capacitor representative of Non-Volatile Memory (NVM) devices. Oxide degradation was modelled through trap defects generation at SiO<sub>2</sub>/Si interface and SiO<sub>2</sub> bulk. A very good agreement was obtained between simulation and experimental data.

#### I. INTRODUCTION

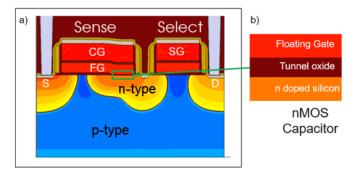

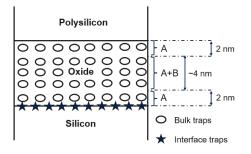

Charge Storage Floating Gate-based Non-Volatile Memory Electrically Erasable Programmable Read Only Memory (EEPROM) and Flash-EEPROM (or, more simply, Flash), are among the most successful devices ever introduced in the semiconductor market [1]. Either stand-alone in Storage Charge Memory (SCM) or embedded in Microcontroller Units (MCUs), they are at the very core of every modern digital equipment, from digital cameras to smartphones, tablets and personal computers, to mention a few. Their operating principle relies in charge transfer from/to a polysilicon layer (called floating gate) through a thin silicon dioxide layer (called tunnel oxide) when appropriate voltage biases are applied to control gate and silicon substrate (Fig.1a, for EEPROM). The basic element for both EEPROM and Flash is therefore a simple PolySi/SiO<sub>2</sub>/Si stack planar capacitor, commonly called MOS capacitor (Fig.1b). The oxide integrity is what ultimately determines the devices' reliability, and consequently, it has been extensively studied in the past three decades [2-5].

Figure 1: a) EEPROM 2T device, consisting of a Sense Transistor (for data storage) and Select Transistor (for data accessing). b) Basic storage element of Sense device is a planar capacitor. <sup>2</sup>Aix-Marseille University, CNRS, IM2NP 5 rue Enrico Fermi 13451 Marseille, France

In this paper, we have performed Technology Computer Aided Design (TCAD) simulations of MOS oxide degradation due to Constant Voltage Stress (CVS). The applied voltage stress is representative of the operating conditions of a 110 nm-CMOS technology node-based 4Mbit EEPROM manufactured by STMicroelectronics and recently introduced in the semiconductor market [6].

#### **II. TCAD Simulation Framework**

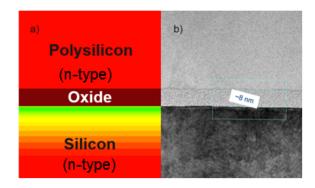

This study was carried out using Sentaurus<sup>TM</sup> Suite by SYNOPSYS®, for both process and electrical simulations [7]. Process simulation was based on a 110 nm embedded NVM CMOS technology. All the relevant front-end process flow steps were included up to metal contacts. The obtained TCAD nMOS structure is shown in Fig.2a and corresponds to a large plate capacitor device with an area of  $1 \times 10^5 \ \mu\text{m}^2$  (in this 2D simulation total surface was taken into account by a scaling area factor). Tunnel oxide thickness is around 8 nm, as measured in TEM cross section (Fig.2b).

Figure 2: Planar MOS Capacitor. a) TCAD process simulation. b) TEM cross section

#### A. Charge transport across tunnel oxide

For typical EEPROM operating voltages (> 10 V) and tunnel oxide thickness (7  $\sim$  10 nm), charge transport across the silicon dioxide is driven by quantum mechanical tunneling through a trapezoidal potential barrier. This phenomenon was first described by Fowler and Nordheim (FN), with a simple closed-form expression for the current density  $J_{FN}$  that is given by [8, 9]:

$$J_{FN} = AF^2 \exp\left(-\frac{B}{F}\right) \tag{1}$$

where *F* is the electric field at the Si/SiO<sub>2</sub> interface and *A*, *B* are physical related parameters. Despite its utility in modeling high field tunneling current thanks to its reliability and simplicity, this model doesn't cover direct tunneling for ultra-thin oxide and trap assisted tunneling of degraded oxide. Consequently, a more general model [10] is used in this paper, that considers band edge profile along the entire path across the SiO<sub>2</sub> between the two points connected by tunneling, also called Non-Local Tunneling (NLT) [8]. The key parameter in NLT is the electron effective tunneling mass, which has been set equal to 0.48 times the electron mass. Moreover, coupled with trap capture and emission models described in [8][11][12], the simulation accounts for traps assisted tunneling (TAT) thus covering a wide spectrum of tunneling phenomena.

#### B. Degradation model

Several models for oxide degradation under high voltage stress can be found in the literature. According to anode hole injection (AHI) mechanism, some of the tunneling electrons reaching the anode with high-enough energy will generate electron-hole pairs in the oxide, and some of the generated holes will be trapped in the oxide [13-15]. This mechanism was initially heralded as the origin of dielectric breakdown, a claim that was first disputed [16] and later disproven [17]. According to another model, hot electrons release hydrogen (HR) near the anode which drift or diffuse through SiO<sub>2</sub> consequently generating defects [18,19,20]. In this paper, defects generation is modeled by stress-induced breaking of Si-H bonds (depassivation). From first-order kinetics [8][21] Si-H concentration  $N_{hb}$  is given by:

$$\frac{dN_{hb}}{dt} = -\nu * N_{hb} \tag{2}$$

where v is a reaction constant that can be described approximately by an Arrhenius law [22]:

$$v = v_0 \exp\left(\frac{-\varepsilon_A}{kT}\right) k_{tun} \tag{3}$$

where  $v_0$  is the reaction depassivation constant, k is the Boltzmann constant, T is the absolute temperature, and  $k_{tun} = 1 + \delta_{tun} (I_t/I_0)^{\rho_{tun}}$  is an enhancement factor due to tunneling current  $I_t$ . The activation energy  $\varepsilon_A$  (not constant) is given by:

$$\varepsilon_A = \varepsilon_A^{\ 0} - \delta_\perp |F|^{\rho_\perp} + kT(1+\beta F) \ln\left(\frac{N-N_{hb}}{N-N_{hb}^0}\right) \tag{4}$$

where  $\varepsilon_A^0$  is the activation energy constant,  $N_{hb}^0$  is the initial Si-H concentration and  $\beta$ ,  $\delta_{\perp}$ ,  $\rho_{\perp}$  are field-enhanced parameters. *N* is the trap concentration saturation value and

varies as a function of energy within the bandgap,  $N - N_{hb}$  is the concentration of hydrogen released (i.e concentration of traps) and  $N - N_{hb}^0$  corresponds to the initial concentration of traps which we have set to 1×10 cm<sup>-2</sup>. Although this model was first developed to describe Si-H breaking mechanism occurring at Si/SiO<sub>2</sub> interface, we have extended it to the bulk oxide where we have set  $N - N_{hb}^0$  equal to 1×10<sup>12</sup> cm<sup>-3</sup>. The complete parameter set used for simulations is reported on Table 1 below.

Table 1: Degradation model parameters set

| Parameter         | Value                 | Unit     |

|-------------------|-----------------------|----------|

| $v_0$             | $2.1 \times 10^{-12}$ | $s^{-1}$ |

| $\varepsilon_A^0$ | 0                     | eV       |

| Т                 | 300                   | Κ        |

| β                 | $1.0 \times 10^{-7}$  |          |

| $\delta_{tun}$    | 8.9×10 <sup>5</sup>   |          |

| $ ho_{tun}$       | 0.9                   |          |

| $\delta_{\perp}$  | 1e-3                  |          |

| $ ho_{\perp}$     | 0.33                  |          |

#### C. Traps distribution

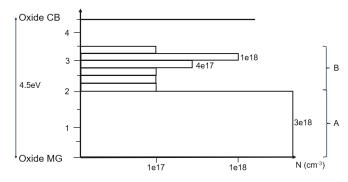

Distribution of the trap concentration parameter N in bulk oxide and at Si/SiO<sub>2</sub> interface are reported in Fig.3 and Fig .4, respectively. For bulk oxide traps, following [23] we have assumed that for each acceptor trap there is a corresponding donor trap. Thus, traps in SiO<sub>2</sub> are generated in the whole bandgap (but only acceptors levels are represented in Fig.3).

Figure 3: Distribution of traps parameter N in bulk SiO<sub>2</sub>. Only the upper part of the band gap is shown (energy levels relative to the mid-gap).

Since we neglected impact ionization during electron injection into polysilicon gate, donor traps stay mostly neutral because no hole are available for trapping. Deep acceptor traps (A), which extend 2 eV from mid-gap (MG), are mostly filled with electrons and have low probability for electron release. This negative trapped charge is responsible for Fowler-Nordheim efficiency reduction. Shallow traps (B) located within the range 2 eV to 3.5 eV from MG, have high capture and emission rates and trigger TAT mechanism. Finally, we assumed that very shallow traps located above 3.5 eV from MG are neutral with a too low capture probability to have any significant effect. We have therefore neglected them.

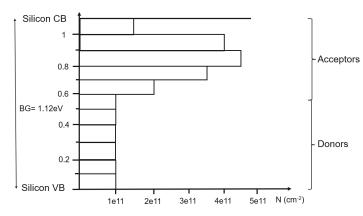

At Si/SiO<sub>2</sub> interface traps spread over the entire silicon bandgap (Fig. 4), both acceptor and donor states are therefore included in this model. Acceptor states, however, have higher concentrations. The concentration peak located at 0.8 eV from the valence band edge is the typical signature of Pb0 center [24] and was reported by the authors in [25], who performed similar stress to ours.

Figure 4: Distribution of traps parameter N at Si/SiO<sub>2</sub> interface. Both acceptors and donors states are included in the simulation.

The spatial location of traps is schematically represented in Fig.5. At the interface, we set a uniform spatial distribution along the entire interface. Furthermore, shallow traps (B) were distributed mainly at the center of the oxide (when they are positioned close to interface, it induces nonrealistic simulated tunneling current value), whereas deep traps (A) evenly distributed inside SiO2.

Figure 5: Traps spatial distribution. Deep traps (A) are uniformly distributed in the oxide. Shallow traps (B) are mainly located at the SiO<sub>2</sub> center.

#### III. Results & Discussion

#### A. Constant Voltage Stress (CVS)

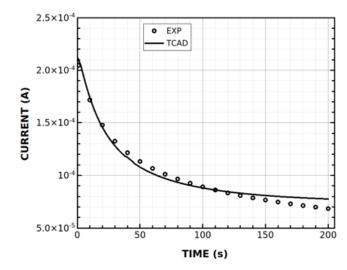

In Fig.6, the measured and simulated CVS curves are represented. Since deep traps located near MG (A traps in Fig.3) have highest electron capture section, they will charge negatively, leading to the observed gate current decrease during CVS.

Figure 6: Gate current during Constant Voltage Stress (CVS).

This mechanism is well captured in our simulations, leading to the excellent agreement with experimental data.

#### B. Capacitance vs Voltage (C-V)

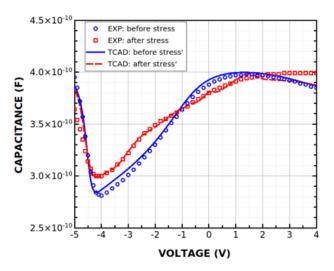

The measured and simulated C-V curves before and after stress are shown in Fig.7, where we can appreciate a very good agreement between the two. The reason is briefly explained in the following considerations  $Si/SiO_2$  interface traps are very sensitivity to the electrostatic field, since small change in the applied voltage (few volts) drastically modify their occupancy state. They therefore strongly influence the C-V shape after oxide degradation.

Figure 7: Capacitance vs voltage before and after stress.

A detailed analysis of C-V after laser induced degradation on MOS [26] showed that donor interface traps (i.e traps with an energy level between the valence band and the mid gap) are the first to release their holes becoming neutral from positively charged, then acceptor interface traps (i.e traps with an energy level between de mid gap and the conduction band) capture electrons and become negatively charged. Assuming this to be also valid after CVS induced oxide degradation, from -4.5 V to -3 V the capacitance degradation is ruled by donor traps, then from -3 V to -1.5 V by acceptor traps and, finally, above -1.5 V there is the cumulate influence of filled interface traps and bulk oxide traps. The small C-V mismatch in the strong inversion regime (above 2V), where poly-depletion effects are known to take place, are likely due to poor TCAD electrical modelling of PolySi.

#### C. Gate Tunneling Current

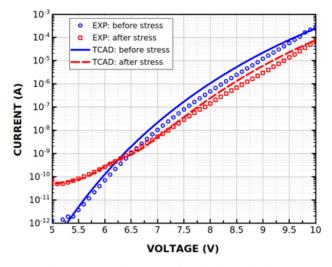

In Fig.8, the measured and simulated I-V curves are represented before and after CVS.

Figure 8: Capacitance vs voltage before and after stress

For an oxide of approximatively 8 nm thick and at low electric field, gate current is mostly due to TAT. At high field, gate current main contributor is Fowler-Nordheim tunneling mechanism.

Concerning the unstressed nMOS capacitor, gate current follows, as expected, a pure Fowler-Nordheim injection curve from 5.5 V to 10 V. On stressed nMOS capacitor, from 5 V to 6 V, TAT is the main contributor to gate current. A combination of TAT and Fowler-Nordheim is observed between 6V to 7V and above, Fowler-Nordheim mechanism becomes preponderant.

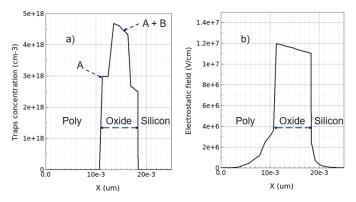

Vertical cuts (TCAD simulated structure) of volumetric trap concentration after stress and electrostatic field at Vg=10V are shown in Fig.9. Due to higher electrostatic field close to the gate, traps concentration increase.

Figure 9: a) Vertical cut of volumetric trap concentration and b) Vertical cut of electrostatic field

However, the impact of electric field is probably overestimated here since we have neglected traps generation due to high kinetic energy injected electrons.

#### V. Conclusion

In this paper, we have performed advanced TCAD simulation of NVM device tunnel oxide degradation during Constant Voltage Stress. We showed that Si/SiO<sub>2</sub> interface traps modify MOS electrostatic behavior throughout capacitance versus voltage measure, whereas SiO<sub>2</sub> bulk acceptor-type traps lead to Fowler-Nordheim tunneling current decrease and to TAT at lower electric field. A very good agreement with experiments was obtained for C-V and I-V pre and post stress. The model used in these simulations could be further improved using dedicated degradation kinetics for bulk and interface traps. Finally, this approach can be easily implemented for endurance and retention simulation of industrial NVM devices.

#### REFERENCES

- [1] P. Capelletti "Non Volatile Memory Evolution and Revolution," IEEE IEDM, 2015

- [2] Papadas C. et al., "Model for Programming Window Degradation in FLOTOX

- EEPROM cells," IEEE Electron Device Letters, vol. 13, no. 2, pp. 89 91, 1992.

[3] Aritome S. et al., "Reliability issues of Flash memory cells, Proceedings of the

- [5] Anone S. et al., Renability issues of rules includy cells, Proceedings of the IEEE, vol. 81, no. 5, pp. 776-788, 1993.

[4] G. Pananakakis, G. Ghibaudo, C. Papadas, E. Vincent and R. Kies, "Generalized

- [4] G. Pananakakis, G. Ghibaudo, C. Papadas, E. Vincent and R. Kies, "Generalized trapping kinetic model for the oxide degradation after Fowler-Nordheim uniform gate stress", J. Appl. Phys, vol. 82, 1997, pp 2548.

- [5] Schroder D. K. and Babcock J. A., "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," J. Appl. Phys, vol. 94, no. 1, pp. 1-18, 2003.

- [6] https://www.st.com/content/st\_com/en/about/media-center/press-

- item.html/p4211.html

- [7] <u>https://www.synopsys.com/silicon/tcad.html</u>

[8] Sentaurus™ Device User Guide Version Q-2019.12, Dec 2019.

- [8] Sentaurus™ Device User Guide Version Q-2019.12, Dec 2019.

[9] Lezlinger M. and Snow E. H., "Fowler-Nordheim tunneling into thermally grown

- SiO2," J. Appl. Phys., vol. 40, no. 1, pp. 278–283, 1969.

[10] Ieong M. et al., "Comparison of Raised and Schottky Source/Drain MOSFETs Using

- a Novel Tunneling Contact Model," IEEE IEDM, pp. 733–736, 1998. [11] F. Jiménez-Molinos et al., "Direct and trap-assisted elastic tunneling through ultra-

- thin gate oxides," Journal of Applied Physics, vol. 91, no. 8, pp. 5116–5124, 2002.

A. Palma et al., "Quantum two-dimensional calculation of time constants of random

- [12] A. Fahna et al., Quantum two-unnerstonar carculation of time constants of random telegraph signals in metal-oxide–semiconductor structures," Physical Review B, vol. 56, no. 15, pp. 9565–9574, 1997.

- [13] I. C. Chen, S. Holland and C. Hu, "Hole trapping and breakdown in thin SiO2", IEEE Electron Device Letters, EDL-7(3), pp. 164-167, 1986.

- [14] K. F.Schuegraf and C. Hu "Hole injection SiO2 breakdown model for very low voltage lifetime extrapolation. IEEE Transactions on Electron Devices, 41(5), pp.761-766, 1994.

- [15] K.F.Schuegraf and C. Hu. "Effects of temperature and defects on breakdown lifetime of thin SiO2 at very low voltage", IEEE Transactions on Electron Devices, 41(7), pp.1227-1232, 1994.

- [16] D. J. DiMaria, "Hole trapping, substrate currents, and breakdown in thin silicon dioxide films" in IEEE Electron Device Letters, vol. 16, no. 5, pp. 184-186, May 1995

- [17] E. M. Vogel, J. S. Suehle, M. D. Edelstein, B. Wang, Y. Chen and J. B. Bernstein, "Reliability of ultrathin silicon dioxide under combined substrate hot-electron and constant voltage tunneling stress," in IEEE Transactions on Electron Devices, vol. 47, no. 6, pp. 1183-1191, June 2002

- [18] D. J. DiMaria, E. Cartier, and D. Arnold, "Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon," in *J. Appl. Phys.*, vol. 73, no. 7, pp. 3367-3384, 1993

- [19] D. J. DiMaria, D. A. Buchanan, J. H. Stathis, and R. E. Stahlbush, "Interface states induced by the presence of trapped holes near the silicon silicon-dioxide interface," J. Appl. Phys., vol. 77, pp. 2032–2040, 1995.

- [20] J. Sune and E. Wu, "A new quantitative hydrogen-based model for ultra-thin oxide breakdown," 2001 Symposium on VLSI Technology. Digest of Technical Papers (IEEE Cat. No.01 CH37184), pp. 97-98, 2001

- [21] A. Plonka, "Time-Dependent Reactivity of Species in Condensed Media," Lecture Notes in Chemistry, vol. 40, Berlin: Springer, 1986.

- [22] O. Penzin et al., "MOSFET Degradation Kinetics and Its Simulation," IEEE Transactions on Electron Devices, vol. 50, no. 6, pp. 1445–1450, 2003.

- [23] R. S. Scott et al., "Properties of High-Voltage Stress Generated Traps in Thin Silicon Oxide," IEEE Transactions on electron devices, vol. 43, no. 7, pp. 1133-1143, 1996

- [24] Pei Li et al., "First-principles study of defects in amorphous-SiO2/Si interfaces," J. Appl. Phys, vol. 483, pp. 231-240, 2019

- [25] P. Chiquet et al., "Investigation of the effects of constant voltage stress on thin SiO2 layers using dynamic measurement protocols," Microelectronics Reliability, pp. 1895-1900, 2012

- [26] R. Llido et al., "Effects of 1064 nm laser on MOS capacitor," Microelectronics Reliability, vol. 52, pp. 1816-1821, 2012