## Non-volatile tuning of normally-on and off states of deep depletion ZrO 2 /Oterminated high voltage diamond MOSFET

Beatriz Soto, Marine Couret, Jesús Cañas, Anne Castelan, Nicolas C. Rouger, Daniel Araujo, María del Pilar Villar, Julien Pernot

#### ▶ To cite this version:

Beatriz Soto, Marine Couret, Jesús Cañas, Anne Castelan, Nicolas C. Rouger, et al.. Non-volatile tuning of normally-on and off states of deep depletion ZrO 2 /Oterminated high voltage diamond MOSFET. Diamond and Related Materials, 2023, 134, pp.109802. 10.1016/j.diamond.2023.109802. hal-03867147v2

## HAL Id: hal-03867147 https://hal.science/hal-03867147v2

Submitted on 8 Mar 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Non-volatile tuning of normally-on and off states of deep depletion ZrO2/O-terminated high voltage diamond MOSFET

DIAMOND RELATED MATERIALS

B. Soto, M. Couret, J. Canñas, A. Castelan, N. Rouger, D. Araujo, M.P. Villar, J. Pernot

PII: S0925-9635(23)00127-9

DOI: https://doi.org/10.1016/j.diamond.2023.109802

Reference: DIAMAT 109802

To appear in: Diamond & Related Materials

Received date: 9 November 2022

Revised date: 4 February 2023

Accepted date: 19 February 2023

Please cite this article as: B. Soto, M. Couret, J. Canñas, et al., Non-volatile tuning of normally-on and off states of deep depletion ZrO2/O-terminated high voltage diamond MOSFET, *Diamond & Related Materials* (2023), https://doi.org/10.1016/j.diamond.2023.109802

This is a PDF file of an article that has undergone enhancements after acceptance, such as the addition of a cover page and metadata, and formatting for readability, but it is not yet the definitive version of record. This version will undergo additional copyediting, typesetting and review before it is published in its final form, but we are providing this version to give early visibility of the article. Please note that, during the production process, errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

© 2023 Published by Elsevier B.V.

## Non-volatile tuning of normally-on and off states of deep depletion ZrO<sub>2</sub>/O-terminated high voltage diamond MOSFET

B.Soto<sup>a,b,\*</sup>, M. Couret<sup>c</sup>, J. Canñas<sup>a,b</sup>, A. Castelan<sup>c,d</sup>, N. Rouger<sup>c</sup>, D. Araujo<sup>a</sup>, M.P. Villar<sup>a</sup>, J. Pernot<sup>b</sup>

<sup>a</sup>Dpt. Ciencia de los Materiales e IM y QI, Universidad de Cádiz, 11510, Pto. Real, Cádiz, Spain Univ. Grenoble Alpes, CNRS, Grenoble INP, Institut Néel, 5°000, Grenoble, France

<sup>c</sup>LAPLACE, Université de Toulouse, CNRS,, 31000, Toulouse, France

<sup>d</sup>Institut Catholique d'Arts et Métiers, ICAM,, 31000, Toulouse, France

#### **Abstract**

Based on the stability of the deep depletior regime in diamond and the outstanding properties of this promising material for its use in power devices, p-channel deep depletion metal oxide semiconductor field effect transistors were fabricated on a (001) Ib nitrogen-doped high pressure high temperature diamond substate. Taking advantage of the new concept of the non-volatile diamond-based photo switch, it is demonstrated that it is possible to tune the normally-on and normally-off states of the factorial transistor by configuring the pn-junction space charge region. The devices under study was designed following an interdigital-like and a circular-like architectures presenting low threshold voltages (between 3 V and -3 V), an on/off ratio of 10<sup>7</sup> and a critical electric field numerically assessed of 9 MV.cm<sup>-1</sup> at room temperature. This new degree of freedom opens the route for diamond based power electronics.

Email addresses: beatriz.soto@uca.es (B. Soto), pilar.villar@uca.es (M.P. Villar),

julien.pernot@neel.cnrs.fr (J. Pernot)

<sup>\*</sup> Corresponding author. Tel.: +34 956 016427

*Keywords:* D3MOSFET, critical electric field, p-channel, N-doping, Non-volatile photo switch, threshold voltage control, O-terminated diamond, ZrO<sub>2</sub>

#### 1. Introduction

The next step of the development of power electronics coes through the Ultra Wide Bandgap Semiconductors (UWBGS) because the bandgap i correlated with many of the figures-of-merit and because the performance increases non-lived ly with it. Particularly, BFoM is related to the cubic of the critical electric field, it is if related to the energy bandgap. The relationship between them is a power law depend in a whose refinement is discussed in a recent study by Slobodyan et al [1]. The increase of the breakdown voltage promotes the UWBGS superior performance and breakdown voltage is directly related to the critical electric field. All leading then to an improvement in the specific on-resistance and breakdown voltage trade-off. Among these materials, the focus to about two decades has been on AlGaN/AlN or Ga<sub>2</sub>O<sub>3</sub>, which have been intensively studie <sup>1</sup> for n-channel FETs operation. However, p-channel FETs are far to reach the performance from the n-channel ones due to the low hole mobility. In this line, and in addition to other properties such as the high breakdown field (> 10 MV.cm<sup>-1</sup>) and the high thermal conductivity (>2.200 W.m<sup>-1</sup>K<sup>-1</sup>) makes diamond [2, 3, 4] the most complete and promising material for its use in power electronics. A recent study on diamond based p-channel wide-bandgap FETs [5] shows a normally-off p-channel transistor using Hydrogen-terminated diamond surface and h-BN as the gate insulator, exhibiting a room temperature mobility of 680 cm<sup>2</sup>.V<sup>-1</sup>s<sup>-1</sup> following a promising direction for the development of wide-bandgap complementary circuits.

Moreover, efforts have been done by different groups working on diamond MOSFETs to tune the threshold voltage and control the normally-on, normally-off states. In particular, low threshold voltages between -2 V and -4 V have been achieved using an inversion channel MOSFET OH-terminated [6] or two 2D-Hole MOSFETs partially oxidized [7, 8] (normally-on devices that can be tuned as normally-off).

This work presents an alternative p-channel device: a MOSFET based on O-terminated p-type diamond working in the deep depletion regime [9, 10, 11, 12] combined with a non volatile junction field effect transistor (JFET), the N-doped diamond substrate will be used as the gate of the latter. On one hand, the MOSFET, using ZrO<sub>2</sub> as the gate dielectric, can be electrically controlled no matter the light exposure and works in the  $\alpha$  p depletion regimen similarly to those previously reported using  $Al_2O_3$  as the gate oxide. On the other hand, it is well known that n-type doped diamond shows deep donor levels f. om the conduction band, in particular Nitrogen creates donor levels at 1.7 eV and Phosphorus et 0.58 eV. As a result, at room temperature, electrons remain bounded to the dopants and they cannot be electrically controlled, keeping the diamond layer insulating. Instead of raising temperature to activate the dopants, an alternative way to promote some of those bound electrons to the conduction band is achieved by external illumination. In this case, this promotion leading to an increase of the free carrier concentration is achievable by photon absorption. Hence, with a combination of optical and electrical signals, it is possible to control the pn-junction on/off states in a non-volatile manner. Once the light is removed, the JFET gate cannot be electrically driven anymore until a new light exposure so the system can only be electrically driven by the MOSFET.

The proof of concept of the non-volatility of a diamond pn-junction used as a photo-switch was recently published and described by Masante *et al.* [13]. In such a work, it can be found

experimental evidence of the non-volatile character of the optically activated JFET in a sequence replicated several times to ensure the reliability. The junction with a Nitrogen-doped n-type diamond is only able to commute under an optical signal since no electrostatic modulation can occur in the dark.

The present work proposes an original way of application: we demonstrate that zirconia can be used as gate dielectric in a D3MOSFET and that  $V_{TH}$  can be tuned by controlling optically and electrically the back junction FET. This latter paves the way to the implementation of this kind of devices in circuits without the need of having complementary channel transistors. Also the device can reach a critical electric field of 9 MV.cm<sup>-1</sup> located at the pn-junction showing that the mechanism of breakdown is independent of the transistor back junction-FET configuration.

#### 2. Fabrication

The sample structure is a strot. Consisting of a Ib nitrogen-doped high pressure high temperature (001) diamond substrate with a p-type diamond layer on top. From the CV measurement, it has been deduced for this top layer a net doping concentration of  $9.2 \times 10^{15}$  cm<sup>-1</sup>. The extracted free hole concentration is estimated to be  $4 \times 10^{13}$  cm<sup>-3</sup> assuming a compensation of 10% [14].

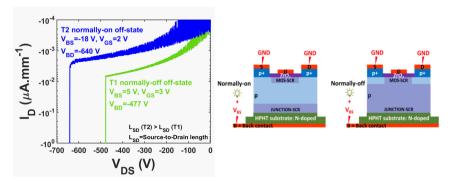

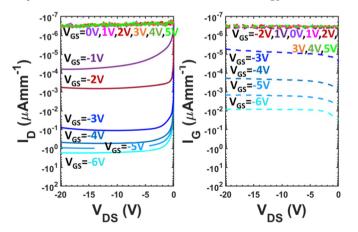

Figure 1: Top view, cross-section and parameters of the transistors under study: a) Interdigital-like D3MOSFET (channel length, L=30  $\mu$  m and channel width, W=4.2 mm). b) Circular-like D3MOSFETs: T1, T3 sharing same channel parameters (channel length, L=30  $\mu$  m and channel width, W=0.75 mm); T2 with larger channel width and channel length (channel length, L=50  $\mu$  m

and channel width, W=0.82 mm).

A selectively localized heavily doped p-type diamond layer was deposited on the p layer to create ohmic contacts (p+, doping concentration of the order of 10<sup>21</sup> cm<sup>-3</sup>). Both p-type diamond layers were grown using a microwave plasma assisted chemical vapor deposition (MPCVD) technique. The oxygen terminated p-doped diamond surface was achieved through a vacuum ultraviolet ozone treatment [15].

Fig.1 shows a schematic of the transistors design exhibiting both the top view and the cross-section of the geometries and parameters for an intercipital-like architecture (Fig.1a)) and a circular-like one (Fig.1b)). The purpose of this study is not focus on the on-state performance but the demonstration of the tunability of a device's formally-on/off behaviour thanks to the non-volatility of diamond used as a photo switch. In spite of that, the interdigital-like geometry was used in order to test new design to recrease the total current by enlarging the channel width and optimizing the footprint surface of the whole device.

The sample was covered with a couple of layers of Ti/Ni (5/300 nm-thick) using the electron beam (ebeam) everyonation technique in order to, after the application of an  $O_2$  plasma, mesa-etch the sample approximately 1  $\mu$  m and avoid a short-circuited transistor. To achieve the ohmic contacts and before the gate oxide deposition, we made use of the selective metallic p+ layer on which a stack of Ti/Pt/Au (with 30/30/30 nm-thick metallic layers) were fabricated by laser lithography (Heidelberg DWL66FS) and ebeam evaporation to finally apply a standard lift-off technique.

The gate dielectric was deposited by atomic layer deposition (ALD) using a Savannah 100 deposition system from Cambridge NanoTech. The ZrO<sub>2</sub> was grown using a precursor of tetrakis

dimethylamido zirconium IV and water vapor as the oxidant alternating  $N_2$  purges. Pulse and exposure times in ALD process were 15 ms and 7 s, alternatively, during 700 cycles, typical base pressure was of the order of  $10^{-1}$  Torr and temperature for deposition was 400 °C.

Other two contacts were fabricated: one of them on the top of the oxide to form the MOS-gate contact, fabricated by laser lithography and ebeam evaporation with same metallic stack and thickness as for the ohmic ones. The other contact, on the back, were added by directly applying Silver paste. Finally, the electrical measurements were performed by a Keithley Source Measure Units two channel 2612B and one channel 2410 models.

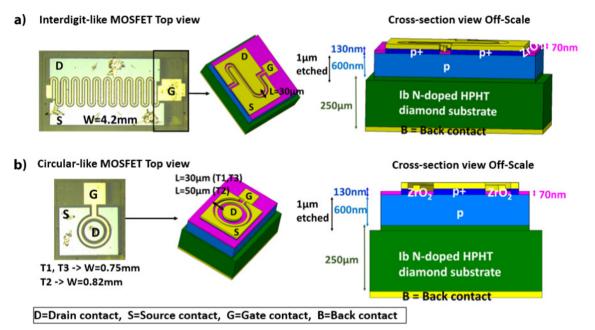

## 3. Concept & Experimental setup

The principle of this hybrid device as neurioned earlier and shown in Fig.2, is based on two properties of diamond: on the one hand, the use of the pn junction as an additional gate to control the space charge region (SCR expansion from the junction since N-donors in the diamond substrate can be activated by visuale light (a polychromatic white LED with an optical power density of 11 mW.cm<sup>-2</sup>). Hence, hanks to a fourth electrode (back electrode on the substrate), the pn-junction SCR could be configured by applying a potential difference between the Ib N-doped HPHT substrate and the source under light and then freezing the configuration by removing the light. The Ib type N-doped substrate is insulating under any external energy source because the dopants are deep donors with a high activation energy of the order of 1.7 eV. When the light is switched on, the photon absorption allows some of the bound electrons to be promoted to the conduction band and then the junction can be electrically driven to enlarge or reduce the potential barrier between the p and n sides (corresponding to reverse or forward biasing the junction). After the light being removed, recombination processes of carriers take place which recover the

insulating property of the N-doped diamond substrate and so the electro-optically imposed potential barrier between the two sides of the junction remains fixed.

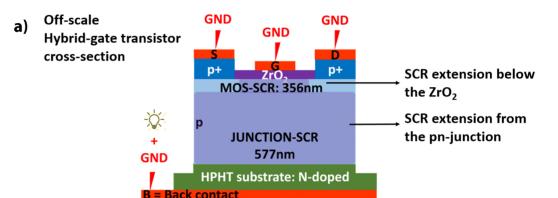

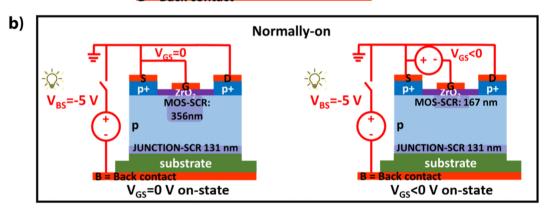

Figure 2: Working principle: gates control of the SCR (in purple) in a 600 nm-thick p-type diamond layer, to modulate the channel on/off states. a) SCR extensions when the back gate has been connected to ground under a light source and after removing the illumination, the MOS gate is connected to ground. b) Normally-on: the substrate has been biased at -5 V under a light source and after removing the illumination, the MOS is biased at  $V_{G^{\circ}}$  (reft) and  $V_{GS}$ =-1 V (right). c) Normally-off: the substrate has been biased at -3 V under a light source and after removing the illumination, the MOS is biased at  $V_{GS}$ =0 V (left) and  $V_{GS}$ -1 V (right).

On the other hand, the stability of the deep depletion regime is complimentarily used to control the on/off states by biasing the MOS gate to open/close the channel. The metallic contacts distribution is shown in Fig.1 cross sec icn.

Fig.2 presents how the SCK is extended below the gate and above the pn junction depending on the applied higs on the gate and the back, respectively. The SCR below the MOS gate is deduced from experimental CV curve. The JFET SCR extension, h, has been calculated at the pn junction interface following the equations:

$$V_{bi} = \frac{k_B T}{q} ln(\frac{N_a N_d}{n_i^2}) \tag{1}$$

$$h = \sqrt{\frac{2\varepsilon_s \varepsilon_0 (V_{bi} + V_{BS})}{qN_a}}$$

(2)

From Eq.1 and Eq.2  $V_{bi}$  is the built-in potential,  $k_B$  the Boltzmann constant, T the temperature, q the elementary electric charge,  $N_a$  and  $N_d$  the B and N-doping concentrations,  $n_i$  the intrinsic

carrier concentration, h is the junction SCR extension,  $\varepsilon_s$  and  $\varepsilon_0$  are the relative dielectric constant of diamond and the vacuum permittivity, respectively and  $V_{BS}$  the bias applied on the back contact relative to the source electrode on the front side.

The experimental setup requires then four electrodes to operate: two for the ohmic contacts (source and drain), one gate contact to control the diamond deep depletion MOSFET (D3MOSFET) and one gate contact on the back which in combination with a light source will allow the control of the junction field effect transistor (JFET). A<sup>11</sup> the measurements were taken under vacuum (typically with a pressure of  $10^{-4}$ - $10^{-3}$  Torr) are a room temperature.

Firstly, the connections were made between the following electrodes: the one on the back contact on which a bias is applied to the substrate, and two context and drain connected to the ground keeping the MOS gate floating. So, we apply a bias on the back under light exposure during 10min for stabilization to later remove the light to freeze the system in a certain back side SCR extension configuration dependent on the bias applied to the pn junction waiting another 10min. After that, the electrode on the back contact is removed and the pn-junction system remains frozen. The non-optimization of the N-doped substrate acting as a photo-switch leads to a long commutation time, the 1% in inutes holding time is safety precautions to be 100% sure that the device is in steady sate and to maintain reproducible states. Times of commutation of few ms have been achieved as a combination of optical wavelength and power density, temperature, doping and geometry. These results have been recently reported at a conference[16]. Further optimization and improvements in n-type back gate layers can even reduce this time constant to be more compatible with applications.

Then, in order to control the D3MOSFET we connect: the source to ground and the MOS gate and the drain to two voltage sources keeping the back floating. At this point, a quasi-static

potential difference between drain and source is established for different MOS gate voltages to get the current-voltage characteristics.

The process is repeated according to the different configurations we can set up using the JFET: from a completely suppressed SCR caused by the forward biasing of the junction ( $V_{BS}$ =-20 V) or intermediate configurations (-20 V <  $V_{BS}$  <-3 V) resulting in a normally-on D3MOSFET, passing through the case where the depletion due to the MOS structure and the one caused by the junction meet (-3 V \le V\_{BS} < 9 V, normally-off D3MOSFET), to find by the also normally-off case where the p-type diamond layer is fully depleted from the projunction ( $V_{BS} \ge 9V$ ), in this later situation the channel is permanently closed and it is no long or possible to control it with the MOS gate.

## 4. Current density versus Vo. age Characteristics

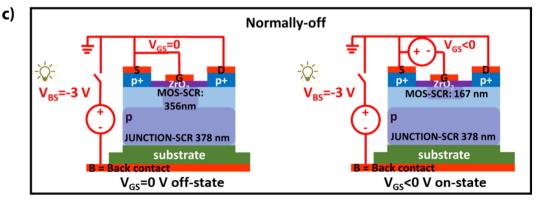

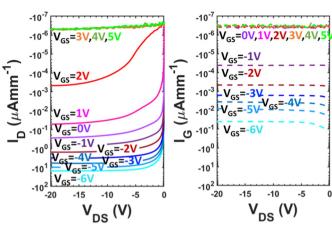

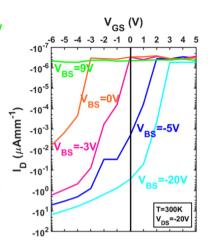

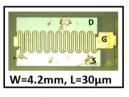

As discussed in Sec.3, the bia  $\{\rho_i\}$  lied to the substrate affects the D3MOSFET behaviour from normally-on to normally-on. Typical current density as a function of drain bias for the interdigit can be found in Fig.3: from the normally-on in Fig.3a) in which the transition of the on/off states is given  $\psi_{ij}$  a  $V_{ij}$ =3 V, followed by the off/on states in Fig.3b) in the normally-off configuration (the channel is closed at  $V_{GS} \ge 0$  V). The on/off ratio is  $10^7$ .

Figure 3: Interdigital-like D3MOSFET current density characteristics as a function of drain bias for different configurations of the pn junction space charge region at room temperature: a)  $V_{BS}$ =-20 V, Normally-on starting condition. b)  $V_{BS}$ =-3 V, Normally-off starting condition. c) Transfer characteristics of a combination of a diamond D3MOSFET with a non volatile diamond JFET at room temperature showing the shift in threshold voltage and the change from normally-on to

normally-off behaviour.

A maximum saturation current density of the order of tens of  $\mu$  A is reached where the SCR due to the N-doped diamond substrate is completely suppressed in the p-layer with a maximum value of leakage current of tens of nA. As we extend the SCR through the p-layer from the junction, the saturation current decreases. The different transfer characteristics as a function of the bias applied to the substrate is evidence of the change in the D5MOSFET's normally-on/off behaviour as it is plotted in Fig.3c).

The geometry of the interdigital-like D3MOSFET was thought to increase the total current. Unfortunately, the results are lower than expected for large channel widths (a comparison of the total current achieved by the different transistor) as ailable in Appendix A). The choice of the interdigit transfer characteristics was made has on the intention to show in a clearer way the threshold voltage shift.

## 5. Breakdown voltage and critical electric field evaluation

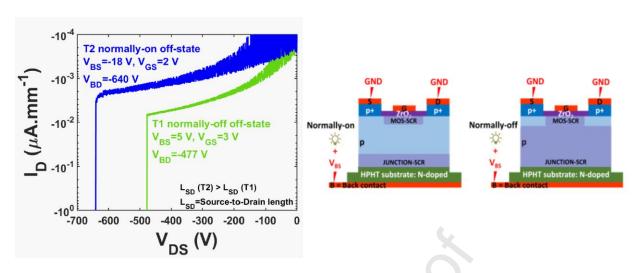

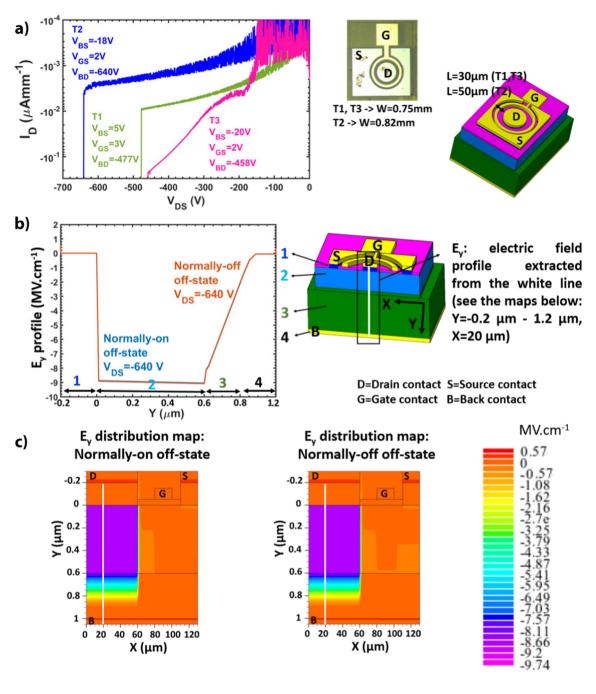

Similarly to how the TV characteristics were performed, the blocking capabilities has been tested by configuring optically and electrically the back pn junction to extend/remove the SCR in a desired configuration, then the illumination is removed and the back contact remains floating. Immediately after, the D3MOSFET is electrically driven to reach the off-state. Fig.4a) shows the different values for the breakdown voltage reached by T1, T2 and T3 D3MOSFETs at room temperature (T1, T2 and T3 are presented in Fig.1). T1 and T3 share the same channel parameters: they were tested in two different configurations of the pn junction SCR, T1 when the  $V_{BS}$  is set to reach the JFET off-state and the p-type layer is fully depleted ( $V_{BS}$ =5 V, JFET pn junction biased

in reverse regime) and T3 when the SCR due to the pn junction is fully removed (V<sub>BS</sub>=-20 V, JFET pn junction biased in forward regime) and the SCR due to the MOS gate closes the channel. From the experimental results, it seems that the on/off behaviour configured by the JFET does not affect the blocking capability performance since similar transistors in different configurations present similar breakdown voltage. In turn, T2 presents a higher breakdown voltage as expected since the distance source-drain in this case is larger. Transistor T3 was damaged and rendered unusable after forcing the transistor to withstand high voltages, however the transistors so-called T1 and T2 were protected with a resistance in series and we found that the breakdown is nondestructive and the measure is repeatable and reliable.

Figure 4: a) Blocking capabilities tested at room temperature for circular-like transistors T1, T2, T3 configuring the pn-juntion space charge region for normally-on (T2,T3) and normally-off (T1) biasing the MOSFET in the off-state. The high voltage measurement were perform in a keithley SMU 2410 model whose limit of detection is  $10^{-5}\mu$ A. b) On the left, the Y-component electric field profile for a normally-on (eque) and a normally-off (orange) configuration using a circular-like MOSFET in the off-state with channel length L=50  $\mu$ m and channel width W=0.8 mm. On the right, the cut line (in white) location from which the profile has been extracted. c) the corresponding electric field distribution maps for the the Y-component when normally-on off-state configuration (on the left) and normally-off off-state configuration (on the right).

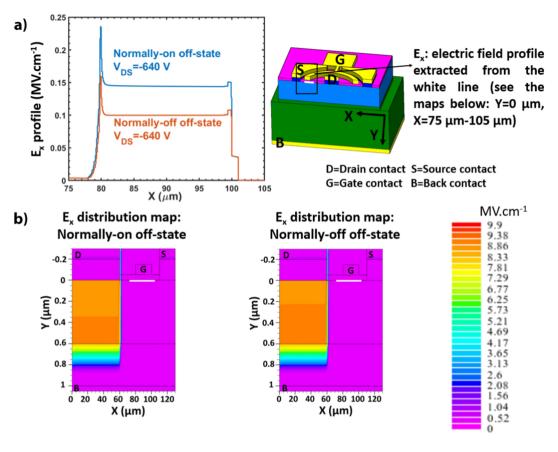

Figure 5: Finite element calculation for the X-component of the electric field: a) On the left, the X-component electric field profile for a normally-on (blue) and a normally-off (orange) configuration using a circular-like MOSFET in the off-state with channel length L=50  $\mu$  m and

channel width W=0.8 mm. On the right, the cut line (in white) location from which the profile has been extracted. b) the corresponding electric field distribution maps for the the X-component when normally-on off-state configuration (on the left) and normally-off off-state configuration (on the right).

Finite element calculation was used to evaluate the electric field in order to understand the breakdown mechanisms. The following parameters were introduced in the simulation for a circular-like device with a channel width of W=0.8mm and a channel length of L=50  $\mu$  m (corresponding to T2): 600 nm-thick p-type diamond layer with a doping concentration of  $N_a=10^{16}$ cm<sup>-3</sup> and 10% compensation; 400 nm-thick N-doped sunstrate with a doping concentration of  $N_d=10^{18}$  cm<sup>-3</sup> and 70 nm-thick oxide with an wide-diamond interface charges density of Q=1.5×10<sup>12</sup> cm<sup>-2</sup> based of previous studies or MOS capacitors [17]. Fig.4c) shows the calculation of the electric field distribution for the Y-component when the D3MOSFET is normally-on biased in off-state (Fig.4c) left map) and rormally-off biased in off-state (Fig.4c) right map) by applying a potential difference between the source and the back contact under illumination and then, after removing the light source Dissing the D3MOSFET to reach the off-state by applying a potential difference between the so, ree and the gate. Through the evaluation of the electric field profile for its Y-component (Fig.4b) left), it can be observed there is no difference between normally-on and off behaviour and we found a critical electric field at the junction between 8.9 MV.cm<sup>-1</sup> (normally-on off-state) - 9.1 MV.cm<sup>-1</sup> (normally-off off-state) at  $V_{DS}$ =-650 V. Fig.5b) shows the calculation of the electric field distribution for the X-component when the D3MOSFET is normally-on biased in off-state (Fig.5b) left map) and normally-off biased in off-state (Fig.5b) right map) by applying a potential difference between the source and the back contact under

illumination and then, after removing the light source, biasing the D3MOSFET to reach the off-state by applying a potential difference between the source and the gate. Through the evaluation of the electric field profile for its X-component (Fig.5a) left), it can be observed a low electric field up to  $0.24 \text{ MV.cm}^{-1}$  at  $V_{DS}$ =-650 V.

The electric field distribution was evaluated using the circular-like T2 D3MOSFET since it has larger source-to-drain length and consequently the largest breakdown voltage. A proper evaluation of the high voltage withstand capability of the interdigital-like D3MOSFET could not be performed. The total area of interdigit is larger than the circular like ones and so more likely to have killer defects which can affect the blocking capabilities and can lead to smaller breakdown voltage than those obtained for a small finger or circular unique gate. However, in absence of defects, interdigit should achieve similar value of the kdown to those reached by T1 and T3 as they share the source-to-drain length.

If one manage to get a low (vertical) leakage, the pn-junction will generate most of the potential gradient (electric field). As a consequence, it is evidenced (see Fig.5) that the MOS region only has a low electric field. The mechanism is nondestructive, so the transistor is capable of recovering after a while and the measurements become repeatable.

An optimization of the diamond epilayers stacks (doping, thickness and architecture) will make possible the association of complementary and efficient diamond FETs improving the on-state performance as well as the blocking capabilities. The details for future improvements in terms of current density are recently described in detail by Masante *et al.* [12]. Regarding the space-charge effects, the drain-source voltage sweep has no effect on the back gate SCR extension. The main advantage of the non-volatility of the diamond photo-switch used here for the control of the threshold voltage is that the back gate cannot electrically drive the junction during the

MOSFET operation (no illumination).

#### 6. Conclusion

The present study demonstrates that a combination of diamond lateral MOSFET and JFET with vertical pn gate junction can be used to tune the normally-on/off behaviour of the device controlling the threshold voltage (keeping it low with values in the range between -3 V and 3 V).

In addition, the double-gate transistor showed a nondertrue ive breakdown mechanism, reaching a critical electric field of 9 MV.cm<sup>-1</sup>, this is a 'right electric field value, close to the theoretical vertical breakdown expected at around 10 1 V.cm<sup>-1</sup> (but still subject to discussion). Such a breakdown occurs at the vertical pn-junction and it is independent of its SCR configuration (electrically controlled under illumination) and electric field crowding effect was observed in the vicinity of the zirconia.

This hybrid device paves the way to a potential application in complex circuits and also answers to the safety requirements of normally-off state for power electronics.

#### **Declaration of interests**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Data availability statement

The data that support the findings of this study are available from the corresponding author

upon reasonable request.

#### **Authors contribution**

B. Soto: Conceptualization, Methodology, Data curation, Formal analysis, Writing original draft. M. Couret: Finite element calculation. J. Cañas: Conceptualization. A. Castelan: Finite element calculation. N. Rouger: Conceptualization, Resources, Writing review & editing. D. Araujo: Resources, Supervision, Formal analysis, Writing review & editing, Funding acquisition, Project administration. M.P. Villar: Resources, Supervision, Formal analysis, Writing review & editing, Funding acquisition, Project administration. J. Pernot: Conceptualization, Resources, Supervision, Formal analysis, Writing review & editing.

#### Acknowledgements

The authors would like to thank the Ministerio de Economia y Competitividad of the Spanish Government for funding under Grant No TEC-2017-86347-C-2-1-R (DiamMOS project) and from ESP2017-9182 I, Pt D2019-110219RB-100 and PID2020-117201RB-C21 projects; The Junta de Andalucía (Comunidad Autónoma of Andalusia Government, Spain) for funding from FEDER-UCA18-106470, FEDER-UCA18-107851 and P20-00946 projects and as well as the grants for stays in research centres from the Promotion Programme of Research Activity of the University of Cadiz.

The simulation were conducted in the context of the ANR LSDMOSFET project: ANR-21-CE50-0036 AAPG-2021 PRCE.

We would also thank to Martin Kah and David Eon (Institut Néel, Université Grenoble

Alpes, CNRS, France) for fruitful discussions. And Nanofab (Institut Néel, CNRS, France) for clean room facilities.

# Appendix A. Transfer characteristics: evaluation on the different D3MOSFETs

As it was mentioned above, the interdigital-like D3MOSFL? was designed to have larger channel width with respect to the circular-like ones in order to increase the total current. Unfortunately, the total current of the interdigital-like D3MOSFET increases by less than one order of magnitude with respect to the circular shaped to assistors, a result lower than expected. Fig.A.6 provides the total current achieved by directent transistors used in this work: Fig.A.6a) related to the interdigit and Fig.A.6b) and Fig.A.6c) related to transistors T1 and T2, respectively.

Figure A.6: a) Interdigital-like D3MOS  $^{\text{FL}}$ T with channel width 4.2 mm and source-to-drain length 30  $\mu$  m: total current as a function of the gate bias for different bias applied to the back substrate. b) Circular-like  $^{\text{FL}}$ MOSFET T1 with channel width 0.75 mm and source-to-drain length 30  $\mu$  m: total current as a function of the gate bias for different bias applied to the back substrate. c) Circular-like D3MOSFET T2 with channel width 0.82 mm and source-to-drain length 50  $\mu$  m: total current as a function of the gate bias for different bias applied to the back substrate.

In all three D3MOSFETs, it is observed that they can operate as normally-on or normally-off depending on the electro-optically induced polarization on the back gate (N-doped substrate). These results support the use of diamond non-volatile photo-switch as a new degree of

freedom in the design and control of p-channel transistors.

## References

- O. Slobodyan, J. Flicker, J. Dickerson, J. Shoemaker, A. Binder, T. S. et al., Analysis of the dependence of critical electric field on semiconductor bandgap, J. Mater. Res. 37 (2022) 849–865. doi:https://doi.org/10.1557/s43578-021-00465-2.

- J. Y. Tsao, S. Chowdhury, M. A. Hollis, D. Jena, N. M. Johnson, K. A. J. et al.,

Ultrawide-bandgap semiconductors: Research opportunities and challenges, Adv.

Electron. Mater. 4 (1) (2018) 1600501.

doi:https://doi.org/10.1002/celry.201600501.

- N. Donato, N. Rouger, J. Pernot, G. Lo 1gol ardi, F. Udrea, Diamond power devices: state of the art, modelling, figures of merit and future perspective, J. Phys. D: Appl. Phys. 53 (2020) 093001. doi:https.//goi.org/10.1088/1361-6463/ab4eab.

- [4] M. W. Geis, T. C. Wade C. H. Wuorio, T. H. Fedynyshyn, B. Duncan, M. E. P. et al., Progress toward dian.and power field-effect transistors, Phys. Status Solidi A. 215 (22) (2018) 1800681. aci:https://doi.org/10.1002/pssa.201800681.

- Y. Sasama, T. Kageura, M. Imur, K. Watanabe, T. Taniguchi, T. U. et al, High-mobility p-channel wide-bandgap transistors based on hydrogen-terminated diamond/hexagonal boron nitride heterostructures, Nat. Electron. 5 (2022) 37–44.

doi:https://doi.org/10.1038/s41928-021-00689-4.

- [6] T. Matsumoto, H. Kato, K. Oyama, T. Makino, M. Ogura, D. T. et al., Inversion channel diamond metal-oxide-semiconductor field-effect transistor with normally off characteristics, Sci. Rep. 6 (2016) 31585.

- doi:https://doi.org/10.1038/srep31585.

- Y. Kitabayashi, T. Kudo, H. Tsuboi, T. Yamada, D. Xu, M. S. et al., Normally-off c-h diamond mosfets with partial c-o channel achieving 2-kv breakdown voltage, IEEE Electron Devices Lett. 38 (3) (2017) 363–366.

doi:https://doi.org/10.1109/LED.2017.2661340.

- [8] N. Oi, T. Kudo, M. Inaba, S. Okubo, S. Onoda, A. H. et al., Normally-off two-dimensional hole gas diamond mosfets through nitrogen-ion implantation, EEE Electron Devices Lett. 40 (6) (2019) 933–936.

doi:https://doi.org/10.1109/LED.2013.2912211.

- [9] T. Pham, J. Pernot, G. Perez, D. Eon, E. Gheera rt, N. Rouger, Deep-depletion mode boron-doped monocrystalline diamond neterizate semiconductor field effect transistor, IEEE Electron Device Lett. 38 (11, '2',17) 1571–1574.

doi:https://doi.org/10.1109/LED.2017.2755718.

- [10] T. Pham, J. Pernot, C. Mas and Electron Devices Meeting (IEDM), 2017, pp. diamond mosfet, in: 2017 IEEE International Electron Devices Meeting (IEDM), 2017, pp. 25.4.1–25.4.4.

- [11] T. Pham, N. Rouger, C. Masante, G. Chicot, F. Udrea, D. E. et al., Deep depletion concept for diamond mosfet, Appl. Phys. Lett. 111 (17) (2017) 173503.

doi:https://doi.org/10.1063/1.4997975.

- [12] C. Masante, N. Rouger, J. Pernot, Recent progress in deep-depletion diamond metal–oxide–semiconductor field-effect transistors, J. Phys. D: Appl. Phys. 54 (23) (2021) 233002. doi:https://doi.org/10.1088/1361-6463/abe8fe.

- [13] C. Masante, M. Kah, C. Hébert, N. Rouger, J. Pernot, Non-volatile photo-switch using a

- diamond pn junction, Adv. Electron. Mater. 8 (1) (2022) 2100542. doi:https://doi.org/10.1002/aelm.202100542.

- [14] A. Traoré, S. Koizumi, J. Pernot, Effect of n- and p-type doping concentrations and compensation on the electrical properties of semiconducting diamond, Phys. Status Solidi A 213 (8) (2016) 2036–2043.

doi:https://doi.org/10.1002/pssa.201600407.

- [15] T. Teraji, Y. Garino, Y. Koide, T. Ito, Low-leakage p-type dia mond schottky diodes prepared using vacuum ultraviolet light/ozone treatme..., 1. Appl. Phys. 105 (2009) 126109. doi:https://doi.org/10.1063/1.3153986.

- [16] M. Kah, C. Masante, F. Donatini, G. Jacopin, N. Kouger, J. Pernot, Commutation time of non-volatile photo-switch based on diamon, inaction field effect transistor, in: 15th

International Conference on New Liamond and Nano Carbons NDNC 2022, Kanazawa,

Japan, 2022. doi:https://doi.org/10.1002/aelm.202100542.

- [17] B. Soto, J. Cañas, D. Araujo, M. F. Villar, J. Pernot, Transport mechanism in o-terminated diamond/zro2 based moscos, Diamond Relat. Mater. 121 (2022) 108745.

doi:https://woi.org/10.1016/j.diamond.2021.108745.

Graphical abstract

## Highlights

- Non-volatile tuning of normally-on/off behavior of an O-terminated diamond-based p-channel MOSFET

- Control of the threshold voltage: from -3 V to 3 V.

- Breakdown voltage: measured up to -640 V.

- Critical electric field evaluation: finite element calculations show a 9 MV.cm<sup>-1</sup> peak

**Graphics Abstract**

Figure 1

Figure 2

#### a) IV characteristic and leakage at V<sub>BS</sub>=-20 V

#### c) Transfer characteristics

#### b) IV characteristic and leakage at V<sub>BS</sub>=-3 V

D=Drain contact S=Source contact G=Gate contact B=Back contact

Figure 3

Figure 4

Figure 5