# Optimizing resource efficiencies for scalable full-stack quantum computers

Marco Fellous-Asiani, Jing Hao Chai, Yvain Thonnart, Hui Khoon Ng, Robert S. Whitney, Alexia Auffèves

### ▶ To cite this version:

Marco Fellous-Asiani, Jing Hao Chai, Yvain Thonnart, Hui Khoon Ng, Robert S. Whitney, et al.. Optimizing resource efficiencies for scalable full-stack quantum computers. PRX Quantum, 2023, 4 (4), pp.040319. 10.1103/PRXQuantum.4.040319. hal-03832698

HAL Id: hal-03832698

https://hal.science/hal-03832698

Submitted on 24 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Optimizing Resource Efficiencies for Scalable Full-Stack Quantum Computers

Marco Fellous-Asiani, <sup>1,2,\*</sup> Jing Hao Chai, <sup>2,3,4</sup> Yvain Thonnart, <sup>5</sup> Hui Khoon Ng, <sup>6,3,7,†</sup> Robert S. Whitney, <sup>8,‡</sup> and Alexia Auffèves, <sup>2,3,7,§</sup>

<sup>1</sup> Centre for Quantum Optical Technologies, Centre of New Technologies, University of Warsaw, Banacha 2c, Warsaw 02-097, Poland

<sup>2</sup> Université Grenoble Alpes, CNRS, Grenoble INP, Institut Néel, Grenoble 38000, France <sup>3</sup> Centre for Quantum Technologies, National University of Singapore, Singapore 117543, Singapore <sup>4</sup> Entropica Labs, 186b Telok Ayer Street, 068632 Singapore

<sup>5</sup> Université Grenoble Alpes, French Alternative Energies and Atomic Energy Commission (CEA)—Laboratory for Integration of Systems and Technology (LIST), Grenoble F-38000, France

<sup>6</sup> Yale–National University of Singapore (NUS) College, Singapore

<sup>7</sup> MajuLab, CNRS-UCA-SU-NUS-NTU International Joint Research Laboratory, Singapore <sup>8</sup> Université Grenoble Alpes, CNRS, Laboratoire de Physique et Modélisation des Milieux Condensés (LPMMC), Grenoble 38000, France

(Received 29 November 2022; accepted 31 July 2023; published 30 October 2023)

In the race to build scalable quantum computers, minimizing the resource consumption of their full stack to achieve a target performance becomes crucial. It mandates a synergy of fundamental physics and engineering: the former for the microscopic aspects of computing performance and the latter for the macroscopic resource consumption. For this, we propose a holistic methodology dubbed metric noise resource (MNR) that is able to quantify and optimize all aspects of the full-stack quantum computer, bringing together concepts from quantum physics (e.g., noise on the qubits), quantum information (e.g., computing architecture and type of error correction), and enabling technologies (e.g., cryogenics, control electronics, and wiring). This holistic approach allows us to define and study resource efficiencies as ratios between performance and resource cost. As a proof of concept, we use MNR to minimize the power consumption of a full-stack quantum computer, performing noisy or fault-tolerant computing with a target performance for the task of interest. Comparing this with a classical processor performing the same task. we identify a quantum energy advantage in regimes of parameters distinct from the commonly considered quantum computational advantage. This provides a previously overlooked practical argument for building quantum computers. While our illustration uses highly idealized parameters inspired by superconducting qubits with concatenated error correction, the methodology is universal—it applies to other qubits and error-correcting codes—and it provides experimenters with guidelines to build energy-efficient quantum computers. In some regimes of high energy consumption, it can reduce this consumption by orders of magnitude. Overall, our methodology lays the theoretical foundation for resource-efficient quantum technologies.

DOI: 10.1103/PRXQuantum.4.040319

#### I. INTRODUCTION

There is a lot of excitement and hope that quantum information processing will help us solve problems of

Published by the American Physical Society under the terms of the Creative Commons Attribution 4.0 International license. Further distribution of this work must maintain attribution to the author(s) and the published article's title, journal citation, and DOI. importance for society. Potential applications are numerous, ranging from optimization [1,2] and cryptography [3,4] to finance [5,6]. The simulation of quantum systems [7–9] for quantum chemistry and material science holds the promise of understanding fundamental phenomena and designing new materials and new drugs [10,11]. Different experimental platforms are currently investigated, including photonics [12], ion traps [13], spin qubits [14], and superconducting qubits [15], among others [16–18]. Owing to impressive experimental efforts, qubit fidelities are starting to approach the fault-tolerance thresholds for scalable quantum computers. Quantum computational advantages have been claimed [19,20], even as the concept is still being discussed [21,22].

<sup>\*</sup>fellous.asiani.marco@gmail.com

<sup>†</sup>huikhoon.ng@yale-nus.edu.sg

<sup>†</sup>robert.whitney@grenoble.cnrs.fr

<sup>§</sup>alexia.auffeves@cnrs.fr

Making quantum computers a concrete reality has a physical resource cost, especially when large-scale processors are targeted. In this spirit, the number of physical qubits required to implement large-scale computations has started to be investigated in various fault-tolerant schemes, including those that employ concatenated codes [23–25], surface codes [24–26], and bosonic qubits [27–29]. The total number of logical gates and qubits required by many algorithms have also been estimated, e.g., for decryption tasks [26,30–32] and material [33–37] or electromagnetic [38] simulations. These studies play an important role in identifying strategies for scaling up quantum processors.

The question of energy consumption was mentioned in the seminal experimental demonstration reported in Ref. [19]: a 5-orders-of-magnitude difference was announced between the power consumption of the quantum processor and that of the classical supercomputer performing the same task. However, the study was on a 50qubit quantum processor and at the present time it remains unclear how the energy consumption of future quantum processors will scale. On the one hand, some studies anticipate energy savings, due to the complexity gains provided by quantum logic, see, e.g., Ref. [39]. They rely on subtle algorithmic details but then assume very simple models for the hardware. On the other hand, studies based on precise hardware details (but agnostic on algorithmic details) [40,41] usually conclude that the overheads needed to control the physical qubits could be so large that they will be to be an issue for scalability [40,42–48], especially in achieving large-scale fault-tolerant quantum computers. This lack of consensus reveals the need for a holistic methodology coupling data from the hardware and the algorithmic frameworks.

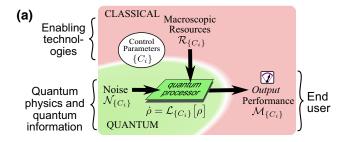

Setting up a holistic methodology is highly challenging, as it requires modeling the full stack of the quantum computer [42,44,45,48-52], and coordinating inputs from currently separated areas of expertise, as sketched in Fig. 1. Improving computational performance requires programming the processor to implement a given algorithm and to reach a satisfactory level of control over noise while the algorithm is being executed. These optimizations are performed at the quantum level and rely on detailed knowledge of quantum hardware and software, e.g., quantum control, noise modeling, environmental engineering, quantum error correction, quantum algorithms, qubit fabrication, etc. However, achieving that in a physical device requires the use of macroscopic resources provided by enabling technologies at the classical level (e.g., cryogenic systems [40,41], classical computers for control [43,53– 57], lasers, detectors [58,59], amplifiers [60–62], etc.). Hence, understanding and managing the resource bill of future quantum processors cannot be restricted to the quantum level, as it provides no access to the macroscopic costs. Reciprocally, a solely macroscopic approach is blind to the computing performance—we do not know what we are

FIG. 1. (a) A schematic of our metric noise resource (MNR) methodology, which models the battle of control against noise. The control parameters affect the performance metric, the noise, and the resource consumption. Such parameters include the qubit temperature, the amount of error correction, etc. The performance metric can be improved by using resources to reduce the noise (e.g., cooling the qubits) or spending resources to make the metric less sensitive to existing noise (e.g., better error correction). (b) A simplified sketch of the physical elements in a typical full-stack superconducting quantum computer, with qubits at temperature  $T_{qb}$  and classical control electronics at temperature  $T_{\rm gen}$ . The classical computer, at room temperature, compiles the user-specified algorithm and code into a sequence of physical gate operations, interprets detected errors in real time, and can modify the gate sequence to correct them. The black arrows indicate information flows. The red arrows indicate heat flows that bring noise that can cause gate errors (heat conducted by wiring, heat generated by attenuators and amplifiers, etc.); more details are shown in Fig. 9. We model the full stack by considering each physical element in (b) in terms of its effect on the metric, noise, and resource in (a).

paying for. Resource-cost assessments and optimizations must be jointly conducted by an interdisciplinary combination of expertise. In the energetic context, this has been dubbed the Quantum Energy Initiative [63].

In this paper, we present a methodology that allows us to optimize the resource cost for the full stack of a quantum computer, under the constraint of a certain performance. Such an optimization under constraint is only possible if the methodology can treat all elements of the quantum computer in a single framework, including both the hardware (such as attenuators and cryogenics) and the quantum software (such as different quantum gates that implement the same quantum algorithm). We provide such a holistic methodology and show how it relates the microscopic description of the quantum computation to the macroscopic resources consumed by the cryogeny, wiring, classical control electronics, etc. We apply it to examples of quantum tasks with increasing complexity, from the operation of a single-qubit gate or a noisy circuit to a fault-tolerant algorithm. Each requires the specification of a relevant performance metric and a detailed description of the physical processes at play. In each example, we use our approach to show how resource costs scale with the size of the computational task. This reveals concrete instances of extreme sensitivity to both hardware characteristics (e.g., the qubit quality or the efficiency of the electronics) and software characteristics (the architecture of the circuits or the type of error-correcting code) and the necessity of treating both aspects in a coordinated manner.

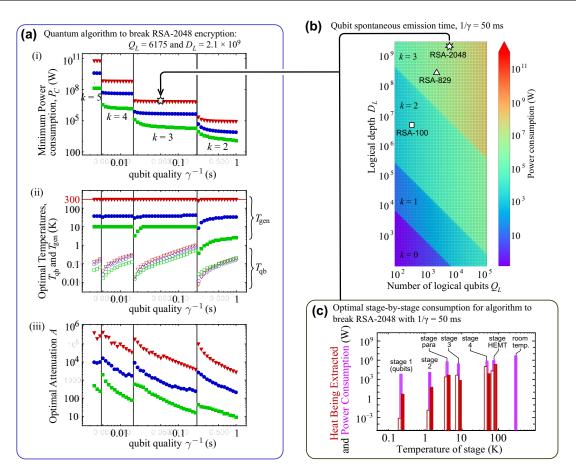

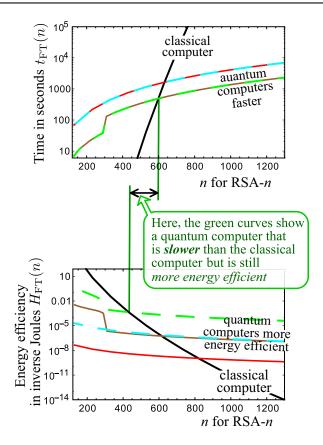

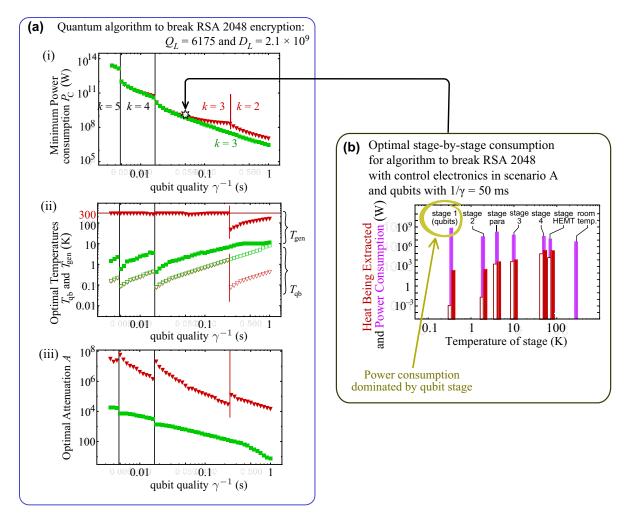

As an important outcome, we analyze quantum resource efficiencies as ratios between the computing performance metric and the resource cost. Different efficiencies can be defined, depending on the metric and the resource(s) of interest. Some permit the benchmarking of different qubit technologies or computing architectures. Others allow a comparison between quantum and classical processors and to define a quantum advantage from the resource perspective, which can further boost practical interest in quantum computers. Focusing on the example of Shor's algorithm to break Rivest-Shamir-Adleman (RSA) encryption, our calculations single out regimes of quantum energy advantage over classical supercomputers for problem sizes still accessible by such supercomputers, including in cases where the quantum computer takes more time to do the job than the supercomputer. These results show that the energy advantage is reached in different regimes than the computational advantage, providing a new and so far overlooked potential practical reason to build quantum computers.

Throughout this paper, we take parameters inspired by the superconducting platform and existing technologies for the control electronics, wiring, and cryogeny. However, our approach is generic and versatile, capable of providing general forms of behavior and typical orders of magnitude for a wide variety of settings. In particular, it shows how diverse the parameters that can affect power consumption are, with a crucial one being qubit quality. It also singles out surprising effects: while it is often optimal to make the qubits cold enough to minimize error correction, our approach shows that there are regimes where the opposite is true, regimes where it is more energy efficient to have warmer qubits with more error correction.

For illustrative simplicity, we base our examples on the concatenated seven-qubit code, which is well documented and allows for straightforward analytical expressions but can be demanding in terms of physical quantum resources. This choice leads us to use parameter values that are sometimes beyond the current state of the art. Nevertheless, we invite the reader to appreciate our results as proofs of concept of our methodology. It can provide on-demand practical guidelines to experimentalists and engineers looking to build resource-efficient quantum processors, allowing them to clearly identify the sequence of challenges to be met. Ultimately, systematic applications of the methodology can help avoid ecologically unacceptable outcomes, such as the current rapid increase in energy consumption of servers for consumer electronics [64] and artificial intelligence [65]. Thus, throughout the paper, we keep the methodology as apparent as possible, so as it can be applied to different qubit platforms and enabling technologies, as well as other error-correcting codes.

Our paper is organized as follows. We present our general optimization methodology in Sec. II, for any kind of resource and any kind of quantum computing platform. In Secs. III- V, we apply it to the special case of a superconducting quantum computer, focusing on energy and power, to illustrate the use of our methodology and of the kinds of conclusions one can draw from such an analysis. Section III describes a simple example for a noisy single-qubit gate, establishing the basic connection between microscopic qubit parameters and macroscopic power consumption. Section IV focuses on a noisy circuit, revealing the close interplay between inputs from the software and the physics of the hardware. Sections III and IV are largely pedagogical in their aims, to shed light on how the performance defined at the quantum level can impact the resource consumption at the macroscopic level. Section V considers a full fault-tolerant quantum computer, using concatenated codes for error correction and performing a calculation of difficulty similar to breaking the well-known RSA encryption. Estimates for faulttolerant quantum computing based on the currently popular surface codes are given at the end of Sec. V. We summarize our findings in Sec. VI.

#### II. METRIC NOISE RESOURCE METHODOLOGY

A quantum computer is a programmable machine; its job is to perform a well-defined sequence of operations on an ensemble of qubits. After the circuit is programmed, the qubits are prepared in a reference state, unitary operations implementing a computational task are then applied, and the qubits are finally measured to extract the result of the calculation. Quantum noise perturbs this sequence, giving rise to errors that decrease the computing performance. This has to be countered by an increase in noise-mitigation measures, in an attempt to reduce the occurrence of errors and to remove their effects on the computation. Such increased noise mitigation is usually associated with increased resource costs. In some cases,

the increased resource cost can itself result in more noise. For instance, more error correction requires more physical qubits and that can result in additional sources of crosstalk, increasing the noise affecting the quantum processor [66]. Hence, finding the minimal resource cost to reach a target performance requires one to explore nontrivial sweet spots. Such an investigation involves coordinated inputs from the software and hardware, at the quantum and classical levels of description. Here, we present a holistic methodology to treat the whole range of inputs. For reasons that become clear below, we have dubbed it the metric noise resource (MNR) methodology, or more simply MNR [67].

The basics of MNR are sketched in Fig. 1(a). The first step consists of identifying the set of parameters—dubbed "control parameters,"  $C_i$ s—that allows us to execute a quantum algorithm with a given target performance. It is with respect to these parameters that the resource cost will be minimized. The control parameters can be of various kinds. Some characterize the quantum processor or the hardware controlling it. Typical examples include the temperature of the qubits or the strength of the attenuators on the control lines. Some are of software nature, reflecting the fact that the same algorithm can be executed by different circuits. Examples include the degree of compression of the circuit or any other quantity capturing the circuit architecture. A crucial control parameter is the size of the quantum error-correcting code, i.e., the number of physical qubits per logical qubit in a fault-tolerant quantum computation.

Once this identification has been done, we can turn to the first element of MNR: the performance metric  $\mathcal{M}$  (later dubbed "metric," for brevity). It is a number measuring the quality of the computation, for which a larger number means a better computation. Naturally, there is some flexibility in the choice of the metric. Some are defined at a low level, focusing on the precision with which states can be generated by executing the programmed sequence of gates. A natural example is the fidelity, which quantifies the distance between the ideal and the real processor states before the extraction of the result. Other metrics are user oriented, such as the Q score [68] or the quantum volume [69], which estimates the maximal size of the problems that can be solved on a quantum computing platform. Some useroriented metrics aim to benchmark classical and quantum processors and to identify quantum computational advantages. Whatever the chosen metric, it depends directly on the level of control over physical processes in the quantum computer.

This brings us naturally to the second element of MNR: the noise in the physical processes. It is taken into account by modeling the dynamics of the noisy quantum processor executing the algorithm. This involves a given time-dependent Hamiltonian, together with a noise model, in the form of a master equation the expression of which depends on the control parameters. Many parameters can enter this

noise model, such as the temperature of the qubits and the temperature of the external control electronics. The time-dependent Hamiltonian corresponds to the sequence of gates applied to the qubits, which is set by the circuit architecture. Hence, such a model allows us to derive a quantitative expression for the metric, as a function of the  $C_i$ s.

The third ingredient of MNR is the resource  $\mathcal{R}$  of interest that we wish to minimize. Formally, a resource can be any cost function that depends on the set of control parameters. While MNR is general and could tackle economic costs, here we shall focus on physical resource costs. They can be extremely diverse in nature, e.g., the physical volume occupied by the quantum processor, the total frequency bandwidth allocated to the qubits, the duration of the algorithm, the amount of classical information processed to perform error correction, or the energy consumption. In this paper, we will address the last of these, by considering the electrical power consumed while a quantum computation is being performed.

Once these steps are completed, MNR basically reduces to a constrained optimization. Fixing a target metric  $\mathcal{M}_0$  boils down to setting a tolerable level of control over noise for a properly programmed processor: it provides a first constraint that the control parameters have to satisfy. The resource cost  $\mathcal{R}$  is then minimized as a function of the control parameters under this implicit constraint. An optimal set of control parameters gives the minimal resource consumption  $\mathcal{R}^{\min}(\mathcal{M}_0)$  needed to reach the metric  $\mathcal{M}_0$  [70]. For instance, if the qubit temperature is a control parameter, MNR provides an optimal working temperature for the qubits to reach a target metric  $\mathcal{M}_0$  with a minimal resource cost and can lead to nontrivial values as shown below. It thus provides practical inputs to designing resource-efficient quantum computations.

MNR relates a metric to its macroscopic resource cost. This makes it drastically different from the common point of view to date, which has been to target the largest metrics, whatever the resource cost. It has been inspired by our earlier work [66], which pointed out that a constraint on resources has a profound effect on fault-tolerant quantum computing. However unlike here, that work only considered quantum-level resources.

#### A. Resource efficiencies

In general, efficiencies characterize the balance between a performance and the resource consumed in achieving it. MNR provides systematic relations between performance and resource costs. Hence, it naturally leads one to define and optimize resource efficiencies for quantum computing. For classical supercomputers, the target performance is computing power, expressed in floating-point operations per second (FLOPS). The energy efficiency is built as the ratio of the computing power to the power consumption

(the resource) of the processor. It is measured in FLOPS/W, has the dimension of the inverse of an energy, and gives rise to the Green500 ranking of the most energy-efficient supercomputers [71]. In this paper, we shall explore quantum equivalents of this energy efficiency. Within the MNR methodology, the resource efficiency is generically defined as  $\eta = \mathcal{M}/\mathcal{R}$ , where  $\mathcal{M}$  is the metric and  $\mathcal{R}$  the resource cost. As mentioned above, two kinds of metrics can be considered: low-level metrics and user-oriented metrics. The resource cost can be defined at the quantum level or at the macroscopic level, giving rise to bare and dressed efficiencies, respectively. The quantum level is crucial for understanding the physics of qubits, while the macroscopic level will be what matters for large-scale applications.

Sections III and IV, respectively, involve noisy gates and circuits. A low-level metric, the fidelity, is natural in both cases. Modeling the processor at the quantum level provides an implicit relation between the noise, the control, and the chosen metric. Applying the MNR methodology to minimize the power consumption  $\mathcal{R}^{\min}(\mathcal{M}_0)$  for the target metric  $\mathcal{M}_0$  unambiguously sets the maximal efficiency of the task at the target  $\mathcal{M}_0$ . Such an efficiency is well suited for benchmarking different technologies of qubits or different computing architectures implementing the same algorithm, i.e., to compare different quantum computing platforms.

Sections IV and V involve algorithms. We thus introduce user-oriented metrics there to explore another kind of resource efficiency. As a typical example, in Sec. V we consider the breaking of RSA encryption. There the relevant metric is the maximal key size that can be broken with a well-defined probability of success. We estimate the energy consumed by full-stack quantum and classical processors as a function of this size. Beyond a typical size, we show that quantum processors are more energy-efficient than classical ones, highlighting a new and essential practical advantage of quantum computing.

#### III. NOISY SINGLE-QUBIT GATE

We start by applying the MNR methodology to the simplest component of a quantum computer: a resonant noisy single-qubit gate. This allows us to introduce the generic type of qubits we will be working with throughout the paper, which take values inspired by the superconducting platform [15,62,72]. We only consider errors due to spontaneous emission and thermal noise, both of which are unavoidable as soon as the qubit is driven by control lines bringing pulses from the signal-generation stage to the processor (see below). All other sources of noise are neglected.

#### A. Quantum level

Let us first focus on the characteristics of the gate at the quantum level. The ground and first excited states of the

superconducting qubit are denoted by  $|0\rangle$  and  $|1\rangle$ , respectively, with a transition frequency set to  $\omega_0 = 2\pi \times 6$  GHz. The gate is implemented by driving the qubit with resonant microwave pulses at a frequency  $\omega_0$  and an amplitude that induces a classical Rabi frequency  $\Omega$ . We consider square pulses of duration  $\tau_{1qb}$ , giving rise to the qubit Hamiltonian  $H = -\frac{1}{2}\hbar\omega_0\sigma_z + \frac{1}{2}\hbar\Omega(e^{i\omega t/2}\sigma_- + e^{-i\omega t/2}\sigma_+)$ , with  $\sigma_{\pm} \equiv \frac{1}{2}(\sigma_x \mp i\sigma_y)$ . For model simplicity, all single-qubit gates are taken as X gates, i.e., each gate is a  $\pi$  pulse of duration  $\tau_{1qb} = \pi/\Omega$ . For driving pulses propagating in control lines,  $\Omega$  and the spontaneous emission rate  $\gamma$  are not independent, with  $\Omega = \sqrt{(4\gamma)/(\hbar\omega_0)}\sqrt{P}$ , where P is the average power of the microwave pulse [66,73]. In the present section, dedicated to study at the quantum level, the gate duration  $\tau_{1qb}$  is taken as the control parameter. The resource cost is defined as the power  $P_{\pi}$  consumed to bring the qubit from  $|0\rangle$  to  $|1\rangle$ :

$$P_{\pi} = \frac{\hbar\omega_0\pi^2}{4\gamma\tau_{\text{lab}}^2}.\tag{1}$$

The spontaneous emission rate  $\gamma$  is set by the specific qubit technology; we use  $\gamma^{-1} = 1$  ms in Sec. III and  $\gamma^{-1} = 10$  ms in Sec. IV. The action of the noise alone is described by a map  $\mathcal{N}$ , obtained by integrating the Lindblad equation over a time interval  $\tau_{1ab}$ ,

$$\frac{d\rho}{dt} = \gamma n_{\text{noise}} \mathcal{L}[\sigma_{-}^{\dagger}](\rho) + \gamma (n_{\text{noise}} + 1) \mathcal{L}[\sigma_{-}](\rho), \quad (2)$$

where  $\mathcal{L}[A](\cdot) \equiv A \cdot A^{\dagger} - \frac{1}{2} \{A^{\dagger}A, \cdot\}, \{\cdot, \cdot\}$  is the anticommutator, and  $n_{\text{noise}}$  denotes the number of thermal photons. We assume this same noise map  $\mathcal{N}$  for every single-qubit gate and write  $\mathcal{G} = G\mathcal{N}$ , where  $\mathcal{G}$  and G are the maps for the noisy and ideal gates, respectively.

We define our "low-level" metric to quantify the performance of the noisy single-qubit gate as the worst-case gate fidelity,

$$\mathcal{M}_{1qb} \equiv \min_{\rho} \mathcal{F}_{\mathcal{G}}(\rho),$$

(3)

where  $\mathcal{F}_{\mathcal{G}}(\rho)$  is the (square of the) fidelity between the output of the ideal gate and the output of the noisy gate. Then,  $\mathcal{F}_{\mathcal{G}}(\rho) \equiv \left[ \mathrm{Tr} \sqrt{(G \rho \, G^\dagger)^{1/2} \mathcal{G}(\rho) (G \rho \, G^\dagger)^{1/2}} \right]^2.$  The concavity of the fidelity ensures that the worst-case fidelity is attained on a pure state. The minimization in Eq. (3) can thus be restricted to over pure states only and  $\mathcal{F}_{\mathcal{G}}(\rho)$  simplifies to  $\langle \psi | G^\dagger \mathcal{G}(\psi) G | \psi \rangle = \langle \psi | \mathcal{N}(\psi) | \psi \rangle$  for  $\rho \equiv |\psi\rangle\langle\psi| \equiv \psi$ . It is useful to rewrite the metric as  $\mathcal{M}_{1qb} \equiv 1 - \mathrm{IF}_{1qb}$ , where  $\mathrm{IF}_{1qb}$  is now the worst-case (i.e., the maximum) gate in fidelity. Straightforward algebra yields an expression for  $\mathrm{IF}_{1qb}$  in terms of the gate and noise

parameters:

$$IF_{1qb} = \gamma \tau_{1qb} \left( 1 + n_{\text{noise}} \right). \tag{4}$$

IF<sub>1qb</sub> scales like  $\gamma \tau_{1qb}$ , the number of spontaneous events during the gate, and increases with the number of thermal photons  $n_{\text{noise}}$ . Equation (4) provides us with an implicit relation between the noise ( $\gamma$  and  $n_{\text{noise}}$ ), the control ( $\tau_{1qb}$ ), and the metric ( $\mathcal{M}_{1qb} = 1 - \text{IF}_{1qb}$ ). The metric can be increased by reducing the time to perform the gate operation,  $\tau_{1qb}$ . However, Eq. (1) tells us that this comes at the cost of increased power consumption.

#### 1. Bare efficiency

We now define the bare efficiency  $\eta_0$ , with "bare" meaning that the resource cost  $P_{\pi}$  is defined at the quantum level:

$$\eta_0 = \frac{\mathcal{M}_{1_{qb}}}{P_{\pi}}.\tag{5}$$

In the MNR methodology, we impose the metric to be equal to a given target value,  $\mathcal{M}_{1qb} = \mathcal{M}_0$ . Let us consider the case where the thermal noise is negligible compared to spontaneous decay, i.e.,  $n_{\text{noise}} \ll 1$ , yielding  $\mathcal{M}_0 = \mathcal{M}_{1qb} = 1 - \gamma \tau_{1qb}$ . Now, we wish to minimize the resource cost  $P_{\pi}$  for the desired  $\mathcal{M}_0$ . Such minimization is performed as a function of the control parameter  $\tau_{1qb}$  and gives rise to the maximal efficiency  $\eta_0^{\text{max}}$ . From Eqs. (1) and (4), we can see that  $\tau_{1qb}$  affects both the resource and the metric. This allows us to write  $\eta_0^{\text{max}}$  solely as a function of the target metric,

$$\eta_0^{\text{max}}(\mathcal{M}_0) = \frac{\mathcal{M}_0}{P_{\pi}^{\text{min}}(\mathcal{M}_0)} = \frac{4}{\pi^2} \frac{\mathcal{M}_0 (1 - \mathcal{M}_0)^2}{\gamma \hbar \omega_0}.$$

(6)

Equation (6) tells us that the bigger the target performance metric, the smaller is the efficiency. In other words, increasing the target by one digit (e.g., to take  $\mathcal{M}_0$  from 0.9 to 0.99) costs more and more power—we will see this general trend in all our examples below. It also reveals the natural unit of power to be  $\gamma \hbar \omega_0$ , which is the power dissipated into the environment through spontaneous decay events. The larger the noise rate  $\gamma$ , the larger is the power dissipated, as the gate has to be performed more quickly to maintain the equality  $\mathcal{M}_{1_{qb}} = \mathcal{M}_0$ . Hence,  $P_{\pi}^{\min}(\mathcal{M}_0)$  increases [74], decreasing the efficiency. Hence, at the level of single gates, good qubits characterized by small  $\gamma$  are typically more energy efficient than bad ones. This observation will carry through to the macroscopic level in all examples in this work.

#### B. Macroscopic level

We now model the macroscopic chain of control to take its resource cost into account. Note that from now

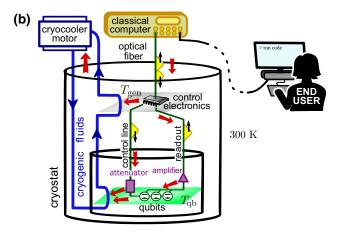

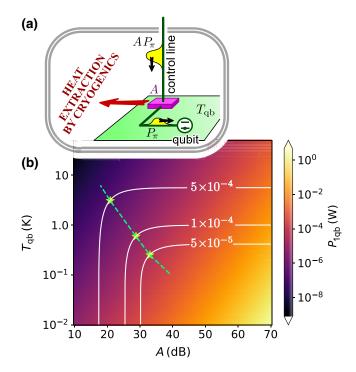

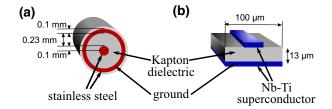

FIG. 2. (a) A sketch of our simplified model of a single qubit in a cryostat. (b) The color scale is the power consumption (in watts) of a single-qubit gate as a function of the qubit temperature  $T_{\rm qb}$  and attenuation A. The parameter values are  $\gamma^{-1}=1$  ms and  $\tau_{\rm 1qb}=25$  ns. Each contour is associated with the target metric (worst-case infidelity) indicated in white. The green stars mark the optimal parameters (those that minimize the power consumption) for each value of the target metric.

on, only such macroscopic resource costs will be considered, for which "dressed" efficiencies are appropriate. Here, we present the basic approach within a simplified model, which will be made more realistic in Sec. V. This simple example is limited to a control line funneling driving pulses from outside the cryostat onto the qubit through a single attenuator, with the cryogenics evacuating the heat dissipated by that attenuator. The implementation of the gate is depicted in Fig. 2(a). The qubit is put in a cryostat and cooled down to the temperature  $T_{\rm qb}$  (typically below a kelvin). The driving signal is generated at room temperature  $T_{\rm ext}$  and sent into the cryostat through a control line. Alongside the signal, the line also brings in unwanted room-temperature thermal noise, which is unavoidable whenever we require external control.

To mitigate the noise, the signal is first generated with a high amplitude for a strong signal-to-noise ratio. An attenuator is then placed on the line [75] (at the qubit level at temperature  $T_{\rm qb}$ ), which lowers the input pulse power by an amount A. Thus A and  $T_{\rm qb}$  are the two control parameters optimized in the present section. For simplicity, we fix the gate duration to be  $\tau_{\rm 1qb} = 25$  ns [15,62,72], chosen to avoid leakage errors [76] that are not modeled here. The two control parameters, A and  $T_{\rm qb}$ , impact the gate noise in

the following manner (see, e.g., Eq. (10.13) in Ref. [77]):

$$n_{\text{noise}} = \frac{A-1}{A} n_{\text{BE}}(T_{\text{qb}}) + \frac{1}{A} n_{\text{BE}}(T_{\text{ext}}), \tag{7}$$

where  $n_{\rm BE}(T)=1/[e^{\hbar\omega_0/(k_{\rm B}T)}-1]$  is the Bose-Einstein photon distribution at temperature T. Here, A is expressed in natural units:  $A=10^{A_{\rm dB}/10}$ , where  $A_{\rm dB}$  is the attenuation expressed in decibels [78]. The noise model is now entirely defined by Eqs. (2) and (7). Keeping the fidelity in Eq. (3) as the metric, increasing it boils down to increasing the level of attenuation A or decreasing the qubit temperature  $T_{\rm qb}$ .

We finally define the macroscopic resource of interest. To get a signal of power  $P_{\pi}$  on the qubit, a power  $AP_{\pi}$  is injected into the cryostat, giving  $\dot{Q} \approx AP_{\pi}$  as the rate of heat generation from the attenuator at  $T_{\rm qb}$  [79]. We assume Carnot-efficient heat extraction, as it already gives the right order of magnitude for large-scale cooling to cryogenic temperatures that can be done at 10–30% of Carnot efficiency, such as the cooling capabilities at CERN [80]. Then, the cryogenic electrical power consumption (dubbed the "cryo-power" below) needed to run the gate is

$$P_{1\text{qb}}(T_{\text{qb}}, A) = \frac{T_{\text{ext}} - T_{\text{qb}}}{T_{\text{qb}}} A P_{\pi}. \tag{8}$$

This is the resource that we consider in the present section. Putting together Eqs. (4)–(8), we can see that increasing the metric by reducing  $T_{\rm qb}$  or increasing A (taking  $A\gg 1$  as in typical experiments) increases the resource cost  $P_{1{\rm qb}}(T_{\rm qb},A)$ . This behavior is apparent in Fig. 2(b), where the cryo-power is plotted as a function of A and  $T_{\rm qb}$ . If we target a specific value  $\mathcal{M}_0$  for the metric, i.e., we require  $\mathcal{M}_{1{\rm qb}}=\mathcal{M}_0$ , this sets an implicit relation between A and  $T_{\rm qb}$ , giving rise to the contours marked in the figure.

In the MNR methodology,  $\mathcal{M}_{1qb} = \mathcal{M}_0$  is the constraint under which  $P_{1qb}(T_{qb}, A)$  is minimized. Using Eqs. (4) and (7), this constraint can be explicitly written as

$$1 - \gamma \tau_{1qb} \left( 1 + \frac{A - 1}{A} n_{BE}(T_{qb}) + \frac{1}{A} n_{BE}(T_{ext}) \right) = \mathcal{M}_0.$$

(9)

In Fig. 2(b), this is indicated by the white contours, while the points with minimum power consumption are marked with green stars. This provides our first example of a nontrivial sweet spot, where the metric defined at the quantum level impacts the macroscopic resource cost, and is an explicit illustration of the necessity of coordinating inputs from both levels of description.

#### 1. Dressed efficiency

We now minimize the cryogenic power consumption as a function of the two control parameters A and  $T_{qb}$ , under

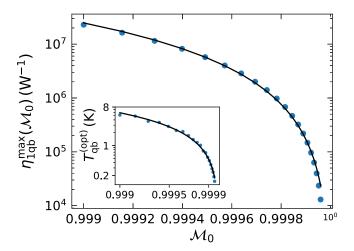

FIG. 3. The maximal dressed efficiency  $\eta_{1qb}^{max}(\mathcal{M}_0)$  (in  $W^{-1}$ ) for a single-qubit gate, as defined in Eq. (10). The inset shows the optimal qubit temperature as a function of the target metric  $\mathcal{M}_0$ . Here,  $\gamma^{-1}=1$  ms.

the constraint  $\mathcal{M}_{1_{qb}} = \mathcal{M}_0$ . We denote this minimum by  $P_{1qb}^{\min}(\mathcal{M}_0)$ . This defines the maximal dressed efficiency of the single-qubit gate:

$$\eta_{1qb}^{\max}(\mathcal{M}_0) = \frac{\mathcal{M}_0}{P_{1qb}^{\min}(\mathcal{M}_0)}.$$

(10)

$\eta_{1qb}^{max}$  is plotted in Fig. 3 as a function of  $\mathcal{M}_0,$  revealing the same behavior as  $\eta_0^{\text{max}}$ : the larger the target metric, the smaller is the efficiency. The inset gives the qubit temperature that achieves the minimal power consumption, as a function of  $\mathcal{M}_0$ . The maximal dressed efficiency is much lower than the maximal bare efficiency  $\eta_0^{\text{max}}$ , with a typical reduction by 3 orders of magnitude. For example,  $\eta_{1qb}^{max}(0.99965) = 3 \times 10^6 \text{ W}^{-1}$ , while  $n_0^{\text{max}}(0.99965) \sim 10^{10} \ W^{-1}$ . While these two examples are not strictly comparable (the gate duration was optimized for the microscopic efficiency but fixed at  $\tau_{1ab} = 25$  ns for the macroscopic case), the main difference is that the cryogenic power consumption is larger than the microscopic power  $P_{\pi}$  by a magnification factor of  $AT_{\rm ext}/T_{\rm qb}$ , which can be very large (approximately  $2 \times 10^4$  for  $\mathcal{M}_{1qb} =$ 0.99965). This illustrates the reduction of efficiency when going from the microscopic to the macroscopic level.

#### IV. EXAMPLE OF NOISY COMPUTATION

Noisy computations are currently considered in the search for use cases with a quantum computational advantage in the noisy intermediate-scale quantum (NISQ) [81] setting, as opposed to fault-tolerant quantum computing (FTQC), which we discuss in Sec. V.

Here, we consider a simplified model of noisy computation (chosen for pedagogy rather than realism), performed with the simplified qubit model from Sec. III. We use this simplified model to introduce how details of the algorithmic implementation enter MNR as control parameters that can be adjusted to minimize the resource consumption.

Readers who want a more realistic indication of the minimal power consumption of a noise computation should look at the corner of Fig. 10(b) marked k=0 (recalling that k=0 means that there is no error correction). It is based on our complete full-stack model in Sec. V, rather than the simplified model presented here. Although its assumptions are for large-scale fault-tolerant calculations not NISQ ones (it assumes large-scale cryogenics and certain approximations mentioned in Ref. [82]), we expect its conclusion of a few milliwatts per physical qubit to be reasonable for an optimistic estimate of the NISQ regime.

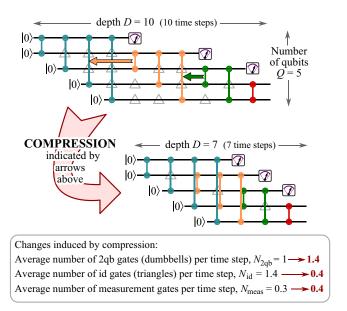

To understand how the algorithm is taken into account by MNR, it is important to note that the same algorithm can be implemented using different circuits. Here, the algorithm refers to the overall operation that we want to perform on the qubits, while a circuit is an instruction set specifying the sequence of gates on the qubits to carry out the algorithm. In the MNR methodology, the architecture of the circuit can be viewed as a control parameter for the algorithmic task. Our simple example here is the algorithm implemented by the circuit in Fig. 4, which bears structural similarities with a quantum Fourier-transform circuit [83]. It comprises sequences of two-qubit (2qb) gates grouped into subcircuits, marked with different colors in Fig. 4). For Q qubits, this circuit has Q-1 subcircuits and  $\frac{1}{2}Q(Q-1)$ 2qb gates. It can be "compressed" by having the subcircuits overlap, noting that there are idling qubits within each subcircuit [84]. We define a compression parameter  $\epsilon$ , set to be zero for the scenario in which all subcircuits are performed in sequence with no overlap (the top circuit of Fig. 4). We can then make a succession of compression where some subcircuits are partially performed in parallel with their preceding subcircuits. The maximum compression occurs when (Q-3)/(Q-1) subcircuits are partially parallelized in this manner (the bottom circuit of Fig. 4).

In this section, the compression  $\epsilon$  plays the role of a control parameter of software nature. This comes in addition to the hardware parameters used for the single-qubit gate, namely, the processor temperature  $T_{\rm qb}$  and the control-line attenuation A (here taken to be identical for all lines). We will thus minimize the resource cost as a function of the triplet  $(T_{\rm qb}, A, \epsilon)$ .

#### A. Noise model and low-level metric

In this section, we consider circuits built from a typical minimal gate set consisting of identity (id), single-qubit (1qb), and two-qubit (2qb) gates acting on Q qubits. We assume that the 2qb gates are implemented with a cross-resonance scheme [85,86] in which the two qubits interact

FIG. 4. A hypothetical circuit made of two-qubit (2qb) gates, each indicated by a colored dumbbell. Each qubit has a 2qb gate with each of the qubits below it. Thus, if the circuit has Q qubits, then it contains  $\frac{1}{2}Q(Q-1)$  2qb gates. In the upper circuit, no two 2qb gates are performed in parallel, so its depth is  $D=\frac{1}{2}Q(Q-1)$  and there are many time steps in which qubits are simply storing information for a later time step. These are indicated by gray triangles, corresponding to noisy identity (id) gates. One can "compress" the circuit step by step, by moving 2qb gates in the direction of the arrows shown on the upper circuit. This increases the average number of 2qb gates per time step, reducing the number of id gates and thereby reducing D. The lower circuit is the fully compressed version of the upper circuit.

by sending a microwave signal to one qubit at the frequency of the other qubit. Such 2qb gates rely on resonant excitations similar to those employed in the 1qb gates. We thus assume the 1qb and 2qb gates to have similar costs and take that cost to be  $P_{\pi}$  of Eq. (1). The 2qb gates are, however, slower than the 1qb gates and we set  $\tau_{2qb} = 100$  ns [85,86]. Finally, the quantum computer runs at a clock frequency determined by its slowest gate. We thus set the clock period, or the time step for gate applications, to be  $\tau_{\text{step}} = \tau_{2qb} = 100$  ns.

We first establish the relation between the local noise afflicting individual gate operations and the global metric characterizing the overall circuit performance.

We follow Sec. III in assuming that the only noise felt by the qubits is the unavoidable noise coming from the control lines. This is modeled as simple probabilistic noise in which each qubit has a probability of having an error during one time step equal to the worst-case infidelity IF<sub>1qb</sub> of the process at each time step, determined from Eq. (2). Here, IF<sub>1qb</sub> is defined as in Eq. (4) but  $\tau_{1qb}$  is replaced by  $\tau_{step} = 100ns$ . Then, a two-qubit gate has twice the infidelity of a single-qubit gate, because two qubits participate

in a two-qubit gate. So each id gate and each 2qb gate, respectively, have probabilities equal to  $IF_{1qb}$  and  $2IF_{1qb}$  of generating an error in the computation.

To quantify the algorithmic performance, we choose a low-level metric,  $\mathcal{M}_{\text{algo}} = 1 - P_{\epsilon}^{\text{error}}$ , where  $P_{\epsilon}^{\text{error}}$  is the probability that at least one error has occurred within the circuit with compression  $\epsilon$ . For the algorithm to have a reasonable chance of success, IF<sub>1qb</sub> should be small. Because of that, the error probability of the circuit can be approximated by  $P_{\epsilon}^{\text{error}} = \mathcal{N}_g(\epsilon)$ IF<sub>1qb</sub>, where  $\mathcal{N}_g(\epsilon) \equiv \left(\mathcal{N}_{\text{id}}(\epsilon) + \mathcal{N}_{\text{1qb}}(\epsilon) + 2\mathcal{N}_{\text{2qb}}(\epsilon)\right)$ . Here,  $\mathcal{N}_i(\epsilon)$  is the total number of gates of type i in the circuit with compression  $\epsilon$ . From this, we deduce that

$$\mathcal{M}_{\text{algo}}(\epsilon, A, T_{\text{qb}}) = 1 - \mathcal{N}_{g}(\epsilon) \operatorname{IF}_{1\text{qb}}(A, T_{\text{qb}}).$$

(11)

Equation (11) makes explicit the influence of control parameters of software ( $\epsilon$ ) and hardware (A,  $T_{\rm qb}$ ) natures on the global performance of the algorithm.

#### **B.** Resource cost

Whenever the calculation time is a parameter (as it is when we introduce the circuit compression shown in Fig. 4), minimizing the average power consumption during the calculation is *not* the same as minimizing the energy cost of the calculation (since that energy cost is the average power times the calculation time). So should we minimize the power or the energy?

We argue that the power consumption should be minimized whenever that power consumption is large enough to be the principal engineering challenge. For example, there are many engineering reasons why it is much harder to consume 1 GW for 1 min, rather than 250 kW for 3 days, even though the two have similar total energy costs. Our main full-stack calculation, in Sec. V, is in the regime in which the power consumption is so high that it will be a huge engineering challenge. Thus it is critical to minimize this power. Hence, for simplicity, we also minimize the power consumption for the pedagogical examples in the work, including for the simplified model of a NISQ calculation considered in this section.

In many cases, we believe that both minimizations will give similar results. Minimizing the energy cost will tend to promote shorter calculation times than minimizing the power consumption alone (since it corresponds to minimizing the power times the calculation time). However, we observe that minimizing the power consumption already tends to favor solutions with fairly short calculation times (see, e.g., Sec. VE4). So the parameters that minimize the power consumption may not be far from those that minimize the energy cost.

We take the resource cost to be the total cryo-power averaged over a specified circuit that implements the algorithm. This is given by

$$P_{\epsilon}(A, T_{qb}) = P_{1qb}(A, T_{qb}) N_{1qb,\epsilon} + P_{2qb}(A, T_{qb}) N_{2qb,\epsilon}.$$

(12)

Here, the cryo-powers supplied to perform a 1qb and 2qb gate are  $P_{1\text{qb}}(A,T_{\text{qb}})$  and  $P_{2\text{qb}}(A,T_{\text{qb}})$ , respectively, and it is assumed that id gates require no power.  $N_{1\text{qb},\epsilon}$  and  $N_{2\text{qb},\epsilon}$  are the average number of 1qb and 2qb gates, respectively, run in parallel per time step of the circuit with compression  $\epsilon$ . Since we consider the power consumption during the execution of the algorithm, we shall only consider one run. The energy considerations of specific NISQ algorithms such as the variational quantum eigensolver (VQE) or the quantum approximate optimization algorithm (QAOA) may require one to take into account the number of runs needed to reach a result with a certain accuracy.

In our plots—see Fig. 5 and onward—we have to choose certain parameters. There, we assume that each time step is 100 ns, where this is the time for a 2qb gate, whereas 1qb gates take only 25 ns. We assume that it takes about the same power to drive 1qb and 2qb gates, given by Eqs. (1) and (8). However, as a 1qb gate is completed in a quarter of a time step, its power consumption averaged over the time step is a quarter that in Eq. (8), so  $P_{1qb}(A, T_{qb}) = P_{2qb}(A, T_{qb})/4$ .

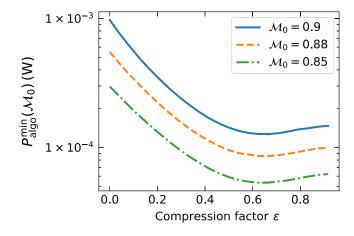

Equations (11) and (12) allow us to optimize the total cryo-power as a function of the three control parameters,  $(A, T_{\rm qb}, \epsilon)$ , under the constraint of a target metric  $\mathcal{M}_{\rm algo} = \mathcal{M}_0$ . To make the impact of the circuit compression obvious, we first minimize the cryo-power with respect to A and  $T_{\rm qb}$ , for various values of the compression  $\epsilon$ . We have performed this optimization for a circuit with Q = 25 qubits (see Fig. 5). The plot shows that the sweet spot of minimal power consumption occurs when the circuit is partially compressed, revealing a competition

FIG. 5. The minimum power as a function of the compression  $\epsilon$  of the circuit (see text). The circuit is a 25-qubit version of the one shown in Fig. 4. Here,  $\gamma^{-1} = 10$  ms.

between two mechanisms. On the one hand, compressed circuits correspond to a reduced total number of gates  $\mathcal{N}$  (including id gates), with a reduced risk of error according to Eq. (11), but to a larger number of gates run in parallel, leading to a larger power consumption. On the other hand, uncompressed circuits, with more idling qubits, increase the total error probability, which has to be compensated for by lowering the error rate per gate, which is achieved by lowering  $T_{\rm qb}$ , hence also increasing the cryo-power per gate (see Fig. 2). This demonstrates that resource optimizations require coordinated inputs from the hardware and the software.

Figure 5 illustrates that minimizing the average power consumption is not equivalent to minimizing the energy cost of the calculation. Multiplying this power by the calculation time (with its relation to the compression factor explained above), we see that one can obtain a lower total energy cost for a higher compression factor (shorter calculation time) than that which minimizes the power consumption. However, one also sees that the difference is not huge (less than a factor-of-2 difference in energy consumption for the simple model in Fig. 5), so a circuit optimized for minimum power consumption will not be far from one optimized for minimum energy consumption.

#### C. Resource efficiencies

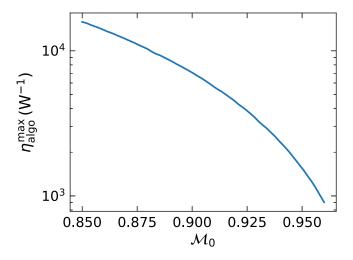

Resource efficiencies for quantum algorithms executed on noisy circuits can be defined in two ways, depending on the target performance. First, one may adopt a low-level metric, such as the fidelity used above. This invites us to define an efficiency  $\eta_{\rm algo} \equiv \mathcal{M}_{\rm algo}/P_{\epsilon}(A,T_{\rm qb})$  for a specified circuit implementation of the algorithm. For a given target metric  $\mathcal{M}_0$ , minimizing  $P_{\epsilon}(A,T_{\rm qb})$  as a function of A,  $T_{\rm qb}$  and the circuit compression  $\epsilon$  defines the maximal algorithmic efficiency  $\eta_{\rm algo}^{\rm max}(\mathcal{M}_0)$ . This is plotted in Fig. 6 as a function of  $\mathcal{M}_{\rm algo} \equiv \mathcal{M}_0$ , for circuits with Q=25 qubits. While it follows the same behavior as the single-qubit gate efficiency, a direct comparison is difficult, because of the complexity of the relationship between the fidelity of a single gate and the fidelity of a whole circuit.

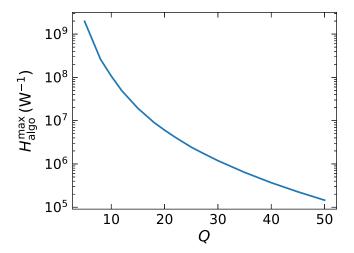

Second, the performance of an algorithm can be quantified by user-oriented metrics. A typical such metric is the size of the problem, which can be solved with a given probability of success. In this example, it can be measured by the size of the data register Q that carries out the algorithm, assuming that the algorithm is executed with a 2/3 success probability. The maximal user-oriented efficiency is given by  $H_{\text{algo}}^{\text{max}} = Q/P_{Q,\epsilon}^{\text{min}}(A, T_{\text{qb}})$ . Here, we have introduced  $P_{Q,\epsilon}^{\text{min}}(A, T_{\text{qb}})$ , the minimal cryo-power for a success probability of 2/3 for a circuit of size Q, optimized with respect to the compression  $\epsilon$ , attenuation A, and processor temperature  $T_{\text{qb}}$ . The maximal efficiency is plotted in Fig. 7 as a function of the target metric Q.

FIG. 6. The optimal efficiency  $\eta_{\rm algo}^{\rm max}(\mathcal{M}_0)$  as a function of the target algorithmic fidelity  $\mathcal{M}_0$ . The circuit is a 25-qubit version of the one shown in Fig. 4. Here,  $\gamma^{-1} = 10$  ms.

This section provides a pedagogical example to understand the impacts of the hardware and software choices on the energy consumption of a quantum computation. It also allows us to play with two different kinds of metrics and efficiencies, either low level or user oriented. To be truly informative, the user-oriented efficiency should be compared to a classical value quantifying the efficiency of a classical processor performing the same algorithm. A larger efficiency reached by the quantum processor provides a signature of a quantum energy advantage. This regime and the potential to reach it are studied in Sec. V, in the context of fault-tolerant computation.

FIG. 7. The optimal efficiency  $H_{\rm algo}^{\rm max}(Q)$  as a function of the target metric Q, the number of qubits needed for an algorithmic success probability of 2/3 (see text). Here,  $\gamma^{-1}=10$  ms.

#### V. FAULT-TOLERANT COMPUTATION

We now turn to the macroscopic power consumption and energy efficiency of fault-tolerant quantum computation, currently the only known route to useful large-scale quantum computers. Fault-tolerant quantum computation is built upon the technique of quantum error correction. The basic idea of quantum error correction is to distribute each qubit of information over many physical qubits, to form what is known as a logical qubit. This gives the logical qubit some resilience against noise that usually affects physical qubits individually. It requires, however, the use of several physical qubits to carry one logical qubit and the addition of regular error-correction operations, namely, syndrome measurements to diagnose what errors have occurred, and recovery gates to remove the effects of those errors on the logical qubit. This means a significant increase in the number of qubits, measurements, and gates, each of which has imperfections and can potentially add noise to the computer. Computing with such logical qubits is said to be done in a fault-tolerant manner if the error-correction operations, as well as the computational operations on the logical qubits (i.e., the logical gates), are designed so that the addition of so many more noisy physical components for the error correction still has the net effect of removing more errors than it introduces. This turns out to be possible only if the physical error rate is below some threshold level, often referred to as the fault-tolerance threshold.

From the user perspective, the fault-tolerant nature of the quantum computer is invisible. The user states the problem to be solved, and the algorithm to solve it, in terms of an ideal (noise-free) operation performed on a given input and specifies a target metric (e.g., the probability of success). This is then converted by the compiler to physical noisy qubits, gates, and measurements, using a prescribed fault-tolerant quantum computing scheme. The user-given input is represented by the logical qubits, encoded into the physical qubits carrying the information. The logical gates between those logical qubits that carry out the steps of the user-specified algorithm are converted into a sequence of physical gates between the physical qubits that make up each logical qubit.

For our simulation, we shall consider fault-tolerant quantum computing built from concatenating a seven-qubit code [83,87–90]. This is a very well-studied scheme and it has the advantage over more recent proposals (e.g., those based on topological codes) in that it has fairly complete and well-documented analyses, allowing us to be sure that we do not overlook any resource requirements. However, it is widely believed that fault-tolerant proposals based on surface codes require vastly less resources than the seven-qubit code. In Sec. V G, we extend our results to such surface codes, confirming this but pointing out open questions there that possibly make our estimates

unreliable. The advantage of our complete analysis of the seven-qubit code allows the reader to clearly see what questions they need to answer before doing similar estimates with their favorite fault-tolerant scheme.

#### A. MNR on a fault-tolerant algorithm

Before coming to the specifics of our model, we provide the reader with a general view on the approach that is valid for any quantum error-correcting code. We let  $p_{\rm err}$  denote the error probability of a physical qubit [91], which is provided by a microscopic model of the noise. If the error correction is successful, the error probability of a logical qubit is reduced to  $p_{\rm err,L} = f(k, p_{\rm err})$ , where f is a function and k quantifies the amount of error correction—the concatenation level in the case of our concatenated seven-qubit-code example. The price to pay for this reduction of errors is that the number of physical qubits per logical qubit grows with k; we denote this number by g(k).

Throughout this section, we consider a simple "rectangular" circuit, with the goal of preserving  $Q_L$  (logical) qubits of quantum information, for a total of  $D_L$  (logical) time steps. Such a rectangular circuit approximates well many fault-tolerant quantum algorithms based on  $Q_L$  qubits and having a circuit with depth  $D_L$  and still yields similar orders of magnitude for the power consumption and the metric (see Sec. V D). As  $(Q_L, D_L)$  is set by the choice of algorithm and circuit, k is the only software parameter that we are left with to perform our optimizations.

The metric  $\mathcal{M}_{FT}$  that we will consider is the probability of success of the rectangular circuit. Denoting the number of locations where logical errors can happen as  $\mathcal{N}_L = Q_L \times D_L$ , we find that

$$\mathcal{M}_{\text{FT}} = (1 - p_{\text{err:}L})^{\mathcal{N}_L}.$$

(13)

Targeting a total success probability of  $\mathcal{M}_{FT}=2/3$ , it translates into a maximal allowed value for  $p_{\text{err},L}$ . This maximal allowed value shrinks as the size  $\mathcal{N}_L$  of the circuit grows. Hence, performing bigger computations while maintaining the same target metric mandates more error correction and hence the consumption of more physical resources.

Estimating the physical resource cost requires the use of a full-stack model. Elaborations of the simple cases studied earlier to give a full-stack model that incorporates more experimental details are presented in Sec. V C, leading to a larger set of hardware control parameters. We also need to specify the physical circuit that carries out the quantum algorithm, which depends on the parameter k. Altogether, we can establish the generic expression of the full-stack power consumption  $P_{\rm FT}$ :

$$P_{\rm FT} = P_{1qb}N_{1qb} + P_{2qb}N_{2qb} + P_{\rm meas}N_{\rm meas} + P_{QQ}.$$

(14)

The first three terms capture the dynamical power consumption: they are nonzero only when a computation is running and involve active gates and measurements. Measurements must be modeled since syndrome measurements for error correction take place all along the fault-tolerant quantum computation. As in Eq. (12),  $N_{1qb}$  and  $N_{2qb}$  are the average numbers of physical 1qb gates and 2qb gates, respectively, performed in parallel, while  $N_{\text{meas}}$  is the average number of physical qubit measurements performed in parallel. These three quantities are determined solely by the software, i.e., the algorithm, the choice of errorcorrecting code, and the parameter k. Conversely,  $P_{1qb}$ ,  $P_{2qb}$  and  $P_{meas}$  are, respectively, the full-stack power consumption of 1qb gates, 2qb gates, and measurements, including all cryogenic and electronic costs; these depend solely on the hardware parameters. Finally, the fourth term in Eq. (14) captures the static power consumption, which we will take to be proportional to the number of physical qubits,  $Q = g(k) \times Q_L$ . Its expression depends both on software and hardware parameters.

The MNR methodology then simply consists of the following steps. (i) Consider an algorithm characterized by  $(Q_L, D_L)$  and a target probability of success equal to 2/3. As in Sec. IV, this 2/3 is a common choice for the success probability for a single run of an algorithm, with an exponential chance of yielding the correct answer with a constant number of reruns. Owing to Eq. (13), this sets an implicit relation between the hardware control parameters and k. (ii) Minimize the power consumption  $P_{\rm FT}$  as a function of the control parameters under the constraint of reaching a probability of success  $\mathcal{M}_{\rm FT}=2/3$ .

#### B. Noise and metric for the seven-qubit code

Let us first consider the noise at the level of a single physical qubit. Instead of the infidelity, we consider the error probability  $p_{\rm err}$  of the qubit. We employ the same noise model as that of Sec. III. We write  $p_{\rm err} = \frac{1}{2} \gamma \tau_{\rm step} \left( \frac{1}{2} + n_{\rm noise} \right)$  [82]. Here,  $\tau_{\rm step}$  is the time step of the quantum computer, taken to be equal to the time taken to perform the slowest qubit gate, i.e., the 2qb gate in our model.

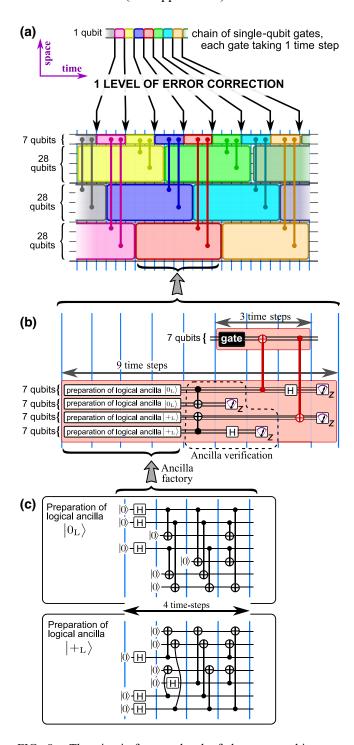

From now on, we focus on the seven-qubit code. The basic components of the fault-tolerance scheme are illustrated in Fig. 8, starting at the top with the logical circuit to be implemented (drawn here, for simplicity, for just single-logical-qubit gates). Each logical gate is broken down into the physical qubits and gate operations that are needed to implement it in a fault-tolerant manner, with qubits that carry the actual logical information, as well as ancillary qubits (or just "ancillas") that permit the syndrome measurements for error correction. Also shown in Fig. 8 are the details of the preparation of the state of the ancilla

for the error correction to work in a fault-tolerant manner. These details are critical inputs to our power-consumption calculations below (see Appendix A).

FIG. 8. The circuit for one level of the seven-qubit error-correction code on a series of single-qubit gates [89,90]. Gates acting on groups of seven qubits are transversal. The *ancilla factory* prepares the state of the logical ancillas [92]. The vertical blue lines indicate time steps in the algorithm. See the main text for a brief description of this circuit, with additional technical details given in Appendix A.

The power of the code can be increased, thereby acquiring the ability to remove more errors, by concatenating the basic seven-qubit code. At the first level of concatenation, the logical qubit is encoded into seven physical qubits; at the next level of concatenation, the logical qubits of the previous level are treated like physical qubits, and the logical qubit at this level is encoded into seven logical qubits of the previous level, thus employing  $7^2$  physical qubits in all; and so on in a recursive manner. Error correction is done at every level of the concatenation. After k levels of concatenation, the error probability per logical qubit per (logical) time step can be shown to be [90]

$$p_{\text{err};L} = p_{\text{thr}} \left( p_{\text{err}} / p_{\text{thr}} \right)^{2^k}, \tag{15}$$

where  $p_{\rm thr} \approx 2 \times 10^{-5}$ . Here,  $1/p_{\rm thr}$  is an integer that counts the number of ways in which the extra physical elements (qubits, gates, and measurements) added to correct errors can have faults (for a fuller explanation, see, e.g., Ref. [83]).  $p_{\rm thr}$  is the aforementioned fault-tolerance threshold: The error per logical qubit decreases as k increases only if the qubit error probability  $p_{\rm err}$  is less than  $p_{\rm thr}$ . This is an important constraint on the physical qubits that we will consider for our simulations, requiring fidelities that can be significantly beyond the state of the art.

Increasing k increases the ability to remove errors and hence compute more accurately. The price to pay, however, is a large increase in the number of physical qubits. For a computation with  $Q_L$  logical qubits, the fault-tolerant scheme requires Q physical qubits, where

$$Q \equiv g(k) \times Q_L = (91)^k Q_L. \tag{16}$$

This formula can be understood from Fig. 8, which illustrates how fault-tolerant quantum computation with the seven-qubit code works. We focus on the first level of concatenation, where one logical qubit is encoded into seven physical qubits. In addition to the seven physical qubits, one needs 28 physical qubits as ancillas to facilitate syndrome measurements for the code. The 28 ancillas are explained in Refs. [89,90]. In short, they should be understood as two groups of 14 ancillas each, with one group for each of the two kinds (X or Z) of syndrome measurements needed for the seven-qubit code. Each group of 14 should again be thought of as two groups of seven ancillas; one of these groups is used to verify the quality of the ancillas in the other group, which is necessary to guarantee fault tolerance. Furthermore, the ancillas have to be prepared in specific states for the syndrome measurement. As the ancilla preparation takes a certain number of time steps to complete (four time steps, as shown in Fig. 8), in order for all 28 ancillas to be ready at the time at which they are needed in the syndrome measurement, we find that, at any one time step, there must be three groups of 28 ancillas each in various stages of preparation (see Fig. 8). This then gives the  $91 = 7 + 3 \times 28$  in Eq. (16), for k = 1. Then, the recursive structure of the concatenation, treating each logical qubit as if it were a physical qubit at the next level, gives the  $(91)^k$  factor for k levels of concatenation in Eq. (16).

This systematic analysis allows us to derive the number of 1qb gates, 2qb gates, and measurements running in parallel as needed in Eq. (14) to estimate the power consumption; the details are given in Appendix A. Finally, the overall metric introduced in Sec. V A for our generic algorithm is given by

$$\mathcal{M}_{\rm FT} = \left[1 - p_{\rm thr} \left(p_{\rm err}/p_{\rm thr}\right)^{2^k}\right]^{\mathcal{N}_L}.\tag{17}$$

For simplicity, we use the linear approximation,

$$\mathcal{M}_{\rm FT} = 1 - \mathcal{N}_L p_{\rm thr} \left( p_{\rm err} / p_{\rm thr} \right)^{2^k}, \tag{18}$$

which slightly overestimates the effect of the errors (i.e., slightly underestimates the metric).

#### C. Full-stack hardware model

We now present our full-stack model, which goes significantly beyond the pedagogical model used in earlier sections. In short, we replace the simplified setup of Fig. 2(a) by the full setup of Fig. 9. This involves key improvements over the simplified setup of Fig. 2(a) that bring us closer to experimental reality. These improvements dealing with the control electronics and the cryogeny are presented below, with more details in the appendixes. We take inspiration from current technologies for the improved model. Nevertheless, our interest is in understanding general trends that will provide guidelines for ongoing and future research and this leads us to consider values that are beyond the current state of the art.

#### 1. Cryogenic model

The first improvement to bring us closer to experimental reality is that we spread the attenuation on the microwave control lines over multiple temperature stages (see the left-hand side of Fig. 9). This is known to be much more energy efficient than placing all the attenuation at  $T_{\rm qb}$ , as we had done in Fig. 2. Much of the heat generated by attenuators is thus dissipated at higher temperatures, where it costs much less power to extract it. Adding more temperature stages always reduces power consumption but it is often technically challenging. We observe that the benefits of adding another stage becomes small once there are about five stages, so we take five temperature stages here. Appendix B 1 gives the detailed specifications of these five stages of attenuation. The heat conducted by the control lines turns out to be significant and to minimize this

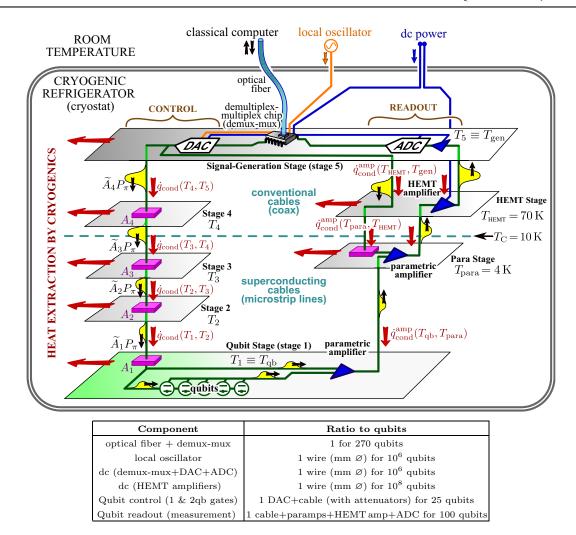

FIG. 9. A sketch of our model of the multistage cryogenics with all components. It is important to maximize the number of physical qubits per other component (using multiplexing etc.), and the table gives reasonable values for the ratio of the number of components to the number of physical qubits. The qubit control lines are particularly crucial to the energy consumption; we model them with four stages of attenuation (attenuators in purple), with conventional coaxial cables down 10 K and superconducting microstrip lines below that. The readout is less crucial to the energy consumption if one uses superconducting parametric amplifiers (paramps) at  $T_{\rm qb}$  and  $T_{\rm amp} = 4$  K, with a third amplification stage using high-electron-mobility transistors (HEMTs) at  $T_{\rm HEMT} = 70$  K. The black arrows indicate the flow of information and/or signals, while the red arrows indicate heat conduction. The demux-mux, digital-to-analog converters (DACs), analog-to-digital converters (ADCs), attenuators, and amplifiers all also generate heat.

heat conduction, we assume all wiring to be superconducting below 10 K and thus to conduct vastly less heat than normal-metal wires. The heat-conduction properties of these control lines are given in Appendix B 2. As above, we assume that the cryogenics have Carnot efficiency and thus use the minimal possible power to evacuate heat as allowed by the laws of thermodynamics. We take this for simplicity as it already gives the right order of magnitude for large-scale cryogenics, where the state of the art is 10–30% of Carnot efficiency [80]. Evidently, the results change if one considers small-scale cryostats that operate far below Carnot efficiency, as shown in the example in Appendix E.

#### 2. Control electronics

A second improvement to bring us closer to experimental reality is that we now add the circuitry to read out the qubits (see the right-hand side of Fig. 9). The signal from the qubits has to be amplified significantly above the thermal noise level at the temperature stage to which the signal is being sent. As amplifiers generate heat, it is again much more energy efficient to have a chain of amplifiers at different temperature stages than to have all the amplification occur at the qubit temperature. Superconducting parametric amplifiers (paramps) generate much less heat than conventional amplifiers but they can only operate at temperatures below 10 K. At

higher temperatures, the best option is amplifiers based on high-electron mobility transistors (HEMTs). Here, we take the amplification chain inspired by recent experiments [60]: We assume one superconducting paramp at the qubit temperature, which sends the signal to another superconducting paramp at 4 K. This then sends the signal to a HEMT amplifier at 70 K, which finally sends it to the chip that reads out the signal. Appendix B 3 gives the detailed specifications for this chain of amplifiers. The readout lines are the same materials as the control lines, so their heat-conduction properties are those described in Appendix B 2.

The third and final improvement is that we assume there is a signal-generation stage at temperature  $T_{\rm gen}$ , with chips that carry out the signal generation and readout. Below, we want to find the optimal value of  $T_{gen}$  that minimizes the power consumption. For this, we need to know the heat dissipated by the signal-generation stage, which requires a specification of what it contains. Our model assumes that the signal-generation stage receives digitized instructions of the wave form to generate for each gate operation down an optical fiber from a conventional (classical) room-temperature computer. The signalgeneration stage contains a demultiplex (demux) chip that demultiplexes the photonic signal in the optical fiber and turns it into digital electrical signals. These digital signals are turned into analog signals in the digital-toanalog converters (DACs) and are then superimposed on the local-oscillator signal (at 6 GHz) to make the microwave signal that performs the desired gates on the target qubits. At the same time, the signal-generation stage takes the microwave wave form coming from the measurement of the qubit through the amplifiers and digitizes it in the analog-to-digital converter (ADC). This is then turned into a multiplexed photonic signal, which is sent through the optical fiber to the conventional roomtemperature computer. This (classical) computer demultiplexes it and digitally demodulates the wave form, allowing it to deduce the state of the qubit in question [62]. It also decodes (i.e., interprets) the syndromes coming from the error-correction procedure and manages the algorithm at the logical level. Further details of this are provided in Appendix B5, which argues that this classical computer will not be a significant contribution to the power consumption, and so can be neglected at our level of approximation.

#### 3. Control parameters

We can now summarize the four control parameters that we will use for our optimizations, namely,  $T_{\rm qb}$ ,  $T_{\rm gen}$ , A (the *total* attenuation on the lines), and k, the concatenation level. The temperature of each stage and the amount of attenuation put on these stages are taken to be functions of  $T_{\rm qb}$ ,  $T_{\rm gen}$  and A [see Eq. (B11) in Appendix B]. As

explained around Eq. (B11), we consider such constraints to lead to a relatively optimal distribution of attenuation and temperatures.

## D. Full-stack power cost for the seven-qubit code 1. Software assumptions

We first write down Eq. (14), describing the power consumption for the specific case of fault-tolerant quantum computing based on the seven-qubit code. For this, we need to look at the circuit for one level of error correction for any Clifford logic gate (see Fig. 8). The circuit looks the same for such any logic gate, except for the contents of the black box marked "gate" [this "gate" in Fig. 8(b) is transversal, containing seven physical gates corresponding to the logic gate]. However, this black box makes a very small contribution to the total number of gate operations in the circuit, so once the error correction is included (i.e.,  $k \ge 1$ ), all logical gates require about the same number of physical gate operations. Thus one expects that any logical gate will have a power consumption very similar to that of a (logical) identity gate that does nothing except preserve the quantum state of the logical qubit. This intuition is confirmed and carefully quantified in Appendix A. As a result, the power consumption of any given algorithm is almost independent of what the algorithm is actually doing at the logical level; it only depends on the number of logical qubits  $Q_L$  and logical depth  $D_L$  of that algorithm. We can thus take the power consumption of any algorithm to be close to that of a logical memory the only job of which is to preserve the state of  $Q_L$  logical qubits for  $D_L$  logical time steps.

The power consumption of such a circuit can be taken as proportional to  $Q_L$  (see Appendix A), with

$$P_{\text{FT}} \simeq Q_L \left( \frac{4(64)^k}{185} \left[ 16P_{2qb} + 7P_{1qb} + 7P_{\text{meas}} \right] + (91)^k P_Q \right),$$

(19)

using an approximation that gets better at higher k. Appendix A shows that this approximation gets the order of magnitude right for any circuit of Clifford gates at k = 1 and is within a few percent of the correct result for  $k \ge 2$ .

To keep the modeling here as compact as possible, we neglect the power consumption associated with fault-tolerant non-Clifford gates (such as T gates). While a quantum computer without at least one type of non-Clifford gate is not universal (and can be efficiently simulated on a classical computer), the modeling of non-Clifford gates is very different than that of Clifford gates. Appendix A 2 discusses this modeling and points out how rare non-Clifford gates are in the algorithms that we consider. It then argues that accounting for them would complicate the modeling without significantly changing the resulting power consumption.

#### 2. Hardware assumptions

What remains to be calculated is the contribution of each hardware component to  $P_{1qb}$ ,  $P_{2qb}$ ,  $P_{meas}$ , and  $P_{Q}$ . We compute  $P_{1qb}$  and  $P_{2qb}$  in the same manner as in the noisy quantum circuit in Sec. IV, except that we now also account for the chain of attenuators at different temperatures. The expressions for  $P_{1qb}$  and  $P_{2qb}$  are given in Appendix B 6. For  $P_{meas}$ , we use a similar approach to that for  $P_{1qb}$ , as the measurement in our model involves sending a microwave signal similar to that for a gate operation. Our estimations, however, show that in most cases  $P_{meas}$  is negligible compared to  $P_{1qb}$ , so we drop it.  $P_{1qb}$ ,  $P_{2qb}$ , and  $P_{meas}$  grow whenever the qubit temperature is reduced to raise the physical qubit fidelity. A larger physical qubit fidelity hence requires a larger power consumption for gates and measurements.

For our simulations, we make the qubit lifetime vary between 3.5 ms and 1 s. However, our main discussion will be based on a lifetime of 50 ms, which is about 100 times better than the state of the art in transmon qubits [93]. This is necessary since, as mentioned above, a successful calculation using a fault-tolerant scheme built from the seven-qubit code requires an error probability smaller than the threshold of  $p_{\rm thr}=2\times10^{-5}$ , which is achievable only for qubits with a long enough lifetime.

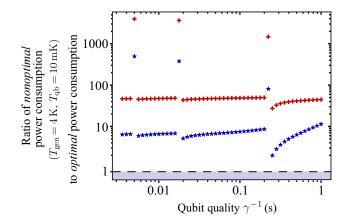

Next,  $P_Q$  is the part of the power consumption that scales as the number of physical qubits, independent of whether gates or measurements are being performed. It has two different contributions. The first is the power consumption of the cryogenics to remove the heat conducted down the microwave lines that control and read out the qubits. Their thermal properties are given in Appendix B 2. The second is the heat generated by all electronics that are always on. This includes the amplifiers at 4 K and 70 K, the electronics for control and readout at  $T_{\rm gen}$ , and the classical computer at ambient temperature. Their detailed specifications are given in Appendix B 3, with the full list of parameters summarized in Tables II and III.