## Cerise: Program Verification on a Capability Machine in the Presence of Untrusted Code

Aïna Linn Georges, Armaël Guéneau, Thomas Van Strydonck, Amin Timany, Alix Trieu, Dominique Devriese, Lars Birkedal

### ▶ To cite this version:

Aïna Linn Georges, Armaël Guéneau, Thomas Van Strydonck, Amin Timany, Alix Trieu, et al.. Cerise: Program Verification on a Capability Machine in the Presence of Untrusted Code. Journal of the ACM (JACM), 2023, 10.1145/3623510. hal-03826854v3

## HAL Id: hal-03826854 https://hal.science/hal-03826854v3

Submitted on 6 Nov 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Cerise: Program Verification on a Capability Machine in the Presence of Untrusted Code

AÏNA LINN GEORGES\*, MPI-SWS, Germany

ARMAËL GUÉNEAU\*, Université Paris-Saclay, CNRS, ENS Paris-Saclay, Inria, Laboratoire Méthodes Formelles. France

THOMAS VAN STRYDONCK, imec-Distrinet, KU Leuven, Belgium

AMIN TIMANY, Aarhus University, Denmark

ALIX TRIEU\*, ANSSI, France

DOMINIQUE DEVRIESE, imec-Distrinet, KU Leuven, Belgium

LARS BIRKEDAL, Aarhus University, Denmark

A capability machine is a type of CPU allowing fine-grained privilege separation using *capabilities*, machine words that represent certain kinds of authority. We present a mathematical model and accompanying proof methods that can be used for formal verification of functional correctness of programs running on a capability machine, even when they invoke and are invoked by unknown (and possibly malicious) code. We use a program logic called Cerise for reasoning about known code, and an associated logical relation, for reasoning about unknown code. The logical relation formally captures the capability safety guarantees provided by the capability machine. The Cerise program logic, logical relation, and all the examples considered in the paper have been mechanized using the Iris program logic framework in the Coq proof assistant.

The methodology we present underlies recent work of the authors on formal reasoning about capability machines [Georges et al. 2021; Skorstengaard et al. 2019a; Van Strydonck et al. 2022], but was left somewhat implicit in those publications. In this paper we present a pedagogical introduction to the methodology, in a simpler setting (no exotic capabilities), and starting from minimal examples. We work our way up to new results about a heap-based calling convention and implementations of sophisticated object-capability patterns of the kind previously studied for high-level languages with object-capabilities, demonstrating that the methodology scales to such reasoning.

CCS Concepts: • Security and privacy  $\rightarrow$  Logic and verification; Formal security models; • Theory of computation  $\rightarrow$  Program verification; Program specifications.

Additional Key Words and Phrases: capability machines, capability safety, universal contracts, program logic, separation logic, CHERI

Authors' addresses: Aïna Linn Georges, ageorges@cs.au.dk, MPI-SWS, Germany; Armaël Guéneau, armael.gueneau@inria.fr, Université Paris-Saclay, CNRS, ENS Paris-Saclay, Inria, Laboratoire Méthodes Formelles, 91190, Gif-sur-Yvette, France; Thomas Van Strydonck, thomas.vanstrydonck@cs.kuleuven.be, imec-Distrinet, KU Leuven, Belgium; Amin Timany, timany@cs.au.dk, Aarhus University, Denmark; Alix Trieu, alix.trieu@ssi.gouv.fr, ANSSI, France; Dominique Devriese, dominique.devriese@kuleuven.be, imec-Distrinet, KU Leuven, Belgium; Lars Birkedal, birkedal@cs.au.dk, Aarhus University, Denmark.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2023 Association for Computing Machinery.

0004-5411/2023/9-ART \$15.00

https://doi.org/10.1145/nnnnnnnnnnnnn

<sup>\*</sup>This work was carried out while the author was affiliated with Aarhus University.

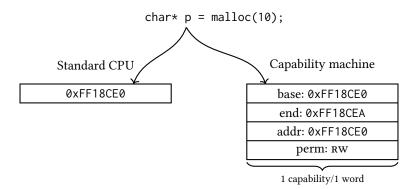

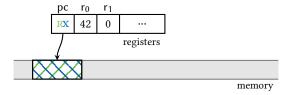

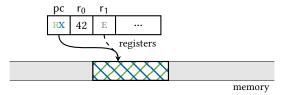

Fig. 1. Representation of a pointer in a standard architecture vs. a capability machine. A capability is similar to a pointer with extra meta-data.

#### **ACM Reference Format:**

#### 1 INTRODUCTION

A capability machine is a type of CPU that enables fine-grained memory compartmentalization and privilege separation through the use of *capabilities*. This type of hardware architecture has been studied since the 1960s [Dennis and Van Horn 1966; Levy 1984], and in particular more recently as part of the CHERI project [Watson et al. 2020]. Capability machines offer fine-grained and scalable privilege separation at the hardware level and they are a compelling target for secure compilation [Chisnall et al. 2017; El-Korashy et al. 2021; Skorstengaard et al. 2019b; Van Strydonck et al. 2019]. As such, capability machines have recently enjoyed a lot of interest from industry as a promising way to mitigate memory safety related vulnerabilities. As part of the Digital Security by Design initiative, a prototype, Morello, has been developed by Arm. Microsoft has also recently announced CHERIoT [Amar et al. 2023], an implementation of CHERI more adapted to small embedded systems. Compared with other security mechanisms like secure enclaves [Maene et al. 2018], or memory-management-unit (MMU)-based models, capability machines offer a fine-grained and flexible security model without compromising on efficiency [Watson et al. 2016].

Capability machines distinguish, at the level of hardware, between machine integers and capabilities; and a capability can be understood as a pointer with associated metadata, cf. Fig 1. A machine word containing an integer value can only be used for numerical computations and cannot be used as a pointer to access memory. On the other hand, a machine word containing a capability can be used to access a given portion of memory, depending on the metadata contained in the capability. We also say that the capability *has authority over* some fragment of memory.

A capability thus corresponds to a native machine value, and can be stored in a CPU register or in memory. While this might seem wasteful due to the amount of extra metadata that needs to be carried around, for realistic capability machines a lot of work has been dedicated to the design of compressed representations for capabilities [see, e.g., Carter et al. 1994; Woodruff et al. 2019]. In this paper, we will abstract from these details and represent capabilities in their uncompressed form, as a tuple carrying the metadata.

A capability machine guarantees the integrity of capabilities: one cannot create fresh capabilities out of thin air or modify the metadata of existing capabilities in arbitrary ways. For instance, CHERI associates tags to machine words to identify whether they represent a capability or an integer. Such a tag bit is checked and set by the machine, and is not directly accessible by software. More generally, new capabilities can only be derived from existing capabilities using a restricted set of operations provided by the machine. As such, all capabilities on the system are recursively derived from the full-authority capabilities that are initially provided to software at boot time. Intuitively, the machine ensures that a given program cannot forge capabilities and obtain more authority than it held previously, a property sometimes referred to as capability monotonicity [Nienhuis et al. 2020].

Capabilities therefore allow a piece of code to interact securely with untrusted third-party code, even within the same address space, by restricting the set of capabilities the untrusted code (transitively) has access to. In a system composed of mutually untrusted components (which might even contain malicious code), capabilities provide a way of enforcing that the overall system nevertheless satisfies some security properties.

Note, however, that capabilities are low-level, flexible, building blocks, which operate at the level of the machine code and whose metadata "just" triggers some additional runtime checks by the machine. This means that the *properties* we can actually enforce using capabilities crucially depend on how we *use* capabilities: the variety of properties that can be enforced stems from how one can use and combine capabilities.

In this paper we show how we can formally *prove* that security properties are enforced for some known verified code, *even when* that code is linked with unverified untrusted third-party code. Our model of interaction between the known and unknown code is very simple: we assume the code is in the same address space and that control is transferred from one to the other using an ordinary jump instruction. We focus on a restricted subset of the capabilities present in the CHERI architecture (using only "normal" read/write capabilities and a kind of so-called sentry capabilities, which provide a basic form of encapsulation, see Section 2.4). Because the security properties we consider hold even in the presence of unverified unknown code, they are sometimes referred to as *robust safety* properties [Swasey et al. 2017]. The security properties we focus on are centered around memory compartmentalization, in particular, local state encapsulation. We consider a range of examples, starting with very basic examples (sharing a buffer with some unknown code), through implementations of closures with encapsulated state, and end up with a quite sophisticated low-level implementation of an interval library, for which we show that certain representation invariants are preserved, even when interacting with unknown code.

We proceed as follows:

- We first explain informally how one can program with capabilities and use capabilities to enforce memory compartmentalization (Section 2).

- We then introduce the formal operational semantics of a simple capability machine with sentry capabilities (Section 3).

- We define the Cerise program logic which can be used to formally verify the correctness of programs running on the capability machine. Our program logic is defined by instantiating the Iris framework [Jung et al. 2018], which provides an expressive separation logic with powerful reasoning principles, including, in particular, the notion of a *logical invariant* (Section 4).

- We define, using our program logic, the specification of what a "safe" capability and a "safe" program is. Intuitively, a capability (respectively, a program) is "safe" if it cannot be used to invalidate an invariant. Hence, safe capabilities can be shared freely with unknown code. Safety of a capability is defined in the program logic as a unary logical relation (Section 5).

- We show that if a program only has access to "safe" values, then running the program itself is also "safe". This is a global property of the capability machine, expressing its capability safety: it is not possible to increase one's authority beyond what was available initially, independently of the sequence of instructions that one executes (Section 5). Concretely, the theorem takes the form of a contract that holds for arbitrary code, and which can be combined in the program logic with specifications for trusted code, which are themselves proved using an interactive proof mode inherited from the Iris framework [Krebbers et al. 2017]. The last piece of the puzzle is then a so-called Adequacy theorem (Section 4), which relates invariants established in the program logic to the operational semantics of the machine. Given a concrete scenario (typically, a complete system mixing known verified code with unknown untrusted code), this makes it possible to obtain a theorem about the execution of the system which only depends on the operational semantics of the machine (not on the program logic).

- In Section 6 we then return to the examples from Section 2 and show how to use Cerise to formally prove that the desired memory compartmentalization results really do hold.

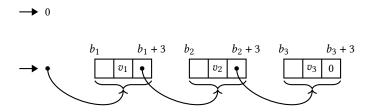

- In Section 7 we consider more sophisticated examples, which involve dynamic memory allocation. We focus on the low-level implementation of ML-like programs, and introduce a heap-based calling convention for closures implementing ML functions. We extend the earlier Adequacy theorem to account for dynamically allocated memory.

- In Section 8 we demonstrate how to use our methodology to establish correctness of object capability patterns (OCPs) from the literature. In particular, we consider the OCP of dynamic sealing, as presented by [Swasey et al. 2017] in the context of a high-level language and we demonstrate that Cerise can be used to prove similar results about a low-level implementation of their example.

- Section 9 offers some perspectives on the relevance of our technical contributions and how we envision them being used in the development of secure systems.

- Finally, we discuss related work in Section 10.

This paper pedagogically introduces and explains the methodology underlying a sequence of recent research papers [Georges et al. 2021; Skorstengaard et al. 2018, 2019a; Van Strydonck et al. 2022], in the form of the Cerise program logic, but also contributes new material. The operational semantics, program logic and logical relation discussed in Sections 3, 4 and 5 are based on those used by Georges et al. [2021] (but we have removed local and uninitialized capabilities as well as Kripke indexing for simplicity and instead added much more extensive explanations and proofs). Sections 2 and 6 are new; they provide a clear and accessible introduction to capability machine programming and our reasoning tools. The examples in Sections 7-8 are also new and represent a non-trivial verification effort.

The results and examples presented here have been fully formalized in Coq, and are available online: https://github.com/logsem/cerise/tree/journal. The development can also be viewed online at https://logsem.github.io/cerise/journal/; we use circled numbers such as ① to link directly to corresponding Coq formal statements in the following.

#### 2 PROGRAMMING WITH CAPABILITIES

Let us give a taste of how one might use capabilities when writing programs with the goal of enforcing some additional memory protection or encapsulation guarantees. We consider a fairly simple but quite general adversarial model, where we wish to verify the correctness of a *known*

<sup>&</sup>lt;sup>1</sup>Because it holds for arbitrary code, we sometimes refer to this as a universal contract.

(b) Scenario 2: being called by untrusted code (possibly many times)

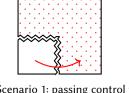

Fig. 2. Two scenarios where a (trusted) component interacts with its (untrusted) context. The trusted component is represented with a plain background, while the untrusted context is represented with a red dotted background.

component interacting with a possibly adversarial third-party component whose code is unverified and untrusted.

In this section we detail two concrete example programs, which use capabilities in two different scenarios. In the first scenario, illustrated in Figure 2a, we consider a program that eventually passes control to the untrusted third-party code, but uses capabilities to protect a region of memory containing some secret data from being accessed by the untrusted code. In the second scenario (Figure 2b), we consider the case of a verified component being called by the third-party code. The goal is then for the verified component to use capabilities to protect (or "encapsulate") a piece of private memory, which it may access during its execution, but which should remain inaccessible to the unverified code.

#### 2.1 Anatomy of a capability (in our model)

We are interested in a subset of the capabilities available in a CHERI capability machine. We thus work with a simplified machine model, featuring basic capabilities that are used to give access to a range of memory, as well as so-called "sealed entry" capabilities (abbreviated as "sentry" capabilities [Watson et al. 2020, §3.8]) that provide encapsulation features. The sentry capabilities were also called "enter" capabilities in earlier work, e.g., in the M-Machine by Carter et al. [1994].

Concretely, we model capabilities as 4-tuples (p, b, e, a). In actual hardware, capabilities are encoded as fixed-size binary words, but here we abstract over their concrete representation.

Capability: (p, b, e, a)  $p \in \{0, R0, RX, RW, RWX, E\}$  permission  $b \in Addr$  base address  $e \in Addr$  end address  $a \in Addr$  current address

A capability (p, b, e, a) represents a machine word that can be used to access memory within the region [b, e) delimited by its base address b and end address e. The permission p specifies what is possible to do within this memory range: permission o specifies that the capability actually gives no access rights, RO grants read-only access to memory, RX grants the right to read and execute the contents of the memory, RW gives read and write access, and RWX gives read, write, and execute access. Capabilities with permission E behave a bit differently (they are used to provide a form of encapsulation), and will be explained later in Section 2.4.

A capability is meant to be used as a pointer, and thus additionally points to a specific address a (typically, but not necessarily, belonging to the range [b, e)). Each time the capability is used to

access memory, the machine will automatically check that a is between bounds b and e, and that the access is permitted according to p. From a capability (p, b, e, a) it is easy to derive another capability (p, b, e, a') pointing to a different address a' also within range [b, e) – in other words, while a capability points to a specific address, it really holds authority over the whole region delimited by its beginning and end address.

Note that, on a capability machine, machine words can represent not only binary-encoded capabilities, but also traditional fixed-size integers. However, unlike on a traditional computer architecture, integers cannot be used as pointers. In other words, without holding a capability, one cannot access memory at all. In this paper, we rely on difference in notation to distinguish between capabilities and integers. In actual hardware, this is done by associating an extra one-bit tag to each word to distinguish capabilities from integers.

#### 2.2 Sometimes, failure is a good thing

It is worth pointing out a sometimes counter-intuitive aspect of reasoning about security of programs running on a capability machine, especially for readers with a background in reasoning about safety in higher-level languages. For a high-level language, program safety can be seen as the absence of undefined behavior or runtime errors. For instance, an out-of-bounds array access is undefined behavior in C, and it leads to a runtime error, such as raising an exception, in memory-safe languages such as Rust or OCaml. We are instead interested in *security* properties for which a runtime failure can actually be considered a good thing.

Generally speaking, a low-level machine has many cases where it can fail at runtime, stopping the normal course of execution. In a standard (non-capability) machine, this can happen, e.g., if the machine attempts to execute an invalid instruction which cannot be decoded. The addition of capabilities only adds more possibilities for runtime faults: each time a capability is used, the capability machine will check that it has adequate permission and bounds, and raise a runtime fault otherwise.

Now, the point is that, from a security perspective, these additional runtime faults are a good thing. Using these additional checks, the capability machine turns dangerous behavior (out-of-bounds accesses leading to buffer overflow attacks, etc.) into proper faults before they can cause damage. Thus, for our purposes, it is always safe for the machine to fail: it means that an illegal operation may have been attempted, and the execution has been stopped in response.

Of course, when writing concrete programs, we will typically want to verify that we do not involuntarily trigger faults, as this would make our programs less useful. But when interacting with adversarial code, this is a possibility that we have to take into account anyway: we cannot prevent unknown code from shooting itself in the foot, e.g. by trying to access memory it does not have a valid capability for, or by decoding illegal instructions.

To sum up, in this work we reason about security properties that are not violated in the case of machine failure. This includes, for example, integrity of private data: no data can be compromised if the machine stops running. It is therefore useful to keep in mind that we consider failure to be trivially safe!

#### 2.3 Restricting access to memory by constraining available capabilities

Consider Scenario 1 from Figure 2a: how can one write a program which passes control to untrusted code while protecting some secret data? That is, we wish to write a program that sets up capabilities so that its secrets are preserved even after it runs untrusted code.

The key intuition is that, at any point of the execution, one can only access the part of memory that is accessible using the currently available capabilities. In other words, the authority of a running program comes from the set of capabilities which are transitively reachable from the CPU registers.

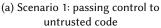

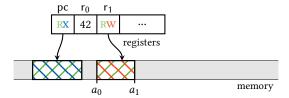

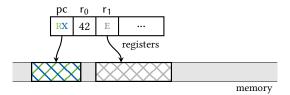

This is illustrated below, in a scenario where the pc register ("program counter") contains a capability with permission Rx pointing to some memory region (containing the code of the program being executed), and register  $r_1$  contains a capability with permission Rw, pointing to a region of memory, which itself contains an Rw capability pointing to another memory region. The collection of the "hatched" memory regions corresponds to the overall subset of memory accessible by the program.

If one wishes to reduce the set of available memory or its associated access rights—for instance to protect secrets from being leaked to an adversary—then it is enough to constrain the capabilities currently available. This can be done in a few different ways.

First, one can simply remove a capability from registers in order to remove access to the memory it was giving access to. For instance, after executing the instruction "mov r1 0", which overwrites the contents of register  $r_1$  with the integer 0, one loses access to the memory regions which were previously accessible from the capability stored in that register.

Alternatively, it is possible to restrict the range of a capability to point to a smaller memory region. This changes the set of accessible memory to a subset of what was previously available. For instance, starting from our initial scenario and running the instruction "subseg r1 a0 a1" will change the range of the capability stored in register  $r_1$  to  $[a_0, a_1)$ . (The machine will check that  $[a_0, a_1)$  is indeed included in the range of the original capability.) In our example scenario (illustrated below), we then only keep the beginning of the region accessible from  $r_1$ , and this entails that the third region of memory becomes inaccessible, since it was only reachable from a capability stored at the end of the region accessible from  $r_1$ .

Finally, one can restrict the permission of a capability to a permission that grants less access rights. For instance, running the instruction "restrict r1 R0" in our initial scenario modifies the capability stored in  $r_1$  to only grant read-only access to its corresponding memory region. Note that we still have read-write access to the last memory region, as we can still read the capability (with permission RW) pointing to it.

```

; initially, PC = (RWX, code, end, code)

r0 = (unknown) capability to the continuation

code:

mov r1 PC

; r1 = (RWX, code, end, code)

lea r1 [data-code]

; r1 = (RWX, code, end, data)

subseg r1 [data] [data+3] ; r1 = (RWX, data, data+3, data)

; jump to unknown code: we give it read-write

; access to the first 3 words of the data,

; but not the secret value

data:

; the first 3 data words contain public data that will be passed

; to the unknown code (the "Hi" string)

'H', 'i', 0,

; they are followed by secret data (the integer 42)

end:

```

Fig. 3. Program sharing a buffer with possibly adversarial code.

*Example: sharing a sub-buffer with unknown code.* Using some of the mechanisms detailed above, we can implement a very simple program that shares a buffer with unknown, possibly adversarial, code while using capabilities to protect some data that would otherwise be vulnerable to buffer overflow attacks.

The assembly code for the program is shown in Figure 3 ②. It consists of a code section containing the instructions of the program, followed by some data which (for simplicity) we simply assume to be statically allocated. The data section holds the zero-terminated string "Hi", which we wish to share with the untrusted code, and the integer 42 which represents our secret data.

Initially, we assume the program counter to contain an RWX capability for the whole region holding our program. This capability serves two purposes: it allows the machine to execute our program, but can also be manipulated by the program itself to derive a capability pointing to its own data. By convention, the register  $r_0$  is assumed to contain a capability to the continuation of the program, i.e. other code that the program will pass control to after it is done executing. As no assumption is made about the contents of  $r_0$ , it is conservatively assumed to point to unknown, arbitrary code.

Our program executes as follows: it first loads the capability held by the program counter into register  $r_1$ . Then, using the lea instruction, it changes the "current address" of the capability to point to the data label (lea modifies a capability by adding an offset to its "current address"). In assembly programs, we use the brackets notation  $[\ldots]$  to denote an arithmetic expression that is computed statically when assembling the program.

At this point, the capability held in r<sub>1</sub> points to the start of the "Hi" string, but has (RWX) authority over the whole code and data section. This capability would be unsafe to share with the untrusted code, as they could simply use lea to increment the capability's current address past the end of the string, and obtain a valid capability to the secret value (thus performing a basic "buffer overflow" attack). To prevent this from happening, we use the subseg instruction to obtain a capability whose range of authority is restricted to the sub-buffer holding the "Hi" string. Note that we are not restricting the permission of the shared sub-buffer capability. Following the principle of least privilege, one might expect that we remove its execute (-x) permission as well. However, while it would have been good practice, doing so would not have been necessary to uphold the expected security property<sup>2</sup>, and we can thus prove something stronger. Finally, we pass control to the untrusted code by using the jmp instruction, loading the contents of register r<sub>0</sub> into pc.

This example illustrates that even a basic mode of use of capabilities (restricting them appropriately) can easily prevent buffer overflow attacks. In Section 6.1, we show how we can formally prove that, for any untrusted code, the value of the secret data will be equal to 42 at every step of the execution, including after control has been passed to the untrusted code. We have also developed a relational model, which can be used to prove that the secret value cannot even be read by the unknown code, but the details of this relational model are out of scope of this paper.

#### 2.4 Securely encapsulating code and private capabilities

The previous example illustrates how to restrict available capabilities to prevent an adversary from accessing secret data. However, what if we additionally want our program to be called back by the untrusted code, as in Scenario 2b? In that case, when the trusted code gets invoked again we would like to recover access to the capabilities it previously had to its private state.

This is unfortunately not achievable with the capabilities that we have described so far. If we remove capabilities to private memory before passing control to untrusted code, then there is no way for us to get them back later on: the only capabilities we will get access to in a further invocation are capabilities the untrusted code itself has access to.

Sentry capabilities provide this missing feature. They implement a form of encapsulation that resembles the use of closures with encapsulated local state in high-level languages, and they allow implementing compartments which encapsulate private state and capabilities but can be called from untrusted code. From a security perspective, sentry capabilities allow setting up protection boundaries: the code executing before and after an invocation of a sentry capability has different authority and thus represent distrusting components. We denote sentry capabilities with permission E (for "Enter", a terminology originating from the M-machine [Carter et al. 1994]).

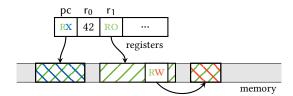

One typically creates a sentry capability pointing to a region of memory describing a compartment containing executable code and local state (or private capabilities to that local state). A sentry capability is opaque: it cannot be used to read or write to the memory region it points to, and it cannot be modified using restrict or subseg. It can thus be safely shared with untrusted third-parties: they will not be able to access the encapsulated code and data. In the figure below, the memory region pointed to by  $r_1$  (hatched in gray) is not accessible for either reading or writing.

<sup>&</sup>lt;sup>2</sup>Indeed, we will see in later sections how the execute permission generally does not provide additional authority over a capability.

The only possible operation is to "invoke" the sentry capability using the jmp instruction, thus passing control to the code held in the region pointed to by the capability (in other words, "running" the compartment). When jmp is called on a sentry capability, it turns the capability into a capability with permission read-execute (RX) over the same memory region, and puts it into the program counter register pc. This simultaneously runs the encapsulated code, and gives access to the data and capabilities stored there, which were previously inaccessible. Running instruction jmp r1 on the scenario of the previous figure leads to the machine state shown below.

Register pc now contains an RX capability to the previously opaque region, meaning that code contained in that region can execute. Furthermore, it may access other capabilities stored in that region, which can in turn be used to transitively access other private regions of memory.

*Example: a counter compartment.* To illustrate the use of sentry capabilities, let us consider the example of a simple secure compartment implementing a counter. An instance of the counter holds a private memory cell containing the current (integer) value of the counter. Every time the code in the counter's compartment is invoked, it increases the value stored in the memory cell. Using a sentry capability, one can expose the counter to an untrusted context, without giving it direct access to the counter value.

It is worth pointing out that this is similar to the use of closures encapsulating local state in high-level languages. Typically, a similar counter program could be implemented in a high-level language as follows, using a function closure to encapsulate a reference holding the counter value.

let

$$x = \text{ref } 0 \text{ in } (\lambda(). \ x := !x + 1; !x)$$

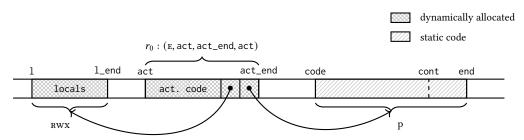

As before, our actual counter program is implemented in assembly, and its code appears in Figure 4 ③. Its implementation is divided into two parts. First, the code starting at label <code>init</code> (and ending at <code>code</code>) is used to set up the counter compartment; it is intended to run only once at the beginning of the program. Then, the region between <code>code</code> and <code>end</code> corresponds to the contents of the counter compartment itself, including its executable code (between <code>code</code> and <code>data</code>) and private data (between <code>data</code> and <code>end</code>).

The role of the initialization code is to create a sentry capability encapsulating the code-end region, and then pass control to the (untrusted) context, giving it access to the newly created sentry capability. Additionally, the initialization code stores at address data a capability giving read-write access to the compartment's region, and pointing to the counter's value at address data+1.

One might wonder why we have this extra indirection to the counter's value through the capability in data. Recall that after calling jmp on a sentry capability, the program counter is only provisioned with an RX capability. For the counter code to be able to actually increment the counter

```

; initially, PC = (RWX, init, end, init)

r0 = (unknown) capability to the context

init:

mov r1 PC

; r1 = (RWX, init, end, init)

lea r1 [data-init]

; r1 = (RWX, init, end, data)

; r2 = (RWX, init, end, data)

mov r2 r1

lea r2 1

; r2 = (RWX, init, end, data+1)

; mem[data] <- (RWX, init, end, data+1)</pre>

store r1 r2

lea r1 [code-data] ; r1 = (RWX, init, end, code)

subseg r1 [code] [end] ; r1 = (RWX, code, end, code)

restrict r1 E

; r1 = (E, code, end, code)

mov r2 0

: r2 = 0

; jump to unknown code: we only give it access

jmp r0

; to an enter capability pointing to 'code'

; when 'code' gets executed from the E capability,

PC = (RX, code, end, code)

r0 = (unknown) return capability to the continuation

code:

mov r1 PC

; r1 = (RX, code, end, code)

lea r1 [data-code]

; r1 = (RX, code, end, data)

load r1 r1

; r1 = (RWX, init, end, data+1)

load r2 r1

; r2 = <counter value>

add r2 r2 1

; r2 = \langle counter \ value \rangle + 1

; mem[data+1] <- <counter value> + 1

store r1 r2

; r1 = 0

mov r1 0

jmp r0

; return to unknown code

data:

0xFFFF, ; will be overwritten with (RWX, init, end, data+1), i.e.

; a read-write capability to the counter value

; our private data: the current value of the counter

a

end:

```

Fig. 4. Program implementing a secure counter

value (at address data+1), it needs to have write access to it. The additional RWX capability stored at address data by the initialization code is thus used to "promote" read access on the compartment's region into read-write access to that same region.

The code of the counter's compartment can then run many times, once each time the context chooses to invoke the sentry capability it got from the initialization code. At each invocation, the counter's implementation (at address code) reads the RWX capability stored in the data section, uses it to increment the value of the counter, and passes control back to its caller.

Let us walk through the details of the code. The initialization code is assumed to run starting with a program counter giving RWX access over the whole program region. The first four instructions derive, from the program counter, RWX capabilities pointing to addresses data and data+1. Then, using the store instruction, the capability (RWX, init, end, data+1) is stored at address data. Next, after using lea and subseg to adjust the address and bounds of the capability, a sentry capability is created pointing to the compartment's region [code, end). This is done using the restrict

instruction, turning a capability with permission RWX into a capability with permission E. Register  $r_2$  is then cleared, to make sure that the RWX capability pointing to the counter value is not leaked to the context. Finally, the initialization code jumps to the capability in  $r_0$ , which by convention points to the context.

The compartment's code (starting at address code) then gets executed each time the context invokes the sentry capability. Because we have only shared a sentry capability (E, code, end, code) with the context, we know that when the compartment gets executed, the program counter must contain (RX, code, end, code). By reading the program counter, the first two instructions of the code then derive an RX capability pointing to address data, and use it (with load) to read the capability that was stored there, granting RXX access to data+1. The subsequent load, add and store instructions use this second capability to increment the value of the counter. Finally, before returning to the context by jumping to  $r_0$ , the program takes care of clearing register  $r_1$ , overwriting its contents with 0. This is quite crucial, as otherwise an RXX capability would be leaked to the context, giving it direct access to the counter's private state!

To sum up, our example program carefully selects which capabilities it shares with unknown code, and leverages the encapsulation properties of sentry capabilities provided by the machine. Consequently, it should seem clear, at least informally, that the integrity of the counter's value is guaranteed through the execution. More precisely, we should be able to formally prove some invariant about it: for instance, that it is nonnegative at every step of the execution, for any untrusted context. In Section 6.2, we show in more detail how to formally establish this property.

In this section, we have showcased how one might program with capabilities in order to obtain security guarantees, and make it possible to interact with adversarial code while protecting private data and invariants.

In the rest of this paper, we show how we can make the intuitions that we have developed so far more precise, and formally prove capability safety for machine code programs that interact with untrusted code. Namely:

- We expect to have some concrete known code, which has some private data and invariants, and interacts with untrusted code.

- We formally define the operational semantics of the capability machine that we consider (Section 3). This precisely defines the behavior of the machine on which the rest of our framework is built.

- Then we develop (Section 4) a program logic which supports formally verifying correctness properties about known code. Given some verified known code, we would then like to be able to conclude some result about a complete execution of the machine, when it runs a combination of the known code and some arbitrary untrusted code.

- To that end we need a way of formally capturing the fact that the machine effectively restricts the behavior of arbitrary code at runtime, by limiting the capabilities it has access to. We do this (Section 5) by defining a logical relation capturing "capability safety" of arbitrary code.

- By combining the Adequacy theorem of our program logic and the Fundamental theorem of our logical relation, we can prove safety of concrete examples (Section 6) and obtain theorems about complete executions of the machine.

#### 3 OPERATIONAL SEMANTICS OF A CAPABILITY MACHINE

The very basis of our framework is a formal description of the capability machine we consider: which instructions it supports, and its behavior when it runs and executes programs. Technically

```

\triangleq [0, AddrMax]

a

∈ Addr

RWX

::= O | E | RO | RX | RW | RWX

∈ Perm

p

\triangleq \{(p, b, e, a) \mid b, e, a \in Addr\}

∈ Cap

с

\triangleq \mathbb{Z} + Cap

∈ Word

RO

reg \in Reg

≜ RegName → Word

\triangleq Addr \rightarrow Word

m

∈ Mem

€ ExecState ::= Running | Halted | Failed

s

\in ExecConf \triangleq Reg \times Mem

Lattice defining the \leq relation.

(We have p_1 \le p_2 if there is a path going up from p_1 to p_2 in the diagram.)

\rho \in \mathbb{Z} + \text{RegName}

r \in \text{RegName} ::= pc | r_0 | r_1 | \dots | r_{31}

i := \operatorname{jmp} r \mid \operatorname{jnz} r r \mid \operatorname{mov} r \rho \mid \operatorname{load} r r \mid \operatorname{store} r \rho \mid \operatorname{add} r \rho \rho \mid \operatorname{sub} r \rho \rho \mid

lt r \rho \rho | lea r \rho | restrict r \rho | subseg r \rho \rho | isptr r r | getp r r |

getb r r \mid gete r r \mid geta r r \mid fail \mid halt

```

Fig. 5. Base definitions for the machine's words, state, and instructions.

speaking, this description corresponds to the operational semantics of the machine, upon which the program logic described next in Section 4 is built.

Our capability machine draws inspiration from CHERI [Watson et al. 2020], albeit in a simplified form, and only covers a subset of the features found in CHERI machines. Compared to a realistic CHERI machine, we consider a number of simplifications: our instruction set is minimal, our machine does not have virtual memory or different privilege levels, machine words can store unbounded integers, every instruction can be encoded in a single machine word, we do not consider memory alignment issues, and we abstract away from the binary encoding of capabilities. Nevertheless, our semantics does capture many of the aspects that make reasoning about machine code programs challenging: our machine has a finite amount of memory, a fixed number of registers, and there are no distinctions between code and data nor structured control flow for programs, owing to the fact that program instructions are simply encoded and stored in memory as normal integers.

Figure 5 ⓐ gives the basic definitions that will play a role in the operational semantics of machine instructions. The set of memory addresses Addr is finite, and corresponds to the integer range  $[0, \operatorname{AddrMax}]$ . A memory word  $w \in \operatorname{Word}$  is either an (unbounded) integer or a capability c. Capabilities are of the form (p, b, e, a), giving access to the memory range [b, e) with permission p, while currently pointing to a. The permissions p are ordered according to the lattice appearing at the top-right of the figure, inducing a bottom-to-top partial order  $\leq$  on permissions. There are six different permissions; the null (o), read-only (ro), enter (e), read-write (row), read-execute (row) and read-write-execute (row) permissions.

The state of the machine is modeled by the semantics as a pair of an execution state s and a configuration  $\varphi$ . An execution state flag indicates whether the machine is presently running (Running), has successfully halted (Halted), or has stopped execution by raising an error (Failed). A configuration  $\varphi$  contains the state of the registers  $\varphi$ . reg and the memory  $\varphi$ . mem. A register file reg consists of a map from register names r to machine words, while the memory m maps addresses to words.

Next, Figure 5 shows the list of instructions of our machine. An instruction i typically operates on register names r, but can also sometimes take integer values as parameters;  $\rho$  denotes an instruction parameter which can be either a register name or a constant integer. Our machine

features general purpose registers  $(r_0-r_{31})$ , on top of the pc register, which points to the address in memory where the currently executing instruction is stored. (Technically speaking, pc must point to a memory cell containing an integer which can be successfully decoded into an instruction.) pc should therefore always contain a capability with at least permission RX; in any other case, the machine fails immediately.

Figure 6 ⑤ defines the small-step operational semantics for the capability machine. The rule EXECSINGLE describes how a single instruction gets executed. An execution step requires an executable and in-bounds capability in the pc register, and fails otherwise. It expects the memory cell pointed to by the capability to store an integer z, decodes it into an instruction and executes the instruction on the current state  $\varphi$ ; the new configuration is denoted  $[\![decode(z)]\!](\varphi)$ . The table making up most of Figure 6 defines the operational behavior  $[\![i]\!](\varphi)$  for each instruction i of the machine.

Most instructions use the auxiliary function updPC to increment the pc register after their proper operations. Because the address space is finite, pointer arithmetic such as incrementing pc can result in illegal addresses. To avoid notational clutter, we will always write as if arithmetic operations succeed, and consider that otherwise the machine transitions to a Failed state. The auxiliary function getWord is used to get the value corresponding to the argument  $\rho$  of an instruction: either its corresponding integer value if it is an immediate integer, or the contents of the corresponding register if it is a register name. The auxiliary function updatePcPerm is used in the definition of the behavior of the jmp and jnz instructions to unseal sentry capabilities. As mentioned previously, an additional effect of these jump instructions is to unseal sentry (E) capabilities into RX capabilities.

We now describe the semantics of the instructions of the machine, as formally defined in the table of Figure 6. The fail and halt instructions stop the execution of the machine, in the Failed and Halted state respectively. mov  $r \rho$  copies  $\rho$  (either an immediate value or the contents of the corresponding register name) into register r. The instructions load and store allow reading and writing memory: load  $r_1$   $r_2$  reads the value pointed to by the capability in  $r_2$  provided it has the permission R and points within its bounds; store  $r \rho$  stores  $\rho$  to the location pointed to by the capability in r provided it has the w permission and points within bounds. The jmp and jnz instructions correspond to an unconditional and conditional jump respectively, thus loading the provided capability into pc. Using updatePcPerm, in the case of a sentry (E) capability, they unseal it into an RX capability first. Three instructions allow deriving new capabilities from existing ones. restrict  $r \rho$  allows restricting the permission of a capability (where  $\rho$  provides an integer encoding of the desired permission), provided it is less permissive than the current permission according to  $\leq$ . subseg  $r \rho_1 \rho_2$  restricts the range of authority of the capability stored in r, provided it is a subset of the current range of the capability, and that the given integers represent valid addresses. lea  $r \rho$  modifies the current address of the capability in r, by adding to it the integer offset  $\rho$ . As should be expected, subseg and lea fail for sentry capabilities. Arithmetic operations are provided by the add, sub and 1t instructions, which implement addition, subtraction, and comparison on integers, respectively. Finally, a number of instructions allow inspecting machine words and capabilities. isptr can be used to query whether a machine word is an integer or a capability, and getp, getb, gete, and geta return the different parts of a capability (permission, bounds and address). (More precisely, getp returns an integer encoding the permission, as given by encodePerm.) If any of the capability checks for an instruction are not satisfied, the machine fails.

An important aspect of our operational semantics is how it explicitly accounts for errors: when a capability check fails (for instance when a program tries to use a capability outside of its range), the semantics does not get stuck (meaning that it would not be able to reduce): instead, it explicitly transitions to a state with the Failed execution state flag.

$$\begin{aligned} \text{ExecSingle} \\ (\text{Running}, \varphi) & \to \left\{ \begin{array}{ll} \llbracket decode(z) \rrbracket(\varphi) & \text{ if } \ \varphi.\text{reg}(\text{pc}) = (p, b, e, a) \land b \leq a < e \land \\ & p \in \{\text{RX}, \text{RWX}\} \land \varphi.\text{mem}(a) = z \\ \\ (\text{Failed}, \ \varphi) & \text{ otherwise} \end{array} \right. \end{aligned}$$

| i                                               | $[i](\varphi)$                                                                                                        | Conditions                                                                                                                                                                                                                           |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fail                                            | (Failed, $\varphi$ )                                                                                                  |                                                                                                                                                                                                                                      |

| halt                                            | $(Halted, \varphi)$                                                                                                   |                                                                                                                                                                                                                                      |

| $mov r \rho$                                    | $updPC(\varphi[reg.r \mapsto w])$                                                                                     | $w = \operatorname{getWord}(\varphi, \rho)$                                                                                                                                                                                          |

| load $r_1$ $r_2$                                | $\mathrm{updPC}(\varphi[\mathrm{reg}.r_1 \mapsto w])$                                                                 | $\varphi$ .reg $(r_2) = (p, b, e, a)$ and $w = \varphi$ .mem $(a)$<br>and $b \le a < e$ and $p \in \{\text{RO}, \text{RX}, \text{RW}, \text{RWX}\}$                                                                                  |

| store $r  ho$                                   | $updPC(\varphi[mem.a \mapsto w])$                                                                                     | $\varphi$ .reg $(r) = (p, b, e, a)$ and $b \le a < e$ and $p \in \{\text{RW}, \text{RWX}\}$ and $w = \text{getWord}(\varphi, \rho)$                                                                                                  |

| $jmp\;r$                                        | (Running, $\varphi[\text{reg.pc} \mapsto \text{newPc}]$ )                                                             | $newPc = \text{updatePcPerm}(\varphi.\text{reg}(r))$                                                                                                                                                                                 |

| jnz <i>r</i> <sub>1</sub> <i>r</i> <sub>2</sub> | if $\varphi$ .reg $(r_2) \neq 0$ , then<br>(Running,<br>$\varphi$ [reg.pc $\mapsto$ newPc])<br>else updPC $(\varphi)$ | $newPc = \text{updatePcPerm}(\varphi.\text{reg}(r_1))$                                                                                                                                                                               |

| restrict $r \rho$                               | $updPC(\varphi[reg.r \mapsto w])$                                                                                     | $\varphi$ .reg $(r) = (p, b, e, a)$ and $p' = \text{decodePerm}(\text{getWord}(\varphi, \rho))$ and $p' \le p$ and $w = (p', b, e, a)$                                                                                               |

| subseg $r \  ho_1 \  ho_2$                      | $\mathrm{updPC}(\varphi[\mathrm{reg}.r \mapsto w])$                                                                   | $\varphi$ .reg $(r) = (p, b, e, a)$ and for $i \in \{1, 2\}$ ,<br>$z_i = \text{getWord}(\varphi, \rho_i)$ and $z_i \in \mathbb{Z}$<br>$b \le z_1 < \text{AddrMax}$ and<br>$0 \le z_2 \le e$ and $p \ne E$ and $w = (p, z_1, z_2, a)$ |

| lea $r  ho$                                     | $updPC(\varphi[reg.r \mapsto w])$                                                                                     | $\varphi$ .reg $(r) = (p, b, e, a)$ and $z = \text{getWord}(\varphi, \rho)$<br>and $p \neq E$ and $w = (p, b, e, a + z)$                                                                                                             |

| add $r  ho_1  ho_2$                             | $\mathrm{updPC}(\varphi[\mathrm{reg}.r \mapsto z])$                                                                   | for $i \in \{1, 2\}$ , $z_i = \text{getWord}(\varphi, \rho_i)$<br>and $z_i \in \mathbb{Z}$ and $z = z_1 + z_2$                                                                                                                       |

| sub $r  ho_1  ho_2$                             | $\mathrm{updPC}(\varphi[\mathrm{reg}.r \mapsto z])$                                                                   | for $i \in \{1, 2\}$ , $z_i = \text{getWord}(\varphi, \rho_i)$<br>and $z_i \in \mathbb{Z}$ and $z = z_1 - z_2$                                                                                                                       |

| lt $r  ho_1  ho_2$                              | $updPC(\varphi[reg.r \mapsto z])$                                                                                     | for $i \in \{1, 2\}$ , $z_i = \text{getWord}(\varphi, \rho_i)$<br>and $z_i \in \mathbb{Z}$ and if $z_1 < z_2$ then $z = 1$ else $z = 0$                                                                                              |

| getp $r_1$ $r_2$                                | $updPC(\varphi[reg.r_1 \mapsto z])$                                                                                   | $\varphi$ .reg $(r_2) = (p, \_, \_)$ and $z = \text{encodePerm}(p)$                                                                                                                                                                  |

| getb $r_1 r_2$                                  | $updPC(\varphi[reg.r_1 \mapsto b])$                                                                                   | $\varphi.\operatorname{reg}(r_2) = (\underline{\ }, b, \underline{\ }, \underline{\ })$                                                                                                                                              |

| gete $r_1$ $r_2$                                | $updPC(\varphi[reg.r_1 \mapsto e])$                                                                                   | $\varphi.\operatorname{reg}(r_2) = (\_,\_,e,\_)$                                                                                                                                                                                     |

| geta $r_1 \; r_2$                               | $updPC(\varphi[reg.r_1 \mapsto a])$                                                                                   | $\varphi.\operatorname{reg}(r_2) = (\_,\_,\_,a)$                                                                                                                                                                                     |

| isptr $r_1 r_2$                                 | $updPC(\varphi[reg.r_1 \mapsto z])$                                                                                   | if $\varphi$ .reg $(r_2) = (\_, \_, \_)$<br>then $z = 1$ else $z = 0$                                                                                                                                                                |

| _                                               | (Failed, $\varphi$ )                                                                                                  | otherwise                                                                                                                                                                                                                            |

$$\operatorname{updPC}(\varphi) = \left\{ \begin{array}{ll} (\operatorname{Running}, \varphi[\operatorname{reg.pc} \mapsto (p,b,e,a+1)]) & \text{if } \varphi.\operatorname{reg}(\operatorname{pc}) = (p,b,e,a) \\ (\operatorname{Failed}, \varphi) & \text{otherwise} \end{array} \right.$$

$$\operatorname{getWord}(\varphi, \rho) = \left\{ \begin{array}{ll} \rho & \text{if } \rho \in \mathbb{Z} \\ \varphi.\operatorname{reg}(\rho) & \text{if } \rho \in \operatorname{RegName} \end{array} \right.$$

$$\operatorname{updatePcPerm}(w) = \left\{ \begin{array}{ll} (\operatorname{Rx}, b, e, a) & \text{if } w = (\operatorname{E}, b, e, a) \\ w & \text{otherwise} \end{array} \right.$$

Fig. 6. Operational semantics: execution of a single instruction.

J. ACM, Vol. 1, No. 1, Article . Publication date: September 2023.

#### 4 PROGRAM LOGIC

The operational semantics presented in the previous section formally define the behavior of our machine when it runs and executes code. Based on that, we expect to be able to formally verify concrete programs running on the machine.

The most direct approach would be to manually establish properties of sequences of reduction steps, based solely on the definition of the operational semantics. We do not follow this approach, because it would quickly become very tedious even for simple programs.

Instead, we draw from previous research in program logics and separation logic, and define Cerise: a program logic which provides a convenient framework in which to modularly reason about programs running on our machine. Indeed:

- It is typically more convenient to devise a system of proof rules for programs, rather than work directly at the level of abstraction provided by the bare operational semantics. Such rules form a program logic, which can be proved sound according to the operational semantics, and then can be used to verify properties of concrete programs.

- Separation logic, a family of program logics, has been widely used to reason about programs manipulating shared mutable state (such as memory). On our capability machine, not only do all programs access a mutable shared memory, but programs are themselves represented as unstructured data in memory; so the use of separation logic is particularly called for. Separation logic enables modular reasoning about programs that operate only on a sub-part of the global state, allowing them to be freely composed with programs that operate on a disjoint part of the state.

The first step is to consider what part of the machine state should be described by separation logic assertions. Here, the machine state consists of both the machine memory and the machine registers. Indeed, it is useful to modularly reason about programs operating on both a subset of memory and a subset of the available registers.

Technically speaking, we build the Cerise program logic on top of the Iris framework [Jung et al. 2018], which provides us with additional useful features, such as invariants. In the following we introduce both the basic separation logic assertions describing the machine state and additional features inherited from Iris (Section 4.1). Then, we describe the rules that are used to specify the execution of machine instructions and programs (Section 4.2).

Note that the program logic is, in a sense, only a technical device. The end goal is to obtain theorems that only refer to reductions in the operational semantics of our machine. To that end, we present (Section 4.3) an Adequacy theorem for our logic, which allows us to "extract" a correctness theorem expressed in terms of the operational semantics of the machine from a proof established in the program logic.

#### 4.1 Basic resources

Figure 7 shows the syntax of our Cerise program logic based on Iris. In this subsection, we present the underlying concepts of Iris used to define the Cerise program logic. We keep the presentation high level, and refer to Birkedal and Bizjak [2022] for a complete and pedagogical presentation of the Iris logic. We write iProp for the universe of propositions. These feature the standard connectives of higher-order logic and separation logic, including the separating conjunction \* and the magic wand -\* (read as an implication). The proposition  $\lceil \phi \rceil$  asserts that the pure proposition  $\phi$  holds, where  $\phi$  is a proposition from the meta logic.

Iris assertions can be divided in two categories: *ephemeral* assertions and *persistent* assertions. Ephemeral assertions describe facts or resources that are available at a given point but might become false or unavailable later. Persistent assertions describe facts that never cease to be true.

```

\begin{array}{lll} P,Q\in iProp::=& & \text{higher-order logic}\\ |P*Q|P \twoheadrightarrow Q|\lceil \phi\rceil \mid \square P\mid \triangleright P & \text{separation logic}\\ |a\mapsto w\mid r\mapsto w\mid \vec{a}\mapsto \vec{l} & \text{machine resources}\\ |P|& & \text{invariants}\\ |\langle P\rangle \rightarrow \langle s,Q\rangle \mid \{P\} \leadsto \{s,Q\} \mid \{P\} \leadsto \bullet \end{array}

```

Fig. 7. The syntax of our program logic.

The assertion  $\Box P$ , read "persistently P", is persistent, and asserts ownership over resources whose duplicable part satisfies P. In other words,  $\Box P$  is like P except that it does not assert any exclusive ownership over resources. As the knowledge associated with a persistent assertion can never be invalidated, persistent assertions can be freely duplicated.

The modality  $\triangleright P$ , read "later P", expresses (roughly) that the assertion P holds after one "logical step" of execution. In this paper, we mainly use it to define recursive predicates using guarded recursion. It is not necessary to understand how the modality behaves in detail and the reader can safely ignore it for the most part and just recall that it supports an abstract accounting of execution steps.

Our logic includes resources (predicates) that describe parts of the current state of the machine 6. The assertion  $a \mapsto w$  expresses that the memory cell at address a contains the machine word w. Furthermore, this assertion should be read as giving *unique ownership* over location a, giving the right to freely read and update the corresponding memory cell. Similarly, the assertion  $r \mapsto w$  asserts ownership of a CPU register r containing the word w. We write  $\vec{a} \mapsto \vec{l}$  for the ownership of contiguous memory cells at addresses  $\vec{a}$  containing  $\vec{l}$  7.

A key feature of the logic is the notion of an invariant. The assertion P asserts that P should hold at all times, now and for every future step of the execution (where P can be any separation logic assertion). An invariant is a persistent assertion. Unlike  $\Box P$ , which does not assert any exclusive ownership over resources and is established by showing it does not depend on other ephemeral assertions, P is used to encapsulate any assertions into an invariant. An invariant P can be created (or "allocated") by handing over the resources for P, turning them into P. Then, whenever we know that P holds, we can get access to the resources P held in the invariant, but only for the duration of one program step. Indeed, since the invariant must hold at every step of the execution, when accessing its resources, one needs to show that it holds again no later than one program step after. A more precise rule for accessing invariants is given next in Section 4.2 (rule Inv).

#### 4.2 Program specifications

The predicates for machine resources we just presented allow describing the state of the machine, as well as modalities to guard those resources, which allows us to relate the state of the machine to its execution steps. Our logic, moreover, includes assertions that can be used to specify machine executions, similar to *Hoare triples* used in program logics for high-level languages. Because we work with a low-level machine (where code is located in memory), we distinguish between three different types of program specifications (8):

```

\langle P \rangle \rightarrow \langle s, Q \rangle single instruction

\{P\} \leadsto \{s, Q\} code fragment

\{P\} \leadsto \bullet complete safe execution.

```

In each case, P are Q are separation logic assertions describing the state of the machine (registers and memory). P corresponds to a pre-condition, Q a post-condition, and s binds in Q the corresponding execution state (of type ExecState, see Figure 5).

Informally,  $\langle P \rangle \to \langle s,Q \rangle$  holds if, starting from a machine state satisfying P, the machine can execute one step of computation, and reach a state satisfying Q in an execution state s. The predicate  $\{P\} \leadsto \{s,Q\}$  holds if, starting from a state satisfying P, then the machine can diverge (i.e. loop) or reach a state satisfying Q in an execution state s. This is typically used to describe the execution of a code fragment. Finally,  $\{P\} \leadsto \bullet$  holds if, starting from a machine state satisfying P, then the machine loops forever or runs until completion, ending in either a Halted or Failed state. In this case, we say that the initial configuration described by P is safe. (Not every configuration is safe: the resources in P describing registers and memory must suffice for the machine to run and execute the code pointed to by pc: for example,  $\{pc \mapsto (RX, a, a+2, a) * a \mapsto mov r_1 z * a + 1 \mapsto halt\} \leadsto \bullet$  cannot be established, since the precondition lacks a resource for  $r_1$ . The configuration where the register and memory maps are the partial maps as defined by the declared points-to assertions is thus not considered safe.)

Additionally, these three specifications *require the logical invariants to be preserved at every step of the execution*. This requirement is implicit in the definition of invariants, but it is a crucial reasoning principle that we will leverage.

Echoing back to Section 2.2, note that our program specification for a complete safe execution allows the program to fail (or diverge). Indeed, we will capture the preservation of security properties by preserving *invariants* throughout execution and having the machine fail is both fine (invariants are trivially preserved when the machine ends up in a failure state) and unavoidable (we cannot prevent unknown code from triggering a capability check failure). Similar considerations apply for divergence.

*Notations.* In the rest of the paper, we will rely on a couple of additional notations when writing program specifications. Because we often want to reason about the case where an instruction (or program fragment) does not fail, we write  $\langle P \rangle \rightarrow \langle Q \rangle$  (respectively  $\{P\} \rightsquigarrow \{Q\}$ ) to denote a resulting execution state equal to Running:

$$\begin{array}{cccc} \langle P \rangle \to \langle Q \rangle & \triangleq & \langle P \rangle \to \langle s. \, \lceil s = \text{Running} \, \rceil * \, Q \rangle \\ \{P\} \leftrightsquigarrow \{Q\} & \triangleq & \{P\} \leftrightsquigarrow \{s. \, \lceil s = \text{Running} \, \rceil * \, Q \} \, . \end{array}$$

When writing pre- and post-conditions, we will often need to include a points-to resource describing the contents of the pc register. We introduce a short-hand notation for that purpose, and write w; P to assert P and additionally that pc is set to w:

$$w: P \triangleq pc \Longrightarrow w * P$$

Using these two notations, the specification for a single instruction, in a case where it does not fail, is written as  $\langle w_0; P \rangle \rightarrow \langle w_1; Q \rangle$  (typically, we have  $w_1 = w_0 + 1$ , except in the case of the jmp and jnz instructions, or when explicitly writing to the pc register).

*Properties.* Our program specifications satisfy the well-known "frame rule" of separation logic, which permits local reasoning, and asserts that it is always possible to extend a specification by adding arbitrary resources not accessed by the program.

Program specifications can also be composed using sequencing rules. In order to establish a specification of the form  $\{P\} \leadsto \{s. Q\}$ , one typically uses single-instructions rules  $(\langle R \rangle \to \langle s. S \rangle)$

in a sequence, one for each instruction of the relevant code block. Specifications for two program fragments that follow each other can also be combined to obtain a specification for the sequence of the two fragments. We prove general sequencing rules for our three kind of specifications; for simplicity, we only reproduce here restricted rules that deal with successful executions (relying on the notations introduced before):

When reasoning about a single execution step, one can additionally access resources held in known invariants. This is done using the INV rule, given below: <sup>3</sup>

$$\frac{\langle P * \triangleright R \rangle \longrightarrow \langle s. \, Q * \triangleright R \rangle}{\boxed{R} \vdash \langle P \rangle \longrightarrow \langle s. \, Q \rangle}$$

Example specifications. As illustrative examples, Figure 8 shows specifications for the subseg, load and store instructions, as well as the rclear macro which is used to clear the contents of a number of specified registers. The first rule shows a specification for the subseg instruction (0). It states that if the program counter contains a capability pointing to a memory location  $a_{pc}$ , if that location contains an integer n which decodes into subseg r  $z_1$   $z_2$ , and if the register r contains a capability, then assuming that the program counter is valid (ValidPC(...)) and that  $z_1$  and  $z_2$  are valid new bounds (ValidSubseg(...)), the machine successfully increments the program counter and restricts the capability held in register r with new bounds  $z_1$  and  $z_2$ .

The second rule is also a specification for subseg, but in a case where it fails a bound check, i.e. ValidSubseg(p, b, e,  $z_1$ ,  $z_2$ ) does not hold  $\bigcirc$ . (For instance, when the new bounds  $z_1$  and  $z_2$  would allow accessing more memory than what is available through the original capability.) Then, the rule does give us a specification for an execution step, but with a resulting execution state of Failed, meaning that the execution cannot continue afterwards.

The third and fourth rules give specifications for the load and store instructions (in non-failing cases) (12) (13). The specification for load states that load *dst src* loads a word from memory pointed to by a capability in register *src* and stores its contents in register *dst*. The specification for store states that store *dst src* reads a word from the *src* register and writes it into the memory location pointed to by the capability in *dst*.

Note that these specifications for subseg, load and store are not in fact the most general specifications for these instructions. They assume that some side-conditions hold, and specify the behavior of the instruction in the case of either a "normal" successful execution, or a failing one. These specifications are typically useful for reasoning about the correctness of a concrete program. We have also proved in Coq (e.g., 14) for the subseg instruction) "most general" specifications, covering in one lemma all possible cases for a given instructions. These are useful for deriving the more specific rules shown previously. Furthermore, we use them directly in the proof of the

$<sup>^{3}</sup>$ For clarity of the presentation, we choose to omit additional details related to Iris invariant namespaces and masks. We refer to the Coq development for the full details (9).

```

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*r \mapsto (p,b,e,a) \rangle \rightarrow \langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*r \mapsto (p,b,e,a) \rangle \rightarrow \langle (p_{pc},b_{pc},e_{pc},a_{pc}+1); \quad a_{pc} \mapsto n*r \mapsto (p,z_1,z_2,a) \rangle }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*r \mapsto (p,b,e,a) \rangle \rightarrow \langle s. \ [s = \text{Failed}] * ((p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*r \mapsto (p,b,e,a) \rangle \rightarrow \langle s. \ [s = \text{Failed}] * ((p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*r \mapsto (p,b,e,a) \rangle }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto -*src \mapsto (p,b,e,a) * a \mapsto w \rangle \rightarrow \langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto w*src \mapsto (p,b,e,a) * a \mapsto w \rangle }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto w*src \mapsto (p,b,e,a) * a \mapsto w \rangle }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto w*src \mapsto (p,b,e,a) * a \mapsto w \rangle }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } } {\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } } {\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } } } {\langle (p_{pc},b_{pc},e_{pc},a_{pc}); \quad a_{pc} \mapsto n*dst \mapsto (p,b,e,a) * src \mapsto w*a \mapsto -\rangle } }

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc})} \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{pc},a_{pc})}

\frac{\text{ValidPC}(p_{pc},b_{pc},e_{pc},a_{pc})}{\langle (p_{pc},b_{pc},e_{pc},a_{pc})} \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{pc},a_{pc}) \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{pc},a_{pc}) \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{pc},a_{pc}) \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{pc},a_{pc}) \Rightarrow \text{ValidPc}(p_{pc},b_{pc},e_{p

```

Fig. 8. Specifications for the machine instructions subseg, load and store and for the rclear macro that sets a given list of registers to zero. Changes to the machine state are highlighted in red.

Fundamental Theorem (Theorem 2), for specifying the behavior of arbitrary instructions that might or might not fail.

The last rule of Figure 8 shows a derivable specification for a program composed of several instructions, the rclear macro  $\bigcirc$ 5. This macro (meaning, a small program that is typically inserted inline as part of a larger program) clears a number of registers by setting their content to 0. It is parameterized by a list l of register names, and its code consists of a sequence of instructions move r 0 for each register name r in l. We state rclear's specification using the program specification for code fragments. This specification is provable using the basic reasoning rules for move. It requires that the body of the macro ("rclear\_instrs l") is laid out contiguously in memory range [a, a + n), while the program counter initially points to a. When the program counter eventually points to a + n, the address immediately after the macro's instructions, then all the registers in l have been cleared and now contain 0. (The "big star"  $\bigstar$  denotes an iterated separating conjunction, here over the registers r in list l.)

#### 4.3 Adequacy theorem

After establishing program specifications and properties at the level of our program logic, we ultimately want to transfer these results into properties of a program execution at the level of the

operational semantics of the bare machine. Generally speaking, we prove using the rules of the Iris logic a statement of the form  $P \vdash Q$ , where P and Q are Iris propositions (read "Q holds assuming invariant P"). From this, we want to deduce that some mathematical proposition  $\Phi$  holds (as a Coq proposition, in our case), where  $\Phi$  describes some property of the machine execution expressed in terms of its operational semantics.

Because we are interested in establishing *invariants* about a program execution, we typically want to obtain in  $\Phi$  that at every step of the execution, the state of the machine satisfies an invariant corresponding to the Iris assertion P.