## EMI Mitigation of GaN Power Inverter Leg by Local Shielding Techniques

Pawel B Derkacz, Jean-Luc Schanen, Pierre-Olivier Jeannin, Piotr J Chrzan, Piotr Musznicki, Mickael Petit

### ▶ To cite this version:

Pawel B Derkacz, Jean-Luc Schanen, Pierre-Olivier Jeannin, Piotr J Chrzan, Piotr Musznicki, et al.. EMI Mitigation of GaN Power Inverter Leg by Local Shielding Techniques. IEEE Transactions on Power Electronics, 2022, 37 (10), pp.11996-12004. 10.1109/TPEL.2022.3176943. hal-03816337

HAL Id: hal-03816337

https://hal.science/hal-03816337

Submitted on 16 Oct 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# EMI Mitigation of GaN Power Inverter Leg by Local Shielding Techniques

Pawel B. Derkacz , *Student Member, IEEE*, Jean-Luc Schanen , *Senior Member, IEEE*, Pierre-Olivier Jeannin , Piotr J. Chrzan , *Senior Member, IEEE*, Piotr Musznicki , and Mickaël Petit ,

Abstract—This article presents local shielding techniques applied to a half-bridge inverter leg with the aim to reduce the common-mode (CM) current noise at converter's dc input. The research study is conducted for 650-V enhancement mode Gallium Nitride power transistor switches. Main contributors of parasitic capacitances referred to the inverter-leg middle point node are identified. Then, shielding solutions are proposed to reduce the CM current emission by these capacitances. Respecting the precautions concerning the isolation of CM currents of the half-bridge inverter leg, the electromagnetic compatibility measurement setup is developed. Experimental step-by-step addition of local shielding copper layers to different contributors of middle point capacitance shows progressive attenuation of CM noise spectra.

Index Terms—Common-mode (CM) current, electromagnetic compatibility (EMC), electromagnetic interference (EMI) mitigation, electrostatic shielding, Gallium Nitride (GaN) power transistor, half-bridge inverter, switching cell.

#### I. INTRODUCTION

ROGRESSIVE employment of Gallium Nitride (GaN)-based transistors in power electronics converters reveals their advantages of higher switching frequency, and improved the efficiency and power density [1], [2]. However, a high switching speed of power devices in a range of few nanoseconds results in extremely high  $\mathrm{d}v/\mathrm{d}t$  (over 100 V/ns) of the associated voltage waveforms across power switches or between dynamically changing circuit nodes potentials and the ground. These phenomena induce severe common-mode (CM) electromagnetic

Manuscript received December 14, 2021; revised March 12, 2022 and April 15, 2022; accepted May 13, 2022. Date of publication May 23, 2022; date of current version June 24, 2022. This work was supported by the French national program "Programme d'investissements d'Avenir, IRT Nanoelec" ANR-I0-AIRT-05. Recommended for publication by Associate Editor M. Hartmann. (Corresponding author: Piotr Musznicki.)

Pawel B. Derkacz is with the Université Grenoble Alpes, CNRS, F-38000 Grenoble, France, and also with the Faculty of Electrical and Control Engineering, Gdańsk University of Technology, 80-233 Gdańsk, Poland (e-mail: pawel.derkacz@pg.edu.pl).

Jean-Luc Schanen and Pierre-Olivier Jeannin are with the Université Grenoble Alpes, CNRS, F-38000 Grenoble, France (e-mail: jean-luc.schanen@grenoble-inp.fr; pierre-olivier.jeannin@g2elab.grenoble-inp.fr).

Piotr J. Chrzan and Piotr Musznicki are with the Faculty of Electrical and Control Engineering, Gdańsk University of Technology, 80-233 Gdańsk, Poland (e-mail: pchrzan@pg.edu.pl; piotr.musznicki@pg.edu.pl).

Mickaël Petit is with the SATIE—CNRS UMR 802, ENS Cachan, National Conservatory of Arts and Crafts (CNAM), 75003 Paris, France (e-mail: mickael.petit@satie.ens-cachan.fr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2022.3176943.

Digital Object Identifier 10.1109/TPEL.2022.3176943

interference (EMI) in the form of conducted and radiated emissions. To minimize their impact on converter operation, different precautions have to be taken at early stages of the power and gate circuits layout design.

Since the stray inductance in the commutation loop has a significant impact on the level of EMI, many papers propose optimization of the printed circuit board (PCB). In [3], the power loop parasitic inductance and the device package common source inductance have been shown to be critical for the performance and efficiency of synchronous buck converter operation. However, low-inductance commutation loops overlapping the bus-bar planes and gate drive tracks increase parasitic capacitances between dynamically changing circuit nodes and the ground. At power switching instants with high dv/dt, they cause that the CM current circulation paths deteriorate the reliability of converter operation [4], [5]. In order to optimize this design tradeoff, diverse integration technologies of GaN power module assemblies were extensively investigated: encapsulation of switching cell in package [6], gate drive circuit integration [7], and 3-D packages for the inverter leg [8].

Other solutions are based on improving the control and modulation strategy or filtering. Attempts to attenuate the CM current noise triggered a number of research efforts: soft-switching converter topologies [9], [10], optimization of the EMI filter design [11], balanced switching circuits [12], passive component location with PCB layout optimization [13], or shielding-cancellation techniques in isolation transformer converters [14], [15]. However, since full cancellation of stray components is not physically possible, then the design objectives were oriented toward managing CM current circulation paths in the nearest proximity of the power switching cell [16]. Thus, the resulting CM current flowing outside the converter in the line impedance stabilization network (LISN) could be reduced. Furthermore, requirements for the EMI input filter design could be progressively reduced in both complexity and volume.

The approved and effective ways to reduce the CM noise include electrostatic shielding techniques that are integrated in a multiconductor circuit layout [17]. In this way, stray capacitances between shielded nodes and the ground are split to enable CM current to recycle around the perturbation source via low impedance of the conductive plane. Previous solutions based on shielding the pulsating node of a boost converter by means of bipolar output voltage tracks for a two-layer PCB were described in [18]. The technique proposed in [19] added a conductive shielding plane between or under tracks and the ground plane.

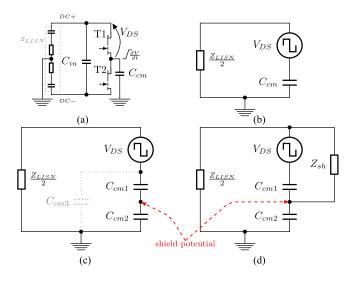

Fig. 1. Lumped CM models of PCB track shielding. (a) Generic circuit of the inverter leg. (b) Unshielded. (c) Conductive shielded plane floating. (d) Conductive shielded plane with bus-bar connection.

In a similar way to diverting the noise back to the dc bus, a method of two stacked direct-bonded-copper (DBC) substrates was proposed in [20].

In this article, another shielding solutions are applied to the inverter leg middle track, the gate driver power supplies, and the power switch cooling pads by connecting conductive shielding layers with bus bars. Thus, the resulting arrangement of parasitic capacitances is changed. Based on the half-bridge inverter topology, the main objective this article is to prove quantitatively the shielding effectiveness by measuring the reduction of CM current spectra at the LISN inverter dc input.

This article is organized as follows. Section II briefly introduces the electrostatic shielding concept of the PCB track. Next, in Section III, the demonstrator board of a half-bridge inverter switching cell is described with focus on the electromagnetic compatibility (EMC) measurement setup. The proposed shielding techniques applied step-by-step to the tested converter are presented in Section IV, and the corresponding experimental CM current attenuation spectra in Section V. Finally, Section VI concludes this article.

#### II. SHIELDING CONCEPT

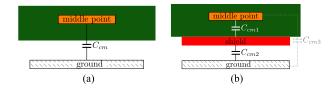

Fig. 1(a) illustrates the basic phenomenon involved in CM generation: the switching cell generates a high  $\mathrm{d}v/\mathrm{d}t$  slope that excites the CM current flow through parasitic capacitance  $C_{\mathrm{cm}}$ , due to natural existence of grounded elements such as metal enclosure, copper/aluminum heat sink, etc., nearby PCB tracks. The LISN is used to close the CM current circulation path and to provide stable input impedance. This action can be represented by a simplified model [see Fig. 1(b)] using the voltage source  $V_{\mathrm{DS}}$ , and the LISN impedance  $Z_{\mathrm{LISN}}/2$  in CM to close the loop. Using a conductive shielding foil between the floating point of the switching leg and the ground (see Fig. 2) changes the distribution of stray capacitances, as illustrated in Fig. 1(c). Three capacitances can be distinguished:  $C_{\mathrm{cm1}}$ ,  $C_{\mathrm{cm2}}$ ,

Fig. 2. Geometrical presentation of the PCB middle point track with stray capacitances. (a) Unshielded. (b) Shielded.

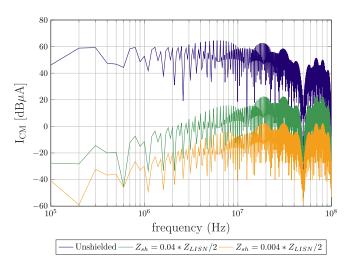

Fig. 3. CM current spectra for different shielding conditions: unshielded referring to Fig. 1(b), and two  $Z_{\rm sh}$  values referring to Fig. 1(d).

$C_{\rm cm3}$ . The capacitances  $C_{\rm cm1}$  and  $C_{\rm cm2}$  come from the capacitive divider and depend on the distance between the shield-ground and shield-track nodes. Their series association is equal to the initial capacitance  $C_{\rm cm}$  of the unshielded case. The parasitic capacitance  $C_{\rm cm3}$  represents the remaining capacitance between the floating point and the ground, which is not exactly equal to zero, due to misalignment of the shield (e.g., when the shield area does not fully cover of the track) and some edge effects. In the case of perfect alignment of shield and middle point areas, the capacitance  $C_{\rm cm3}$  can be neglected.

Hence, the use of the shield according to Fig. 1(c) will not be effective if there is no connection of the shield potential to other potentials of PCB tracks (due to no alternative path for the CM current). In [19], the authors have introduced this type of shield along a wide area of PCB as results of which alternative paths have been created through stray capacitances of other tracks. However, this approach provides paths with high impedance, which results in poor effectiveness of the shield. Based on these considerations, a shield is proposed as a low conductive plane impedance ( $Z_{\rm sh}$ ) connected to the stable potential – positive busbar track of the converter [see Fig. 1(d)].

In the idealized circuit of Fig. 1(d), the CM current  $I_{\rm cm}$  splits into two branches: one flowing through  $C_{\rm cm2}$  and the ground to LISN, and the other circulating through the inserted shielding  $(Z_{\rm sh})$ . The ratio between these two currents corresponds to the impedance ratio of the two branches. The simulation of circuits in Fig. 1(b) and (d) was performed using Saber@Sketch simulator to compare the LISN CM current spectra without shielding and with shielding for two values of shielding impedance  $1\Omega$  (4%

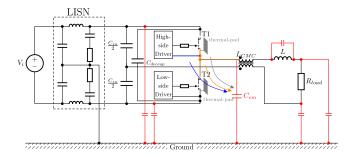

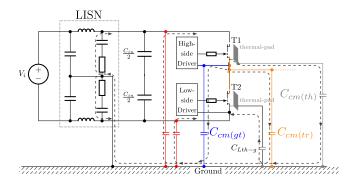

Fig. 4. Half-bridge inverter in the laboratory setup with stray capacitances location.

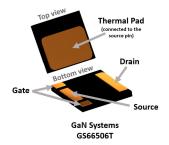

Fig. 5. Description of the GaN package.

of  $Z_{\rm LISN}/2$ ) and  $0.1\Omega$  (0.4% of  $Z_{\rm LISN}/2$ ), where  $Z_{\rm LISN}/2$  for CM was equal to  $25\Omega$ . The  $V_{\rm DS}$  waveform of voltage was trapezoidal with 20-V/ns slope corresponding to the experimental  ${\rm d}v/{\rm d}t$  in this article; see Fig. 6. The preformed simulation results (see Fig. 3) confirm significant CM noise mitigation, up to 70 dB, for the low-impedance conductive shielding plane.

This section has illustrated the basic shielding principle of the CM current, with the shield being connected to a stable potential with low impedance, to facilitate internal recirculation of the CM current. The following section will describe the GaN switching cell to which the aforementioned concept was applied.

#### III. DEMONSTRATOR SYSTEM DESCRIPTION

#### A. Half-Bridge Inverter Description

A half-bridge inverter switching cell (see Fig. 4) is used to investigate CM stray capacitances and the impact of shielding techniques on modification of CM current paths. The inverter is fed from a dc voltage source ( $V_i$ =250 V) through the LISN. Two input capacitors  $C_{\rm in}/2$  split the dc-link voltage  $V_i$  to create a 0-V midpoint connection for the load. The inverter feeds the resistive load  $R_{\rm load}$  via an inductive output filter L=15  $\mu$ H. To attenuate the CM current circulation path through the load circuit, a CM filter choke  $L_{\rm CMC}$ =705  $\mu$ H with coupling factor k=0.99675 and differential inductance of 3.4  $\mu$ H is installed between the inverter output terminals and the filter.

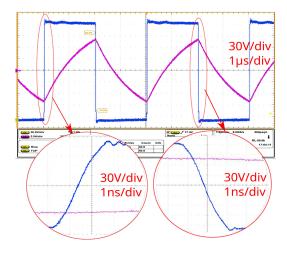

The inverter is switched at 250 kHz. The global waveforms of load voltage and current are depicted in Fig. 6. Due to the resistive-inductive load, all four consecutive conduction states of the half-bridge inverter at rectangular voltage operation mode are obtained. The zoom of the voltage waveform at turn OFF in Fig. 6 shows a reduced voltage overshoot, which validates the

Fig. 6. Inverter voltage and current waveforms.

inverter circuit design layout by minimizing the stray inductance (see Section III-B).

#### B. PCB Layout Design

The inverter demonstrator was designed using a four-layer PCB. It is composed of: positive (dc+) and negative (dc-) power bus bars, two series-connected electrolytic capacitors  $C_{\rm in}/2$ , T1–T2 inverter leg, decoupling capacitors  $C_{\rm decoup}$ , and CM filter choke  $L_{\rm CMC}$ .

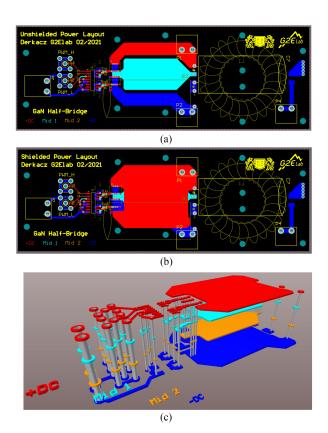

The enhancement mode GaN power transistors (GS66506 T) T1 and T2 are used in the inverter leg. Since GaN HEMT transistors have reverse conduction capability, the synchronous operation of the inverter leg is obtained without freewheeling diodes. The transistors are top-side cooled: they possess thermal pads internally connected with the source terminal and substrate (see Fig. 5). A planar 2-D placement of power switches [8] has been chosen where both transistors are soldered at the top of the PCB. Owing to top-side cooling devices, heat dissipation is easily realized by the heat sink mounted directly on both devices. In further consideration, the heat sink potential is assumed as the ground. Its location is crucial for CM noise generation. In detail, the source potential of the high-side switch (T1) is connected to its thermal pad located close to the grounded heat sink. It increases the total CM stray capacitance  $C_{\mathrm{cm}}$  of the inverter's middle point. To reduce the power loop, decoupling capacitors have been placed directly beneath the transistors, on the bottom side of the PCB. Also, the layout of the dc+ and dc- tracks (bus bars) has been designed such as to provide a symmetrical and as-short-as-possible power loop (see Fig. 7). Close to the transistor gate terminals is placed a half-bridge driver with two isolated channels for top and bottom transistor control. The gate circuit consists of two branches with resistors  $R_{\rm on}$  and  $R_{\rm off}$  and diode  $D_{\rm off}$  to separately tune the speed of transients. The isolated secondary sides of the driver are supplied from a separate PCB, mounted perpendicular to the main board to reduce the impact of parasitic capacitances of the power supply circuit on the CM current generation. Particular consideration has been taken to the layout of the inverter middle point track, which is forced to

Fig. 7. View of the demonstrator with middle track. (a) Unshielded. (b) Shielded. (c) Exploded 3-D view of shielded PCB: Sandwich between dc+, middle point, and dc- as described in Section IV-A, (thickness of the board in scale 10:1) (colors: Red—Top Layer, Blue—Bottom Layer, and Yellow and Cyan—Middle Layers).

change dynamically the voltage during inverter operation. The layout of this track was designed using the two middle layers of PCB (Yellow and Cyan layers in Fig. 7) with the same tracks' geometry connected by vias to increase the current capability of the converter. The size of this track was intentionally increased to obtain the values of track stray capacitances comparable with the capacitance between the GaN transistor thermal pad and the ground (see Fig. 7).

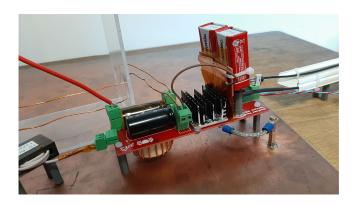

#### C. Test Setup for Conducted EMI Measurement

To perform the comparative study of shielding effectiveness, a dedicated setup for conducted EMI measurements has been built (see Fig. 8). In this test bench, the converter is supplied from an external power source through a CISPR-16 compliant LISN. The gate transistor drivers are fed by two 9-V batteries (see Fig. 9). The CM current is captured on a spectrum analyzer with a current probe including both plus and minus wires between the LISN and the converter input. To provide clean and fully repeatable measurements, several precautions have been introduced, which are as follows:

- 1) The converter board and the output filter have fixed position and distance to the ground (2.5 cm above the copper ground plane) (see Fig. 8).

- 2) Power and signal wires are mounted on dedicated stands with fixed position and distance to the ground (2.5 cm).

Fig. 8. EMC measurement setup with introduced all precautions.

Fig. 9. Zoom on converter with driver fed by two 9-V batteries, and output inductance on the left ( $L_{\rm CMC}$  is on the bottom side of the PCB).

- 3) All unnecessary equipment (auxiliary power supplies, signal generator, oscilloscope, etc.) are moved out of the table (far from the ground area) to mitigate stray capacitances and to avoid unknown CM paths.

- 4) As mentioned earlier, a CM Choke is placed between the middle point of the inverter and the output inductor. Its aim is to significantly increase the CM impedance path through the load, and therefore, to prevent flowing of the CM current in this direction;

- 5) The resistive load is built from discrete parts in a TO-247 package mounted on the aluminum heat sink. This set is placed perpendicularly 40 cm above the ground plane to reduce stray CM capacitance of the load.

- 6) A dedicated stand with wires and spot for the current probe is used between the LISN and the converter input to provide the same conditions and position of the measurement device.

## IV. SHIELDING OF THE THREE MAIN CM CAPACITANCE CONTRIBUTORS

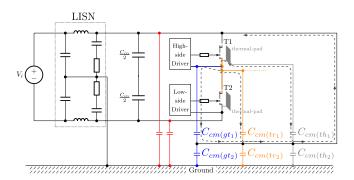

CM noise generation in inverters is mainly related to the existence of parasitic capacitance between the inverter leg midpoint and the ground. A systematic experimental study of a half-bridge inverter leg based on the lateral GaN HEMT structure has indicated three main contributors of CM capacitance: middle point PCB track to ground, thermal pad of the top switch (T1)

Fig. 10. CM stray capacitances and current circulation paths of the unshielded converter.

Fig. 11. CM stray capacitances and CM current paths (recirculation) for the shielded converter (shielded: Middle point track, thermal pad, gate supply circuit).

to ground, and gate circuit of the top switch (T1) to ground (see Fig. 10). All these three parts are connected to the point with high  $\mathrm{d}v/\mathrm{d}t$ , and each of them increases the area of this point (by copper tracks), thus resulting in the increased stray capacitance to ground. The application of shielding techniques, as described in details in next paragraphs, provides new paths for the CM current to recirculate inside the converter (see Fig. 11), which leads to the reduction of the CM noise.

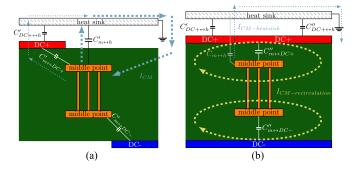

#### A. Inverter Middle Track Shielding

The middle point track (power part) shielding by the conductive local plane is realized by extending the surface of the dc+ and dc- bus-bars planes. These planes are acting as a shield, as referred to in Section II, and overlapping the middle point track in 92.55% of the area for shielded layout [see Fig. 7(b)]. For comparison, only 2.14% of the middle point area is overlapped for the unshielded layout [see Fig. 7(a)]. For the unshielded version shown in Fig. 12(a), the CM current flows mainly through the capacitance between the middle track and the heat sink. The capacitance  $C_{\rm cm}$  (as in Fig. 2) is approximately equal to  $C'_{\rm m\leftrightarrow h}$ [see Fig. 12(a)], since the capacitances  $C'_{m\leftrightarrow DC+}$  and  $C'_{m\leftrightarrow DC-}$ between the middle track and dc+ and between the middle track and dc-, respectively, are relatively small (see Table I). It is noteworthy that in the unshielded version, the capacitance  $C'_{\mathrm{DC}+\leftrightarrow \mathrm{h}}$  between dc+ and heat sink has a significant value, but it is series connected with small  $C'_{m \leftrightarrow DC+}$ , and therefore, can be neglected as a component of capacitance  $C_{\rm cm}$ . Additionally, this

Fig. 12. Stray capacitance distribution in the PCB cross section. (a) Unshielded. (b) Shielded middle track.

TABLE I STRAY CAPACITANCE VALUES FOR UNSHIELDED AND SHIELDED MIDDLE POINT TRACK

| Capacitance           | Value [pF] |  |  |  |

|-----------------------|------------|--|--|--|

| Unshielded (Fig. 12a) |            |  |  |  |

| C' <sub>m↔h</sub>     | 5.8        |  |  |  |

| C' <sub>DC+↔h</sub>   | 3.7        |  |  |  |

| C' <sub>m↔DC+</sub>   | 1.09       |  |  |  |

| C' <sub>m↔DC-</sub>   | 0.9        |  |  |  |

| Shielded (Fig. 12b)   |            |  |  |  |

| C" <sub>m↔h</sub>     | 0.56       |  |  |  |

| C" <sub>DC+↔h</sub>   | 10.3       |  |  |  |

| C" <sub>m↔DC+</sub>   | 33.7       |  |  |  |

| C" <sub>m↔DC-</sub>   | 33.6       |  |  |  |

capacitance is not connected to a floating point but to a stable potential. Therefore, it does not contribute to CM generation, but rather to CM internal recycling.

When shielding is applied, the extended surfaces of dc+ and dc- bus bars [see Fig. 12(b)] increase the capacitances between the bus bars and the middle track, which affects the switching speed [described in Section V-A]. The capacitance  $C'_{\mathrm{DC}+\leftrightarrow\mathrm{h}}$  between dc+ and the heat sink is increased by the parallel-connected capacitance C' $_{\mathrm{DC}+\leftrightarrow\mathrm{h}}$ . The CM current  $I_{\mathrm{cm}}$ flows through the capacitance  $C''_{m\leftrightarrow DC+}$ . At the dc+ node,  $I_{cm}$ splits in two parts: the -first component recirculates within the switching cell through low impedance of the shield and the dc+ tracks, while the -second component flows through capacitance  $C'_{\mathrm{DC}+\leftrightarrow \mathrm{h}}$  +  $C''_{\mathrm{DC}+\leftrightarrow \mathrm{h}}$  to the heat sink. Since the value of  $C''_{\text{m}\leftrightarrow\text{DC}+}$  is much larger than that of  $C'_{\text{DC}+\leftrightarrow\text{h}} + C''_{\text{DC}+\leftrightarrow\text{h}}$ , a proportionally smaller current flows to the heat sink. Most of the  $I_{\rm cm}$  current recirculates inside the switching cell according to (1) (with a given value of C" $_{DC+\leftrightarrow h}$  and the assumption that  $Z_{\rm sh}=0.1\Omega$ ).

At 150 kHz,  $I_{\rm cm-heatsink} = 0.00000097 \cdot I_{\rm cm-recirculation}$ . At 30 MHz,  $I_{\rm cm-heatsink} = 0.00019 \cdot I_{\rm cm-recirculation}$ .

$$\frac{I_{\rm cm-heatsink}}{I_{\rm cm-recirculation}} = \frac{Z_{\rm sh}}{\frac{Z_{\rm LISN}}{2} + j\omega C_{\rm DC+\leftrightarrow h}''}. \tag{1}$$

#### B. GaN Thermal Pad Shielding—Lab Solution

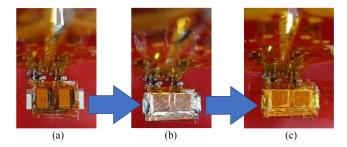

The next step of recirculating the  $I_{\rm cm}$  current in internal path is mounting the shielding layer between the thermal pad and the heat sink (see Fig. 13). This approach is a further extension of

Fig. 13. Thermal pad shield cross view.

Fig. 14. Stages of thermal pad shield application. (a) Placing first insulation layer on the thermal pad of GaN package. (b) Applying copper foil shield and soldering it to the bus bar.(c) Placing second insulation layer between shield and grounded heat sink.

the middle point shielding. However, its practical realization in this study had to be adapted to laboratory conditions. A copper foil was used as a conductive shield connected to the constant potential dc+. The isolation between the thermal pad and the shield, and between the shield and the heat sink was made using a Kapton insulator, as presented in Fig. 14. It ensured capacitive coupling between the transistors' thermal pads (source connected) and the dc+ bus bar, which resulted in increasing the total  $C_{\rm cm}$  capacitance but also in providing an additional path for CM recirculation (as described in the previous paragraph). The application of the thermal pad shielding to the lower switch (T2) created an additional stray capacitance  $C_{L{\rm th}-g}$  (see Fig. 10), which increased the total dc- to ground stray capacitance and helped in CM current recirculation inside the GaN power inverter leg.

#### C. Shielding of Power Supply Boards for Gate Drivers

The isolated secondary sides of the gate driver are supplied from dedicated PCB boards. On these boards, 9-V batteries with voltage conditioning circuits are used as the voltage sources for each channel of the dual channel gate driver. To minimize the CM capacitance of these circuits to the reference ground plane, the boards are mounted perpendicularly to the main board [see Fig. 15(b)]. However, a grounded heat sink is still placed in the nearby of these boards, which increases the CM capacitance. As in the previous case, shielding can also be applied to this part of the converter. In laboratory conditions, similarly to the thermal pad, Kapton insulation and copper foil were used to create the shield, which was by short wire connected to the dc+ potential [see Fig. 15(a)].

Fig. 15. Gate driver power supply boards. (a) View with applied shielding. (b) Perpendicular installation of supply boards in the converter.

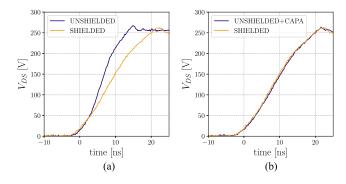

Fig. 16. Comparison of  $V_{\rm DS}$  slopes. (a) PCB with shielded (orange) and unshielded (blue) middle point. (b) PCB with shielded (orange) middle point and unshielded with additional lumped capacitors C=80 pF (blue).

#### V. EXPERIMENTAL RESULTS

#### A. Impact of Individual Shielding

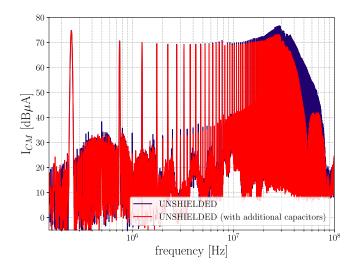

The laboratory measurement of  $I_{\rm cm}$  current was performed in four steps for progressive shielding application variants. The first variant represented the middle point track shielding being the result of introduction of additional parasitic capacitance parallel to the transistor internal capacitance  $C_{\mathrm{DS}}$ , which changed the rising time of  $V_{\rm DS}$  [see Fig. 16(a)]. To check the effectiveness of shielding, an additional capacitor C=80 pF was installed in the unshielded PCB between the drain and source transistors' nodes to get the voltage slopes the same in both cases, as presented in Fig. 16(b). The  $I_{\rm cm}$  spectra of unshielded PCB with additional capacitor and the PCB with unshielded middle point are compared in Fig. 17. Slight differences are noticed in the spectrum for frequencies above 15 MHz. Then, a significant difference is observed above 20 MHz, which depicts the impact of slope reduction on  $I_{\rm cm}$  generation. Adding 80 pF to the (unshielded) reference case allowed having the same dv/dt for comparison.

The  $I_{\rm cm}$  spectra for the unshielded PCB and with the shielded middle point track are compared in Fig. 18. It can be noticed that for PCB with shielded middle point track, the basic harmonic and its subharmonics are reduced by about 2–3 dB, while for

Fig. 17. CM current emissions of the unshielded middle point and unshielded with additional lumped capacitors.

Fig. 18. CM current emissions with and without shielded middle point track.

frequencies above 10 MHz, this reduction reaches 5.5 dB. Comparing these results with Fig. 17 proves that the reduction of  $I_{\rm cm}$  emission in the frequency range up to 20 MHz is caused by shielding the middle point track (and not due to  ${\rm d}v/{\rm d}t$  reduction, as the  ${\rm d}v/{\rm d}t$  values have been equalized with the 80 pF capacitance in the unshielded case).

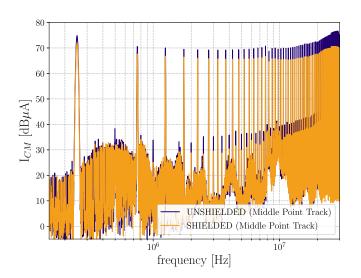

Further reduction of  $I_{\rm cm}$  can be obtained via shielding of the thermal pad. The effectiveness of the thermal pad shielding is demonstrated in Fig. 19 by comparing the spectrum of the shielded middle point track with that of the shielded middle point track and shielded thermal pad, (here, the orange spectrum from Fig. 18 is used as reference and plotted blue). The emission attenuation is observed in the whole frequency range, from 0.8 to 30 MHz, with the greatest diminution amounting to 7 dB.

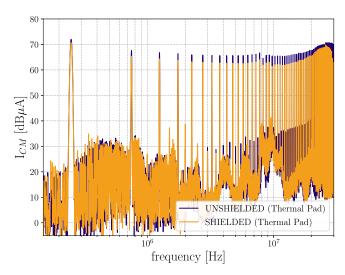

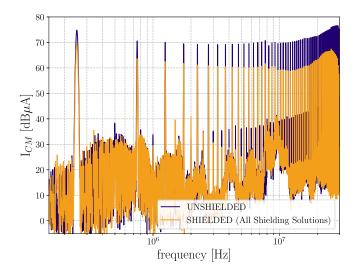

In the next step, shielding of the gate circuit power supplies was investigated. The copper foil was used to create a low conductive shield. As a result, successive decrease of  $I_{\rm cm}$  level by 2–5.5 dB was observed in the spectrum (see Fig. 20).

Fig. 19. Effectiveness of thermal pad shielding.

Fig. 20. Effectiveness of shielding of gate driver supplies.

TABLE II

COMPARISON OF CM NOISE LEVELS AT SPECIFIC FREQUENCIES (REDUCTION INDICATED IN BRACKETS)

| Specific frequency of spectrum | Unshielded<br>[dBµA] | Shielded:<br>middle point<br>[dBµA] | Shielded:<br>middle point<br>& thermal<br>pad<br>[dBµA] | Shielded: middle point & thermal pad & gate power supplies [dBµA] |

|--------------------------------|----------------------|-------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|

| 1.25MHz                        | 70.01                | 66.79 (-3.22)                       | 64.29 <b>(-5.72)</b>                                    | 62.43 ( <b>-7.58</b> )                                            |

| 10.025MHz                      | 69.72                | 65.36 ( <b>-4.36</b> )              | 61.95 (-7.77)                                           | 59.2 ( <b>-10.52</b> )                                            |

| 29.76MHz                       | 75.17                | 69.91 ( <b>-5.26</b> )              | 62.87 ( <b>-12.3</b> )                                  | 57.5 ( <b>-17.67</b> )                                            |

#### B. Total Shielding Effectiveness and Quantitative Data Comparison

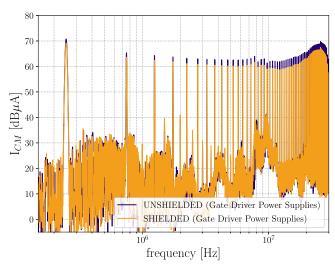

The comparison of the unshielded and totally shielded converters is presented in Fig. 21, where significant reduction of  $I_{\rm cm}$  noise is achieved in the whole investigated frequency range.

The comparison of quantitative data is presented in Table II. The noise levels for specific frequencies (beginning, middle,

Fig. 21. CM current emissions with and without total shielding solutions.

and the end of the conducted emission spectrum range) are put together. In this way, the impact of individual contributors of shielding can be compared. Moreover, the scale of reduction with respect to the unshielded version is given in Table II in brackets for each shielding step.

#### C. Discussion of EMC Versus Thermal Performances

The application of shielding by conductive copper layers increases parasitic capacitances between the drain and source terminals of switching transistors, thus introducing extra power switching losses.

The thermal pad shielding requires two layers of insulation. It doubles the thermal resistance from the case to the heat  $\operatorname{sink}(R_{\operatorname{th}(c-h)})$ , which is one of the disadvantages of this CM suppression method. The use of Kapton as insulation and thermal interface material, as presented in Section IV-B, is sufficient to verify the effectiveness of the thermal pad shielding. However, it does not present a commercial solution. The impact of doubling Kapton can be minimized in the designing step by the appliance of other materials. These constrains should be taken into account in the designing process and global optimization of the converter to achieve the tradeoff between CM current emission, power switching losses, and thermal performance [21].

#### VI. CONCLUSION

In this article, the proposed shielding technique is described and explained in detail. The new approach by shielding connecting to the positive or negative potential of the stable bus bar has been presented, simulated, and measured, and its effectiveness has been proved. Moreover, three different contributors of CM capacitance: middle point track, thermal pad, and gate circuit power supplies were extracted and highlighted. The shielding concept was successfully applied to each of them, which resulted in a total of over 17 dB reduction of the CM noise. In order to guarantee that the CM reduction is directly the effect of shield implementation, care has been taken to have the same  $\mathrm{d}v/\mathrm{d}t$  for the unshielded and shielded cases.

The proposed shielding solutions can be used in the embedded integration of power device dies in PCBs. Due to the obtained reduction of CM current noise, they can be essentials for wide band gap power devices. Resulting in weight and volume reduction of EMI filters, and does not impact the power density of the converter without a noticeable increase in additional copper layer weight.

#### ACKNOWLEDGMENT

The authors would like to thank the CEDMS of IUT Grenoble for their expertise, advice, and capabilities with PCB assembly and SMD technology.

#### REFERENCES

- L. C. M. Carrasco and A. J. Forsyth, "Energy analysis and performance evaluation of GaN cascode switches in an inverter leg configuration," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2015, pp. 2424–2431.

- [2] D. Reusch and J. Strydom, "Evaluation of gallium nitride transistors in high frequency resonant and soft-switching DC–DC converters," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 5151–5158, Sep. 2015.

- [3] D. Reusch and J. Strydom, "Understanding the effect of PCB layout on circuit performance in a high-frequency gallium-nitride-based point of load converter," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 2008– 2015, Apr. 2014.

- [4] J.-L. Schanen and P.-O. Jeannin, "Integration solutions for clean and safe switching of high speed devices," in *Proc. CIPS 10th Int. Conf. Integr. Power Electron. Syst.*, 2018, pp. 1–11.

- [5] E. Gurpinar, F. Iannuzzo, Y. Yang, A. Castellazzi, and F. Blaabjerg, "Design of low-inductance switching power cell for GaN HEMT based inverter," *IEEE Trans. Ind. Appl.*, vol. 54, no. 2, pp. 1592–1601, Mar./Apr. 2018.

- [6] E. Hoene, G. Deboy, C. R. Sullivan, and G. Hurley, "Outlook on developments in power devices and integration: Recent investigations and future requirements," *IEEE Power Electron. Mag.*, vol. 5, no. 1, pp. 28–36, 2018.

- [7] A. B. Jørgensen, S. Beczkowski, C. Uhrenfeldt, N. H. Petersen, S. Jørgensen, and S. Munk-Nielsen, "A fast-switching integrated full-bridge power module based on GaN eHEMT devices," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2494–2504, 2019.

- [8] P. B. Derkacz, J.-L. Schanen, P.-O. Jeannin, P. Musznicki, P. J. Chrzan, and M. Petit, "3D PCB package for GaN inverter leg with low EMC feature," in *Proc. 22nd Eur. Conf. Power Electron. Appl.*, 2020, pp. P.1–P.10.

- [9] M. Turzynski and P. J. Chrzan, "Reducing common-mode voltage and bearing currents in quasi-resonant DC-Link inverter," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9553–9562, Sep. 2020.

- [10] P. B. Derkacz, P. Musznicki, and P. J. Chrzan, "EMI attenuation in a DC–DC buck converter using GaN HEMT," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 4, pp. 4146–4152, Aug. 2021.

- [11] S. Jiang, Y. Liu, X. Ye, and X. Pan, "Design of a fully integrated EMI filter for a single-phase grid-connected inverter," *IEEE Trans. Ind. Electron.*, vol. 68, no. 12, pp. 12 296–12 309, Dec. 2021.

- [12] M. Shoyama, G. Li, and T. Ninomiya, "Balanced switching converter to reduce common-mode conducted noise," *IEEE Trans. Ind. Electron.*, vol. 50, no. 6, pp. 1095–1099, Dec. 2003.

- [13] J. Yao, S. Wang, and Z. Luo, "Radiated EMI reduction by layout improvement in power converters in automotive applications," in *Proc. IEEE 9th Int. Power Electron. Motion Control Conf.*, 2020, pp. 1894–1899.

- [14] L. Xie, X. Ruan, Q. Ji, and Z. Ye, "Shielding-cancelation technique for suppressing common-mode EMI in isolated power converters," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 2814–2822, May 2015.

- [15] C. Fei, Y. Yang, Q. Li, and F. C. Lee, "Shielding technique for planar matrix transformers to suppress common-mode EMI noise and improve efficiency," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1263–1272, Feb. 2018.

- [16] F. Costa, C. Gautier, E. Labouré, and B. Revol, Electromagnetic Compatibility in Power Electronics, London, U.K.: Wiley-ISTE, 2014.

- [17] J. Wang, R. Burgos, D. Boroyevich, J. Stewart, and Y. Xu, "Low impedance multiconductor layered bus structure with shielding," U.S. Patent 16/879078, Nov. 2020.

- [18] L. Rossetto, S. Buso, and G. Spiazzi, "Conducted EMI issues in a 600-W single-phase boost PFC design," *IEEE Trans. Ind. Appl.*, vol. 36, no. 2, pp. 578–585, Mar./Apr. 2000.

- [19] J. Aime, J. Roudet, C. Vollaire, P. Baudesson, and J. Ecrabey, "Layout techniques for reduction of common mode current in static converters," in *Proc. 41st Annu. Meeting IEEE Ind. Appl. Soc.*, 2006, vol. 5, pp. 2296– 2303.

- [20] A. I. Emon, M. U. Hassan, A. B. Mirza, Z. Yuan, and F. Luo, "EMI propagation path modeling of 3-level t-type NPC power module with stacked DBC enabled EMI shielding," *IEEE Energy Convers. Congr. Expo.*, 2021, pp. 5233–5239.

- Expo., 2021, pp. 5233–5239.

[21] Z. Yang et al., "Factors and considerations for modeling loss of a GAN-based inverter," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 3042–3052, Mar. 2021.