# Charge transport across Au-P3HT-Graphene Van der Waals vertical heterostructures

Jacopo Oswald, Davide Beretta, Michael Stiefel, Roman Furrer, Alessia Romio, Michel Daher Mansour, Dominique Vuillaume, Michel Calame

# ▶ To cite this version:

Jacopo Oswald, Davide Beretta, Michael Stiefel, Roman Furrer, Alessia Romio, et al.. Charge transport across Au-P3HT-Graphene Van der Waals vertical heterostructures. ACS Applied Materials & Interfaces, 2022, 14, pp.48240-48249. 10.1021/acsami.2c13148. hal-03797563v2

# HAL Id: hal-03797563 https://hal.science/hal-03797563v2

Submitted on 15 Oct 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

www.acsami.org Research Article

# Charge Transport Across Au-P3HT-Graphene van der Waals **Vertical Heterostructures**

Jacopo Oswald, Davide Beretta,\* Michael Stiefel, Roman Furrer, Alessia Romio, Michel Daher Mansour, Dominique Vuillaume, and Michel Calame\*

Cite This: https://doi.org/10.1021/acsami.2c13148

**ACCESS** I

Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Hybrid van der Waals heterostructures based on 2D materials and/or organic thin films are being evaluated as potential functional devices for a variety of applications. In this context, the graphene/organic semiconductor (Gr/OSC) heterostructure could represent the core element to build future vertical organic transistors based on two back-to-back Gr/OSC diodes sharing a common graphene sheet, which functions as the base electrode. However, the assessment of the Gr/OSC potential still requires a deeper understanding of the charge carrier transport across the interface as well as the development of wafer-scale fabrication methods. This work investigates the charge injection and transport across Au/OSC/Gr vertical heterostructures, focusing on poly(3-hexylthiophen-2,5-diyl) as the OSC, where the PMMA-free graphene layer functions as the top electrode. The structures are fabricated using a

combination of processes widely exploited in semiconductor manufacturing and therefore are suited for industrial upscaling. Temperature-dependent current-voltage measurements and impedance spectroscopy show that the charge transport across both device interfaces is injection-limited by thermionic emission at high bias, while it is space charge limited at low bias, and that the P3HT can be assumed fully depleted in the high bias regime. From the space charge limited model, the out-of-plane charge carrier mobility in P3HT is found to be equal to  $\mu \approx 2.8 \times 10^{-4}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, similar to the in-plane mobility reported in previous works, while the charge carrier density is  $N_0 \approx 1.16 \times 10^{15}$  cm<sup>-3</sup>, also in agreement with previously reported values. From the thermionic emission model, the energy barriers at the Gr/P3HT and Au/P3HT interfaces result in 0.30 eV and 0.25 eV, respectively. Based on the measured barriers heights, the energy band diagram of the vertical heterostructure is proposed under the hypothesis that P3HT is fully depleted.

KEYWORDS: organic, semiconductor, graphene, interface, transport, vertical, van der Waals

### INTRODUCTION

Hybrid van der Waals heterostructures based on 2D materials and/or organic thin films are being extensively studied<sup>1-3</sup> for a variety of applications encompassing field effect transistors, organic solar cells, 4-6 photodetectors, 7,8 vertical transistors, 9-14 and light emitting diodes. 15,16 Despite solid progress, developing a better understanding of the electron transport across hybrid van der Waals interfaces remains crucial to better control functionality and enhance performance. In this context, graphene is an excellent candidate as 2D electrode to contact organic thin films due to its inherent ability to form  $\pi - \pi$ stacking and van der Waals bonds.<sup>17</sup> Many studies to date aimed at unraveling the physical mechanisms behind charge injection at Gr/OSC interfaces for applications in diverse fields of micro- and nanoelectronics: 18-20 typically, graphene is used as the bottom electrode in barristors  $9^{-14}$  or transferred on top of an OSC film together with a protecting polymer, e.g., PMMA. However, other more complex multilayer designs could benefit from graphene full potential as monatomic thick, semitransparent, flexible and surface-conformal electrode. For instance, graphene could replace the base in vertical transistors, enabling organic transistors with nanoscale channels and higher operation frequencies that could meet the requirements of high-frequency applications, or function as interlayer electrode in OLEDs. <sup>21–24</sup> In this framework, the development of large-scale photolithographic fabrication methods compatible with hybrid architectures that exploit graphene as the top or interlayer electrode, and the understanding and modeling of the charge transport in the latter is crucial for the design and optimization of novel functional devices.

For this study, the authors developed a fabrication process for Au/P3HT/Gr hybrid VdW heterostructures, where PMMA-free graphene lies on top of a p-type OSC and

Received: July 22, 2022 Accepted: September 26, 2022

**ACS Applied Materials & Interfaces**

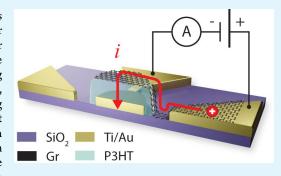

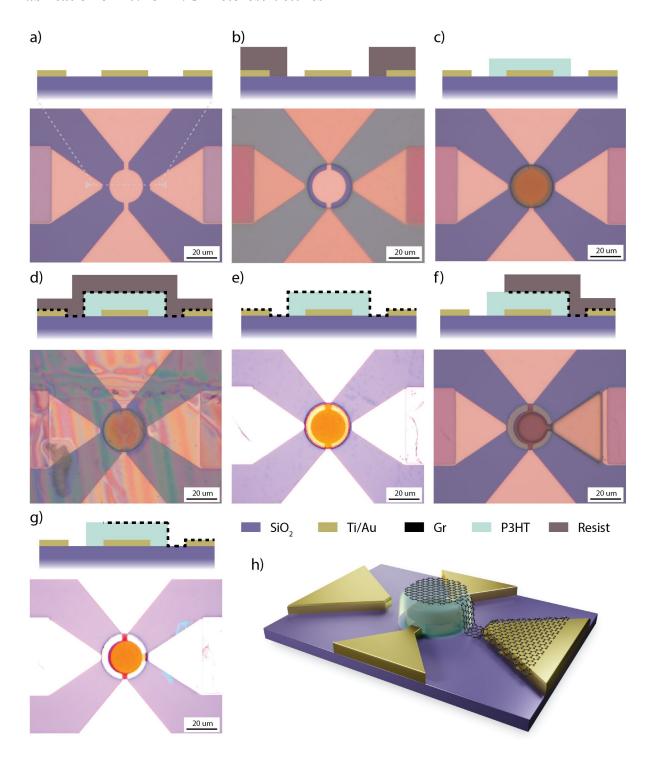

Figure 1. (a) 3D schematic of a representative Au/P3HT/Gr heterostructure (not to scale). (b) Schematic of the fabrication process. AFM (c) height and (d) phase images of a representative  $20 \,\mu m$  device. (e) SEM of a FIB cut cross-section of a representative Au/P3HT/Gr heterostructure in the center of the device. (f) Raman spectra of P3HT powder (blue line) and of a representative Au/P3HT/Gr device (dashed green line). The optical image shows the acquisition position of the spectra (the red scale bar is  $10 \,\mu m$ ). The inset shows the Raman spectra of a device graphene against the Raman spectrum of a representative CVD graphene on SiO<sub>2</sub>.

functions as the top electrode for the vertical stack, and investigated and modeled the charge injection across the two interfaces, i.e., Au/P3HT and P3HT/Gr, by temperature-dependent I-V measurements, impedance spectroscopy, and Kelvin probe force microscopy (KPFM). The charge transport across the device was found to be described by the thermionic emission (TE) assisted by image-charge induced barrier lowering model in the high voltage regime (|V| > 1 V) and by the space-charge limited (SCL) current model in the low voltage regime (|V| < 1 V). The models allowed us to extract the charge carrier concentration and the out-of-plane mobility of P3HT, and the reduced effective Richardson constant of and the potential barrier height at the two interfaces, ultimately

making it possible to sketch the energy band diagram of the whole stack.

### EXPERIMENTAL METHODS

**Materials.** Poly(3-hexylthiophene-2,5-diyl) (Regio-Regular (RR) > 99%,  $M_{\rm n}=27~000-45~000$ ) was purchased from Tokyo Chemicals and used as received to prepare solutions of 10 mg/mL in chlorobenzene. Graphene was grown in-house by chemical vapor deposition (CVD) on copper foils with a fully automated setup. The graphene growth protocol can be found in previously reported works.  $^{25-27}$

**Fabrication.** The study was conducted on a single chip including two different sets of devices: (i) Au/P3HT/Gr vertical stacks (119 devices) and (ii) graphene bridges (34 devices) (refer to Figure 1a

**ACS Applied Materials & Interfaces**

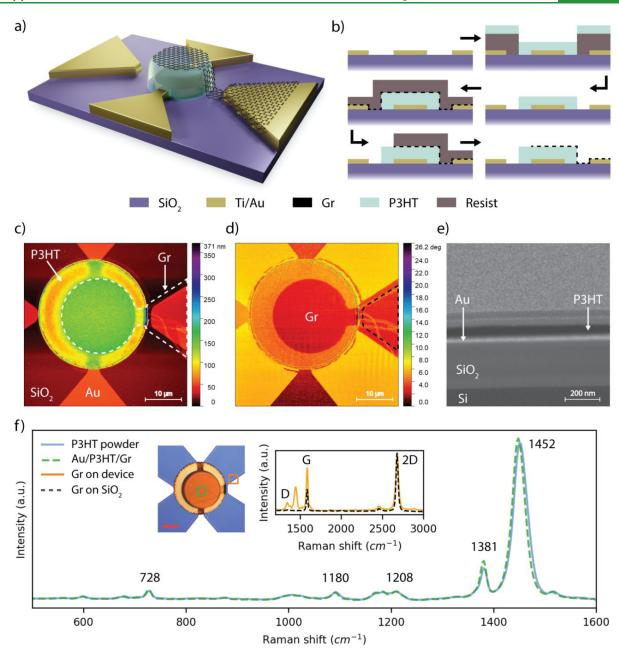

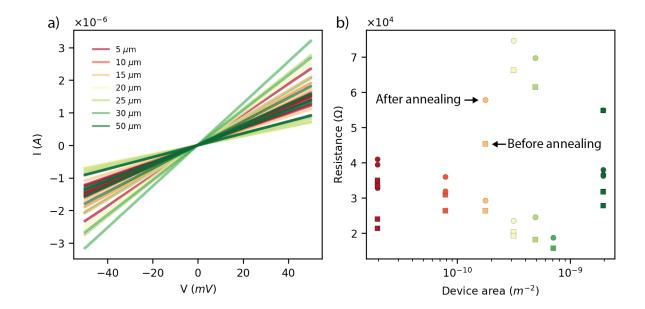

Figure 2. (a) Device schematics and electrical schemes of the Au/P3HT/Gr stack and of the graphene bridge devices.  $R_s$  is the graphene series resistance,  $R_s$  is the out-of-plane resistance, and  $R_s$  in vacuum and in vacuum after annealing (17 samples). The inset shows two representative I-V traces of side-contacted graphene. The resistance is calculated from the linear fit (dashed lines). (c) Current density of representative devices with diameter 5, 10, 15, 20, 25, 30, and 50  $\mu$ m. The inset shows the same traces on log scale. (d) Temperature-dependent I-V characteristic of a 5  $\mu$ m device from 200 to 300 K in steps of 5 K. The inset shows the Richardson plot for 5 V and I-I0 and I-I1 values.

and 2a for a schematic of the devices architecture). The chip was fabricated on a Si(525  $\mu$ m)/SiO<sub>2</sub>(300 nm) substrate at the Binnig and Rohrer Nanotechnology Center (BRNC) and EMPA. In both architectures, P3HT is sandwiched between a gold (bottom) and a graphene (top) circular electrode. In the bridge architecture, graphene is side-contacted so that one can force a current through it to evaluate its resistance independently from the underlying P3HT film (see Figure 2a for the electrical scheme). The chip includes devices having various nominal diameters, i.e. 5, 10, 15, 20, 25, 30, and 50  $\mu \mathrm{m}.$  The bottom gold electrodes are 2  $\mu$ m larger than the top graphene electrodes. The fabrication was done by photolithography under ambient conditions, as illustrated in Figure 1b and thoroughly described in the Supporting Information. Briefly, Au electrodes were deposited by e-beam physical vapor deposition (EBPVD) and patterned by lift-off. P3HT was then spin-coated at 1000 rpm for 60 s and patterned by lift-off. Finally, the CVD graphene top electrode was wet transferred and patterned by reactive ion etching (RIE).

**Electrical Characterization.** The electrical characterization at room temperature was done in the dark, in air, under vacuum ( $\sim$ 1  $\times$  10<sup>-6</sup> mbar), using a Keithley 236 source-measure unit controlled via Python. The voltage was swept in the range from -10~V to +10~V in steps of 50 mV, with sweep rate of ca. 100 mV/s and internal averaging of 20 ms, keeping the bottom Au electrode on ground. The graphene resistance was characterized in graphene bridge devices by sweeping the voltage in the range from -50~mV to +50~mV in steps of 1 mV, with a sweep rate of ca. 3 mV/s and internal averaging of 20 ms.

The temperature-dependent I-V traces were collected in the range 200–300 K in steps of 5 K in a Lakeshore probe station (CRX-6.5K) operating under vacuum ( $\sim 1 \times 10^{-6}$  mbar), in the dark. The electronics comprised an AdWin Gold II ADC-DAC unit operating at 100 kHz and a low-noise current to voltage converter (Basel SP983C). The ADC-DAC was controlled via *Python*. The voltage was swept in the range from -10 V to +10 V in steps of 0.1 V, with internal averaging of 20 ms and a delay between the source and

measurement point of 100 ms, corresponding to an effective voltage sweep rate of ca.  $0.8~{

m V/s}.$

Impedance spectroscopy was carried out on one representative device per area using an Agilent 4294a precision impedance analyzer controlled via *Python*, from 40 Hz to 1 MHz in 201 steps, in the dark, under a vacuum ( $\sim 1 \times 10^{-6}$  mbar), with the oscillator level set to 100 mV. Open/short compensation was performed after the acquisition and following the *Agilent Impedance Measurement Handbook*. To this purpose, we designed and fabricated devices for open/short compensation on the same chip.

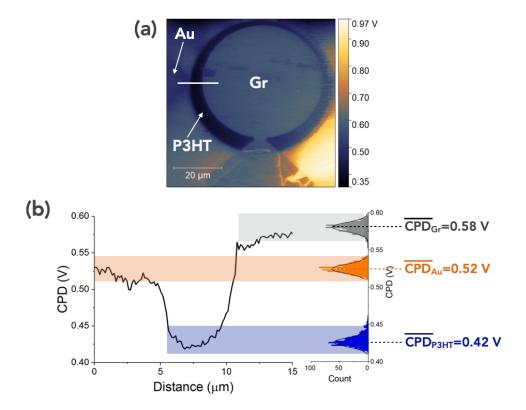

KPFM measurements were carried out at room temperature in air (22 °C and 35% relative humidity) with a Dimension 3100 (Bruker), using a Pt/Ir tip. Topography (tapping mode AFM) and KPFM images were recorded using a standard two-pass procedure, in which each topography line acquired in the tapping mode is followed by the acquisition of CPD (contact potential difference between the tip and the sample) data in a lift mode. Since the CPD images on Au, Gr, and P3HT are acquired with the same tip, the interface barrier energy is directly given by the difference in the CPD values, i.e.,  $\Phi_{\rm B,Gr/P3HT} = q({\rm CPD_{\rm Gr}} - {\rm CPD_{\rm P3HT}})$ , where q is the electron charge.

**Raman Spectroscopy.** Raman spectra were acquired in ambient conditions using a 532 nm excitation wavelength with a WITec Alpha 300R confocal Raman microscope mounting a LD 100× objective (Zeiss EC Epiplan-Neofluar Dic, NA = 0.75) and a 300 mm lens-based spectrometer (grating: 600 g mm<sup>-1</sup>) equipped with a TE-cooled charge-coupled device (Andor Newton). P3HT powder and films spectra were acquired by averaging over a 5 × 5  $\mu$ m<sup>2</sup> area with a laser power and an integration time of 0.1 mW and 0.1 s, while graphene spectra were acquired with a laser power and an integration time of 1 mW and 10 s.

**Atomic Force Microscopy (AFM).** AFM height and phase images were collected in tapping mode in ambient conditions using a Bruker Icon AFM equipped with a TESPA-V2 cantilever with a tip apex radius of 7 nm (resonant frequency: 320 kHz, spring constant 37 N/m).

FIB-SEM. The device cross-section was prepared by means of a FEI Helios 660 G3 UC FIB/SEM-System. Prior to cutting, a protective layer of platinum was deposited in a two-step process, first by electron-induced deposition (3 keV, 800pA), followed by ion-induced deposition (30 keV, 230pA) in order to prevent ion induced damage to the layers of interest. The cross-section was cut in a 30 kV gallium ion beam at an ion current of 47 nA. The cross-section was sequentially polished at different ion currents, down to a minimal current of 790 pA.

**Modeling, Fitting, and Plotting.** Modeling, fitting, and plotting of the data were done in *Python*. Three main libraries were used (i) numpy polyfit, <sup>29</sup> for the estimation of graphene series resistance; (ii) scipy curve\_fit, <sup>30</sup> for the SCL and TE modeling; and (iii) impedance.py, <sup>31</sup> for the circuit modeling and fitting of the impedance analysis measurements.

### ■ RESULTS AND DISCUSSION

Figure 1a shows the schematic of a Au/P3HT/Gr heterostructure, fabricated according to the procedure illustrated in Figure 1b and described in the Experimental Methods and in the Supporting Information. Figures 1c,d show the AFM height and phase images of a representative device having a diameter of 20  $\mu$ m, where a white dashed line marks the contour of the graphene and a black dashed line marks the Au side-electrode. The thickness of the Au/P3HT/Gr stack in the center of the device is ca. 130 nm as measured by AFM (see the Supporting Information). Given that the bottom Ti/Au electrode is 35 nm thick, the thickness of the P3HT film is ca. 100 nm. Figure 1e shows a cross-section of the Au/P3HT/Gr stack in the center of the device. Starting from the bottom, one can distinguish Si (525  $\mu$ m), SiO<sub>2</sub> (300 nm), Ti (5 nm), Au (30 nm), and P3HT (100 nm) as annotated in the figure. The graphene electrode is too thin to be visible in the cross-section.

Figure 1f superimpose the Raman spectrum of the P3HT powder as received, with the Raman spectrum of the Au/ P3HT/Gr stack. The vibrational modes of P3HT are found at 728, 1180, 1208, 1381, and 1452 cm<sup>-1</sup>, in agreement with the literature. 32,33 The vibrational modes of graphene are not discernible from P3HT for three reasons: (i) the G and D peaks of graphene are hidden by the overlapping modes of P3HT at 1381 and 1452 cm<sup>-1</sup>, (ii) the 2D peak is hidden by the strong background signal of P3HT, and (iii) the P3HT is much thicker than graphene, therefore resulting in a much stronger spectral signal. Therefore, the Raman spectrum of graphene was measured on SiO2, in close proximity to the Au contact. The graphene Raman spectrum is shown in the inset of Figure 1f against the Raman spectrum of a representative CVD graphene on SiO<sub>2</sub>. The characteristic G (1580 cm<sup>-1</sup>) and 2D (2680 cm<sup>-1</sup>) peaks of graphene<sup>34</sup> are identified, as well as the D (1350 cm<sup>-1</sup>) peak, possibly due to defects induced by the fabrication, and an additional peak at 1445 cm<sup>-1</sup>, most likely due to P3HT or resist residues. The AFM, SEM, and Raman data demonstrate that the fabrication process is compatible with P3HT and graphene and therefore suitable for the fabrication of vertical van der Waals devices based on these materials.

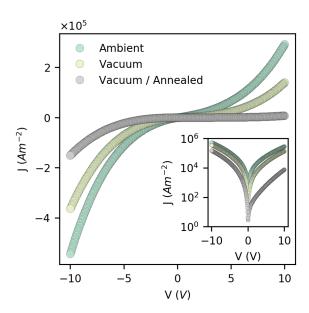

The electrical properties of OSCs are very sensitive to the environment. Figure S3 shows the J-V traces of a representative 10  $\mu$ m device measured in ambient, in vacuum and in vacuum after annealing at 110° for 12 h. The current density is higher in ambient and it decreases in vacuum, reaching a minimum after annealing, with peak current density at -10 V going from  $5.4 \times 10^5 \text{ Am}^{-2}$  to  $1.5 \times 10^5 \text{ A m}^{-2}$ . The traces are asymmetric: defining the rectification ratio as RR = J(-10V)/J (10V), the latter increases from RR = 1.9 in ambient, to RR = 2.6 in a vacuum, and finally to RR = 19.2 in a vacuum after annealing. This trend is ascribed to the graphene and P3HT dedoping: it is known that P3HT is doped by  $O_{2}^{35}$ while graphene is doped by O2 and H2O, 36-38 and that their doping level can be reduced by annealing under a vacuum. 39,40 Accordingly, an annealing under vacuum shifts the Fermi level of graphene, resulting in a realignment of the energy bands at the OSC/graphene interface, which leads to the observed change in the rectification ratio. The hypothesis is further supported by the graphene resistance shown in Figure 2b: the graphene/Au interface is Ohmic and the graphene resistance increases after vacuum exposure and annealing.

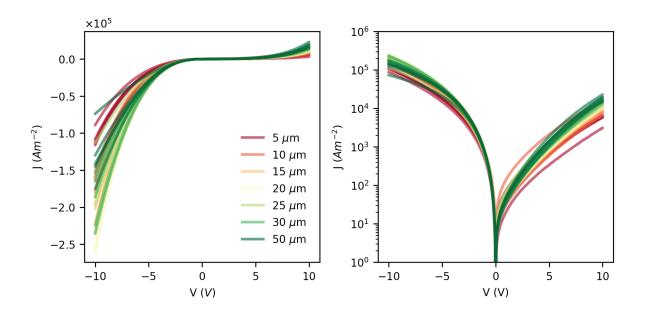

In order to minimize the variability among different devices due to uncontrolled doping of P3HT and graphene, the charge transport analysis that follows was done in a vacuum after annealing for 12 h at 110 °C. Figure 2c shows the current density of five representative devices, one per device area, measured in a vacuum after annealing (see the Supporting Information for the I-Vs of all devices). The current density is calculated assuming the area of the (smaller) graphene electrode  $(J = I/A_{Gr})$ . The current density variability falls within ca. one order of magnitude (between  $7.3 \times 10^4$  and 2.6 $\times 10^{5}$  at -10 V, and between 3.1  $\times 10^{3}$  and 2.3  $\times 10^{4}$  at +10 V) and all J-Vs display the same shape. This suggests that the scaling of the device, from 50  $\mu$ m down to 5  $\mu$ m in diameter, does not affect the transport mechanism, and that the variability between devices is due to fabrication uncertainties. In all measurements conditions, and for both positive and negative bias, the current density grows exponentially with the applied voltage above a certain threshold. This trend is typically described by a variety of analytical models that allows

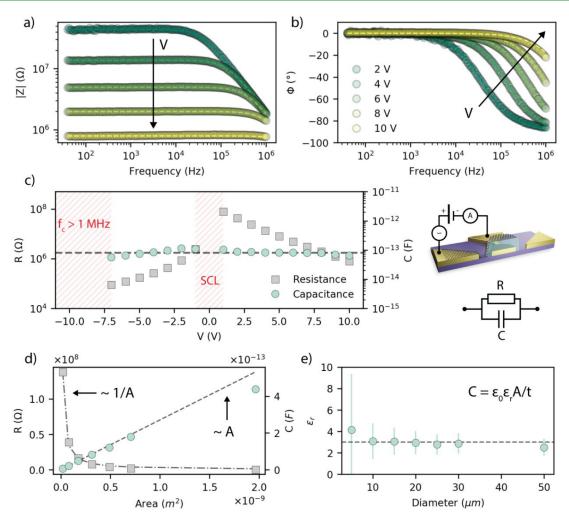

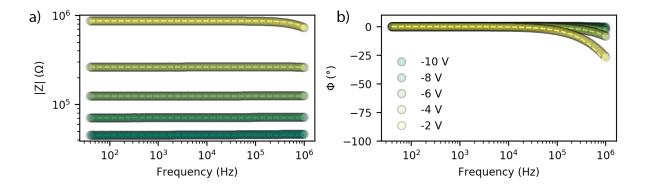

Figure 3. Impedance analysis. (a) Modulus and (b) phase of a representative 20  $\mu$ m device: data (circles), RIIC model fit (dashed lines) (c) Resistance R and capacitance C extracted from the RIIC model fit at different biases. R and C are not calculated in the SCL region and for V < -7.5 V, where the cutoff frequency  $f_c$  is outside the measurement range. (d) Extracted R and C values for the devices with diameter: 5, 10, 15, 20, 25, 30, and 50  $\mu$ m. The green dashed line is the linear fit of the capacitance vs area. (e)  $\epsilon_r$  vs device diameter (error bars calculated as described in the Supporting Information).

us to extract transport parameters (e.g., charge carrier mobility and density and the energy barriers at the interfaces). Among these models are the thermionic emission (TE) assisted by image-charge-induced potential barrier lowering, 41 the Poole-Frenkel emission (PFE),41 and the modified TE (MTE) for graphene/semiconductor interfaces. 42,43 The fittings of the J-Vs with the PFE model (not reported) were found to return relative dielectric permittivity of P3HT around 20-40, i.e., about 1 order of magnitude larger than what discussed in the literature. 44-46 Therefore, the PFE model was excluded from the analysis. The hypothesis of the MTE model requires that the charge at the graphene/semiconductor interface depends on the bias. However, the capacitance measurements discussed in the following show that the organic semiconductor is fully depleted. Hence, the charge at the interface is bias independent and therefore the MTE model was not considered for the analysis that follows. The TE model has been successfully applied to metal-OSC interfaces 47-50 and was found to be in good agreement also with the measurements of this work in the high voltage regime, that is |V| > 1 V. According to the TE model, the J-V traces shown in Figure 2c are the reverse currents of the Au/P3HT and Gr/P3HT interfaces for

negative and positive bias, respectively. The reverse current reads:<sup>41</sup>

$$J_{\rm R}^{\rm (TE)} = A^{**} T^2 \exp \left[ \frac{-q(\phi_{\rm B} - \sqrt{qV'/4\pi\epsilon_0 \epsilon_{\rm r} t})}{k_{\rm B} T} \right] \tag{1}$$

Where  $A^{**}$  is the reduced effective Richardson constant, T is the temperature, q is the elementary charge,  $\phi_{\rm B}$  is the barrier height potential,  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_{\rm r}$  is the P3HT dielectric permittivity,  $k_{\rm B}$  is the Boltzmann constant, t the thickness of the device, and  $V = V - R_{\rm s}I$  is the applied voltage V minus the voltage that drops over the graphene (series) resistance  $R_{\rm s}$ . The  $R_{\rm s}I$  term becomes relevant when the out-of-plane resistance of Au/P3HT/Gr is comparable to  $R_{\rm s}$ , which typically happens for V < -5 V and device diameter larger than 10  $\mu$ m (see Figure S7).

At lower bias voltage, the J-V traces do not agree anymore with the TE model, but they show the typical trap-free space-charge limited (SCL)<sup>41,51,52</sup> dependency where, on the one hand, if the charge carrier density at the contact  $N_0$  is larger

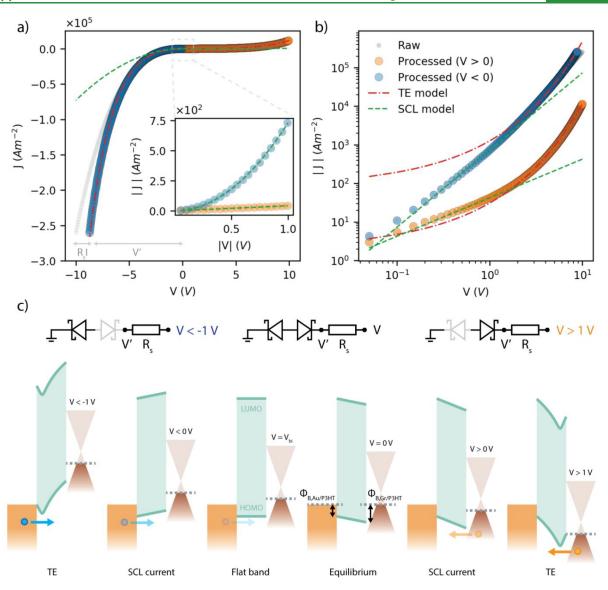

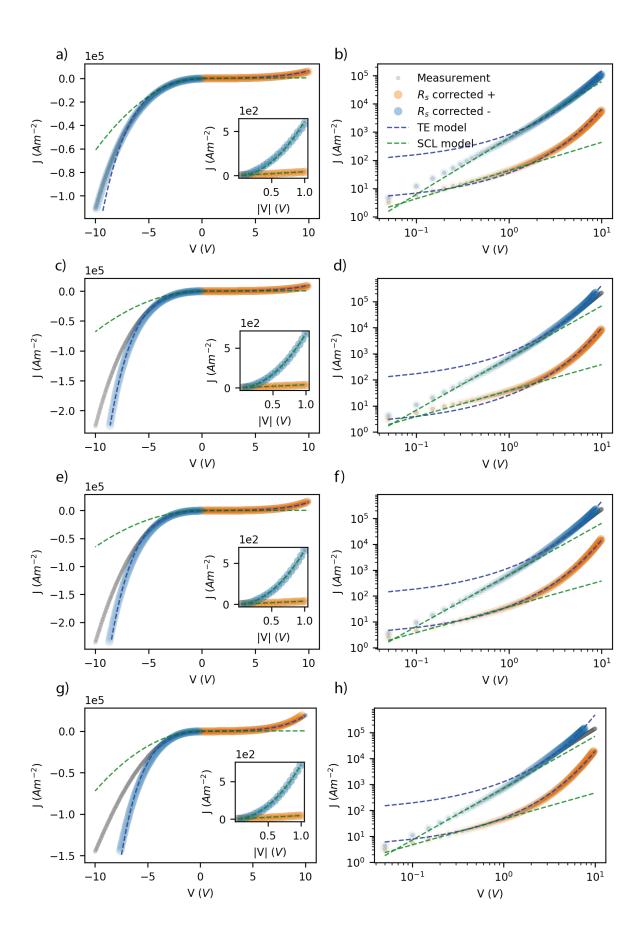

Figure 4. (a) Current density across a 20  $\mu$ m device. Raw data are represented by gray circles. Processed data (orange and blue circles) takes into account for the graphene series resistance. The graph shows the fitting results of the SCL current (green dashed lines) and TE (red dashed lines). The inset shows the  $\pm 1$  V region where the space-charge effect is limiting the current across the heterostructure. (b) Current density shown in logarithmic scale. The current density for positive and negative biases is represented by orange and blue circles, respectively. (c) Band diagram of the Au/P3HT/Gr heterojunction illustrating the charge transport regimes and equivalent circuit. The shaded Schottky diodes are forward biased.

than  $\sqrt{\frac{J\epsilon_0\epsilon_r}{2\mu tq^2}}$ , where  $\mu$  is the charge carrier mobility of the organic semiconductor, then

$$J = \frac{9}{8} \epsilon_0 \epsilon_r \mu \frac{V^2}{t^3} \tag{2}$$

and on the other hand, if  $N_0$  is smaller than  $\sqrt{\frac{J\epsilon_0\epsilon_r}{2\mu tq^2}}$  then

$$J = q\mu N_0 \frac{V}{t} \tag{3}$$

From eqs 1–3, one can extract the barrier height  $\phi_{\rm B}$ , the mobility  $\mu$ , and the charge carrier density at the interfaces, provided knowledge of  $\epsilon_{\rm r}$  and  $A^{**}$ . The effective Richardson constant  $A^{**}$  can be obtained from temperature-dependent measurements through the Richardson plot  $(\ln(J/T^2) \text{ vs } 1/T)$ , while the dielectric permittivity  $\epsilon_{\rm r}$  can be either taken from the literature or extracted from capacitive measurements under the

hypothesis of a fully depleted semiconductor. Since the extraction of the barrier height is sensitive to  $\varepsilon_{\rm r}$  and the latter depends on the measurement environment, it is beneficial to measure the dielectric permittivity of P3HT on the system under study, if possible. Given that the charge carrier density of unintentionally doped organic P3HT films is typically in the range of  $1\times 10^{17}$  to  $1\times 10^{18}$  cm $^{-3},^{35,40}$  and that the doping concentration is usually reduced to roughly  $1\times 10^{15}$  cm $^{-3}$  by annealing in a vacuum,  $^{40,53}$  the P3HT can be safely assumed fully depleted and therefore  $\varepsilon_{\rm r}$  extracted from impedance spectroscopy. This hypothesis can be assessed by measuring the capacitance of the heterostructure as a function of the applied bias: if the capacitance does not depend on the bias, then the depletion region extends over the entire thickness of the device.

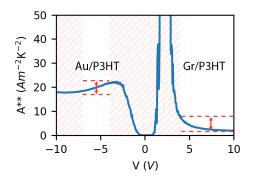

$A^{**}$  was extracted from the Richardson plot of a representative device having diameter of 5  $\mu$ m at bias  $\pm 5$  V, such that the graphene series resistance  $R_{\rm s}$  was negligible

Table 1. Statistics of the Fitting Parameters<sup>a</sup>

|                    |                     | space-charge                                | model (IVI < 1 V)                                                           | thermionic emission model ( $ V  > 1 V$ ) |                         |                         |  |  |

|--------------------|---------------------|---------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------|-------------------------|-------------------------|--|--|

| diameter $(\mu m)$ | P3HT thickness (nm) | $N_0 \ (\times \ 10^{15} \ \text{cm}^{-3})$ | $\mu \ (\times \ 10^{-4} \ \text{cm}^{-2} \ \text{V}^{-1} \ \text{s}^{-1})$ | $R_{\rm s}~({\rm k}\Omega)$               | $\Phi_{B,Gr/P3HT}$ (eV) | $\Phi_{B,Au/P3HT}$ (eV) |  |  |

| 5                  | 130                 | $0.94 \pm 0.40$                             | $4.36 \pm 0.61$                                                             | 35 (fixed)                                | $0.30 \pm 0.02$         | $0.25 \pm 0.01$         |  |  |

| 10                 | 120                 | $1.14 \pm 0.12$                             | $3.72 \pm 0.92$                                                             | 35 (fixed)                                | $0.29 \pm 0.01$         | $0.25 \pm 0.01$         |  |  |

| 15                 | 100                 | $1.11 \pm 0.26$                             | $2.26 \pm 0.21$                                                             | $42.0 \pm 7.9$                            | $0.31 \pm 0.01$         | $0.26 \pm 0.01$         |  |  |

| 20                 | 100                 | $1.13 \pm 0.26$                             | $2.37 \pm 0.09$                                                             | $19.1 \pm 10.9$                           | $0.31 \pm 0.01$         | $0.25 \pm 0.01$         |  |  |

| 25                 | 100                 | $1.44 \pm 0.37$                             | $2.41 \pm 0.21$                                                             | $24.6 \pm 16.5$                           | $0.30 \pm 0.01$         | $0.25 \pm 0.01$         |  |  |

| 30                 | 100                 | $1.16 \pm 0.26$                             | $2.13 \pm 0.08$                                                             | $12.7 \pm 6.4$                            | $0.30 \pm 0.01$         | $0.25 \pm 0.01$         |  |  |

| 50                 | 100                 | $1.20 \pm 0.14$                             | $2.32 \pm 0.09$                                                             | $11.2 \pm 12.8$                           | $0.29 \pm 0.01$         | $0.25 \pm 0.01$         |  |  |

| all                | 100                 | $1.16 \pm 0.65$                             | $2.80 \pm 2.17$                                                             | $25.6 \pm 24.3$                           | $0.30 \pm 0.02$         | $0.25 \pm 0.02$         |  |  |

<sup>a</sup>The average on five devices is given for  $N_0$ ,  $\mu$ ,  $R_s$ , and  $\Phi$ . The reported error is the min/max value. All SCL and TE model fits were done using  $\epsilon_r \approx 3$ ,  $A_{\rm Gr/P3HT}^{***} = 4.3$  A m<sup>-2</sup> K<sup>-2</sup> and  $A_{\rm Au/P3HT}^{***} = 20.5$  A m<sup>-2</sup> K<sup>-2</sup>. The series resistance of the 5 μm and 10 μm devices is very small compared to the device out-of-plane resistance. In order to prevent the fitting algorithm to maximize  $R_s$ , the latter was set to 35 kΩ for 5 μm and 10 μm devices. Figure S5 shows the current density and the fits of various devices.

compared to the out-of-plane resistance of the stack and therefore V' ( $\pm 5$  V) = V ( $\pm 5$  V). Figure 2d shows the J-Vcharacteristics as a function of temperature, from 200 to 300 K in steps of 5 K. The current density increases with temperature, peaking at -10 V from  $1 \times 10^4 \text{ A} \text{ m}^{-2}$  (200 K) to  $9.5 \times 10^4 \text{ A}$  $m^{-2}$ , (300 K) while the J-Vs exhibit the typical exponential character of the TE model over the whole temperature range. The inset of Figure 2d shows the Richardson plot for bias +5 V (hole injection from Gr) and bias −5 V (hole injection from Au). From the intercept of the linear fit, the reduced effective Richardson constants results in  $A_{Gr/P3HT}^{**} = 4.3 \text{ A m}^{-2} \text{ K}^{-2}$  for hole injection from Gr and  $A_{\text{Au/P3HT}}^{**}$  = 20.5 A m<sup>-2</sup> K<sup>-2</sup> for hole injection from Au, similar to the values previously reported for metal/OSC<sup>47,48</sup> and Gr/OSC<sup>43</sup> interfaces. It is worth observing that  $A^{**}$  could be extracted from the Richardson plot in the whole voltage range where the I-V is exponential and  $R_s$  is negligible. However, Figure S8 shows that (i)  $A^{**}$ does not vary significantly in that voltage range and (ii) the potential barrier heights extracted from the fittings do not depend significantly on the particular choice of  $A^{**}$ . Therefore, the chosen values of  $A^{**}$  did not affect the results

The dielectric permittivity  $\epsilon_r$  was extracted from the impedance spectroscopy on a representative device per device area. Figure 4a, b shows the impedance of a representative device having a diameter of 20  $\mu$ m, in the frequency range of 40 Hz to 1 MHz, for positive bias (refer to the Supporting Information for the impedance for negative biases). The impedance exhibits the typical behavior of an RIIC circuit. The resistance R and the capacitance C of the system are therefore extracted by fitting the experimental data with a nonideal capacitor model RIIC, and are reported in Figure 3c. The high negative voltage range corresponding to V < -7 V was not fitted because the cutoff frequency of the system is beyond 1 MHz (upper limit of the measurement range). The low voltage region (|V| < 1 V) was also not considered because the spacecharge would result in a capacitance 3 / 2 larger than the geometrical one.<sup>52</sup> The resistance decreases with the applied bias, from 80.7 M $\Omega$  at 1 V to 791 k $\Omega$  at 10 V, possibly due to the image-charge-induced potential barrier lowering, while the capacitance is bias-independent around 80 fF, confirming that the organic semiconductor is fully depleted. §4 The dielectric constant of P3HT is estimated from the geometrical capacitance (i.e.,  $C = \epsilon_0 \epsilon_r A/t$ , where A is the area of the graphene electrode), without considering the edge effects and assuming a nominal thickness of 100 nm (see Figure S2),

resulting in  $\epsilon_{\rm r}\approx 3$ , in agreement with previously reported values for P3HT. Head of the capacitance scale as 1/A and A, respectively. It is worth observing that the dielectric constant calculated for small devices is affected by the large error due to geometrical variability as reported in Figure 4e.

Given  $A^{**}$  and  $\epsilon_{\rm r}$ , one can finally use eqs 1-3 to fit the experimental J-Vs and extract  $\phi_B$ ,  $\mu$ , and  $N_0$ , as anticipated above. Figure 4a shows the J-V curve of a representative device having a diameter of 20  $\mu$ m. The gray circles represent the raw data, while the orange and blue circles are the processed data for the positive and negative biases, respectively, where V is replaced by  $V' = V - R_s I$ . The barrier height and  $R_s$  are obtained by a parametric fit of the TE model (eq 1) in  $R_s$  of the processed data in the high voltage regime ( VI > 1), where  $R_s$  spans the interval 0–100 k $\Omega$  in steps of 100 Ω. The fit result in  $R_s$  = 15.4 kΩ,  $Φ_{B,Gr/P3HT}$  = 0.31 eV, and  $\Phi_{\rm BAu/P3HT}$  = 0.25 eV, giving a built-in potential of about 60 meV. The barrier height measured by KPFM in ambient on a representative device resulted in  $\Phi_{B,Au/P3HT}^{(KPFM)} = 0.10 \pm 0.03 \text{ eV}$ and  $\Phi_{B,Gr/P3HT}^{(KPFM)} = 0.16 \pm 0.03$  eV, which differ from those extracted from the fit of the J-Vs, although they follow the same trend  $\Phi_{B,Gr/P3HT} > \Phi_{B,Au/P3HT}$  (refer to the Supporting Information for details on the KPFM measurements). This inconsistency should not be a surprise, as the KPFM strongly depends on the purity of the surface and therefore on the measuring environment,<sup>56</sup> which differs from the environment of the J-V measurements. Nevertheless, the built-in potential measured by KPFM matches the value obtained from the fitting of the J-V curves. This could be ascribed to a similar shift in the graphene and gold work functions, such that the built-in potential of the stack depends mostly on the doping of P3HT when exposed to air.<sup>35,39</sup> It is worth observing that  $\Phi_{B,Au/P3HT}$  differs from previously reported values for Au/ P3HT interfaces measured with other techniques or in different environments, 57,58 ultimately pointing to the fact that the estimation of the barrier height is very sensitive to both the measurement conditions and the measurement method. The inset of Figure 4a shows the current density in the low voltage regime (|V| < 1). Since the built-in potential is very small, the flat-band condition is very close to the equilibrium condition. Therefore, the SCL is observed for small biases, in agreement with eq 2. Fitting the current density for negative biases with eq 2 results in an out-of-plane hole mobility of  $\mu \approx 2.4 \times 10^{-4} \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , similar to previously reported values for in-plane hole mobility in P3HT. 40,53 Fitting

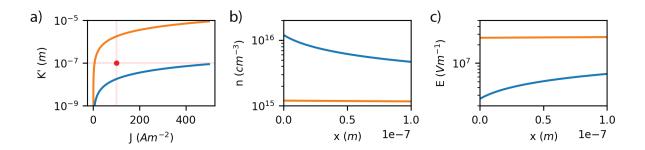

the current density for positive biases with eq 3 gives the density of charge carriers at the Gr/P3HT interface, which corresponds to the intrinsic carrier concentration of P3HT (see the Supporting Information). This results in  $N_0\approx 1.1\times 10^{15}~{\rm cm}^{-3}$ , also in agreement with previously reported values for intrinsic P3HT in a vacuum. In the SCL model, the charge carrier density at the contacts depends on the density of states in the semiconductor and on the potential barrier height at the interface. From  $N_0$ , one can therefore calculate the charge carrier density at the Au/P3HT interface, resulting in  $\sim 1.2\times 10^{16}~{\rm cm}^{-3}$ . The difference between  $N_{0,{\rm Au/P3HT}}$  and  $N_{0,{\rm Gr/P3HT}}$ , is in agreement with the experimental evidence that  $J\sim V$  for positive bias and  $J\sim V^2$  for negative bias (see the Supporting Information for a discussion). The J-V dependencies are especially clear in the inset of Figure 4a and in Figure 4b.

Figure 4c shows the energy band diagram of the Au/P3HT/Gr heterostructure sketched using the barrier heights extracted from the fit of the J–Vs, and assuming that the P3HT is fully depleted, as proven by capacitive measurements. The curvature of the HOMO and LUMO levels in proximity of the interfaces qualitatively describes the potential barrier lowering due to the image charge effect. The Fermi level of P3HT lies close to the HOMO level, as expected from Fermi level pinning due to interface states.  $^{59,60}$

Table 1 reports a statistical summary on five devices per area of the extracted electrical parameters. The dispersion of the extracted parameters is quite small. In order to take into account the edge effects (see the Supporting Information), the P3HT thickness of small devices was set to a value slightly larger than that measured by AFM on a representative device having a diameter of 20  $\mu$ m.

### CONCLUSIONS

This work demonstrates a potentially upscalable fabrication process for Au/P3HT/Gr VdW heterostructures on Si/SiO $_2$  and describes the charge injection and transport mechanism across the heterostructures. The device output characteristic is independent from the device size for device diameters from 50  $\mu$ m down to 5  $\mu$ m, making device downscaling accessible and possibly limited solely by lithography resolution.

Impedance spectroscopy measurements shows that the P3HT is fully depleted in the high bias regime (|V| > 1 V or |V|/t > 10 MV/m), and therefore, the dielectric constant of P3HT is determined from the geometrical capacitance of the devices, resulting in  $\epsilon_{\rm r} \approx 3$ . The electrical transport measurements show that the charge injection across the Au/ P3HT and Gr/P3HT interfaces is dominated by TE in the high bias regime (|V| > 1 V), with potential barriers of  $\Phi_{B,Gr/P3HT}$  = 0.31 eV and  $\Phi_{B,Au/P3HT}$  = 0.25 eV, respectively, and by the SCL current in the low bias regimes (|V| < 1 V). The intrinsic carrier concentration and the out-of-plane hole mobility of P3HT, determined by fitting the J-Vs in the low bias regime with the SCL model, resulted in  $\mu \approx 2.8 \times 10^{-4}$ cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $N_0 \approx 1.16 \times 10^{15}$  cm<sup>-3</sup>, similar to literature values extracted from in-plane FET measurements. The energy band diagram of the heterostructure shows that the interface traps/defects pin the Fermi level very close to the HOMO level of P3HT.

Since the current in Au/P3HT/Gr heterostructures is injection-limited, the hole mobility of P3HT does not limit the operating frequency of the stack, which exceeds 1 MHz for bias approaching 10 V. Higher cutoff frequencies could be

achieved by making Ohmic the contact between the electrodes and P3HT, for instance, by introducing a (heavily) doped OSC layer between the electrodes and the OSC, such as  $F_4TCNQ$ -or  $F_6TCNQ$ -doped P3HT.

Overall, this work shows that graphene can be implemented as a top or interlayer electrode in vertical devices based on multilayer van der Waals heterostructures. For instance, the charge injection between gold and P3HT could be optimized to achieve high operating frequencies, while the Gr/P3HT interface is kept as is to exploit its rectifying nature. With graphene acting as a permeable electrode, the Gr/P3HT heterostructure studied in this work could become the core element to build future vertical organic transistors based on two back-to-back Gr/P3HT diodes.

### ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.2c13148.

Fabrication process of Au/P3HT/Gr heterostructures; FIB/SEM/AFM characterizations; electrical transport characterization, including all traces from all devices; Kelvin probe force microscopy (KPFM) analysis of the interfaces; chip overview; space-charge limited (SCL) current modeling. (PDF)

### AUTHOR INFORMATION

### **Corresponding Authors**

Davide Beretta — Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland; orcid.org/0000-0002-7739-7494;

Email: davide.beretta@empa.ch

Michel Calame — Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland; Swiss Nanoscience Institute and Department of Physics, University of Basel, Basel CH-4056, Switzerland; orcid.org/0000-0001-7467-9915;

Email: michel.calame@empa.ch

### **Authors**

Jacopo Oswald — Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland; Swiss Nanoscience Institute, University of Basel, Basel CH-4056, Switzerland; orcid.org/0000-0003-1328-8843

Michael Stiefel – Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland

Roman Furrer — Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland

Alessia Romio — Transport at Nanoscale Interfaces Laboratory, EMPA, Swiss Federal Laboratories for Materials Science and Technology, Dübendorf CH-8600, Switzerland

Michel Daher Mansour – Institute of Electronic, Microelectronic and Nanotechnology, Centre National de la Recherche Scientifique, Villeneuve d'Ascq 59652, France

Dominique Vuillaume – Institute of Electronic, Microelectronic and Nanotechnology, Centre National de la Recherche Scientifique, Villeneuve d'Ascq 59652, France; o orcid.org/0000-0002-3362-1669

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.2c13148

### **Author Contributions**

J.O. and M.S. fabricated the devices. J.O. took the Raman spectra. J.O. and D.B. did all electrical measurements and modeling. R.F. grew the CVD graphene. J.O. and A.R. took the AFM images. M.D.M. and D.V. performed and analyzed the KPFM experiments. The manuscript was written by J.O. and D.B. with contributions and discussions from all authors. The work was supervised by M.C. and D.B. The SNF and ANR funding were acquired by M.C. and D.V. The H2020 funding was acquired by D.B. All authors have participated to the review of and have given approval to the final version of the manuscript.

### **Funding**

M.C. acknowledges financial support from the Swiss National Science Foundation (SNF) under Grant 182544, D.V. from the Agence Nationale De La Recherche (ANR) under the grant ANR-18-CE93-0005-01, and D.B. from the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska-Curie Grant Agreement 754364,

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors acknowledge Lars Lüder for the realization of the 3D schematics. The authors also thank the Cleanroom Operations Team of the Binnig and Rohrer Nanotechnology Center (BRNC) for their help and support.

### ABBREVIATIONS

OSC, organic semiconductor; Gr, graphene; PMMA, poly-(methyl methacrylate); VdW, van der Waals; P3HT, poly(3-hexylthiophene-2,5-diyl); TE, thermionic emission; SCL, space-charge limited; PFE, Poole—Frenkel emission; CVD, chemical vapor deposition; RR, regio-regular; OLED, organic light emitting diode

### REFERENCES

- (1) Gobbi, M.; Orgiu, E.; Samori, P. When 2D Materials Meet Molecules: Opportunities and Challenges of Hybrid Organic/Inorganic van Der Waals Heterostructures. *Adv. Mater.* **2018**, *30* (18), 1706103.

- (2) Jariwala, D.; Marks, T. J.; Hersam, M. C. Mixed-Dimensional van Der Waals Heterostructures. *Nat. Mater.* **2017**, *16* (2), 170–181.

- (3) Lee, G.-H.; Lee, C.-H.; van der Zande, A. M.; Han, M.; Cui, X.; Arefe, G.; Nuckolls, C.; Heinz, T. F.; Hone, J.; Kim, P. Heterostructures Based on Inorganic and Organic van Der Waals Systems. *APL Mater.* **2014**, *2* (9), 092511.

- (4) Wang, Y.; Tong, S. W.; Xu, X. F.; Özyilmaz, B.; Loh, K. P. Interface Engineering of Layer-by-Layer Stacked Graphene Anodes for High-Performance Organic Solar Cells. *Adv. Mater.* **2011**, 23 (13), 1514–1518.

- (5) Park, H.; Rowehl, J. A.; Kim, K. K.; Bulovic, V.; Kong, J. Doped Graphene Electrodes for Organic Solar Cells. *Nanotechnology* **2010**, 21 (50), 505204.

- (6) Liu, Z.; Li, J.; Yan, F. Package-Free Flexible Organic Solar Cells with Graphene Top Electrodes. *Adv. Mater.* **2013**, 25 (31), 4296–4301.

- (7) Grotevent, M. J.; Hail, C. U.; Yakunin, S.; Dirin, D. N.; Thodkar, K.; Borin Barin, G.; Guyot-Sionnest, P.; Calame, M.; Poulikakos, D.;

- Kovalenko, M. V.; Shorubalko, I. Nanoprinted Quantum Dot-Graphene Photodetectors. *Adv. Opt. Mater.* **2019**, *7* (11), 1900019.

- (8) Huisman, E. H.; Shulga, A. G.; Zomer, P. J.; Tombros, N.; Bartesaghi, D.; Bisri, S. Z.; Loi, M. A.; Koster, L. J. A.; van Wees, B. J. High Gain Hybrid Graphene-Organic Semiconductor Phototransistors. ACS Appl. Mater. Interfaces 2015, 7 (21), 11083–11088.

- (9) Liu, Y.; Zhou, H.; Weiss, N. O.; Huang, Y.; Duan, X. High-Performance Organic Vertical Thin Film Transistor Using Graphene as a Tunable Contact. ACS Nano 2015, 9 (11), 11102–11108.

- (10) Berke, K.; Tongay, S.; McCarthy, M. A.; Rinzler, A. G.; Appleton, B. R.; Hebard, A. F. Current Transport across the Pentacene/CVD-Grown Graphene Interface for Diode Applications. *J. Phys.: Condens. Matter* **2012**, *24* (25), 255802.

- (11) Lemaitre, M. G.; Donoghue, E. P.; McCarthy, M. A.; Liu, B.; Tongay, S.; Gila, B.; Kumar, P.; Singh, R. K.; Appleton, B. R.; Rinzler, A. G. Improved Transfer of Graphene for Gated Schottky-Junction, Vertical, Organic, Field-Effect Transistors. *ACS Nano* **2012**, *6* (10), 9095–9102.

- (12) Hlaing, H.; Kim, C.-H.; Carta, F.; Nam, C.-Y.; Barton, R. A.; Petrone, N.; Hone, J.; Kymissis, I. Low-Voltage Organic Electronics Based on a Gate-Tunable Injection Barrier in Vertical Graphene-Organic Semiconductor Heterostructures. *Nano Lett.* **2015**, *15* (1), 69–74.

- (13) Kim, K.; Lee, T. H.; Santos, E. J. G.; Jo, P. S.; Salleo, A.; Nishi, Y.; Bao, Z. Structural and Electrical Investigation of C  $_{60}$  -Graphene Vertical Heterostructures. *ACS Nano* **2015**, 9 (6), 5922–5928.

- (14) Shih, C.-J.; Pfattner, R.; Chiu, Y.-C.; Liu, N.; Lei, T.; Kong, D.; Kim, Y.; Chou, H.-H.; Bae, W.-G.; Bao, Z. Partially-Screened Field Effect and Selective Carrier Injection at Organic Semiconductor/ Graphene Heterointerface. *Nano Lett.* **2015**, *15* (11), 7587–7595.

- (15) Matyba, P.; Yamaguchi, H.; Chhowalla, M.; Robinson, N. D.; Edman, L. Flexible and Metal-Free Light-Emitting Electrochemical Cells Based on Graphene and PEDOT-PSS as the Electrode Materials. *ACS Nano* **2011**, *5* (1), 574–580.

- (16) Wu, J.; Agrawal, M.; Becerril, H. A.; Bao, Z.; Liu, Z.; Chen, Y.; Peumans, P. Organic Light-Emitting Diodes on Solution-Processed Graphene Transparent Electrodes. *ACS Nano* **2010**, *4* (1), 43–48.

- (17) Lee, C.-H.; Lee, G.-H.; van der Zande, A. M.; Chen, W.; Li, Y.; Han, M.; Cui, X.; Arefe, G.; Nuckolls, C.; Heinz, T. F.; Guo, J.; Hone, J.; Kim, P. Atomically Thin p-n Junctions with van Der Waals Heterointerfaces. *Nat. Nanotechnol.* **2014**, *9* (9), 676–681.

- (18) Kim, C.-H.; Kymissis, I. Graphene-Organic Hybrid Electronics. *J. Mater. Chem. C* **2017**, *5* (19), 4598–4613.

- (19) Pang, S.; Hernandez, Y.; Feng, X.; Müllen, K. Graphene as Transparent Electrode Material for Organic Electronics. *Adv. Mater.* **2011**, 23 (25), 2779–2795.

- (20) Schlierf, A.; Samorì, P.; Palermo, V. Graphene-Organic Composites for Electronics: Optical and Electronic Interactions in Vacuum, Liquids and Thin Solid Films. *J. Mater. Chem. C* **2014**, 2 (17), 3129.

- (21) Dollinger, F.; Iseke, H.; Guo, E.; Fischer, A.; Kleemann, H.; Leo, K. Electrically Stable Organic Permeable Base Transistors for Display Applications. *Adv. Electron. Mater.* **2019**, *5* (12), 1900576.

- (22) Guo, E.; Dollinger, F.; Amaya, B.; Fischer, A.; Kleemann, H. Organic Permeable Base Transistors Insights and Perspectives. *Adv. Opt. Mater.* **2021**, *9*, 2002058.

- (23) Wu, Z.; Liu, Y.; Guo, E.; Darbandy, G.; Wang, S.-J.; Hübner, R.; Kloes, A.; Kleemann, H.; Leo, K. Efficient and Low-Voltage Vertical Organic Permeable Base Light-Emitting Transistors. *Nat. Mater.* **2021**, *20* (7), 1007–1014.

- (24) Huang, W.; Facchetti, A. Organic Circuits Reach New Heights. *Nat. Electron.* **2021**, *4*, 544.

- (25) Braun, O.; Overbeck, J.; El Abbassi, M.; Käser, S.; Furrer, R.; Olziersky, A.; Flasby, A.; Borin Barin, G.; Sun, Q.; Darawish, R.; Müllen, K.; Ruffieux, P.; Fasel, R.; Shorubalko, I.; Perrin, M. L.; Calame, M. Optimized Graphene Electrodes for Contacting Graphene Nanoribbons. *Carbon* **2021**, *184*, 331–339.

- (26) Braun, O.; Furrer, R.; Butti, P.; Thodkar, K.; Shorubalko, I.; Zardo, I.; Calame, M.; Perrin, M. L. Spatially Mapping Thermal

ı

https://doi.org/10.1021/acsami.2c13148 ACS Appl. Mater. Interfaces XXXX, XXX, XXX—XXX

- Transport in Graphene by an Opto-Thermal Method. Npj 2D Mater. Appl. 2022, 6 (1), 6.

- (27) Schmuck, O.; Beretta, D.; Furrer, R.; Oswald, J.; Calame, M. A Method to Fabricate Nanoscale Gaps in Graphene Nano-Constrictions by Electrical Breakdown. *AIP Adv.* **2022**, *12* (5), 055312.

- (28) Agilent Impedance Measurement Handbook, 4th ed.; Agilent Technologies, 2009.

- (29) Harris, C. R.; Millman, K. J.; van der Walt, S. J.; Gommers, R.; Virtanen, P.; Cournapeau, D.; Wieser, E.; Taylor, J.; Berg, S.; Smith, N. J.; Kern, R.; Picus, M.; Hoyer, S.; van Kerkwijk, M. H.; Brett, M.; Haldane, A.; del Río, J. F.; Wiebe, M.; Peterson, P.; Gérard-Marchant, P.; Sheppard, K.; Reddy, T.; Weckesser, W.; Abbasi, H.; Gohlke, C.; Oliphant, T. E. Array Programming with NumPy. *Nature* **2020**, *585* (7825), 357–362.

- (30) Virtanen, P.; Gommers, R.; Oliphant, T. E.; Haberland, M.; Reddy, T.; Cournapeau, D.; Burovski, E.; Peterson, P.; Weckesser, W.; Bright, J.; van der Walt, S. J.; Brett, M.; Wilson, J.; Millman, K. J.; Mayorov, N.; Nelson, A. R. J.; Jones, E.; Kern, R.; Larson, E.; Carey, C. J.; Polat, İ.; Feng, Y.; Moore, E. W.; VanderPlas, J.; Laxalde, D.; Perktold, J.; Cimrman, R.; Henriksen, I.; Quintero, E. A.; Harris, C. R.; Archibald, A. M.; Ribeiro, A. H.; Pedregosa, F.; van Mulbregt, P.; Vijaykumar, A.; Bardelli, A. P.; Rothberg, A.; Hilboll, A.; Kloeckner, A.; Scopatz, A.; Lee, A.; Rokem, A.; Woods, C. N.; Fulton, C.; Masson, C.; Häggström, C.; Fitzgerald, C.; Nicholson, D. A.; Hagen, D. R.; Pasechnik, D. V.; Olivetti, E.; Martin, E.; Wieser, E.; Silva, F.; Lenders, F.; Wilhelm, F.; Young, G.; Price, G. A.; Ingold, G.-L.; Allen, G. E.; Lee, G. R.; Audren, H.; Probst, I.; Dietrich, J. P.; Silterra, J.; Webber, J. T.; Slavič, J.; Nothman, J.; Buchner, J.; Kulick, J.; Schönberger, J. L.; de Miranda Cardoso, J. V.; Reimer, J.; Harrington, J.; Rodríguez, J. L. C.; Nunez-Iglesias, J.; Kuczynski, J.; Tritz, K.; Thoma, M.; Newville, M.; Kümmerer, M.; Bolingbroke, M.; Tartre, M.; Pak, M.; Smith, N. J.; Nowaczyk, N.; Shebanov, N.; Pavlyk, O.; Brodtkorb, P. A.; Lee, P.; McGibbon, R. T.; Feldbauer, R.; Lewis, S.; Tygier, S.; Sievert, S.; Vigna, S.; Peterson, S.; More, S.; Pudlik, T.; Oshima, T.; Pingel, T. J.; Robitaille, T. P.; Spura, T.; Jones, T. R.; Cera, T.; Leslie, T.; Zito, T.; Krauss, T.; Upadhyay, U.; Halchenko, Y. O.; Vázquez-Baeza, Y. SciPy 1.0: Fundamental Algorithms for Scientific Computing in Python. Nat. Methods 2020, 17 (3), 261-

- (31) Murbach, M.; Gerwe, B.; Dawson-Elli, N.; Tsui, L. Impedance.Py: A Python Package for Electrochemical Impedance Analysis. *J. Open Source Softw.* **2020**, *5* (52), 2349.

- (32) Tsoi, W. C.; James, D. T.; Kim, J. S.; Nicholson, P. G.; Murphy, C. E.; Bradley, D. D. C.; Nelson, J.; Kim, J.-S. The Nature of In-Plane Skeleton Raman Modes of P3HT and Their Correlation to the Degree of Molecular Order in P3HT:PCBM Blend Thin Films. *J. Am. Chem. Soc.* **2011**, *133* (25), 9834–9843.

- (33) Kumar, S.; Kumar, M.; Rathi, S.; Yadav, A.; Upadhyaya, A.; Gupta, S. K.; Singh, A. Study of P3HT/ PCBM Morphology Using Raman Spectroscopy. *AIP Conf. Proc.* **1953**, 100074.

- (34) Graphene, 1st ed.; Rao, C. N. R., Sood, A. K., Eds.; Wiley, 2012.

- (35) Abdou, M. S. A.; Orfino, F. P.; Son, Y.; Holdcroft, S. Interaction of Oxygen with Conjugated Polymers: Charge Transfer Complex Formation with Poly(3-Alkylthiophenes). *J. Am. Chem. Soc.* **1997**, *119* (19), 4518–4524.

- (36) Yu, Y.-J.; Zhao, Y.; Ryu, S.; Brus, L. E.; Kim, K. S.; Kim, P. Tuning the Graphene Work Function by Electric Field Effect. *Nano Lett.* **2009**, 9 (10), 3430–3434.

- (37) Garg, R.; Dutta, N.; Choudhury, N. Work Function Engineering of Graphene. *Nanomaterials* **2014**, 4 (2), 267–300.

- (38) Long, F.; Yasaei, P.; Sanoj, R.; Yao, W.; Král, P.; Salehi-Khojin, A.; Shahbazian-Yassar, R. Characteristic Work Function Variations of Graphene Line Defects. ACS Appl. Mater. Interfaces 2016, 8 (28), 18360–18366.

- (39) Rep, D. B. A.; Huisman, B.-H.; Meijer, E. J.; Prins, P.; Klapwijk, T. M. Charge-Transport in Partially-Ordered Regioregular Poly(3-Hexylthiophene) Studied as a Function of the Charge-Carrier Density. *MRS Proc.* **2000**, *660*, 79.

- (40) Rep, D. B. A.; Morpurgo, A. F.; Klapwijk, T. M. Doping-Dependent Charge Injection into Regioregular Poly(3-Hexylthiophene). *Org. Electron.* **2003**, *4* (4), 201–207.

- (41) Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, 2007.

- (42) Zhong, H.; Xu, K.; Liu, Z.; Xu, G.; Shi, L.; Fan, Y.; Wang, J.; Ren, G.; Yang, H. Charge Transport Mechanisms of Graphene/Semiconductor Schottky Barriers: A Theoretical and Experimental Study. *J. Appl. Phys.* **2014**, *115* (1), 013701.

- (43) Di Bartolomeo, A. Graphene Schottky Diodes: An Experimental Review of the Rectifying Graphene/Semiconductor Heterojunction. *Phys. Rep.* **2016**, *606*, 1–58.

- (44) Knipper, M.; Parisi, J.; Coakley, K.; Waldauf, C.; Brabec, C. J.; Dyakonov, V. Impedance Spectroscopy on Polymer-Fullerene Solar Cells. Z. Naturforsch. A 2007, 62, 490.

- (45) Wang, C.; Zhang, Z.; Pejic, S.; Li, R.; Fukuto, M.; Zhu, L.; Sauve, G. High Dielectric Constant Semiconducting Poly(3-Alkylthiophene)s from Side Chain Modification with Polar Sulfinyl and Sulfonyl Groups. *Macromolecules* **2018**, *51*, 9368.

- (46) Shen, Y.; Gupta, M. C.Investigation of Electrical Characteristics of P3HT:PCBM Organic Solar Cells. In 2012 38th IEEE Photovoltaic Specialists Conference; IEEE: Piscataway, NJ, 2012; pp 002770–002774.

- (47) Scott, J. C.; Malliaras, G. G. Charge Injection and Recombination at the Metal-Organic Interface. *Chem. Phys. Lett.* **1999**, 299 (2), 115–119.

- (48) Scott, J. C. Metal-Organic Interface and Charge Injection in Organic Electronic Devices. J. Vac. Sci. Technol. Vac. Surf. Films 2003, 21 (3), 521–531.

- (49) Sarker, B. K.; Khondaker, S. I. Thermionic Emission and Tunneling at Carbon Nanotube-Organic Semiconductor Interface. *ACS Nano* **2012**, *6* (6), 4993–4999.

- (50) Lou, Y. Charge Transport Characteristics in P3HT:PCBM Organic Blends under Illumination: Influence of Metal Work Functions. *Chem. Phys. Lett.* **2012**, 529, 64–68.

- (51) Mott, N. F.; Gurney, R. W. Electronic Processes in Ionic Crystals; Oxford University Press: London, 1940.

- (52) Tessler, N. Experimental Techniques and the Underlying Device Physics. J. Polym. Sci., Part B: Polym. Phys. **2014**, 52 (17), 1119–1152.

- (53) Meijer, E. J.; Mangnus, A. V. G.; Hart, C. M.; de Leeuw, D. M.; Klapwijk, T. M. Frequency Behavior and the Mott-Schottky Analysis in Poly(3-Hexyl Thiophene) Metal-Insulator-Semiconductor Diodes. *Appl. Phys. Lett.* **2001**, 78 (24), 3902–3904.

- (54) Kim, C. H.; Yaghmazadeh, O.; Tondelier, D.; Jeong, Y. B.; Bonnassieux, Y.; Horowitz, G. Capacitive Behavior of Pentacene-Based Diodes: Quasistatic Dielectric Constant and Dielectric Strength. *J. Appl. Phys.* **2011**, *109* (8), 083710.

- (55) Scheunemann, D.; Järsvall, E.; Liu, J.; Beretta, D.; Fabiano, S.; Caironi, M.; Kemerink, M.; Müller, C. Charge Transport in Doped Conjugated Polymers for Organic Thermoelectrics. *Chem. Phys. Rev.* **2022**, 3 (2), 021309.

- (56) Melitz, W.; Shen, J.; Kummel, A. C.; Lee, S. Kelvin Probe Force Microscopy and Its Application. *Surf. Sci. Rep.* **2011**, *66* (1), 1–27.

- (57) Thakur, A. K.; Mukherjee, A. K.; Preethichandra, D. M. G.; Takashima, W.; Kaneto, K. Charge Injection Mechanism across the Au-Poly(3-Hexylthiophene-2,5-Diyl) Interface. *J. Appl. Phys.* **2007**, *101* (10), 104508.

- (58) Lyon, J. E.; Cascio, A. J.; Beerbom, M. M.; Schlaf, R.; Zhu, Y.; Jenekhe, S. A. Photoemission Study of the Poly(3-Hexylthiophene)/ Au Interface. *Appl. Phys. Lett.* **2006**, *88* (22), 222109.

- (59) Braun, S.; Salaneck, W. R.; Fahlman, M. Energy-Level Alignment at Organic/Metal and Organic/Organic Interfaces. *Adv. Mater.* **2009**, 21 (14–15), 1450–1472.

- (60) Hwang, J.; Wan, A.; Kahn, A. Energetics of Metal-Organic Interfaces: New Experiments and Assessment of the Field. *Mater. Sci. Eng. R Rep.* **2009**, *64* (1–2), 1–31.

# Supporting information

# Charge transport across Au-P3HT-Graphene Van der

# Waals vertical heterostructures

Jacopo Oswald, a,b Davide Beretta, \*\* Michael Stiefel, Roman Furrer, Alessia Romio, Michel Daher Mansour, Dominique Vuillaume, Michel Calame \*\* Alessia Romio, Michel Calame \*\* Alessia Romio, Daher Mansour, Dominique Vuillaume, Michel Calame \*\* Alessia Romio, Michel Calame \*\* Alessia Romio, Daher Mansour, Daher Michael Stiefel, Alessia Romio, Michael Stiefel, Daher Mansour, Daher Michael Stiefel, Daher Michael Stiefel, Michael Stiefel, Daher Mansour, Daher Michael Stiefel, Michael Stiefel, Daher Mansour, Michael Stiefel, Michael Stiefel, Michael Stiefel, Daher Mansour, Michael Stiefel, Michael

E-mail of the corresponding authors.

Davide Beretta: davide.beretta@empa.ch

Michel Calame: michel.calame@empa.ch

### **Contents**

| Fabrication of Au/P3HT/Gr heterostructures  | 2  |

|---------------------------------------------|----|

| FIB/SEM/AFM Characterization                |    |

| Electrical transport characterization       | 7  |

| Kelvin Probe Force Microscopy (KPFM)        | 13 |

| Chip overview                               | 15 |

| Space-charge limited (SCL) current modeling | 16 |

| References                                  | 19 |

<sup>&</sup>lt;sup>a</sup> Empa, Swiss Federal Laboratories for Materials Science and Technology, Transport at Nanoscale Interfaces Laboratory, Überlandstrasse 129, CH-8600, Dübendorf, Switzerland

<sup>&</sup>lt;sup>b</sup> Swiss Nanoscience Institute, University of Basel, Klingelbergstrasse 82, CH-4056, Basel, Switzerland

<sup>&</sup>lt;sup>c</sup> Department of Physics, University of Basel, Klingelbergstrasse 82, CH-4056, Basel, Switzerland

<sup>&</sup>lt;sup>d</sup> Institute of Electronic, Microelectronic and Nanotechnology, Centre National de la Recherche Scientifique, Villeneuve d'Ascq, France.

# Fabrication of Au/P3HT/Gr heterostructures

Figure S1. Fabrication steps of the vertical Au/P3HT/Gr heterostructure. (a) Patterning of the bottom electrodes. The grey dashed lines show the schematic of the section (top) on the optical microscope image (bottom). (b) Preparation of the lift-off resist. (c) P3HT deposition and

patterning. (d) CVD graphene transfer. (e) PMMA removal from graphene. (f) RIE patterning of the graphene top electrode. (g) PMMA/Optical resist removal from graphene. (h) 3D schematic of the device (not in scale)

Figure S1 shows the main fabrication steps of the Au/P3HT/Gr heterostructure, which consists in

### a) Patterning of the bottom electrodes

Ti (5nm) / Au (30 nm) electrodes are fabricated on a 4 inches Si (525  $\mu$ m) / SiO<sub>2</sub> (300 nm) wafer, which is pre-cleaned in oxygen plasma (600 W for 5 min). The electrodes (Ti/Au) are deposited by e-beam physical vapour deposition (EBPVD) and patterned by lift-off in DMSO at 100°C for 30 min. The resist for the lift-off (AZ2020nlof) is spin-coated (4000 rpm for 60 s), exposed to UV light (lamp intensity 11 mW/cm²) through an optical mask, and then developed (AZ726mif, 35 s).

### b) Preparation of the lift-off resist

The chip with pre-patterned electrodes (Si/SiO<sub>2</sub>/Ti/Au) is ultra-sonicated in Acetone for 5 min, rinsed with IPA and blown dry with nitrogen. Then, it is exposed to oxygen plasma at 600 W for 5 min. After HMDS treatment, the chip is coated with a double layer positive optical resist: first, the chip is spin-coated with a LOR5B resist (4000 rpm, 40 s) and backed at 180°C for 5 min. Then, it is spin-coated with an AZ1505 positive resist (4000 rpm, 40 s) and backed at 110°C for 1 min. The device area is exposed for 1.8 s to UV light (lamp intensity 11 mW/cm², dose 20 mJ) through an optical mask. Finally, the exposed resist is developed in AZ400K (400K:DIW, 1:4) for 25 s and rinsed with de-ionized water.

# c) P3HT deposition and patterning

A 100 nm film of P3HT is obtained by spin-coating 10 mg/ml solution of P3HT in chlorobenzene (1000 rpm for 60 s) on the substrate. Subsequently, the P3HT film is patterned by lift-off in DMSO (5 min). The chip is then rinsed in de-ionized water, blown dry with nitrogen and finally annealed overnight at 110°C in vacuum (~1mbar).

# d) CVD graphene transfer

CVD graphene foil (Cu/Gr/PMMA) is placed to float in a copper etchant (Transene CE-100) for 1h, the PMMA layer facing upwards. Once the copper is completely etched (Gr/PMMA), the etchant is removed and replaced with de-ionized water, twice. Then, the foil is transferred to a 10% HCL cleaning solution for 5 min and transferred back to de-ionized water, twice. The

floating graphene foil (Gr/PMMA) is transferred onto the substrate (Si/SiO $_2$ /Au/P3HT/Gr/PMMA) and let dry in air for 1 h.

## e) PMMA removal from graphene

The chip is annealed overnight at 80°C in vacuum (~1 mbar). The top PMMA layer is removed in Acetone (5 min) and the chip annealed again overnight at 80°C in vacuum (~1 mbar).

# f) RIE patterning of the graphene top electrode

The chip is first spin-coated with a 50K PMMA resist (AR-P 632.06, 4000 rpm for 60 s), then with an AZ1505 optical resist (4000 rpm, 40 s) and backed at 110°C for 1 min. The device area is exposed for 1.8 s to UV light (lamp intensity 11 mW/cm2) through an optical mask. The exposed optical resist is developed in AZ400K (400K:DIW, 1:4) for 15 s and rinsed with de-ionized water. Then, RIE is used to remove the first layer of PMMA 50K and graphene (O<sub>2</sub>, 30 sccm, 25 W).

### g) PMMA/Optical resist removal from graphene

The PMMA/Optical resist protecting the graphene electrode is removed with Acetone (1 min), then the chip is rinsed in de-ionized water and blown dry with nitrogen.

### FIB/SEM/AFM Characterization

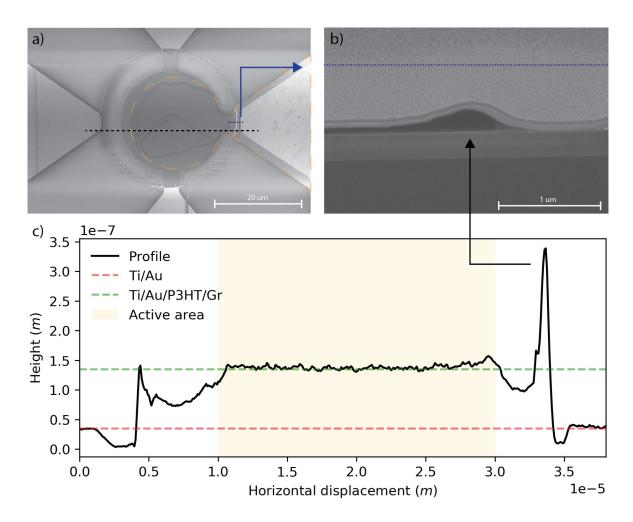

Figure S2. SEM images. (a) Top view of a representative device. The orange dashed line shows the contour of the graphene electrode. The blue dashed line shows the location of the cross-section of (b). (b) Cross-section showing the right edge of P3HT. (c) AFM height profile of the Au/P3HT/Gr stack. The red dashed line show the height of the Ti/Au electrodes, i.e. 35 nm. The green dashed line represent the height of the Tia/Au/P3HT/Gr stack, i.e. 135 nm. From this, the deduced thickness of the P3HT layer is roughly 100 nm.

Figure S2a shows the SEM image and of a representative device. The graphene electrode is clearly visible and contoured with an orange dashed line. Graphene bilayers are distinguishable on the Au side contact. Figure S2b and S2c shows the cross-section corresponding to the dotted blue and

dashed black line, respectively, in Figure S2a. The thickness of the P3HT film in the device center is uniform, while it is not on the device edge, where a higher ring possibly due to capillary/adhesion forces of the P3HT to resist prior to lift-off is observed. Although not desirable, the high edge does not affect the geometry of the device, which is entirely dictated by the region where the bottom and the top electrodes superimpose (active area shown in Figure S2c), and does represent an issue for the graphene electrode since it can easily adapt to the smooth shape of the P3HT edge (Figure S2b).

# **Electrical transport characterization**

Figure S3. J-V traces of a 10  $\mu$ m wide vertical Au/P3HT/Graphene device in ambient, in vacuum and in vacuum after annealing at 110 ° C for 12 h. The inset shows the same traces on log scale.

Figure S4. Graphene in-plane conductivity measurements. The total number of samples shown in the plot is 17. (a) Measured current vs. bias in the devices. Square symbols represent the devices measured in vacuum before annealing. Circles represent the devices measured after annealing. (b) Graphene resistance vs. device area.

Figure S5. J-Vs of five devices per area of the vertical Au/P3HT/Gr devices measured in vacuum after annealing.

Figure S6. Impedance analysis. Modulus (a) and phase (b) of a representative 20  $\mu$ m device for negative applied bias. The R||C system cut off frequency shifts above 1MHz for negative applied bias, where the resistance drops and becomes comparable to the graphene series resistance.

The dielectric constant  $\epsilon_r$  of P3HT for different devices is calculated using the parallel plate capacitor equation (Eq. S1). The results are shown in Table 1.

$$C = \epsilon_0 \epsilon_r \frac{A}{t}$$

Eq. S1

Where  $\epsilon_0$  is the vacuum permittivity, A is the device area and t the device thickness. The propagation errors at first order is calculates as shown in Eq. S2.

$$\Delta \epsilon_r = \frac{1}{\epsilon_0} \sqrt{\left(\frac{t}{A} \Delta C\right)^2 + \left(\frac{C}{A} \Delta t\right)^2 + \left(\frac{Ct}{A^2} \Delta A\right)^2}$$

Eq. S2

Where  $\Delta C$  is the fit error,  $\Delta t = 30$  nm is the estimation of the thickness error and  $\Delta A = \pi \left( (d_{Au} - d_{Gr})/2 \right)^2$  is the estimation of the area error. Where  $d_{Au}$  and  $d_{Gr}$  are the diameter of the gold and graphene electrodes, respectively.

Figure S7. SCL and TE models fitting for different device with diameters: (a-b) 5  $\mu$ m, (c-d) 15  $\mu$ m, (e-f) 25  $\mu$ m, and (g-h) 50  $\mu$ m. Table 1 shows the statistic of fitting parameters. (a-b) In Fig. S2, one can observe a slightly thicker organic layer around the edge of the devices active area. The latter could have affect the actual average thickness of small devices. To take this effect into account, the thickness of the 5  $\mu$ m and 10  $\mu$ m device was set to 130 nm and 120 nm. For all the other devices, where the edge area can be neglected compared to the whole device area, the thickness was set to 100 nm.

| A** (Aı | m-2K-2) | Φ (eV)  |         |  |  |  |

|---------|---------|---------|---------|--|--|--|

| Gr/P3HT | Au/P3HT | Gr/P3HT | Au/P3HT |  |  |  |

| 2       | 18      | 0.29    | 0.25    |  |  |  |

| 2       | 22      | 0.29    | 0.25    |  |  |  |

| 7       | 18      | 0.32    | 0.25    |  |  |  |

| 7       | 22      | 0.32    | 0.25    |  |  |  |

Figure S8. (Left)  $A^{**}$  as a function of voltage extracted from temperature dependent IV measurements on the representative 5  $\mu$ m device.  $A^{**}$  in the range from -10 V to -7 V is neglected because of the graphene series resistance. Similarly,  $A^{**}$  in the range from -4 V to 4 V is also neglected because of instrumentation sensitivity. (Right) Potential barrier height calculated for  $A^{**}$  values spanning the whole range (ca. 18-22  $Am^{-2}K^{-2}$  for Au/P3HT and 2-7  $Am^{-2}K^{-2}$  for Gr/P3HT).

### **Kelvin Probe Force Microscopy (KPFM)**

Figure S9. (a) CPD image of a 50 µm device with the different parts (bottom Au electrode, P3HT film and top graphene electrode) indicated. (b) CPD profile along the white line shown in (a) and histograms of the CPD values measured on Au, Gr and P3HT. The black lines are the fits with a Gaussian distribution, the mean CPD values are given in the figure (FWHM of 14 meV in all cases).

Figure S9a shows a Contact Potential Difference (CPD) image of a 50  $\mu$ m device, where the top Gr electrode, the P3HT and the bottom Au electrode are clearly distinguishable. A CPD profile along the white line shown in Figure S9a reveals (Figure S6b) the variations of the CPD for the Au electrode, the P3HT film and the graphene electrode. CPD histograms recorded locally on the Au, P3HT and Gr are shown in the right panel of Figure S9b. Therefore, the deduced potential barrier at the interfaces are  $\Phi_{B,Au/P3HT} = 0.10 \pm 0.013$  eV and  $\Phi_{B,Gr/P3HT} = 0.16 \pm 0.013$  eV. These values show a similar trend as obtained from the I-V measurements ( $\Phi_{B,Gr/P3HT} > \Phi_{B,Au/P3HT}$ ) with the same built-in potential (60 meV). However, the KPFM barrier heights are

smaller. This can be ascribed to the fact that the I-V measurements were done in vacuum after annealing. In this latter case, the obtained potential barriers at the interfaces are larger than the ones obtained from KPFM measurements done in air and ambient condition.

# Chip overview

| ,    | Α.   | A B   | С     | D     | Е      | F     | G     | Н     | I     | J      | K      | GE    | ME    |

|------|------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|-------|-------|

|      | A    | D     | C     | D     | E      | Г     | G     | п     | 1     | J      |        | diam. | diam. |

| A    | AA   | AB    | AC    | AD    | AE     | AF    | AG    | АН    | AI    | AJ     | AK     | 5     | 7     |

| В    | BA   | BB    | BC    | BD    | BE     | BF    | BG    | ВН    | BI    | BJ     | BK     | 5     | 7     |

| С    | CA   | СВ    | CC    | CD    | CE     | CF    | CG    | СН    | CI    | CJ     | CK     | 5     | 7     |

| D    | DA   | DB    | DC    | DD    | DE     | DF    | DG    | DH    | DI    | DJ     | DK     | 10    | 12    |

| Е    | EA   | EB    | EC    | ED    | EE     | EF    | EG    | EH    | EI    | EJ     | EK     | 10    | 12    |

| F    | FA   | FB    | FC    | FD    | FE     | FF    | FG    | FH    | FI    | FJ     | FK     | 15    | 17    |

| G    | GA   | GB    | GC    | GD    | GE     | GF    | GG    | GH    | GI    | GJ     | GK     | 15    | 17    |

| Н    | HA   | HB    | HC    | HD    | HE     | HF    | HG    | НН    | HI    | HJ     | HK     | 20    | 22    |

| I    | IA   | IB    | IC    | ID    | ΙE     | IF    | IG    | IH    | II    | IJ     | IK     | 20    | 22    |

| J    | JA   | JB    | JC    | JD    | JE     | JF    | JG    | JH    | JI    | JJ     | JK     | 20    | 22    |

| K    | KA   | KB    | KC    | KD    | KE     | KF    | KG    | KH    | KI    | KJ     | KK     | 25    | 27    |

| L    | LA   | LB    | LC    | LD    | LE     | LF    | LG    | LH    | LI    | LJ     | LK     | 25    | 27    |

| M    | MA   | MB    | MC    | MD    | ME     | MF    | MG    | МН    | MI    | MJ     | MK     | 30    | 32    |

| N    | NA   | NB    | NC    | ND    | NE     | NF    | NG    | NH    | NI    | NJ     | NK     | 30    | 32    |

| О    | OA   | OB    | OC    | OD    | OE     | OF    | OG    | ОН    | OI    | OJ     | OK     | 50    | 52    |

| P    | PA   | PB    | PC    | PD    | PE     | PF    | PG    | PH    | PI    | PJ     | PK     | 50    | 52    |

| Q    | QA   | QB    | QC    | QD    | QE     | QF    | QG    | QH    | QI    | QJ     | QK     | 50    | 52    |

| Type | Open | Short | Stack | Stack | Stack. | Stack | Stack | Stack | Stack | Bridge | Bridge |       |       |

Table S1. Overview of the entire chip. Green cases show the working devices, while the red cases are the not working ones. Roughly, 50% of the chip devices are working and show the same J-V behavior of the device shown in Fig. 5.

# Space-charge limited (SCL) current modeling

The analytical solution of the space-charge limited (SCL) current is here reported for convenience, as proposed in previous works.<sup>1–4</sup>

1) From the continuity equation:

$$J = qn\mu E(x) + qD\frac{\partial n}{\partial x}$$

Eq. S3

and the Poisson equation:

$$\frac{\partial}{\partial x}E(x) = -\frac{q}{\epsilon}n(x)$$

Eq. S4

2) Assuming that the diffusion current is negligible<sup>3</sup>:

$$J = qn\mu E(x) = -\epsilon \mu E(x) \frac{\partial E(x)}{\partial x}$$

Eq. S5

3) Integrating Eq. S5:

$$\int_0^x J d\vartheta = J \int_0^x d\vartheta = \epsilon \mu \int_0^x E(\vartheta) \frac{\partial E(\vartheta)}{\partial \vartheta} d\vartheta$$

$$Jx + K = \frac{1}{2} \epsilon \mu E(x)^2$$

Eq. S6

where *K* is a constant.

4) Solving Eq. S6 for the electrical field E(x):

$$E(x) = \sqrt{\frac{2J}{\epsilon\mu}(x + K')}$$

Eq. S7 where  $K' = \frac{K}{I}$ .

5) K' is found using the boundary conditions at the injecting contact (x = 0). Defining  $n|_{x = 0} = N_0$  and applying the Dirichlet boundary condition  $\frac{dE(x)}{dx}|_{x = 0} = \frac{qN_0}{\epsilon}$ , K' is

$$K' = \frac{J\epsilon}{2\mu N_0^2 q^2}$$

Eq. S8

6) Then, plugging K' in Eq. S7:

$$E(x) = \sqrt{\frac{2J}{\epsilon\mu} \left( x + \frac{J\epsilon}{2\mu N_0^2 q^2} \right)}$$

Eq. S9

$$E(0) = \sqrt{\frac{J^2}{\mu^2 N_0^2 q^2}} = \frac{J}{\mu N_0 q}$$

7) Finally, the voltage associated to the current J in the semiconductor of length L is given by:

$$V = -\int_0^L E(x)dx = \sqrt{\frac{8J}{9\epsilon\mu}} \left[ (L + K')^{\frac{3}{2}} + K'^{\frac{3}{2}} \right]$$

Eq. S10

8) The current-voltage relation is found solving Eq. S10 for the current. Two solutions are found:

$$J = \frac{9}{8} \epsilon \mu \frac{V^2}{L^3} \qquad \text{for K'} << L$$

Eq. S11

$$J = q\mu N_0 \frac{V}{L} \qquad \text{for K'} >> L$$

Eq. S12

J is the current density driven through the device by applying the bias V. The other parameters are defined by the semiconductor properties.  $N_0$ , that it the charge carrier density at the interface, is defined by the density of states of the semiconductor  $N_{\text{DOS}}$  and by the potential barrier height  $\Phi_B$  at the interface:

$$n|_{x=0} = N_0 = N_{DOS}e^{-\frac{E_{HOMO} - \Phi_M}{kT}} = N_{DOS}e^{-\frac{\Phi_B}{kT}}$$

Eq. S13

The case of a 20  $\mu$ m representative device shown in Fig. 5 is considered.  $N_0$  at the Gr/P3HT interface can be measured by (i) extracting the hole mobility of P3HT using Eq. S11 for negative biases and (ii) applying Eq. S12 in the linear region for positive biases. The obtained charge carrier density at the Gr/P3HT interface is  $N_0 = 1.1 \times 10^{15}$  cm<sup>-3</sup>.

Then, using the potential barrier height (0.31 eV, extracted from TE model) and  $N_0$  at the Gr/P3HT interface,  $N_{DOS}$  of P3HT can be calculated:  $N_{DOS} = 2.4 \times 10^{20}$  cm<sup>-3</sup>. Finally,  $N_0$  at the Au/P3HT can be computed using Eq. S11 and the potential barrier height (0.25 eV). Obtained charge carrier density at the Au/P3HT interface is  $N_0 = 1.2 \times 10^{16}$  cm<sup>-3</sup>. It is worth observing that the image-charge induced lowering of potential barrier is not considered.  $N_0$  may depend on the applied bias and be larger than the estimated value<sup>1</sup>. Figure S10 shows K' vs. J, i.e. the charge carrier density and the electrical field across the stack for the two different boundary conditions.

Figure S10. Space-charge limited current model calculated in the current density range of the measured devices. (a) K' vs. J showing the two different solution of the space-charge limited current model (Eq. S9 and S10). The horizontal red line shows L = 100 nm of Eq. S8. Orange line corresponds to  $N_0 = 1.1 \times 10^{15}$  cm<sup>-3</sup> (K' > L) and blue line to  $N_0 = 1.2 \times 10^{16}$  cm<sup>-3</sup> (K' < L). The vertical red line show the current density used to calculate n(x) and E(x) of plot (b) and (c). (b) Charge carrier density (b) and electrical field (c) across the across the vertical for a current density  $J = 100 \text{ Am}^{-2}$ .

## References

- (1) Tessler, N. Experimental Techniques and the Underlying Device Physics. *J. Polym. Sci. Part B Polym. Phys.* **2014**, *52* (17), 1119–1152. https://doi.org/10.1002/polb.23550.

- (2) Sze, S. M.; Ng, K. K. *Physics of Semiconductor Devices*, 3rd ed.; Wiley-Interscience: Hoboken, N.J, 2007.

- (3) Schilling, R. B.; Schachter, H. Neglecting Diffusion in Space-Charge-Limited Currents. *J. Appl. Phys.* **1967**, *38* (2), 841–844. https://doi.org/10.1063/1.1709422.

- (4) Mott, N. F.; Gurney, R. W. *Electronic Processes in Ionic Crystals*; Oxford University Press: London, 1940.