# Predictive gate ageing-laws of SiC MOSFET under repetitive short-circuit stress

Frédéric Richardeau, Yazan Barazi

# ▶ To cite this version:

Frédéric Richardeau, Yazan Barazi. Predictive gate ageing-laws of SiC MOSFET under repetitive short-circuit stress. Microelectronics Reliability, 2022, pp.114706. 10.1016/j.microrel.2022.114706 . hal-03791964

HAL Id: hal-03791964

https://hal.science/hal-03791964

Submitted on 29 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Predictive gate ageing-laws of SiC MOSFET under repetitive short-circuit stress

F. Richardeau<sup>a,\*</sup>, Y. Barazi<sup>a,b</sup>

<sup>a</sup> Laplace, University of Toulouse, CNRS, Toulouse INP, UT3, France <sup>b</sup> IRT Saint-Exupéry, Toulouse, France

Abstract This paper proposes SiC MOSFET gate ageing-laws under repetitive short-circuit stress. Based on analytical studies, physical forms and preconditioning data, numerical fitting based on stress variables  $\Delta T_{j}$ ,  $T_{Pulse\ Gate\ Damage\ \%}$  and  $E_{sc}$  is proposed. Accuracy and prediction capabilities of ageing-laws have been evaluated and compared. Resulting in suggesting a new ageing-law based on  $\Delta T_{Al\ Top}$  metal-source. This one gives the best fitting accuracy. Finally, the ageing-law based directly on the short-circuit energy  $E_{sc}$  appears to have the best in prediction capability.

#### 1. Introduction

SiC MOSFETs increase the power converter efficiency [1]. Today, it is mandatory to guarantee operational level of reliability and robustness capabilities in accidental extreme operation. However, due to a higher current density and shorter channels in planar structure, the short-circuit (SC) withstanding time (T<sub>SCWT</sub> @2/3 x V<sub>DSmax</sub>) of SiC MOSFETs is lower than silicon devices one, within  $t_{SCWT} = 2\mu s$  instead of  $t_{SCWT} = 10\mu s$  for Si IGBTs. Many efforts have been recently addressed to study dedicated SiC MOSFETs failure mechanisms under short circuit tests [2,3]. High temperature variations lead to have cumulated thermo-mechanical stresses around the gate-region and Al source-metal. Those often lead for the SiC MOSFET not being able to exceed the threshold of 1000 repeated short-circuit cycles, derived from the silicon standard. The prediction of the number of short-circuit cycles allowed by the SiC MOSFET, before its gate is damaged, is a fact that is not well known today and yet it is of prime concern in the operational phase. In [4], a Weibull distribution and a direct  $\Delta T_i$  Coffin-Manson ageing-law were proposed but under reduced drain-source voltage bias 200V and using a gate-trench device. In [5], authors experimentally confirm the gate-ageing dependence with  $\Delta T_i$  stress but the Coffin-Manson parameters were not fitted and the prediction capability was not proposed.

In this paper, repetitive SC study has been led in order to model and to propose a set of predictive analytical gate-ageing laws on a SiC MOSFET device. Proposed fitted laws have been evaluated in terms of accuracy, practicality and prediction capability for a shorter SC stress than ones used in the fitting operation. The paper is organized as fellow: in §2. SC test bench and methodology are presented; in §3. dedicated thermal simulations, modelling and prediction tests are analyzed; finally, in the conclusion, best accurate and predictive laws are highlighted.

## 2. Repetitive short-circuit stress

### 2.1. DUT and test bench used

This study is a continuous analysis of the second-Microelectronics<sup>TM</sup> generation STdevice 1200V, 75mΩ, 33A @ $T_{Case} = 25$ °C planar-gate type device, in an automotive-grade 3-lead TO247 case [6, 7]. The device was placed under extreme shortcircuit mode, which is known as Hard Switch Fault HSF. The DUT (Device Under Test) was placed on the low side of a phase-leg power test bench presented in Fig. 1. A copper clip is used at the highside socket to replicate the SC behavior. A 10µF-720V decoupling capacitor is soldered closest the phase-leg including a 2nH coaxial shunt. The total stray inductance of the equivalent power loop is 15nH. With less than 2 joules stored, there is no risk of case explosion, allowing relevant failure analysis to be performed on the chips. Tank capacitors are used upstream to provide instantaneous short-circuit power for 100µs max. (200J). To secure this stage, a fast IGBT electronic breaker (800ns) and two fast CMS fuse-bars are used. Low voltage signals (as

F.Richardeau et al. - Microelectronics Reliability journal - Elsevier 2022 - https://doi.org/10.1016/j.microrel.2022.114706

$V_{Drv}$  and  $V_{GS})$  are measured with self-compensated voltage probes (Tektronix TPP1000 - 300V, 1GHz bandwidth). High voltages (as  $V_{DS})$  are typically measured with a probe (Tektronix TPP0850 - 1000V, 800MHz bandwidth). The current  $(I_{DS})$  is measured through a 2GHz coaxial shunt.  $I_{GS}$  waveform is traced on the scope by the operation :  $(V_{Drv}-V_{GS}) \, / \, R_{Gate}.$

Fig. 1. Secure SC test-bench: max 600V, 400A, 100μs, 125°C.

#### 2.2. Set-up, methodology and experimental results

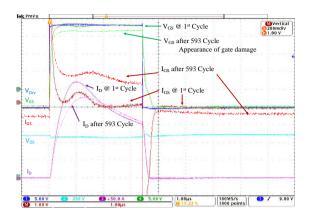

Previous work [6] have shown for the same device, under the same power bench and under the same  $(V_{DS} = 600V, V_{Drv} = -5V/18V)$  $T_{Case} = 25$ °C), that average  $T_{Pulse\ Gate\ Damage} = 4.9 \mu s$ with a safe gate damage-mode. In this paper, a repetitive short-circuit test is applied including a turn-off of 5s between each pulse. Different percentages of T<sub>Pulse GD</sub> have been used, giving T<sub>Pulse</sub> <sub>GD X%</sub>: 50%, 60%, 70%, 80% and 90% respectively equal to a pulse width T<sub>Pulse</sub>: 2.5 µs, 3 µs, 3.5 µs, 4 µs and 4.5 µs. Three devices have been chosen for each percentage. Fig. 2 presents for 70% x T<sub>Pulse GD</sub>; a behavior comparison between the first SC cycle and the 593th SC gate-damage cycle. A permanent gateleakage and a gate-source voltage depolarization by the external gate-resistor clearly appears. In all stresses, drain-source voltage was limited to 600V to avoid possible thermal runaway catastrophic drain-source failure-mode.

$$\begin{split} Fig.~2.~(V_{GS},\,V_{Drv},\,I_{GS},\,V_{DS},\,I_{D})~Oscilloscope~waveforms\\ &~under~repetitive~SC~@70\%~of~T_{Pulse~GD},\\ &~T_{Pulse\_GD\_70\%}=3.5\mu s.~@V_{DS}=600V,\,R_{G}=47\Omega,\\ &~V_{Drv}=-5V/18V. \end{split}$$

#### 3. Gate-ageing modelling and prediction

#### 3.1. Transient thermal simulation

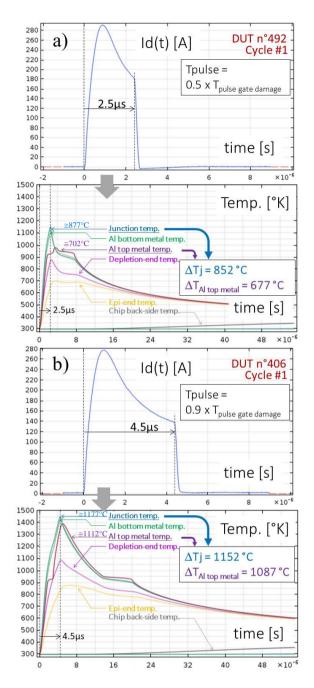

In order to prepare the modelling step, all stress points from §2 has been thermally simulated to extract junction temperatures  $\Delta T_i$  and Al top sourcemetal  $\Delta T_{Al Top Metal}$  temperature variations on the top of the gate-region, where the damage is developed. A dedicated electro-thermo-metallurgical developed by authors [8] is re-used. This one considers the temperature dependency of thermal conductivity and mass heat of the SiC from [10] as defined in (1) and (2), as well the solidus-liquidus phase transition of the upper Al layer from [11]. Using Comsol<sup>TM</sup> software, I<sub>DS</sub>(t) waveforms from §2.2 is used as input data of the model with  $V_{DS} = 600 \text{ V}$ . Fig. 3 a) presents a thermal simulation under the shortest pulse time  $T_{pulse} = 2.5 \mu s$  (50%), the figure is supported by its respective I<sub>D</sub>(t) waveform. It shows that the Al top source-metal temperature just exceeds the solidus-liquidus phase transition band (933K  $\pm$  30K) for 2 $\mu$ s. Conversely, Fig. 3 b) presents a thermal simulation under the longest pulse time  $T_{pulse} = 4.5 \mu s$  (90%). The figure is supported by its respective I<sub>D</sub>(t) waveform. In this last extreme stress test, it shows that the Al top source-metal temperature is greatly above the solidliquid phase transition band for 11µs. It can be noted that the ILD-SiO<sub>2</sub> mechanical strength temperature around 600K [9] is clearly exceeded in all these cases. Therefore, all these results confirm the existence of favorable mechanical and metallurgical conditions for the gate-region to be subject to

Fig. 3. Transient thermal simulation in short-circuit stress, a) Shortest pulse 2.5 $\mu$ s, b) Longest pulse 4.5 $\mu$ s.

@ $V_{DS} = 600V$ ,  $V_{Drv} = -5V/+18V$ ,  $R_{Gate} = 47\Omega$ ,  $T_{Case} = T_{Amb}$

thermo-mechanical ageing.

$$\lambda_{SiC} = (-0.0003 + 1.05 \ 10^{-5} T)^{-1}$$

(1)

$$Cp_{SiC} = 925.65 + 0.3772 T$$

$$- 7.9259 10^{-5} T^{2}$$

$$- 3.946 10^{7} T^{-2}$$

(2)

With [10]:  $\lambda_{SiC}$ , SiC thermal conductivity;  $Cp_{SiC}$ , SiC heat capacity. Note that Al layer solidus – liquidus phase transition thermal laws  $(T_s \rightarrow_l)$  are much more non-linear and complex in form and are described in [11] for  $\lambda_{Al}(T_s \rightarrow_l)$  and  $Cp_{Al}(T_s \rightarrow_l)$ . A latent heat of melting  $Lf_{Al} = 397kJ/kg$  over a  $\Delta T_s \rightarrow_l$  range of 30K is considered to allow the convergence of the model.

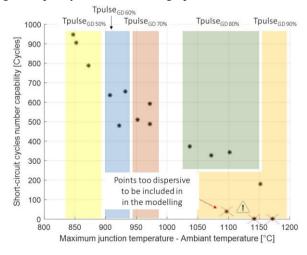

#### 3.2. Distribution $Nb_{cycles}(\Delta Tj)$ results

Fig. 4 shows an overview of the cycling results distribution from §2.2, versus the temperature variation  $\Delta T_j$  simulated by the transient thermal model in §3.1. Temperature variation is defined by:  $\Delta T_j = T_{jmax} - T_{amb}$ . The general shape of the scattered points reveals a non-linear behavior specific to ageing effect. However, three of the four stress points @T<sub>Pulse GD 90%</sub> are too far apart to be considered in the fitting. Indeed, this high level of thermo-mechanical stress can cause early damage in a very small number of cycles on weak components. Only one point [ $\Delta T_j = 1152$ °C, Nb<sub>cycles</sub> = 180]; which is not off-trend; is retained as it greatly improves the global quality of the next fitting operation.

Fig. 4. Scatter plotting of §2. results versus  $\Delta T_{\rm j}$  @ $V_{\rm DS}$  = 600V,  $V_{\rm Drv}$  = -5V/+18V,  $R_{\rm Gate}$  = 47 $\Omega$ .

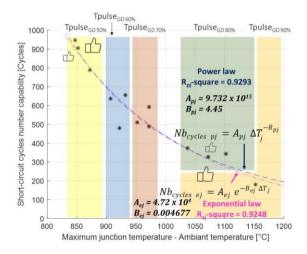

#### 3.3. $Nb_{cycles}(\Delta T_i)$ fitting law

Two general ageing-laws have been numerically fitted from the scatter plotting in Fig. 4; a power law (1) as a Coffin-Manson form and an exponential law (2). These two laws are based on offset parameters  $(A_{pj}$  and  $A_{ej})$  and shape factor parameters  $(B_{pj}$  and  $B_{ej})$ . These coefficients have been adjusted using a Levenberg-Marquardt optimization algorithm in Matlab<sup>TM</sup>. This algorithm is known and used for its robustness and ability to find a global minimum even with spread initial conditions. The quality of the fitting will be given by the coefficient of determination R-square.

$$Nb_{cycles\ pj} = A_{pj}\ \Delta T_i^{-B_{pj}} \tag{3}$$

$$Nb_{cycles\ ej} = A_{ej}\ e^{-B_{ej}\ \Delta T_j} \tag{4}$$

Results of the fitting using stress variable  $\Delta T_j$  are given in Fig. 5. Both laws fit very well and are very close, respectively  $R_{pj\text{-}Square} = 0.9293$  for the power law and  $R_{ej\text{-}square} = 0.9248$  for the exponential law. It can be observed that the power law fits slightly better around stress point  $@T_{Pulse\ GD\ 50\%}$ , whereas the exponential law fits slightly better when approaching stress point  $@T_{Pulse\ GD\ 90\%}$ . The power law is therefore more interesting to keep for predicting the cycles number  $@T_{Pulse\ GD\ X\%} < @T_{Pulse\ GD\ 50\%}$ .

Fig. 5. Nb<sub>cycles</sub>( $\Delta T_j$ ) fitting laws and parameters @V<sub>DS</sub> = 600V, V<sub>Drv</sub> = -5V/+18V, R<sub>Gate</sub> = 47 $\Omega$ .

3.4.  $Nb_{cycles}(T_{Pulse})$ ;  $Nb_{cycles}(E_{sc})$ ;  $Nb_{cycles}(\Delta T_{Al\ Top\ Metal})$  fitting laws and synthesis

Three others ageing-laws, based on power and exponential forms, have been evaluated in terms of accuracy, using variables pulse time  $T_{Pulse\ GD\ \%}$ , SC energy  $E_{sc}$  and  $\Delta T_{Al\ Top\ Metal}$  in place of variable  $\Delta T_j$  in (1) and (2).

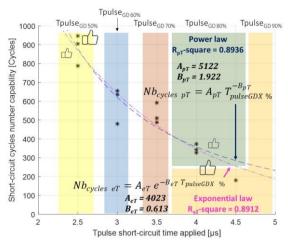

Stress variable  $T_{Pulse\ GD\ \%}$  is simply and directly based on the gate-pulse signal. Scatter plotting versus  $T_{Pulse\ GD\ \%}$  and results of the fitting are illustrated in Fig. 6. With  $R_{pT-Square}=0.8936$  for the power law and  $R_{eT-square}=0.8912$  for the exponential law, the average fitting quality is 4% slightly lower than the fitting quality with variable  $\Delta T_j$ . In addition, with  $B_{pT}\cong B_{pTj}/2$  we verify physically that thermal diffusion follows a law close to the square root of time.

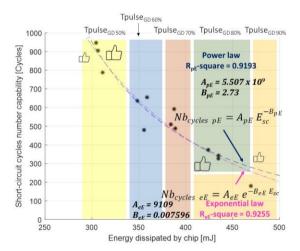

SC energy variable  $E_{sc}$  can be "quite easily measured" from the scope or post-processed from the recorded  $I_{DS}(t)$  and  $V_{DS}(t)$  waveforms, without use of complex transient thermal simulation. Scatter plotting versus  $E_{sc}$  and results of the fitting are illustrated in Fig. 7. With  $R_{pE-Square} = 0.9193$  for the power law and  $R_{eE-square} = 0.9255$  for the exponential law, the average fitting quality is only 0.5% lower than the fitting quality with variable  $\Delta T_j$ . Thus, these gate ageing-laws promise to be a good compromise between precision and "easy to use".

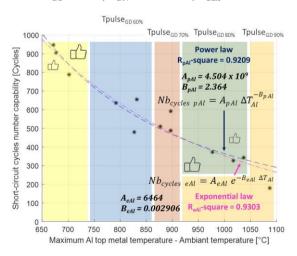

In contrast we suggest introducing in this study a new stress variable  $\Delta T_{Al\ Top\ Metal}$  calculated from the transient thermal simulation described in §3.1: indeed, as illustrated in Fig. 3 a) and b), the gatedamage mode seems to be correlated to the existence of a solidus - liquidus phase transition of the Al top source-metal layer combined with a mechanical strength of the ILD around the gate fingers. The scatter plotting versus  $\Delta T_{Al\_Top\_Metal}$  and results of the are illustrated in Fig. 8.  $R_{pAl \ square} = 0.9209$ for the power  $R_{eAl \, square} = 0.9303$  for the exponential law, the average fitting quality is only 0.15% lower than the fitting quality with variable  $\Delta T_j$ . However, note specifically that R<sub>eAl-square</sub> value is the best of all others R-square values, showing that the variable  $\Delta T_{Al\_Top\_Metal}$  combined with an classical exponential law provide the best fitting at the expense of greater complexity of use because such variable requires a transient thermal simulation.

Fig. 6.  $Nb_{cycles}(T_{Pulse~GD~\%})$  fitting laws and parameters @ $V_{DS}=600V$ ,  $V_{Drv}=-5V/+18V$ ,  $R_{Gate}=47\Omega$ .

Fig. 7. Nb<sub>cycles</sub>( $E_{sc}$ ) fitting laws and parameters @V<sub>DS</sub> = 600V, V<sub>Drv</sub> = -5V/+18V, R<sub>Gate</sub> = 47 $\Omega$ .

Fig. 8. Nb<sub>cycles</sub>( $\Delta T_{Al\_Top\_Metal}$ ) fitting laws and parameters @V<sub>DS</sub> = 600V, V<sub>Drv</sub> = -5V/+18V, R<sub>Gate</sub> = 47 $\Omega$ .

In summary, Table 1 gives the ranking fitting performance considering the impact of all described variables. As previously analyzed,  $\Delta T_{Al\_Top\_Metal}$  variable with exponential law provides the best fitting. This result can be explained by considering the temperature variation closest to the gate-damage region. However, the use of this variable requires a transient thermal simulation of the chip. Conversely, the  $\Delta T_{Pulse~GD~X\%}$  variable gives the worst results but does not require simulation.

Table 1 Quality of the gate-ageing laws fitting based on R-square performance.

| Ranking  | R-square<br>and law type            | Ranking   | R-square and law type                   |

|----------|-------------------------------------|-----------|-----------------------------------------|

| 1 (best) | 0.9303<br>exp. ΔT <sub>Al Top</sub> | 5         | 0.9209 pow. $\Delta T_{Al\ Top}$        |

| 2        | $0.9293$ pow. $\Delta T_j$          | 6         | 0.9193<br>pow. E <sub>sc</sub>          |

| 3        | 0.9255<br>exp. E <sub>sc</sub>      | 7         | 0.8936<br>pow. ΔT <sub>Pulse GD %</sub> |

| 4        | 0.9248<br>exp. ΔT <sub>j</sub>      | 8 (worst) | 0.8912<br>exp. ΔT <sub>Pulse GD %</sub> |

# 3.5. Prediction capability test

All previous laws are now subject to a prediction test with  $\Delta T_{Pulse\ GD\ X\%} < 2.5 \mu s$ . Indeed, under low pulse duration, the cycling capability becomes high, which makes experimentation complicated and expensive. The prediction capability then becomes useful. A first test considering  $\Delta T_{Pulse\ GD\ 40\%} = 2\mu s$  did not allow to yield experimentally a gate-damage in less than 3000 cycles. Indeed, on this low stress level the temperature variation does not reach the onset of the solidus-liquidus phase transition. Hence, a change in the damage-mode and ageing-laws are to be expected such as the Al grain boundaries reconstruction. In order to keep the initial damagemode on the gate-region as the basis for the proposed modelling,  $\Delta T_{Pulse\ GD\ 45\%} = 2.25 \mu s$  is retained. This stress level leads experimentally to  $Nb_{cycles} = 1270$ . On this stress point, all new variables  $\Delta T_i$ ,  $E_{sc}$  and  $\Delta T_{Al\ Top\ Metal}$  are calculated or simulated in Comsol<sup>TM</sup> and injected in all the proposed ageing-laws in §3.3 and §3.4 to compare their prediction capability with experience. Results and ranking are given in Table 2.

Table 2 Prediction performance of the fitted gate ageinglaws.

| T <sub>Pulse_GD_45%</sub> - Prediction performance<br>Nb cycles target (experimentation) = 1270 |                                 |              |  |

|-------------------------------------------------------------------------------------------------|---------------------------------|--------------|--|

| Ranking                                                                                         | Law type                        | [Min, Max]*  |  |

|                                                                                                 | and variable                    | prediction   |  |

|                                                                                                 |                                 | Nb cycles    |  |

| 1 (best)                                                                                        | pow. Esc                        | [1043, 1391] |  |

| 2                                                                                               | exp. E <sub>sc</sub>            | [1006, 1254] |  |

| 3                                                                                               | pow. $\Delta T_j$               | [986, 1228]  |  |

| 4                                                                                               | exp. $\Delta T_j$               | [964, 1163]  |  |

| 5                                                                                               | pow. $\Delta T_{Al Top}$        | [1050, 1090] |  |

| 6                                                                                               | exp. $\Delta T_{Al Top}$        | [1009, 1039] |  |

| 7                                                                                               | pow. $\Delta T_{Pulse\ GD\ \%}$ | 1077         |  |

| 8 (worst)                                                                                       | exp. $\Delta T_{Pulse GD \%}$   | 1012         |  |

- \*: considering  $I_{DSmax}$  at 1st cycle and  $I_{DSmin}$  at last cycle due to  $V_{GSth}$  slight drift during cycling test.

- The  $T_{Pulse\;GD\;X\%}$  based law gives a confirmation of the worst estimation, as was found in the fitting ranking based on R-square.

- The power form based on  $E_{sc}$  is the best in prediction @T<sub>Pulse GD 45%</sub> although it is slightly less good in global fitting quality for T<sub>Pulse GD %</sub> > 45%.

- Temperature laws ( $\Delta T_j$ , and  $\Delta T_{Al\ Top\_Metal}$ ) are acceptable and can be clearly used. They allow cycles prediction with less than 20% deviation compared to the experimental result.

#### 4. Conclusion

SiC MOSFET planar gate-ageing laws in repetitive short-circuit stress are proposed. Stress variables  $\Delta T_{j,}$   $T_{Pulse\ Gate\ Damage\ \%}$  and  $E_{sc}$  are considered. Based on analytical physical forms, preconditioning data and numerical fitting, accuracy and prediction capability have been evaluated and compared. A new ageing-law based on stress variable  $\Delta T_{Al\_Top}$  metal-source is suggested. This one gives the best fitting accuracy but requires a transient thermal simulation in addition of the experimental test. Finally, the ageing-law based directly on the practical short-circuit energy  $E_{sc}$  appears the best suited in prediction capability without requiring a post-simulation process.

#### 5. References

- [1] F. Wang and Z. Zhang. Overview of Silicon Carbide Technology: Device, Converter, System, and Application. Power Electr. and Appl. Trans on. CPSS, vol. 1, no. 1, pp. 13-32, Dec. 2016. doi: 10.24295/CPSSTPEA.2016.00003.

- [2] L. Ceccarelli, P.D. Reigosa, F. Iannuzzo, F. Blaabjerg. A survey of SiC power MOSFETs short-circuit robustness and failure mode analysis. Microelec. Rel., vol. 76–77, 2017, pp.: 272-276. doi.org/10.1016/j.microrel.2017.06.093.

- [3] Romano, G.; Fayyaz, A.; Riccio, M.; Maresca, L.; Breglio, G.; Castellazzi, A.; Irace, A. A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 978–987. doi: 10.1109/JESTPE.2016.2563220.

- [4] C. Unger and M. Pfost. Particularities of the Short-Circuit Operation and Failure Modes of SiC-MOSFETs. IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 9, no. 5, pp. 6432-6440, Oct. 2021. doi: 10.1109/JESTPE.2021.3053127.

- [5] H. Du, P. Diaz Reigosa, L. Ceccarelli and F. Iannuzzo, "Impact of Repetitive Short-Circuit Tests on the Normal Operation of SiC MOSFETs Considering Case Temperature Influence. IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 1, pp. 195-205, March 2020. doi: 10.1109/JESTPE.2019.2942364.

- [6] Y. Barazi, F. Richardeau, W. Jouha, J-M. Reynes, V<sub>DS</sub> and V<sub>GS</sub> Depolarization Effect on SiC MOSFET Short-Circuit Withstand Capability Considering Partial Safe Failure Mode. Energies 2021, 14, 7960. doi.org/10.3390/en14237960.

- [7] D. Cavallaro, M. Pulvirenti, E. Zanetti, M. G. Saggio. Capability of SiC MOSFETs under Short-Circuit tests and development of a Thermal Model by Finite Element Analysis. Materials Science and Engineering Journal, pp. 788-791, 2018. (no DOI).

- [8] F. Boige, F. Richardeau, S. Lefebvre and M. Cousineau. SiC power MOSFET in short-circuit operation: Electro-thermal macro-modelling combining physical and numerical approaches with circuit-type implementation. Mathematics and Computers in Simulation (2018, Vol. 158) 375-386. doi.org/10.1016/j.matcom.2018.09.020.

- [9] J. Liu, G. Zhang, B. Wang, W. Li, and J. Wang. Gate Failure Physics of SiC MOSFETs Under Short-Circuit Stress. IEEE Electron Device Lett. (2020), 41, 103– 106. doi: 10.1109/LED.2019.2953235.

- [10] L. L. Snead, T. Nozawa, Y. Katoh, T.-S. Byun, S. Kondo, and D. A. Petti, 'Handbook of SiC properties for fuel performance modeling', J. Nucl. Mater., vol. 371, no. 1, pp. 329–377, Sep. 2007 doi.org/10.1016/j.jnucmat.2007.05.016.

- [11] J. E. Hatch, Aluminum: Properties and Physical Metallurgy. ASM International, 1984. (no DOI).