# Medium Voltage Diode Rectifier Design for High Step-Up DC-DC Converter

Pierre Le Métayer, Cyril Buttay, Drazen Dujic, Piotr Dworakowski

## ▶ To cite this version:

Pierre Le Métayer, Cyril Buttay, Drazen Dujic, Piotr Dworakowski. Medium Voltage Diode Rectifier Design for High Step-Up DC-DC Converter. European Power Electronics conference (EPE ECCE 2022), Sep 2022, Hannovre, Germany. hal-03790420

## HAL Id: hal-03790420 https://hal.science/hal-03790420v1

Submitted on 28 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Medium Voltage Diode Rectifier Design for High Step-Up DC-DC Converter

Pierre Le Métayer<sup>1,2</sup>, Cyril Buttay<sup>2</sup>, Drazen Dujic<sup>3</sup>, Piotr Dworakowski<sup>1</sup>

<sup>1</sup>SUPERGRID INSTITUTE 23 Rue Cyprian 69100 Villeurbanne, France +33 7 63 66 19 15 pierre.lemetayer@supergrid-institute.com https://www.supergrid-institute.com

<sup>2</sup>Univ Lyon, CNRS, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, Ampère, UMR 5005, 69621 Villeurbanne, France http://www.ampere-lab.fr

> <sup>3</sup>Power Electronics Laboratory (PEL) École Polytechnique Fédérale de Lausanne 1015 Lausanne, Switzerland https://www.epfl.ch/labs/pel/

#### Acknowledgements

This work was supported by a grant overseen by the French National Research Agency (ANR) as part of the "Investissements d'Avenir" Program (ANE-ITE-002-01)

## Keywords

«Diode», « Medium voltage converter », « Silicon Carbide », « DC-DC power converter », «Photovoltaic »

### Abstract

A medium voltage rectifier, relying on series connection of SiC Schottky diodes, is designed and tested within a unidirectional isolated DC-DC converter. The design is realized considering efficiency, static and dynamic balancing and failure mode considerations. The model of the rectifier circuit is improved compared to the previous literature enabling to precisely represent the voltage oscillations due to switching, facilitating the design of the snubbers. Experimental results are presented to validate the design. The developed model results show good fit with the measurements.

### Introduction

Medium voltage direct current (MVdc) networks are considered in numerous works for the integration of renewable energy sources [1]–[4]. In particular, the photovoltaic (PV) application is discussed in [3], [4]. Step-up DC-DC converters are required to interface low voltage PV clusters to an MVdc collection network. The MVdc collection network is expected to be in the order of  $\pm 10$  kV, the actual value depending on various design parameters, specific to particular application [3].

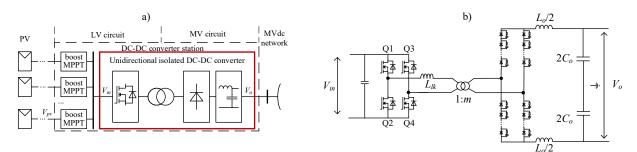

Fig. 1: a) Unidirectional isolated DC-DC converter in MVdc PV application, b) PSFB with a medium voltage rectifier using series connected diodes.

Unidirectional power flow is considered in PV application, as the power is only exported towards the network. Multiple maximum power point tracking (MPPT) boost DC-DC converters are used to interface PV strings with a Phase Shifted Full Bridge (PSFB) converter, selected as the unidirectional isolated step-up DC-DC converter [5] (this later converter having significantly higher power ratings than individual MPPT boosts). The PSFB circuit (Fig. 1b) uses a diode rectifier on the MV side (as compared to transistors for, e.g. the dual active bridge), making it an attractive solution from the control and cost point of view. The rectifier bridge components have a current rating of a few tens of amperes [5]. Diodes of such rating are most commonly found in discrete component packages with voltage ratings up to 3.3 kV [6]. A series connection of diodes is addressed in this paper, and presented in details below, focusing on the detailed design of the snubber components to limit switching overvoltage.

The *LC* output filter of the PSFB was shown in [7] to be advantageous compared with a simple output capacitor when the converter experiences faults on the MV side. However, the presence of an inductor between the rectifier and the output capacitor means that the rectifier bridge voltage is not clamped to the output voltage. Voltage oscillations occur at the diode turn-off, due to resonances between the transformer leakage inductance and parasitic capacitances of transformer and diodes, as described in [8], [9]. It is desirable to keep this voltage ringing low, so as to limit the peak voltage experienced by the diodes, and so as to limit electro-magnetic interferences (EMI). The *RC* snubber design for the series connection of SiC diodes takes into account the dynamic voltage balancing as well as the voltage ringing in the PSFB converter.

This paper presents the design of a medium voltage (4 kVdc) medium frequency rectifier, intended to operate with non-clamped voltage, based on series-connected SiC Schottky diodes. The choices of diode rating and number of series connected diodes are discussed considering efficiency and reliability. The voltage oscillations are modelled based on [9], adapted to series-connected assemblies of diodes, with the inclusion of the effects of transformer primary-secondary capacitance and limited switching speeds. This simplified model enables rapid snubber design. Tests are performed on the designed rectifier and measured waveforms are compared with the results expected from derived models.

#### Design of the rectifier

Diode assemblies are commercially available for medium voltage applications [10]. However, these assemblies usually use silicon bipolar diodes. Thus, reverse recovery happens at diode turn-off [11], yielding power losses. In [3] it is shown that step-up DC-DC converters for MVdc collection network in PV applications are expected to reach efficiencies similar to that of state of the art PV inverter cascaded with transformer for MVac collection network. Thus, very high efficiency is needed for all components of the converter. SiC Schottky diodes exhibit little to no reverse recovery current [11] and they are thus adapted for medium frequency, high efficiency applications. As a consequence, this article investigates the use of SiC diodes in the output rectifier of PSFB converter.

The rectifier presented in this paper is designed for a voltage of 4 kVdc, and maximum currents  $I_{mean} = 6$  A,  $I_{rms} = 9$  A,  $I_{peak} = 20$  A as in the converter design presented in [5]. The switching frequency is 20 kHz [5].

Commercially available diodes with ratings in the range of the specified currents are mostly found in discrete packages, with voltage ratings up to 1.7 kV (3.3 kV diodes are less common and have less available current ratings). In order to limit the number of series connected diodes only 1.2 kV and 1.7 kV

diodes are considered. One diode of each voltage rating and of similar current ratings is picked from the same manufacturer for comparison.

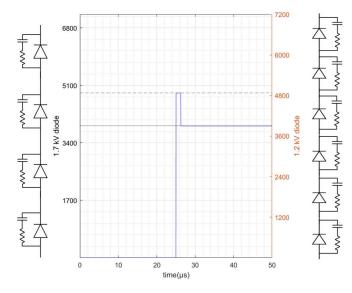

The choice of the number of series connected diodes is motivated by the presence of overvoltages at switching instant and failure mode considerations. Fig.2 shows a simplified rectifier voltage waveform with an overvoltage at switching instant, considered to be limited by the snubber design to 1.25 times the steady state voltage. The number of diodes  $n_{diodes}$  is chosen so as  $n_{diodes}$ -1 diodes rated blocking voltage is sufficient to withstand the switching instant overvoltage. Indeed, it is shown in [12] that for series connected diodes, an event of cosmic radiation interaction does not lead to single event burnout, as the blocking voltage is transferred to the other diodes of the series connection. However, this is only possible if the remaining diodes have enough blocking capability. If this is the case, the impacted diode does not fail and its blocking capability is recovered after a period of time dependent on the applied voltage [12]. Number of series connected diodes and resulting conduction losses (at nominal current) for both voltage ratings are presented in Table I. The junction temperature is considered to be 125°C, as a worst-case scenario. Losses weighted with European efficiency coefficients (standardized efficiency measure considering the power distribution for a PV system operating under the European climate) [13] are also presented as a way to evaluate the impact of losses at lower powers on the comparison. It must be noted that these values have no real physical meaning but they are relevant for comparisons.

Fig. 2: Simplified rectifier waveform (blue) with overvoltage at switching instant, considered to be limited by the snubber design to 1.25 times the steady state voltage. Implementations with 6x1.2 kV or 4x1.7 kV series-connected diodes are represented. No static balancing resistors are represented as the leakage current of used diodes is considered sufficiently low.

| Diode reference          | Voltage<br>rating | Number<br>of diodes | Individual diode<br>conduction losses<br>at nominal<br>current | Full bridge rectifier<br>conduction losses at<br>nominal current | Full bridge<br>rectifier losses<br>with EU<br>efficiency<br>coefficients |

|--------------------------|-------------------|---------------------|----------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|

| Genesic<br>GB10MPS17-247 | 1700 V            | 4                   | 10.6 W                                                         | 170 W                                                            | 68.2 W                                                                   |

| Genesic<br>GD15MPS12-247 | 1200 V            | 6                   | 9.4 W                                                          | 225 W                                                            | 91.7 W                                                                   |

Table I: Comparison of rectifier bridge performance for 2 selected SiC Schottky diodes

One can note that the 1.2 kV diode has inferior individual losses compared to the 1.7 kV model. However, it is seen that 1.7 kV diodes choice leads to lower rectifier losses thanks to lower number of

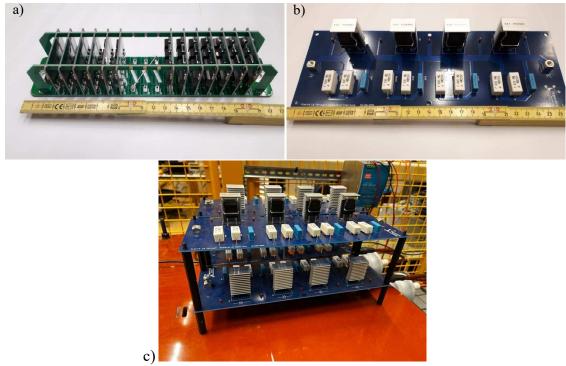

diodes, and this rating is thus selected. The losses weighted with EU efficiency coefficients confirm this choice, with proportionally an even slightly larger losses reduction compared to the 1.2 kV option. Thermal management of diode losses is met by individual heatsinks [14] at floating electrical potential, in natural convection condition. Each heatsink is referenced to the cathode of the diode, thus its potential varies according to ground in rectifier operation. This is beneficial for diode balancing as the parasitic capacitances to the ground are expected much lower than in a one common grounded heatsink scenario (such capacitances degrade voltage balancing in the series string [15]). It must be noted that the presented rectifier prototype is designed to validate electrical properties and the thermal aspects are not presented further in this paper. The cooling of the rectifier of a converter such as in Fig. 1 would beneficiate from being designed together with the medium frequency transformer and the output filter. Snubbers are placed in parallel to each diode of the series connection, in order to ensure dynamic voltage (voltage after oscillating transient). The snubber is composed of a capacitor  $C_{d1diode}$  and a resistor  $R_{d1diode}$  in series. It is proposed to select the snubber values based on following equations, adapted from [16]:

$$C_{d_{1diode}} = k_{sc} \cdot C_{j_{1diode}} \qquad R_{d_{1diode}} = k_{sr} \cdot \sqrt{\frac{m \cdot L_{lk}}{C_{d_{1diode}}}} \tag{1}$$

With  $C_{j1diode}$  the junction capacitance of a single diode of the series connection, *m* the transformer ratio and  $L_{lk}$  the transformer leakage inductance (see Table II). The value of  $C_{j1diode}$  is dependent on the reverse voltage applied to the diode. The  $C_{j1diode}$  capacitance value at 50% of the operating voltage (80 pF for the selected diode) is selected in order to simplify the calculations. Parameters  $k_{sc}$  and  $k_{sr}$  are the design parameter that can be adjusted in order to reduce oscillating transient overvoltages at switching instants. It is proposed to initially set  $k_{sc} = 3$  and  $k_{sr} = 1$  following typical design rules of generic *RC* snubbers [16] and tune them for overvoltages concerns using the model presented in the following section. The final values selected for this prototype are  $C_{d1diode} = 270$  pF and  $R_{d1diode} = 650 \Omega$ .

High value resistor in parallel of each diode can be added for static voltage balancing required due to diode leakage current deviations. However, considering the low value of leakage current of the selected diode (9  $\mu$ A at 175 °C of junction temperature) they are not implemented in this design.

Fig. 3: a) An example of commercially available high voltage diode assembly, intended for forced air or oil cooling; b) Diode assembly composed of four series connected diodes, designed for natural convection cooling c) Full-bridge rectifier composed of 4 diode assemblies.

#### Model and simulations

In order to analyze the voltage oscillations occurring at diode turn-off, the rectifier and transformer are modeled taking into account their parasitic elements. The model is derived according to [9], adapted to a full bridge rectifier and including the primary-secondary parasitic capacitance of the medium frequency transformer (MFT) modeled with lumped elements. The values of the parasitic elements of the MFT used in the test set-up can be found in Table II. The circuit model is presented in Fig. 4. The voltage source is driven by rate-limited step function representing the limited switching speed of the input bridge.

| <b>Table I</b> | I: MFT | parameters |

|----------------|--------|------------|

|----------------|--------|------------|

a)

| Transformation<br>ratio | Leakage<br>inductance | Primary winding capacitance | Secondary winding capacitance | Primary to secondary<br>winding capacitance |

|-------------------------|-----------------------|-----------------------------|-------------------------------|---------------------------------------------|

| m = 2.33                | $L_{lk}$ = 34 µH      | $C_p = 16 \text{ pF}$       | $C_s = 100 \text{ pF}$        | $C_{ps} = 30 \text{ pF}$                    |

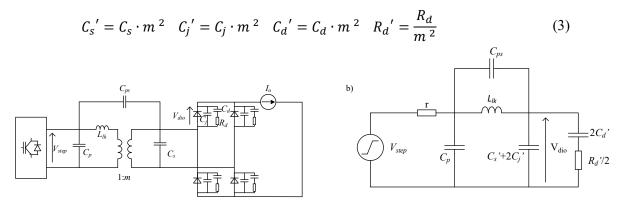

The diodes in Fig. 4 represent the series connection of  $n_{diodes}$ . Thus, the junction capacitance  $C_j$ , snubber capacitor  $C_d$ , and snubber resistor  $R_d$  are defined as:

$$C_j = \frac{C_{j_{1diode}}}{n_{diodes}} \qquad C_d = \frac{C_{d1diode}}{n_{diodes}} \qquad R_d = R_{d1diode} \cdot n_{diodes} \tag{2}$$

In Fig. 4b, the simplified model is represented from the primary side of the MFT; secondary side components are moved to the primary following equations (3). At switching instant, the parasitic components of the pair of diodes in blocking state are in parallel to each other in the equivalent circuit of the converter. This results in the values of the aggregated components of the simplified model given in Fig. 4b.

Fig. 4: a) Model of the PSFB converter including parasitic elements, b) Simplified PSFB model at diode turn-off used to study the voltage ringing phenomenon.

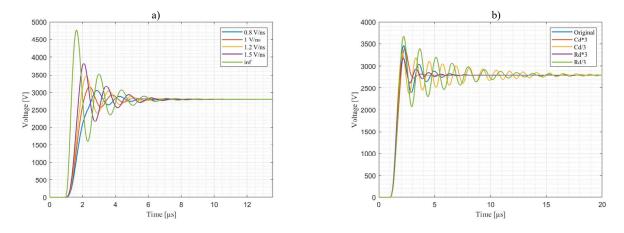

The quantity of interest is the voltage across each diode,  $V_{dio}$ . The effect of the switching is shown in Fig. 5a where the circuit is driven by different rate-limited step functions. The effect of variation of snubber parameters is also shown in Fig. 5b.

Fig. 5: Resulting  $V_{dio}*m$  (voltage across a diode string) from Fig. 4b model, with a) different switching speeds of  $V_{step}$  (base case 1.2 V/ns), b) snubber components parameter variations.

It is observed that oscillations are more severe for high switching speed, with important overvoltages. Thus, designing the snubber to attenuate the overvoltages associated with a perfect step input would lead to oversizing compared with a more realistic case.

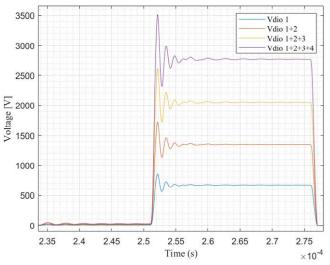

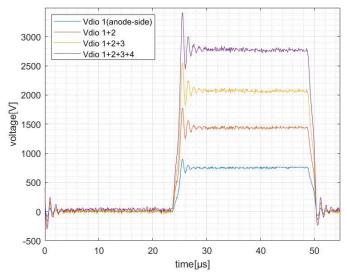

In order to validate the simplified PSFB model, a detailed circuit model is implemented using the Simulink Simscape Electrical library. Each diode is modeled with its junction capacitance (with voltage dependency taken into account via a lookup table) and *RC* snubber. The input inverter bridge is also modeled. Rectifier voltage oscillations obtained with the detailed model (Fig. 6) are similar to those presented in Fig. 5a (simplified model) for similar rates of change in voltage. This detailed simulation with each individual diode also enables to verify the voltage distribution across the series-connected diodes. Results are shown in Fig. 6.

Fig. 6: Detailed simulation of a diode series connection, voltage distribution between the 4 diodes of the series connection. Voltages are stacked from the anode-side diode to the cathode-side diode.

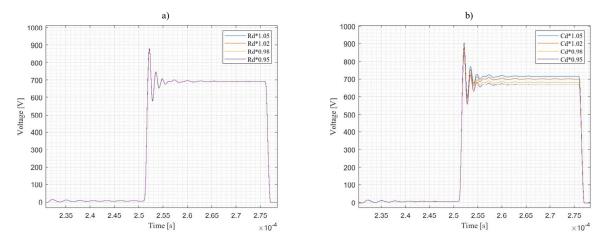

The effect of value deviation (caused by manufacturing tolerances) of the snubber components on the voltage balancing can be seen (Figs. 7a and b). Snubber capacitor value deviation has a larger influence on balancing than that of snubber resistance.

Fig. 7: Detailed simulation of a diode series connection, a) snubber resistor value deviation effect on voltage distribution, b) snubber capacitor value deviation effect on voltage distribution.

One should note that although complete simulations of the switching circuit enables to design the snubber precisely, the addition of so many parasitic components slows down the simulation that is already using a very small time step (typically inferior to  $0.1 \ \mu$ s). Previous model presented in Fig. 4b is thus preferred when iterating on snubber components selection with regards to overvoltage limitation.

### **Experimental results**

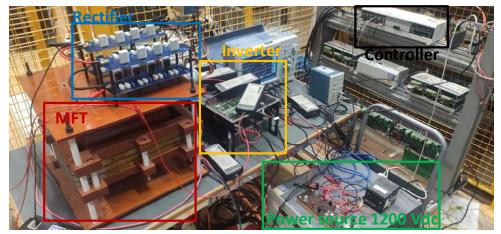

The designed rectifier is tested within the DC-DC converter test setup shown in Fig. 8. The inverter is operated at 20 kHz, with a full wave modulation. The MFT parasitic elements shown in Table II were characterized following the procedure given in [17].

Fig. 8: Test setup: a 1200 Vdc power supply feeds an inverter controlled in open loop to produce square waves at 20 kHz. The inverter is connected to the low voltage side of the MFT of ratio 1:*m*. The high voltage side of the MFT is connected to the studied rectifier, made of 4 assemblies shown in Fig. 3b.

The rectifier is tested in a non-clamped voltage configuration (inductive output) with an input voltage of  $V_{in} = 1200$  V. The voltage distribution between the 4 diodes of an assembly is shown in Fig. 9. The maximum measured voltage imbalance is around 10%. The measured waveforms are similar to simulation results.

Fig. 9: Voltage distribution between the 4 diodes of the series connection. Voltages are stacked from the anode-side diode to the cathode-side diode.

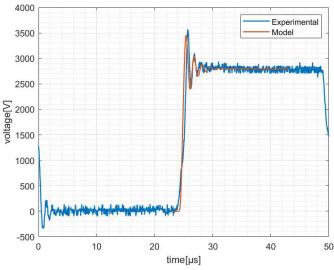

The simplified model presented in the previous section (Fig. 4b) is ran with the same switching speed of the input bridge as observed in the measured waveforms (1.2 V/ns), the snubber components values from the design section, and the parasitic elements from Table II. The measured voltage across one diode string is shown in Fig. 10, superimposed with the model result.

Fig. 10: Comparison between simulation results using the simplified model and experimental measurements of a diode assembly at turn-off.

The model result is close to the measured waveform. We can observe only small differences in terms of peak voltage, frequency of the oscillation and speed of the voltage step. These are considered to be due to inaccuracies in the transformer parasitic capacitances, as such small values (a few pF or tens of pF) are complicated to characterize with precision. However, the results still show the relevance of the simplified model for designing the snubber components in order to limit the overvoltage.

#### Conclusion

A rectifier for medium voltage medium frequency DC-DC converter has been designed and tested. The design choice in terms of number of series connected diodes is motivated by efficiency and reliability. The particular operation of the rectifier with an *LC* output filter ("unclamped operation") is studied and a simplified model is improved based on the literature. The model allows fast simulations of turn-off

voltage oscillations, enabling snubber design taking into account DC-DC converter parasitic elements. Measurements confirm the proposed design and model.

#### References

- M. De Prada Gil, J. L. Domínguez-García, F. Díaz-González, M. Aragüés-Peñalba, and O. Gomis-Bellmunt, 'Feasibility analysis of offshore wind power plants with DC collection grid', *Renewable Energy*, vol. 78, pp. 467–477, Jun. 2015.

- [2] CIGRE WG C6.31, 'Medium voltage direct current (MVDC) grid feasibility study', Feb. 2020.

- [3] P. Le Métayer *et al.*, 'Break-even distance for MVDC electricity networks according to power loss criteria', in 2021 23rd European Conference on Power Electronics and Applications (EPE'21 ECCE Europe), 2021, pp. 1–9.

- [4] H. A. B. Siddique, S. M. Ali, and R. W. De Doncker, 'DC collector grid configurations for large photovoltaic parks', in 2013 15th European Conference on Power Electronics and Applications (EPE), 2013, pp. 1–10.

- [5] P. Le Métayer, Q. Loeuillet, F. Wallart, C. Buttay, D. Dujic, and P. Dworakowski, 'Unidirectional Isolated dc-dc converter for Photovoltaic MVdc Power Collection Networks', submitted to *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 2022.

- [6] 'Silicon Carbide (SiC) Schottky Diode GeneSiC Semiconductor', *GeneSiC Semiconductor, Inc.* [Online]. Available: https://www.genesicsemi.com/sic-schottky-mps/. [Accessed: 06-Dec-2021].

- [7] P. Dworakowski, P. Le Métayer, C. Buttay, and D. Dujic, 'Unidirectional step-up isolated DC-DC converter for MVDC electrical networks', accepted for CIGRE Session 2022, 2022.

- [8] I. Ferencz, D. Petreus, and T. Pătărău, 'Comparative Study of Three Snubber Circuits for a Phase-Shift Converter', in 2020 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), 2020, pp. 763–768.

- [9] G. R. Zhu, D. H. Zhang, W. Chen, and F. Luo, 'Modeling and analysis of a rectifier voltage stress mechanism in PSFB converter', in *2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2012, pp. 857–862.

- [10] 'High Voltage Rectifier Unit Series'. [Online]. Available: https://www.hv-semi.com/gyzldyxl. [Accessed: 06-Dec-2021].

- [11] Z. Zeng et al., 'Performance Comparison of FRD and SiC Schottky Diode in Si/SiC Hybrid Switch Power Module', in 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), 2020, pp. 1890–1893.

- [12] X. Liao, Y. Liu, J. Li, J. Cheng, and Y. Yang, 'A possible single event burnout hardening technique for SiC Schottky barrier diodes', *Superlattices and Microstructures*, vol. 160, p. 107087, Dec. 2021.

- [13] Z. Salam and A. Rahman, 'Efficiency for photovoltaic inverter: A technological review', presented at the 2014 IEEE Conference on Energy Conversion, CENCON 2014, 2014, pp. 175–180.

- [14] 'C247-025-1VE Ohmite Mfg Co'. [Online]. Available: https://www.ohmite.com/catalog/c-series-heatsink/C247-025-1VE. [Accessed: 30-Mar-2022].

- [15] Y. He and D. J. Perreault, 'Diode Evaluation and Series Diode Balancing for High-Voltage High-Frequency Power Converters', *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 6301–6314, Jun. 2020.

- [16] CDE Cornell Dubilier, 'Application guide, Designing RC Snubber Networks'. .

- [17] C. Liu, L. Qi, X. Cui, and X. Wei, 'Experimental Extraction of Parasitic Capacitances for High-Frequency Transformers', *IEEE Transactions on Power Electronics*, vol. 32, no. 6, pp. 4157–4167, Jun. 2017.