## Extended charge layers in metal-oxide-semiconductor nanocapacitors revealed by Operando electron holography

C. Gatel, R. Serra, K. Gruel, A. Masseboeuf, L. Chapuis, R. Cours, L. Zhang, B. Warot-Fonrose, Martin Hÿtch

## ▶ To cite this version:

C. Gatel, R. Serra, K. Gruel, A. Masseboeuf, L. Chapuis, et al.. Extended charge layers in metal-oxide-semiconductor nanocapacitors revealed by Operando electron holography. Physical Review Letters, 2022, 129 (13), pp.137701. 10.1103/physrevlett.129.137701. hal-03787333

## HAL Id: hal-03787333 https://hal.science/hal-03787333v1

Submitted on 24 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Extended Charge Layers in Metal-Oxide-Semiconductor Nanocapacitors Revealed by Operando Electron Holography

C. Gatel<sup>®</sup>, \*R. Serra, K. Gruel<sup>®</sup>, A. Masseboeuf<sup>®</sup>, L. Chapuis, R. Cours, L. Zhang<sup>®</sup>, B. Warot-Fonrose, and M. J. Hÿtch<sup>®</sup>†

CEMES, Université de Toulouse, CNRS, 29 rue Jeanne Marvig, 31055 Toulouse, France

(Received 26 February 2022; accepted 22 August 2022; published 19 September 2022)

The metal-oxide-semiconductor (MOS) capacitor is one of the fundamental electrical components used in integrated circuits. While much effort is currently being made to integrate new dielectric or ferroelectric materials, capacitors of silicon dioxide on silicon remain the most prevalent. It is perhaps surprising therefore that the electric field within such a capacitor has never been measured, or mapped out, at the nanoscale. Here we present results from *operando* electron holography experiments showing the electric potential across a working MOS nanocapacitor with unprecedented sensitivity and reveal unexpected charging of the dielectric material bordering the electrodes.

DOI: 10.1103/PhysRevLett.129.137701

Introduction.—Metal-oxide-semiconductor (MOS) capacitors are widely used in many advanced devices whose performance is dependent on their miniaturization and operation [1]. They can be employed individually or as an element of more elaborate components such as the fieldeffect transistor, flash memory, dynamic random-access memory, and active regions of image sensors. A MOS capacitor is composed of a thin oxide layer sandwiched between a top metal electrode and a bottom electrode of semiconductor substrate [2]. While new materials for the dielectric are constantly being explored from high-K materials [3] to ferroelectrics [4] and negative capacitance ferroelectric stacks [5], silicon dioxide is still the most widely used dielectric material and is featured prominently in textbooks on semiconductor physics. By applying bias across the two electrodes, charge is stored at the two interfaces. In reality, the physics is rich and complex, ranging from band-bending, depletion regions and inversion layers in the semiconductor substrate to charge trapping in the dielectric oxide and at the interfaces. It is the latter phenomenon that is of particular interest here.

Charge trapping changes the capacitance and performance of real devices by modifying the threshold voltage and frequency response [6] and is a major concern for dielectric breakdown [7]. Some traps are expected to be stable over time and others occupied dynamically as a function of the applied bias. Much discussion has been made of the nature of the traps and where they occur: at the interface, in immediate vicinity to the interface, or within the bulk of the dielectric [8]. Others refer to border traps, being near the interface but within the dielectric layer [9]. Interest in the topic has recently been revived since interface and border traps have been linked to reliability issues [10,11]. The uncertainty concerning their location arises from the fact that the majority of the characterization

techniques are based on indirect measurements. Electrical characterization by Fermi-probe techniques, thermal activation, photoemission, x-ray photoelectron spectroscopy, and electron spin-based methods measure the global response of a device or lack the spatial resolution to probe the distribution of traps at the nanometer length scale [12]. We have therefore explored whether transmission electron microscopy, and in particular electron holography, can be used as a new way of studying these systems.

Electron holography is a powerful technique for measuring local fields in materials, from electric and magnetic [13–15] to mechanical strain [16]. Indeed, the phase of the electron hologram can be directly related to the electrostatic potential encountered by the fast electron along its trajectory:

$$\phi^{E}(x,y) = C_{E} \int V(x,y,z)dz, \qquad (1)$$

where  $C_E$  depends only on universal constants and the accelerating voltage of the microscope. While it was shown early on that electric fields could be measured in semiconductor devices in such a way [17,18], the development of *operando* experiments has been a long one.

The *p-n* junction was the first object of study, since there is a built-in electric field requiring no external applied bias. After pioneering *in situ* observations [19], an important breakthrough was achieved when the projected potential across a junction was measured for the first time by applying contact clamps to the wafer [20]. This led to the identification of key issues such as specimen preparation, surface damage layers, stray fields, and electron radiation [21–23]. Rare, however, has been the study of biased devices even with dedicated probe-based

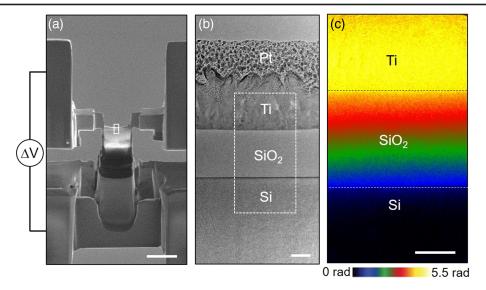

FIG. 1. Operando electron holography of nanocapacitor. (a) Scanning electron microscopy (SEM) image of specimen device within the FIB showing Pt deposited contacts to chip gold electrodes. (b) TEM image of active region showing substrate highly doped silicon, dielectric layer of silicon-dioxide (120 nm), top electrode of Ti, and Pt contact layer. (c) Phase map of projected electric potential obtained by electron holography [dotted region in (b)]. Scale bars are 5  $\mu$ m for (a) and 50 nm for (b) and (c).

holders [24]. The main problem is that the stray field around the nanoprobe is significant, perturbing the reference area of the hologram [25] and the potential applied to the active area [26]. In addition, the contact resistance between nanoprobe and sample is unknown, poorly controllable, and causes mechanical instabilities. To make the quantitative measurement of electric field feasible in devices such as a nanocapacitor, a different approach is needed.

Result.—Specimen device adapted to operando electron holography: To this end, along with other groups [26–31], we have been developing the fabrication of what we call "specimen devices" (Fig. 1): an operational device that is both electron transparent and contacted on a chip for biasing in situ without the need of a nanoprobe [32]. First, a thin lamella is extracted directly from thin film wafers or devices by focused-ion beam (FIB). Second, the lamella is placed across the electrodes of a specially designed chip with patterned electrodes and contacts made between the lamella and electrodes by depositing metal with the gasinjection system of the FIB. Final polishing for electron transparency is performed at low energy to limit the surface contamination and damage layers (for more details, see Supplemental Material [33]). The chip can then be inserted into a dedicated biasing holder of the TEM [34].

This chip-based technology and sample geometry avoids the problems associated with a nanoprobe contact, the bias being applied in a very similar way to the real device. Furthermore, the top electrode naturally shields the vacuum area above the specimen from the electric field in the active area, making other shielding schemes unnecessary [28,32,35]. These specimen devices are, however, extremely fragile and electrically sensitive. For example,

the MOS nanocapacitor studied here has a nominal capacitance of the order of 80 aF. The shielding and electrical protection of the connections from the sample holder to external power supply were therefore an essential part of the instrument development.

One of the other major reasons that local charge distributions have rarely been studied is that the signal is extremely weak. Elementary charges on nanoparticles can indeed be counted using electron holography because the field can be measured in the surrounding vacuum and the exact specimen geometry is known [36]. A working device made by FIB is much more challenging [37]. The methodology for the electron holography experiments also needed to be improved. Part of the solution was achieved by relying on the inherent advantage of operando experiments: the device is observed during operation and at rest. Here, operation means applying a constant (dc) bias across the two electrodes to create an electric field across the dielectric capacitor. By grounding the two electrodes, a reference hologram can be recorded that contains all the experimental artifacts: variable lamella thickness, damage layers, diffraction contrast, and electron-beam-induced charging [38,39]. By subtracting the reference signal from the holograms acquired during device operation, the artifacts are removed and the remaining signal can be attributed to the applied electrical biasing. For the experimental data presented in this Letter, this was not sufficient, however. We also needed to profit from the extremely long exposure times made possible by dynamic automation of the electron microscope [40] and smart acquisition routines [41]. Only then can the signal-to-noise ratio in the holograms be at an acceptable level for analysis of the local charges.

The sample device of study [Fig. 1(a)] fashioned by FIB is a thin film of 120-nm-thick thermally grown silicon dioxide on a highly p-doped silicon wafer ( $10^{18}$  atom  $\cdot$  cm<sup>-3</sup>) and topped with an electrode of titanium (see Supplemental Material [33]). The lamella thickness was measured to be  $55 \pm 5$  nm. Once connected to the chip with locally deposited platinum and inserted into a dedicated TEM biasing holder, the substrate was grounded while positive, negative, or zero biases were applied in situ to the top electrode. Electron holography experiments were carried out in Lorentz mode on an HF3300-C (Hitachi) equipped with a BCOR aberration corrector [42] from CEOS and using two postspecimen biprisms to allow flexibility in the holographic configurations and to eliminate the Fresnel fringe artifacts [43]. Holograms were acquired in the region shown in Fig. 1(b) and the phase calculated. The phase has been corrected for the phase at zero bias, and a region within the silicon substrate was used as an internal reference (see electron holography and hologram analysis in Supplemental Material for experimental details and data analysis [33]). The resulting phase map for a positive bias of 5 V is shown in Fig. 1(c), where we can see the change in phase across the capacitor due to the applied bias.

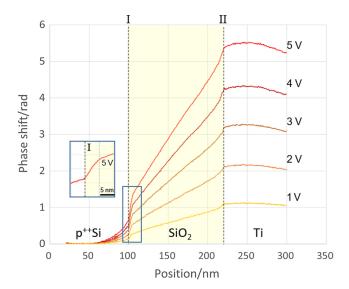

Phase profiles analysis: In order to improve the signal-to-noise ratio further, phase profiles were averaged over 100 nm parallel to the interface and the results shown in Fig. 2. The phase noise is now less than 10 mrad for a spatial resolution of 0.8 nm. The phase change across the capacitor can be seen clearly and increases linearly with applied bias, as expected from Eq. (1). However, the phase is not constant in the regions corresponding to the electrodes, whereas we would expect the electrodes to be at a

FIG. 2. Phase profiles as function of applied bias (1-5 V). Note the curvature of the phase within the electrodes (highly doped Si and Ti) and the phase jumps at the electrode-dielectric interfaces extending more than 5 nm inside the  $\text{SiO}_2$  layer (see enlargement for 5 V bias).

uniform potential. This is due to the fact that the phase is also sensitive to the stray field above and below the sample [27]. To interpret the profiles quantitatively, it is therefore necessary to carry out modeling of the electric potential in and around the thin sample.

A feature of particular interest to the analysis is the pronounced step in the phase occurring at both interfaces. The enlargement in Fig. 2 shows that here are two points of inflection, one at the interface plane and another at least 5 nm deep into the dielectric layer. This feature was unexpected and required much exploration to understand its origin.

We therefore carried out extensive finite element method simulations to understand the phase profiles. Our models took into account the specimen geometry, in particular, the lamella thickness and the width of the electrodes, but also the possibility of charge layers in the dielectric. Corresponding phase profiles were obtained by applying Eq. (1) to the simulated electrical potential and internal reference applied as for the experimental case.

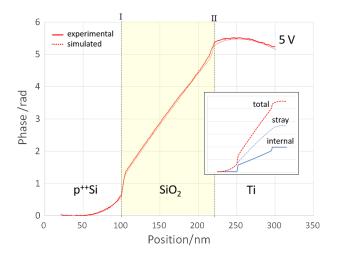

The best fit for the 5 V phase profile is shown in Fig. 3. Simulations confirm that the global phase change between the two electrodes (5.5 rad) corresponds exactly to an applied voltage of 5 V measured on the power supply, assuming the measured sample thickness to be correct. From a methodological point of view, this is highly encouraging and suggests that macroscopically applied bias is transmitted to the nanometer-sized active area of the device (the dielectric layer in this case). A large surface damage layer created by FIB would favor a leakage current and a voltage drop through the contact resistances between the sample and the grid. In addition, this means that the

FIG. 3. Finite element method modeling of electric potential in sample device. Experimental phase profile for 5 V bias (red line), best fitting simulation (red dotted line). Inset: simulated phase contributions from internal potential (blue line), stray field (blue dotted line), and total (red dotted line). Potential steps at interfaces caused by dielectric charge layers.

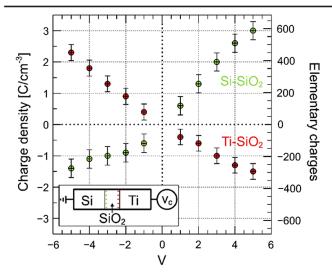

FIG. 4. Dielectric charge as a function of applied bias at  $Si-SiO_2$  and  $SiO_2-Ti$  interfaces. Left-hand axis in charges per unit volume. Right-hand axis in number of elementary charges contained in the analyzed region in the experimental specimen device.

phase sensitivity of 10 mrad is equivalent to only 9 mV of applied bias.

Quantification of volume charge densities within the dielectric layer: Analysis also shows that the curvature of the phase in the region corresponding to the electrodes is indeed caused by the stray fields around the thin specimen (see inset in Fig. 3). We see no evidence of a depletion layer in the silicon for a positive bias, which is expected for the high doping level with a thin depletion width (<10 nm for 5 V of applied bias) and a low surface potential (0.1 V). The only way the step in phase at the interface could be modeled successfully, however, was to include a layer of charge within the dielectric layer, similar to double charge layers observed in solid-state batteries [27]. We modeled this as a layer of uniform volume charge over 5.5 nm for both interfaces. Using this model, and by only changing the charge density, we were able to nicely reproduce the experimental profiles for the complete biasing experiment as depicted in Fig. 3.

The charge densities required to fit the experimental data are summarized in Fig. 4, including the negative biasing results. We have also indicated (right-hand scale) the number of elementary charges this represents in the region analyzed and represented by the phase profiles (i.e., 100 nm of interface in the 55-nm-thick lamella) to highlight the sensitivity of the measurements. The error bars reflect the experimental uncertainties, for example, the exact thickness of the lamella, much larger than the effect of the depletion layer for a positive bias. The resolution of the phase profiles is also limited giving our estimate for the width of the charge layers of  $5.5 \pm 0.5$  nm, which in turn introduces a certain interplay between the width of the charge layers and the charge density therein. Nevertheless, given the detailed

form of the profiles and the signal-to-noise ratio of the phase, the resulting error bars are contained (Fig. 4), representing sometimes as little as 50 elementary charges in the region analyzed.

Discussion.—It is well known that charges can be trapped in dielectric capacitors. However, it is generally considered that traps are in the immediate vicinity of the interface, that is, within a tunneling distance of 1–2 nm. It is therefore highly surprising that a homogeneous charge layer extends to a distance of over 5 nm from the interface. Furthermore, this distance is much larger than the structural or chemical width of the interface, as verified by highresolution TEM and electron energy-loss spectroscopy (see Supplemental Material [33]). The second interesting feature is that, contrary to an origin by quantum tunneling, the charge density varies monotonically with the applied bias, with an almost linear dependence, and follows the sign of the applied bias with an opposite sign to the charges on the nearby electrodes. Both negative and positive charges are therefore created on biasing. Overall, more positive charges are created than negative, particularly for the Si-SiO<sub>2</sub> interface. Finally, the density of charge does not depend on the history of the biasing. This was tested experimentally by returning from time to time to previous values of bias within a cycle. In addition, the hologram phase was stable over the acquisition time for each particular bias. All this suggests that the charges within the sample are in thermal equilibrium. Furthermore, the phase profiles are observed to change almost instantaneously on applying bias, suggesting that the equilibrium is attained very quickly.

To explore the implications for a full device, we have developed an analytical description of a capacitor having infinite parallel electrodes but including uniform dielectric charge layers at the interfaces using parameters measured by electron holography. The model also allows us to compare capacitors with and without dielectric charging and gives the electric potential, capacitance, and the electrostatic energy stored in the capacitor. We find a capacitance of 17 nF cm<sup>-2</sup> compared with an ideal capacitor (without the dielectric charge layers) of 29 nF cm<sup>-2</sup>, a significant reduction.

The slope of the electric potential corresponds to the electric field and is smaller in the capacitor due to the potential steps created by the charge layers (cf. inset Fig. 3). Indeed, from Gauss's law, the overall charge on the electrode plus the charge layer is reduced with respect to the ideal capacitor. Counterintuitively, the charge on the electrode is in fact much higher, over 10 times that of the ideal capacitor, being compensated by the charges in the dielectric. For example, there are 590 positive charges in the dielectric layer near the interface with silicon for 5 V of bias (cf. Fig. 4). From the model, we can calculate that there are 620 negative charges on the silicon electrode, producing a net charge of only 30 negative charges. In the absence of

dielectric charge, the capacitor would have had 50 negative charges on the silicon electrode.

From a purely electrostatic point of view, the creation of charge layers in the dielectric costs energy. The electrostatic energy stored can thus be calculated as  $1.2 \,\mu\text{J}\,\text{cm}^{-2}$  compared with  $0.36 \,\mu\text{J}\,\text{cm}^{-2}$  for the ideal capacitor. If we assume that this energy difference is compensated by the charge trapping, this corresponds to 340 meV per trap.

These experiments show the extreme sensitivity of electron holography for the study of charge distributions in operating devices, down to a handful of elementary charges in the region analyzed and 9 mV of applied bias, and opens possibilities for the study of many other types of device. We have shown that the measured capacitance is much less than expected for a capacitor based on SiO<sub>2</sub>, the most widely used dielectric. Macroscopic characterization might have attributed a reduction to poor quality of the interfaces or a larger than expected oxide thickness, contrary to what we observed. It should also be noted that our experiments are carried out for dc bias: other techniques are usually carried out at high frequency. The consequences are important however. While the electric field in the bulk of the dielectric layer is lower than expected, the electric field at the interface can be 10 times higher than for the ideal capacitor, with implications for the reliability. A very unexpected finding is that the charge layer extends to over 5 nm from the interface. Our results suggest that the charge trapping mechanisms and charge transfer at interfaces over long timescales needs to be reevaluated.

We are very grateful to Laurent Mazenq (LAAS-CNRS Toulouse) for preparing the thin films. The research leading to these results has received funding from the European Union Horizon 2020 research and innovation programme under Grant Agreement No. 823717—ESTEEM3. This work has been supported by the French National Research Agency under the "Investissement d'Avenir" program reference No. ANR-10-EQPX-38-01. This work was also supported by the French national project IODA (ANR-17-CE24-0047) and the international associated laboratory M<sup>2</sup>OZART.

- \*Corresponding author. christophe.gatel@cemes.fr †Corresponding author. martin.hytch@cemes.fr

- [1] E. H. Nicollian and J. R. Brews, *MOS (Metal Oxide Semi-conductor) Physics and Technology* (John Wiley and Sons, New York, 2002).

- [2] S. M. Sze, L. Yiming, and K. K. Ng, *Physics of Semi-conductor Devices*, 4th ed. (John Wiley and Sons, New York, 2021).

- [3] J. Robertson, Interfaces and defects of high-K oxides on silicon, Solid-State Electron. 49, 283 (2005).

- [4] M. P. Warusawithana *et al.*, A ferroelectric oxide made directly on silicon, Science **324**, 367 (2009).

- [5] A. I. Khan, K. Chatterjee, B. Wang, S. Drapcho, L. You, C. Serrao, S. R. Bakaul, R. Ramesh, and S. Salahuddin, Negative capacitance in a ferroelectric capacitor, Nat. Mater. 14, 182 (2015).

- [6] B. E. Deal, M. Sklar, A. S. Grove, and E. H. Snow, Characteristics of the surface-state charge  $(Q_{ss})$  of thermally oxidized silicon, J. Electrochem. Soc. **114**, 266 (1967).

- [7] D. J. DiMaria, E. Cartier, and D. Arnold, Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon, J. Appl. Phys. **73**, 3367 (1993).

- [8] B. E. Deal, Standardized terminology for oxide charges associated with thermally oxidized silicon, J. Electrochem. Soc. 127, 979 (1980).

- [9] D. M. Fleetwood, "Border traps" in MOS devices, IEEE Trans. Nucl. Sci. 39, 269 (1992).

- [10] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, F. Schanovsky, J. Franco, M. T. Luque, and M. Nelhiebel, The paradigm shift in understanding the bias temperature instability: From reaction—diffusion to switching oxide traps, IEEE Trans. Electron Devices 58, 3652 (2011).

- [11] D. M. Fleetwood, Border traps and bias-temperature instabilities in MOS devices, Microelectron. Reliab. 80, 266 (2018).

- [12] O. Engström, *The MOS System* (Cambridge University Press, Cambridge, England, 2014).

- [13] R. E. Dunin-Borkowski, A. Kovács, T. Kasama, M. R. McCartney, and D. J. Smith, Electron Holography, in *Springer Handbook of Microscopy*, edited by P. W. Hawkes and J. C. H. Spence (Springer International Publishing, Cham, 2019), pp. 767–818.

- [14] M. McCartney, R. E. Dunin-Borkowski, and D. Smith, Quantitative measurement of nanoscale electrostatic potentials and charges using off-axis electron holography: Developments and opportunities, Ultramicroscopy 203, 105 (2019).

- [15] C. Gatel, B. Warot-Fonrose, N. Biziere, L. A. Rodríguez, D. Reyes, R. Cours, M. Castiella, and M. J. Casanove, Inhomogeneous spatial distribution of the magnetic transition in an iron-rhodium thin film, Nat. Commun. 8, 15703 (2017).

- [16] M. Hÿtch, F. Houdellier, F. Hüe, and E. Snoeck, Nanoscale holographic interferometry for strain measurements in electronic devices, Nature (London) **453**, 1086 (2008).

- [17] M. R. McCartney, D. J. Smith, R. Hull, J. C. Bean, E. Voelkl, and B. Frost, Direct observation of potential distribution across Si/Si *p-n* junctions using off-axis electron holography, Appl. Phys. Lett. **65**, 2603 (1994).

- [18] W. D. Rau, P. Schwander, F. H. Baumann, W. Höppner, and A. Ourmazd, Two-Dimensional Mapping of the Electrostatic Potential in Transistors by Electron Holography, Phys. Rev. Lett. 82, 2614 (1999).

- [19] S. Frabboni, G. Matteucci, G. Pozzi, and M. Vanzi, Electron Holographic Observations of the Electrostatic Field Associated with Thin Reverse-Biased *p-n* Junctions, Phys. Rev. Lett. **55**, 2196 (1985).

- [20] A. C. Twitchett, R. E. Dunin-Borkowski, and P. A. Midgley, Quantitative Electron Holography of Biased Semiconductor Devices, Phys. Rev. Lett. 88, 238302 (2002).

- [21] D. Wolf, A. Lubk, A. Lenk, S. Sturm, and H. Lichte, Tomographic investigation of fermi level pinning at focused

- ion beam milled semiconductor surfaces, Appl. Phys. Lett. **103**, 264104 (2013).

- [22] J. B. Park, T. Niermann, D. Berger, A. Knauer, I. Koslow, M. Weyers, M. Kneissl, and M. Lehmann, Impact of electron irradiation on electron holographic potentiometry, Appl. Phys. Lett. 105, 094102 (2014).

- [23] S. Yazdi, T. Kasama, M. Beleggia, M. Samaie Yekta, D. W. McComb, A. C. Twitchett-Harrison, and R. E. Dunin-Borkowski, Towards quantitative electrostatic potential mapping of working semiconductor devices using off-axis electron holography, Ultramicroscopy 152, 10 (2015).

- [24] N. Ikarashi, H. Takeda, K. Yako, and M. Hane, In-situ electron holography of surface potential response to gate voltage application in a sub-30-nm gate-length metal-oxidesemiconductor field-effect transistor, Appl. Phys. Lett. 100, 143508 (2012).

- [25] L. de Knoop, F. Houdellier, C. Gatel, A. Masseboeuf, M. Monthioux, and M. Hytch, Determining the work function of a carbon-cone cold-field emitter by *in situ* electron holography, Micron **63**, 2 (2014).

- [26] M. Duchamp, V. Migunov, A. H. Tavabi, A. Mehonic, M. Buckwell, M. Munde, A. J. Kenyon, and R. E. Dunin-Borkowski, *In situ* transmission electron microscopy of resistive switching in thin silicon oxide layers, Resolut. Discov. 1, 27 (2016).

- [27] Y. Aizawa, K. Yamamoto, T. Sato, H. Murata, R. Yoshida, C. A. J. Fisher, T. Kato, Y. Iriyama, and T. Hirayama, *In situ* electron holography of electric potentials inside a solid-state electrolyte: Effect of electric-field leakage, Ultramicroscopy 178, 20 (2017).

- [28] Y. Nomura, K. Yamamoto, T. Hirayama, and K. Saitoh, Electric shielding films for biased TEM samples and their application to *in situ* electron holography, Microscopy **67**, 178 (2018).

- [29] Y. Xie, W. Kim, Y. Kim, S. Kim, J. Gonsalves, M. BrightSky, C. Lam, Y. Zhu, and J. J. Cha, Self-healing of a confined phase change memory device with a metallic surfactant layer, Adv. Mater. 30, 1705587 (2018).

- [30] Q. Huang, Z. Chen, M. J. Cabral, F. Wang, S. Zhang, F. Li, Y. Li, S. P. Ringer, H. Luo, Y.-W. Mai, and X. Liao, Direct observation of nanoscale dynamics of ferroelectric degradation, Nat. Commun. 12, 2095 (2021).

- [31] A. Vogel, M. F. Sarott, M. Campanini, M. Trassin, and M. D. Rossell, Monitoring electrical biasing of Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub> ferroelectric thin films in situ by DPC-STEM imaging, Materials 14, 4749 (2021).

- [32] M. Brodovoi, K. Gruel, A. Masseboeuf, L. Chapuis, M. Hÿtch, F. Lorut, and C. Gatel, Mapping electric fields in real nanodevices by operando electron holography, Appl. Phys. Lett. 120, 233501 (2022).

- [33] See Supplemental Material at http://link.aps.org/supplemental/10.1103/PhysRevLett.129.137701 for details on the sample preparation methodology, hologram acquisition and analysis, chemical and structural investigation, and finite element modelling.

- [34] F. Börrnert, R. Voigtländer, B. Rellinghaus, B. Büchner, M. H. Rümmeli, and H. Lichte, A cheap and quickly adaptable in situ electrical contacting TEM sample holder design, Ultramicroscopy 139, 1 (2014).

- [35] T. Wagner, T. Niermann, F. Urban, and M. Lehmann, Nanosecond electron holography by interference gating, Ultramicroscopy **206**, 112824 (2019).

- [36] C. Gatel, A. Lubk, G. Pozzi, E. Snoeck, and M. Hÿtch, Counting Elementary Charges on Nanoparticles by Electron Holography, Phys. Rev. Lett. 111, 025501 (2013).

- [37] Y. Yao, C. Li, Z. L. Huo, M. Liu, C. X. Zhu, C. Z. Gu, X. F. Duan, Y. G. Wang, L. Gu, and R. C. Yu, In situ electron holography study of charge distribution in high-κ charge-trapping memory, Nat. Commun. 4 (2013).

- [38] F. Ubaldi, G. Pozzi, T. Kasama, M. R. McCartney, S. B. Newcomb, and R. E. Dunin-Borkowski, Interpretation of electron beam induced charging of oxide layers in a transistor studied using electron holography, J. Phys. Conf. Ser. 209, 012064 (2010).

- [39] P. F. Fazzini, P. G. Merli, G. Pozzi, and F. Ubaldi, Effects of beam-specimen interaction on the observation of reverse-biased *p-n* junctions by electron interferometry, Phys. Rev. B **72**, 085312 (2005).

- [40] C. Gatel, J. Dupuy, F. Houdellier, and M. J. Hÿtch, Unlimited acquisition time in electron holography by automated feedback control of transmission electron microscope, Appl. Phys. Lett. **113**, 133102 (2018).

- [41] V. V. Volkov, M. G. Han, and Y. Zhu, Double-resolution electron holography with simple Fourier transform of fringe-shifted holograms, Ultramicroscopy **134**, 175 (2013).

- [42] E. Snoeck, F. Houdellier, Y. Taniguch, A. Masseboeuf, C. Gatel, J. Nicolai, and M. Hytch, Off-axial aberration correction using a B-COR for Lorentz and HREM modes, Microsc. Microanal. **20**, 932 (2014).

- [43] K. Harada, A. Tonomura, Y. Togawa, T. Akashi, and T. Matsuda, Double-biprism electron interferometry, Appl. Phys. Lett. 84, 3229 (2004).