## A CMOS Compatible Thermoelectric Device made of Crystalline Silicon Membranes with Nanopores

Thierno-Moussa Bah, Stanislav Didenko, Di Zhou, Tianqi Zhu, Hafsa Ikzibane, Stephane Monfray, Thomas Skotnicki, Emmanuel Dubois, Jean-François Robillard

### ▶ To cite this version:

Thierno-Moussa Bah, Stanislav Didenko, Di Zhou, Tianqi Zhu, Hafsa Ikzibane, et al.. A CMOS Compatible Thermoelectric Device made of Crystalline Silicon Membranes with Nanopores. Nanotechnology, 2022, 33 (50), pp.505403. 10.1088/1361-6528/ac8d12. hal-03766399

HAL Id: hal-03766399

https://hal.science/hal-03766399

Submitted on 24 Nov 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A CMOS Compatible Thermoelectric Device made of Crystalline Silicon Membranes with Nanopores

Thierno-Moussa Bah<sup>1,2</sup>, Stanislav Didenko<sup>2</sup>, Di Zhou<sup>2</sup>, Tianqi Zhu<sup>2</sup>, Hafsa Ikzibane<sup>2</sup>, Stephane Monfray<sup>1</sup>, Thomas Skotnicki<sup>3,4</sup>, Emmanuel Dubois<sup>2</sup>, Jean-François Robillard<sup>2</sup>

<sup>1</sup> STMicroelectronics - 850 rue jean Monnet 38920 Crolles, France

<sup>2</sup> Univ. Lille, CNRS, Centrale Lille, Junia, Univ. Polytechnique Hauts-de-France, UMR 8520 - IEMN – Institut d'Electronique de Microélectronique et de Nanotechnologie, F-59000 Lille, France

#### Abstract

Herein, we report the use of nanostructured crystalline silicon as a thermoelectric material and its integration into thermoelectric devices. The proof-of-concept relies on the partial suppression of lattice thermal conduction by introducing pores with dimensions scaling between the electron mean free path and the phonon mean free path. In other words, we artificially aimed at the well-known "electron crystal and phonon glass" trade-off targeted thermoelectricity. The devices were fabricated using CMOScompatible processes and exhibited power generation up to 5.5mW/cm<sup>2</sup> under a temperature difference of 280 K. These numbers demonstrate the capability to power autonomous devices with environmental heat sources using silicon chips of centimeter square dimensions. We also report the possibility of using the developed devices for integrated thermoelectric cooling.

**Keywords:** Silicon, Silicon-on-Insulator, CMOS, Thermoelectricity, Energy Harvesting, Phonon Scattering, Peltier cooling

#### Introduction

The blooming of the Internet of Things (IoT) and wireless autonomous sensor nodes has been delayed owing to the lack of reliable, safe, and low-cost energy sources [1]. Thermoelectric generators (TEG) have these advantages [2]. Silicon has the advantages of being abundant, non-toxic. Numerous facilities and CMOS technological processes for low-cost mass production exist for silicon while conventional thermoelectric materials (Bi, Sb, Te, Pb alloys) are far less developed. The research for Si-based TEG [3-5] has attracted increasing interest. However, silicon is an inefficient thermoelectric material owing to its high thermal conductivity of 150W/m/K [6], whereas bismuth telluride alloys exhibit hundred times lower conductivity (~1.5W/m/K) [7]. Moreover, the dimensionless figure of merit zT which characterizes the thermoelectric efficiency, is approximately 1 for Bi<sub>2</sub>Te<sub>3</sub> at room temperature [8] and below 0.01 for bulk silicon [9]. At temperature T, zT is defined as

$$zT = \frac{\sigma \cdot S^2}{\kappa} \cdot T \tag{1}$$

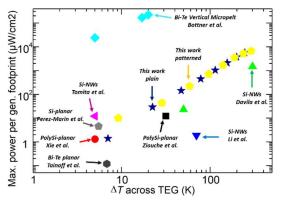

$\sigma$ , S and  $\kappa$  being the electrical conductivity, Seebeck coefficient, and thermal conductivity, respectively. The thermal conductivity accounts for the performance gap between the Si and Bi<sub>2</sub>Te<sub>3</sub> micro-TEGs (Figure 1). Efforts are oriented towards cutting the phonon part of heat transport, which is the dominant contribution in semiconductors [10]. The phonon contribution is evaluated in the diffusive regime

as

$$\kappa_{ph} = \frac{c \cdot v \cdot \Lambda}{3} \tag{2}$$

where c,  $\nu$  and  $\Lambda$  are the specific heat, group velocity (average elastic wave velocity), and phonon mean free path, respectively. The heat capacity depends on the atomic density of the material, and thus cannot be modified. Group velocity modulation would require modifying the atomic structure of the crystal to induce coherent effects, unexpected at room temperature. Suppression of the lattice contribution can be achieved by reducing the phonon mean free path through diffusion through artificial defects and boundaries. This process can be obtained by the use of thin films [6], nanowires [11], the addition of impurities or polycrystalline silicon [12], and silicon nanopatterning [13,14]. Previous studies have shown that holey structures can further decrease the thermal conductivity with a minor impact on the electrical conductivity [15]. The combination of thin films and phonon scattering by nanometric pores lowers the thermal conductivity to 34 W/m/K [13] and even to 2 W/m/K [14,15] depending on the specific design. The first value was for samples with partially perforated patterns and thus constitutes a conservative hypothesis. The lowest value represents the amorphous limit of silicon thermal conductivity [16], which makes it a very ambitious limit that can probably be obtained only at the cost of substantial material defects.

In addition to reducing the thermal conductivity of silicon, research in recent years has dealt with the development of silicon-based (mainly polysilicon and silicon nanowires) thermoelectric micro-harvesters or generators. Figure 1 reports the main results [3,5,17–20] from state-of-art silicon-based micro-harvesters with respect to state-of-art bismuth telluride harvesters [21]. The silicon TEGs exhibit output power in the  $\mu W/cm^2$  range against  $mW/cm^2$  for vertical  $Bi_2Te_3$  [21,22] TEG for same temperature differences. The thermoelectric properties of these materials primarily explain this gap.

In this study, we demonstrate a proof-of-concept thermoelectric device using patterned silicon membranes. The device consists of a silicon frame equipped with planar configuration thermopiles. For the sake of demonstration, the hot source is emulated by resistive heaters. A thermoelectric converter could be made from this device, by adding a silicon cap, mounted onto the hot source and etched in order to distribute the heat flow at the locations of the resistive heaters. An example of such configuration is given by Ziouche et al. [17]. In the following section, we present the fabrication process and discuss its performance with respect to plain membranes devices and especially according to the state-of-

<sup>&</sup>lt;sup>3</sup> Warsaw University of Technology, Centre for Advanced Materials and Technologies CEZAMAT, ul. Poleczki 19, 02-822 Warsaw, Poland

<sup>&</sup>lt;sup>4</sup> Warsaw University of Technology, Faculty of Electronics and Information Technology, Institute of Microelectronics and Optoelectronics, ul. Koszykowa 75, 00-662 Warsaw, Poland

art presented in Figure 1. We also mention modeling results reported in [23] that suggests that the performance of PE Sibased TEG compares favorably with that of Bi<sub>2</sub>Te<sub>3</sub> based TEG when the heat flow is not controlled by a bulky heat sink (*i.e.*, in the specific use case for IoT, which is deeply constrained by compactness and low form factor requirements).

Figure 1: State-of-art micro-harvesters' maximum output power per footprint area as a function of the temperature difference across the generator [3,5,17,19–22,24]

#### **Experimental Methods**

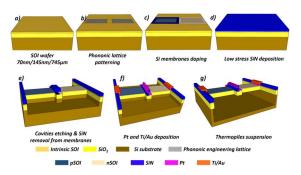

The devices were fabricated from SOI wafers using the conventional CMOS processes (Figure 2). The process is mainly based on previous work carried out to reduce the thermal conductivity of silicon by means of silicon thinning coupled to pore lattices [13,25]. The departure point is an SOI wafer with a 70 nm thick active layer (a) high-resolution ebeam lithography and Cl<sub>2</sub>/Ar reactive ion etching (RIE) was performed to define the pore patterns (b). Then, the silicon is p-boron and n-phosphorus doped by ion implantation with a target of 10<sup>19</sup> cm<sup>-3</sup>. Sheet resistivity measurements give  $2.34\times10^{-2}$   $\Omega$ .cm and  $6.38\times10^{-3}$   $\Omega$ .cm for p and n-type respectively corresponding to an effective doping level of  $6\times10^{18}$  cm<sup>-3</sup> and  $9\times10^{18}$  cm<sup>-3</sup> (c). A low-stress silicon nitride was then deposited (d) to insulate the thermopiles from the central platinum resistive heater emulating the devices' hot source. Silicon nitride also aims at improving the mechanical strength of structures. Cavities are etched around the thermopiles as apertures for subsequent suspension (e). Metallic sensors and leads are obtained by platinum and gold evaporation (f).

Figure 2: Patterned silicon membranes thermoelectric devices' fabrication process.

Before metallization, the Si membranes a thermal oxide layer is grown to protect them from xenon-difluoride (XeF<sub>2</sub>) etching (g). This last step of the process ensures thermal insulation of the Si membranes from the wafer. The device

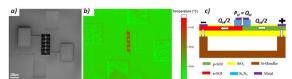

was made of five thermopiles connected electrically in series and thermally in parallel (Figure 3-a). It was equipped with four pads to supply heating power and I-V measurements. Each thermopile (50μm long, 10μm wide and 205 nm thick) was composed of two n- and p-doped membranes, as shown in Figure. 3-b. The membrane stack is composed of the following components: 15nm SiO<sub>2</sub>/62 nm Si/ 145 nm SiO<sub>2</sub>. At the center, two platinum straps electrically short-circuit the p-n boundary (Figure 3-c). Platinum resistive heaters were deposited over the silicon nitride layer to avoid current leakage (Figure 3-b, c, d). On half of the devices, a lattice of 40 nm diameter pores and 100 nm pitch patterns was etched (Figure 3-e, f). These dimensions are chosen as a compromise between technological capabilities and minimizing the pitch size, neck size and maximizing the porosity in order to enhance the effect of thermal conductivity reduction [26,27]. The electrical continuity of the thermopiles was ensured using a metallic Pt strap between adjacent thermopiles.

Figure 3: (a) Scanning Electron Micrograph of a thermoelectric device made of 5 suspended thermopiles. (b) Close-up view of three thermopiles. (c) Platinum resistive heater. (d) Detail of the membranes pore patterns. (e) Cross section Transmission Electron Micrograph of the membrane.

The devices were studied both in terms of energy harvesting under a temperature gradient (Seebeck effect) and thermoelectric cooling when current flows across thermopiles (Peltier effect). Regarding Seebeck effect, the devices were characterized by a thermo-resistive methodology [14,15,28]. Indeed, Pt is known to have a significant temperaturedependent coefficient of resistance  $\alpha=2.5\times10^{-3}/K$  in this case. This value differs from the bulk value because the Pt film is 30 nm thin and was systematically measured for each sample before the thermometry measurement. Infrared imaging (Figure 4-b) demonstrates the functionality of these heaters. The electrical power  $(P_{\rm H})$  produced at the center of the thermopiles is converted into heat flux  $(Q_H)$  and, in the first approximation, equally diffuses across the thermopiles (Figure 4-c) to the cold ends. Measurements were performed under vacuum to eliminate conducto-convective fluxes on in air and guide heat flux into the membranes. During the measurements, the frame wafer was maintained at a constant temperature of 25°C. Because the thermopiles were etched from the SOI substrate, efficient heat coupling was achieved at the cold ends. This assumption is supported by the high thermal conductance of the frame wafer and the infrared thermometry. It follows that the cold sides of the membranes are at the same temperature as the substrate, which was verified by IR imaging. The characterization was performed in two steps: i) by variation of the Pt heating current, a  $V-\Delta T$ characteristic enables measurement of the Seebeck voltage, and ii) at a constant Pt heating current, the I-V curves characterize the power generation. To capture the Peltier effect, a current was applied to the thermopiles and imaged using IR thermometry in ambient air. This electrical current should produce heat absorption or generation at the center of thermopiles depending direction.

**Figure 4:** SEM view of a 5 thermopiles device (a) IR imaging (performed in ambient air) after Pt resistive serpentines voltage bias (b) and cross-sectional scheme of a thermopile.

#### Results & Discussions

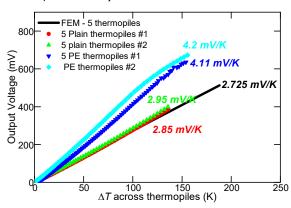

First, the heaters are calibrated in order to achieve a given temperature difference. We note that patterned thermopiles sustain a higher temperature difference for a given amount of heating power. There is a two-fold interest in this result. First, the use of a thin-film planar device significantly increases the thermal resistance to approximately 106K/W. This value governs the temperature difference in a TEG and should be compared to the typical Bi<sub>2</sub>Te<sub>3</sub> TE legs of 10<sup>4</sup>K/W [22]  $(10^2 \text{K/W} \text{ for bulk Si with typical leg dimensions of } 1 \times 1 \times 5$ mm<sup>3</sup>). In addition to the thin-film geometry, patterning enhances thermal resistance by a factor of 1.8. The reduction in thermal conductivity [13,14] with patterning explains this gain. Figure 5 shows the Seebeck voltage generated as a function of temperature difference across the thermopiles. Again, characterization was performed on plain and patterned samples. As expected, the Seebeck voltage increased linearly with the temperature gradient. Furthermore, the plain devices produced an electrical voltage close to the value expected by a Finite Element Method (FEM) software using a Seebeck coefficient  $S_p$ - $S_n$ = 545 $\mu$ V/K. The FEM cannot model the physical effect of pore pattering, therefore, the modeling results can only be compared to those of plain devices. The measurements showed Seebeck coefficients per thermopile of 570μV/K and 590μV/K for the plain devices and 820μV/K and 840µV/K for the patterned devices.

Figure 5: 5 plain thermopiles (black squares & red dots) and 5 patterned thermopiles (green & blue triangles) output voltage with respect to the temperature difference across thermopiles

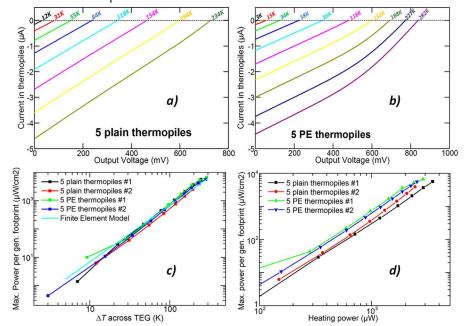

Power generation was investigated by studying the I-V characteristics of the thermopiles as a function of the applied temperature difference. Figures 6-a and -b report respectively the plain and patterned thermopiles I-V curves for  $\Delta T$  from 0 to 282 K temperature differences, respectively. Typical thermoelectric characteristics were obtained, and a generator regime (IV <0) was observed. The electrical current is given by

$$I = \frac{V_{Gbias} - V_{S}(\Delta T)}{R_{G}} \tag{3}$$

where  $V_{\text{Gbias}}$  is the thermopile bias voltage,  $V_{\text{S}}(\Delta T)$  is the Seebeck voltage at a given temperature difference across the

thermopiles, and  $R_G$  is the devices' internal resistance, which is approximately  $130k\Omega$  and  $260k\Omega$  for plain and patterned thermopiles, respectively. This increase of electrical resistivity with patterning is confirmed by independent fourprobe resistivity Van-der-Pauw measurements on dedicated areas of the wafer. Because the dimensions of the patterned lattice are much larger than the typical electron mean free path (a few nanometers [29]), it is unlikely that the resistivity is significantly affected by the pore patterns. We note that the change of resistivity between plain and patterned membranes can be evaluated as an effective change of the dopant concentration. (see Suppl. Material) A concomitant increase in the Seebeck coefficient and resistivity is then expected from the Mott relation [30,31] which order of magnitude is quite in agreement with the 1.4 times increase of the Seebeck coefficient.

From the I-V curves, we calculated the output power corresponding in the generation regime and extracted the maximum output power. Figures 6-c and -d present the maximum output power densities with respect to the temperature difference across the thermopiles (Figure 6-c) and according to the heating power of the Pt heaters (Figure 6-d). Figure 6-c shows that compared to the temperature difference across the thermopiles, the plain and patterned devices exhibit comparable performance. This observation reflects that the Seebeck effect is enhanced by patterning while the electrical resistance is increased, leading to a constant power factor. The maximum output power is given by (4), and at a given temperature difference, it depends only on the Seebeck coefficient and electrical resistance.

$$P_{MAX} = \frac{V^2}{4 * R_G} = \frac{S^2 * \Delta T^2}{4 * R_G} \tag{4}$$

where S and  $\Delta T$  are the Seebeck coefficient and the temperature difference across the thermopiles, respectively. Globally, patterning would therefore have no impact on generator performance. Figure 6-c also shows a comparison between the measurements and FEM modeling showing perfect agreement with the measurements.

The patterned and plain devices were compared again, but this time with respect to the heating power of the Pt heaters (Figure 6-d). Under these conditions, we can notice that, compared to the heating power, patterned devices exhibit better performance than plain thermopiles. This highlights the benefits of thermal gradient management for thermoelectric harvesting. Indeed, (5) gives the maximum output power, which depends not only on the Seebeck coefficient and electrical resistance that compensate each other, but also on the temperature difference across the thermopiles. The temperature difference across the PE thermopiles was higher for a given heating power (see Suppl. Material).

$$P_{MAX} = \frac{V^2}{4 * R_G} = \frac{S^2 * Q^2 * r_{TEG}^2}{4 * R_G}$$

$$\Delta T = Q * r_{TEG}$$

(5)

Q and r<sub>TEG</sub> are the heat gradient across the thermopiles (or heating power) and the thermal resistance of the thermopiles, respectively. Figures 6-c and -d highlight then the fact that the main benefit of pore patterning is better thermal gradient management, especially owing to a thermal conductivity reduction [13–15]. The gap between the patterned and plain thermopiles in figure 6-d can be improved with a better patterns design. From the range of output power, we can

easily imagine the use of a few cm<sup>2</sup> of such generators to supply power to autonomous sensor nodes [32]. Moreover, compared to the state-of-the-art (Figure 1), with respect to the silicon-based thermoelectric microharvesters, the developed devices mainly exhibit better performance for the same temperature differences. The material crystalline structure and harvester architectures can explain this difference in

performance. Polysilicon has lower electrical resistivity than crystalline silicon. Low-dimensionality systems, such as silicon nanowires, feature improved thermoelectric efficiency. Tomita et al. [19] managed to develop Si nanowire (NWs)-based harvesters exhibiting state-of-the-art performance.

Figure 6: 5 plain (a) and PE (b) thermopiles I-V curves with temperature gradient and measured maximum output power density versus temperature difference across thermopiles (c) and versus the Pt heaters' heating power (d)

As expected, the performance of the vertical bismuth telluride micro harvesters [21] is four orders over the developed devices. This is related to several causes. First, bismuth telluride legs feature lower electrical resistance, less than  $1\Omega$ , against tens of  $k\Omega$  per leg for the developed devices. Secondly, the bulk  $Bi_2Te_3$  parts exhibit low thermal conductivity. However, these performances are greatly diminished when the heat cooling capacity is low. This cooling capacity is quantified by an effective conducto-convective transfer rate h (W/m²/K) (see Suppl. Material).

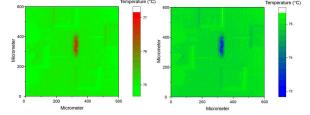

The characterization of the devices is completed with the observation of Peltier cooling. Figure 7 shows infrared (IR) images of a device biased at  $\pm 7.5$ V. The left picture represents the result of current propagation from p to n end, and the right picture represents the current propagation from n to p end. The figure shows that, depending on the current direction, heat generation or absorption is observed at the center of the thermopiles, which is characteristic of the Peltier effect.

Figure 7: IR imaging pictures of the device with respect to the electrical current direction in the thermopiles in Peltier mode. Left: current for p end to n end and right: current from n end to p end.

The heat generation and absorption were only observable at the center of the thermopiles because, first, the sample was maintained at 75°C during all the experiments, and second, the silicon membranes were too thin to absorb IR waves. The Peltier effect and, in particular, Peltier cooling, is then possible on silicon technologies, opening the way to a possible integration of thermoelectric coolers. However, it is worth noting that the TEG device was not designed for Peltier cooling, which is naturally much lower than Joule heating.

#### **Conclusion**

In summary, a phonon scattering approach was used to reduce the heat conduction in crystalline silicon thin membranes. The fabrication and demonstration of thermoelectric conversion using crystalline silicon was shown. The device principle relies on better use of the available thermal difference in a planar thin membrane architecture and additional pore patterning. The results

demonstrated the benefits of patterning. Moreover, phonon scattering induces an increase in the Seebeck coefficient compensated by an increase in electrical resistance and better thermal gradient management through the thermopiles. The net gain remains positive and we report  $400 \text{nW/cm}^2$  under  $\Delta T = 3 \text{K}$  up to  $5.5 \text{mW/cm}^2$  under  $\Delta T = 282 \text{K}$  according to the temperature difference across the thermopiles. This CMOS-

compatible device opens perspective in the relevant range (cm<sup>2</sup> footprint, mW power) for IoT power supply. In addition, the studied devices can be considered as state-of-the-art

silicon micro-harvesters. This study also highlights the feasibility of using integrated crystalline silicon thermoelectric coolers.

#### Acknowledgments

This work has received: i) funding from STMicroelectronics-IEMN common laboratory; ii) funding from the European Research Council under the European Community's Seventh Framework Programme (FP7/2007-2013) ERC Grant Agreement no. 338179, iii) support from the French RENATECH network, iv) support from the NANO2017 program, and v) support from the French government through the National Research Agency (ANR) under program PIA EQUIPEX LEAF ANR-11-EQPX-0025 and project TIPTOP ANR-16-CE09-0023.

#### Data availability statement

All data that support the findings of this study are included within the article. More details regarding the fabrication process and characterization methodology can be found in the supplementary material.

#### References

- Nordrum, A. Popular Internet of Things Forecast of 50 Billion Devices by 2020 Is Outdated. *IEEE Spectrum: Technology, Engineering, and Science News* (2016).

- Haras, M. & Skotnicki, T. Thermoelectricity for IoT A review. Nano Energy 54, 461–476 (2018).

- 3. Dávila, D. *et al.* Monolithically integrated thermoelectric energy harvester based on silicon nanowire arrays for powering micro/nanodevices. *Nano Energy* **1**, 812–819 (2012).

- Wang, Z. et al. Characterization of a Bulk-Micromachined Membraneless In-Plane Thermopile. Journal of Electronic Materials 40, 499–503 (2011).

- Xie, J., Lee, C. & Feng, H. Design, Fabrication, and Characterization of CMOS MEMS-Based Thermoelectric Power Generators. *Journal of Microelectromechanical Systems* 19, 317–324 (2010).

- Haras, M. et al. Thermoelectric energy conversion: How good can silicon be? Materials Letters 157, 193–196 (2015).

- 7. Pinisetty, D. & Devireddy, R. V. Thermal conductivity of semiconductor (bismuth-telluride)-semimetal (antimony) superlattice nanostructures. *Acta Materialia* **58**, 570–576 (2010).

- 8. Očko, M., Žonja, S. & Ivanda, M. Thermoelectric materials: problems and perspectives. in 2010 Proceedings of the 33rd International Convention MIPRO 16–21 (2010).

- 9. Hao, Q. *et al.* Theoretical studies on the thermoelectric figure of merit of nanograined bulk silicon. *Applied Physics Letters* **97**, 063109 (2010).

- Jin, J. S. Prediction of phonon and electron contributions to thermal conduction in doped silicon films. *J Mech Sci Technol* 28, 2287–2292 (2014).

- Boukai, A. I. et al. Silicon nanowires as efficient thermoelectric materials. Nature 451, 168–171 (2008).

- Lee, J.-H., Galli, G. A. & Grossman, J. C. Nanoporous Si as an Efficient Thermoelectric Material. *Nano Lett.* 8, 3750–3754 (2008).

- Haras, M. et al. Fabrication of Thin-Film Silicon Membranes With Phononic Crystals for Thermal Conductivity Measurements. IEEE Electron Device Letters 37, 1358–1361 (2016).

- 14. Tang, J. *et al.* Holey Silicon as an Efficient Thermoelectric Material. *Nano Lett.* **10**, 4279–4283 (2010).

- Yu, J.-K., Mitrovic, S., Tham, D., Varghese, J. & Heath, J. R. Reduction of thermal conductivity in phononic nanomesh structures. *Nat Nano* 5, 718–721 (2010).

- Wada, H. & Kamijoh, T. Thermal Conductivity of Amorphous Silicon. *Jpn. J. Appl. Phys.* 35, L648 (1996).

- 17. Ziouche, K. et al. Silicon-Based Monolithic Planar Micro Thermoelectric Generator Using Bonding Technology. Journal of Microelectromechanical Systems 26, 45–47 (2017).

- Li, Y., Buddharaju, K., Singh, N., Lo, G. Q. & Lee, S. J. Chip-Level Thermoelectric Power Generators Based on High-Density Silicon Nanowire Array Prepared With Top-Down CMOS Technology. *IEEE Electron Device Letters* 32, 674–676 (2011).

- Tomita, M. et al. 10μW/cm2-Class High Power Density Planar Si-Nanowire Thermoelectric Energy Harvester Compatible with CMOS-VLSI Technology. in 2018 IEEE Symposium on VLSI Technology 93–94 (2018). doi:10.1109/VLSIT.2018.8510659

- Perez-Marín, A. P. et al. Micropower thermoelectric generator from thin Si membranes. Nano Energy 4, 73– 80 (2014).

- Bottner, H. Micropelt miniaturized thermoelectric devices: small size, high cooling power densities, short response time. in *ICT 2005. 24th International Conference on Thermoelectrics*, 2005. 1–8 (2005). doi:10.1109/ICT.2005.1519873

- 22. Tainoff, D. *et al.* Network of thermoelectric nanogenerators for low power energy harvesting. *Nano Energy* **57**, 804–810 (2019).

- Bah, T.-M. et al. Performance Evaluation of Silicon Based Thermoelectric Generators Interest of Coupling Low Thermal Conductivity Thin Films and a Planar Architecture. in 2018 48th European Solid-State Device Research Conference (ESSDERC) 226–229 (2018). doi:10.1109/ESSDERC.2018.8486919

- 24. Li, J.-F. *et al.* Microfabrication of thermoelectric materials by silicon molding process. *Sensors and Actuators A: Physical* **108**, 97–102 (2003).

- 25. Lacatena, V. et al. Phononic engineering of silicon using "dots on the fly" e-beam lithography and plasma etching. *Microelectronic Engineering* **121**, 131–134 (2014).

- R. Yanagisawa, J. Maire, A. Ramiere, R. Anufriev, and M. Nomura, Impact of limiting dimension on thermal conductivity of one-dimensional silicon phononic crystals, Appl. Phys. Lett. 110, 133108 (2017)

- E. Dechaumphai and R. Chen, Thermal transport in phononic crystals: The role of zone folding effect, J. Appl. Phys. 111, 073508 (2012)

- 28. Maire, J. & Nomura, M. Reduced thermal conductivities of Si one-dimensional periodic structure and nanowire. *Jpn. J. Appl. Phys.* **53**, 06JE09 (2014).

- 29. Qiu B. et al. First-principles simulation of electron mean-free-path spectra and thermoelectric properties in silicon. *EuroPhysics Letters* **109**, 57006 (2015).

- Cutler, M. & Mott, N. F. Observation of Anderson Localization in an Electron Gas. *Phys. Rev.* 181, 1336– 1340 (1969).

- 31. Fritzsche, H. A general expression for the thermoelectric power. *Solid State Communications* **9**, 1813–1815 (1971).

- 32. Vullers, R. J. M., van Schaijk, R., Doms, I., Van Hoof, C. & Mertens, R. Micropower energy harvesting. *Solid-State Electronics* **53**, 684–693 (2009).