# Etude de l'" Advanced Spice Model " pour la modélisation des transistor HEMT GaN

Alexandre Santos, Julien Frederic, Florent Gaillard, Jean-Christophe Nallatamby, Christopher Chang, Raphaël Sommet

# ▶ To cite this version:

Alexandre Santos, Julien Frederic, Florent Gaillard, Jean-Christophe Nallatamby, Christopher Chang, et al.. Etude de l'" Advanced Spice Model " pour la modélisation des transistor HEMT GaN. XXIIèmes Journées Nationales Microondes, Jun 2022, Limoges, France. hal-03745063

HAL Id: hal-03745063

https://hal.science/hal-03745063

Submitted on 4 Aug 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# XXIIèmes Journées Nationales Microondes 8-10 juin 2022 – Limoges

# Etude de l'« Advanced Spice Model » pour la modélisation des transistor HEMT GaN

A. Santos<sup>1</sup>, J. Frédéric<sup>1</sup>, F. Gaillard<sup>1</sup>, J.C. Nallatamby<sup>1</sup>, C. Chang<sup>2</sup>, R. Sommet<sup>1</sup>

<sup>1</sup> Laboratoire XLIM, 16 rue Jules Vallès, 19100 Brive-La-Gaillarde <sup>2</sup> UMS, Bâtiment Charmille, 10 avenue du Québec. 91140 Villebon-sur-Yvette

raphael.sommet@xlim.fr

Résumé - Le modèle Advanced Spice Model (ASM) développé par S. Khandelwal et al. [1] a été utilisé pour la modélisation d'un transistor GH15 de la fonderie UMS. Il met en jeu le potentiel de surface, calculé à partir du niveau de Fermi  $(E_t)$ , qui permet de proposer un modèle analytique pour les charges intrinsèques ainsi que le courant de drain. D'autres effets parasites doivent également être modélisés et mis en équations afin de correspondre au mieux aux mesures (résistances d'accès, effet de grille courte, pièges, température...).

## 1. Introduction

Ces dernières années, les transistors à haute mobilité électronique (HEMT) AlGaN/GaN sont apparus comme des candidats prometteurs pour les applications à hautes fréquences et à forte puissance [2] en raison de leurs propriétés telles que la tension de claquage, la densité de charge et la mobilité électronique élevées [3]. Les modèles analytiques compacts basés sur la physique sont une solution puissante pour exploiter tout le potentiel de ces dispositifs, accompagner leur évolution vers des fréquences encore plus élevées et permettre une simulation rapide et précise des circuits dont ils font l'objet.

La plupart des modèles actuellement disponibles pour les dispositifs HEMT AlGaN/GaN sont basés sur des calculs numériques, des expressions de modèles semiempiriques, et/ou des approximations simplificatrices [4] [5] [6]. Les modèles reposant sur des calculs numériques sont lents, tandis que les modèles semi-empiriques comportent un grand nombre de paramètres dont la détermination reste délicate. De plus, leurs équations doivent souvent être adaptées avec la perpétuelle montée en fréquence et notamment la prise en compte des effets associés (effets de grille courte par exemple). Les modèles analytiques basés sur la physique des dispositifs sont souhaitables pour surmonter ces difficultés. Parmi les modèles analytiques basés sur la physique, les modèles utilisant la notion de Potentiel de Surface (SP) sont privilégiés pour la prochaine génération de modélisation compacte en raison de leur symétrie intrinsèque et l'utilisation d'une seule expression pour décrire toutes les régions du fonctionnement du dispositif [7]. Parmi ces modèles le plus connus est le modèle ASM [1]. Il a intégré depuis quelques années la CMC (Compact Model

Coalition) et est utilisé par d'importantes compagnies comme Keysight, Infineon dans le domaine de l'électronique.

# 2. Description du modèle ASM

Etablissement du modèle de courant de drain et des charges intrinsèques

Le transistor réel est tout d'abord décomposé en un transistor intrinsèque (partie sous la grille du transistor réel) associé à des accès de source et de drain.

Figure 1. Structure générale d'un transistor HEMT GaN

Le potentiel de surface φ est exprimé en tout point x du canal à partir du potentiel électrique V<sub>x</sub> et du niveau de Fermi E<sub>f</sub>:

$$\varphi_{x}(v_{g}) = E_{f}(v_{g}) + V_{x}$$

$\phi_x \big( v_g \big) = E_f \big( v_g \big) + V_x$  Il est issu de la résolution conjointe de l'équation de Schrödinger et de Poisson dans le puits quantique du gaz 2D du HEMT en considérant une quantification à 2 niveaux d'énergie. Celui-ci est calculé dans 3 régions distinctes (Vg inférieure à la tension de pincement, Vg modérée, Vg forte). La force de ce modèle réside sur la formulation du potentiel de surface pour toutes les tensions V<sub>g</sub> par la relation suivante dont l'erreur est de l'ordre du femtovolt [1] :

$$E_{f,\text{unified}} = V_{\text{go}} - \frac{2V_{th} \ln\left(1 + e^{\frac{V_{go}}{2V_{th}}}\right)}{\frac{1}{H(V_{go})} + \frac{C_g}{qD} e^{-\frac{V_{go}}{2V_{th}}}}$$

(1)

$$V_{\text{go}} + V_{\text{th}} \left[1 - \ln(\beta V_{\text{gon}})\right] - \frac{V_0}{3} \left(\frac{C_g V_{\text{go}}}{qD}\right)^{2/3}$$

Où  $V_{g0} = V_{gs} - V_{off}$ ,  $V_{off}$  la tension de pincement,  $V_{th}$  la tension à l'équilibre thermique/tension thermique, q la charge de l'électron, D la densité d'état électronique.

Le courant Id et les charges intrinsèques s'expriment naturellement en fonction de ce potentiel de surface. Leur intégration le long du canal intrinsèque conduit à une expression pour Id et pour les charges intrinsèques (Qg, Qs et Qd) en fonction du potentiel de surface calculé aux extrémités source ( $\psi_s$ ) et drain du canal ( $\psi_d$ ). Le courant de drain Id est alors établi :

$$I_d = \frac{W}{L} \mu C_g (V_{g0} - \psi_m + V_{th}) \psi_{ds}$$

(2)

Où W est la largeur du canal, L la longueur du canal,  $\mu$  la

mobilité des électrons, Cg la capacité de grille par unité de surface,  $\psi_m = (\psi_s + \psi_d)/2$  le potentiel de surface au point milieu.

Pour les charges, un partitionnement de type Ward-Dutton est utilisé [8]:

$$Q_d = \int_0^L \frac{x}{L} Q_{ch}(V_g, V_x) dx \tag{3}$$

$$Q_{s} = \int_{0}^{L} \left( 1 - \frac{x}{t} \right) Q_{ch}(V_{a}, V_{x}) dx \tag{4}$$

$$Q_a = -Q_s - Q_d \tag{5}$$

$Q_d = \int_0^L \frac{x}{L} Q_{ch}(V_g, V_x) dx$  (3)  $Q_s = \int_0^L \left(1 - \frac{x}{L}\right) Q_{ch}(V_g, V_x) dx$  (4)  $Q_g = -Q_s - Q_d$  (5)  $Q_{ch}$  s'exprime en fonction du potentiel de surface. L'intégration le long de la grille conduit donc également à des charges qui s'expriment entièrement à partir du régime DC. Les expressions présentées ici étant incomplètes, d'autres effets doivent être définis pour obtenir un modèle plus précis. Il s'agit notamment de la mobilité dépendante du Champ électrique, de la modulation de la longueur du canal, de la température... comme le montre la figure 2.

Figure 2. Représentation des effets pris en compte dans le modèle ASM

L'effet d'auto-échauffement correspond, comme son nom l'indique, à l'échauffement du transistor lors de son utilisation. La dégradation de la mobilité ainsi que la saturation de la vitesse, induites par les composantes verticales effectives et latérales du champ électrique, respectivement, impliquent des perturbations sur la mobilité et sur la vitesse des électrons dans le canal. La modulation de la longueur du canal, majoritairement induite par l'expansion du canal vers la source, correspond à la diminution de la longueur du canal. Cette réduction de la longueur du canal accentue le phénomène d'abaissement de la barrière de potentiel (DIBL) qui apparaît lorsqu'une tension Vg, inférieure à la tension de pincement Voff, est utilisée avec une tension de drain Vd importante. Comme la longueur du canal diminue, la tension V<sub>d</sub> augmente ce qui favorise l'expansion du canal vers la source de la couche de déplétion induisant un abaissement de la barrière de potentiel. Cet abaissement tend à contribuer à l'apparition de courant de fuite.

D'autres fuites de courant ont été observées dans la zone précédant la zone de pincement, zone où il n'est pas supposé y avoir de transition d'électrons. Ces fuites sont caractérisées par le phénomène dit de pente de sous-seuil. La température influençant la majorité de ces phénomènes, il est nécessaire de parfaitement la connaitre et de la contrôler. Ainsi une dépendance en fonction de la température est présente pour un bon nombre de paramètres.

Concernant les phénomènes de pièges ou de Field Plate, ces derniers sont encore mal connus pour être incorporés dans le modèle de courant de drain I<sub>d</sub> complet. En ajoutant les relations des phénomènes physiques présentés cidessus au modèle de courant de drain I<sub>d</sub>, la figure 2 devient la figure 3:

Figure 3. Représentation des effets par leurs relations pris en compte dans le modèle ASM

## 3. Résultats et Discussion

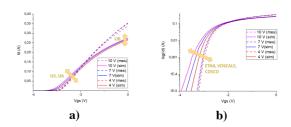

Le modèle ASM présenté ci-dessus a été simulé et comparé à des mesures DC que nous avons réalisées au laboratoire. Connaissant les caractéristiques du transistor (type, taille, nombre de doigts, etc...), le modèle est alors ajusté pour ainsi définir au mieux les paramètres du modèle. La Figure 4 illustre notamment la prise en charge de la dégradation de la mobilité avec le champ (4.a) et des effets de canal court (4.b) (DIBL) sur un transistor 8x50μm avec une largeur de grille de 0.15μm. En effet, des paramètres permettent de régler la courbe I<sub>d</sub> (V<sub>d</sub>) dans le régime de transition tandis qu'un autre règle le plateau. L'action des paramètres d'effets de canal court est plus visible en échelle logarithmique (4.b). Un paramètre contrôle la précision sur la tension de pincement et d'autres gèrent le coefficient de pente et l'espacement entre les différentes tensions V<sub>d</sub>.

Figure 4. Exemple d'ajustement avec dégradation de la mobilité (a.) et effets de canal court (b.)

Le modèle ASM complet comporte de nombreux paramètres qui agissent parfois sur la même région. Parmi ces paramètres certains sont géométriques et connus, d'autres sont à déterminer comme, par exemple, les résistances d'accès. Les résistances d'accès (côté drain et côté source) s'expriment par la formule:

$$R_{drain} = \frac{_{RDC(T)}}{_{w\cdot NF}} + TRAPRD.vcap + R_{trap}(T) + ron_{trap}$$

$$+ \frac{_{LDG}}{_{W.NF.q.NSOACCD.U0ACCD}} \cdot \left(1 - \left(\frac{l_{ds}}{l_{sat,drain}}\right)^{MEXPACCD}\right)^{\frac{-1}{MEXPACCD}}$$

Dans cette expression, nous reconnaissons notamment l'influence de la résistance de contact RDC, celle des effets de pièges s'ils existent (R<sub>trap</sub>(T), ron<sub>trap</sub>, TRAPRD. vcap), ainsi que la résistance d'un accès au canal 2D constituée de NF doigts de largeur W, de longueur LGD, de conductivité électrique (q. NSOACCD. UOACCD) où NS0ACCD U0ACCD sont des et constantes correspondantes respectivement à la densité d'électron dans le gaz 2D d'accès ainsi que la mobilité dans la zone d'accès de la résistance de drain. Le couple de paramètres (I<sub>sat,drain</sub>, MEXPACCD) permet de moduler cette résistance en fonction du niveau de courant dans le composant.

L'art de la modélisation repose essentiellement sur la réalisation de mesures précises et adaptées à l'identification des paramètres du modèle suivant un processus bien déterminé. À la suite de ce processus, un modèle adapté est obtenu comme le montre la figure 5.

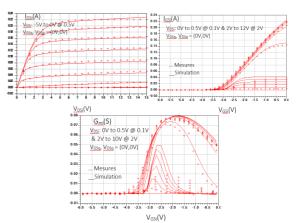

Figure 5. Mesures DC et simulation de courbes  $I_d(V_d)$  et  $I_d(V_g)$  sur un transistor  $8x50\mu m$

Des mesures IV impulsionnelles ont également été effectuées sur un transistor 4 x 50 µm avec une longueur de grille de 0.15 µm afin de caractériser l'influence des pièges sur le transistor comme le montre les figures 6 et 7. Ces mesures I(V) impulsionnelles et simulations I<sub>d</sub>(V<sub>d</sub>),  $I_d(V_g)$  et transconductance  $G_m(V_g)$  ont été réalisées à 25°C au point de polarisation de repos pour différentes  $V_{\rm g}$  et  $V_{\rm d}$ respectivement allant de -5V à 0V par pas de 0.5V pour  $I_d(V_d)$ , de 0V à 0.5V par pas de 0.1V et 2V à 12V par pas de 2V pour  $I_{\text{\tiny d}}(V_{\text{\tiny g}})$  ainsi que de 0V à 0.5V par pas de 0.1V et de 2V à 10V par pas de 2V pour les mesures de transconductances. Les points représentent les données mesurées et les traits continus les données simulées. Il existe cependant un écart entre les mesures et la simulation notamment pour des valeurs de V<sub>d</sub> inférieures à 0.5V pour la transconductance. En pulsé, la variation de température sur le transistor au point de polarisation choisie est négligeable ce qui implique que les phénomènes dépendants de la température ne le sont plus. Les paramètres utilisés pour contrôler des parties de courbes ne seront pas aussi « efficace » en pulsé qu'en DC. Les effets de pièges, bien que le point de polarisation

choisi limite le plus possible l'effet des pièges sur les caractéristiques de sortie, sont toujours présent et joue un rôle sur l'écart entre les simulations et les mesures. Il est aussi possible que cet écart soit lié à l'imprécision des équations des résistances d'accès.

Figure 6. Mesures IV impulsionnelles et simulation de courbes  $I_d(V_d)$ ,  $I_d(V_g)$  et  $G_m$  sur un transistor  $4x50\mu m$

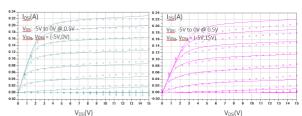

Afin de montrer l'influence des effets de pièges sur le transistor, trois courbes  $I_d(V_d)$  ont été comparées. Elles ont toutes les trois été réalisées à 25°C sur un transistor avec des  $V_g$  allant de -5V à 0V par pas de 0.5V, mais avec différents points de polarisation. En effet, la courbe rouge sur la figure 6 est au point de repos (0,0), la courbe verte et violette, sur la figure 7, représente respectivement le phénomène de gate-lag (–5,0) et de drain-lag (-5,15). On remarque que les pointillés, qui correspondent aux mesures, ne coïncident pas avec les résultats de simulations, en trait plein, dans la région ohmique et dans la région saturée lorsque le canal est semi-ouvert. Le modèle de piège présent dans ASM ne prend donc pas correctement en compte les phénomènes de pièges dans le transistor.

Figure 7. Courbes  $I_d(V_d)$  impulsionnelles pour différents points de polarisations sur un transistor  $4x50\mu m$

Les charges intrinsèques  $Q_{si}$ ,  $Q_{di}$  et  $Q_{gi}$  dont des charges stockées au sein du transistor extraites à partir de la charge du canal exprimée en fonction du potentiel de surface. Les paramètres S sont également mesurés afin de valider le jeu de paramètres obtenu pour modéliser les sources de courant correspondant à la caractéristique courant-tension intrinsèque du composant. Il s'agit d'une comparaison mesures-modèles petit signal pour  $V_d$ =10V et  $I_d$ =10V et

35GHz. La comparaison des coefficients de réflexion S11 et S22, des coefficients de transmission S12 et S21 ainsi que le module du gain maximum (MAG) sont présentés figure 8.

Figure 8. Paramètres S sur un transistor 4x50 $\mu$ m avec le MAG pour 2 courants différents et la magnitude pour S12 et S21.

Les écarts les plus significatifs portent sur  $S_{22}$  et  $S_{12}$ . Ceci provient à la mauvaise évaluation des éléments intrinsèques, d'une représentation simplifiée de la jonction de drain et de l'absence de modèle des effets dispersifs.

## 4. Conclusion

Nous avons présenté le modèle ASM, initialement développé dans [1] permettant de définir le courant Id et les charges intrinsèques à partir du potentiel de surface. Ce modèle analytique « physique » permet de prendre en compte de nombreux effets parasites présents dans les HEMT. Notre travail initial a consisté à prendre en main ce modèle écrit en « verilog A » et à l'intégrer pour une utilisation sous ADS. La 2e étape consiste désormais à établir clairement le protocole de mesures nécessaires à l'extraction dudit modèle. La suivante consistera à intégrer au modèle ASM le savoir-faire d'XLIM en termes de pièges et de thermique. Notre vecteur de test repose sur la filière HEMT GaN de la fonderie UMS (longueur de grille  $0.15\mu$ m). Nous adresserons ensuite une longueur de

grille de 100 nm qui permettra de valider l'adaptation du modèle ASM à la montée en fréquence.

#### Remerciements

Les auteurs tiennent à remercier le Labex GaNext et le projet GREAT pour leur soutien financier.

#### Références

- [1] S. Khandelwal, Y.S. Chauhan, and T.A. Fjeldly, « Analytical Modeling of Surface-Potential and Intrinsic Charges in AlGaN/GaN HEMT Devices », IEEE Transactions on Electron Devices, vol. 59, no. 8, Octobre 2012

- [2] U. K. Mishra, L. Shen, T. E. Kazior and Y.-F. Wu, « GaN-based RF power devices and amplifiers », Proc. IEEE, vol. 96, no. 2, pp. 287-305, Feb. 2008. [3] L. M. Tolbert, B. Ozpineci, S. K. Islam and M. S. Chinthavali, « Wide band-gap semiconductors for utility applications », Proc. Power Energy System, pp. 317-321, 2003-Feb.

- [4] A. Koudymov, M. S. Shur, G. Simin, K. Chu, P. C. Chao, C. Lee, et al., « *Analytical HFET* \\$\Lambda\\$\=\\$\ Model in presence of current collapse », *IEEE Trans. Electron Devices*, vol. 55, no. 3, pp. 712-720, Mar. 2008.

- [5] S. Kola, J. M. Golio and G. N. Maracas, « An analytical expression for Fermi Level versus sheet carrier concentration for HEMT modelling », IEEE Electron Device Lett., vol. 9, no. 3, pp. 136-138, Mar. 1988.

- [6] X. Cheng and Y. Wang, « A surface-potential-based compact model for AlGaN/GaN MODFETs », IEEE Trans. Electron Devices, vol. 58, no. 2, pp. 448-454, Feb. 2011.

- [7] P. Bendix, "Detailed comparison of SP2010 EKV and BSIM3 models", Proc. Intl. Conf. Model Symp. Microsyst., pp. 649, 2002.

- [8] D.E.Ward and R.W. Dutton, « A Charge-Oriented Model for MOS Transistor Capacitances », Journal Of Solid-State circuits, vol. sc-13, no. 5, oct 1978

- [9] Franz Sischka, « Experiences with Using the ASM-HEMT Model for III/IV HEMTs », Bipolar Arbeitskreis (Bip-AK) Meeting, Crolles, Nov. 2019