# Selective sublimation of GaN and regrowth of AlGaN to co-integrate enhancement mode and depletion mode high electron mobility transistors

Thi Huong Ngo, Rémi Comyn, Sébastien Chenot, Julien Brault, Maud Nemoz, Philippe Vennéguès, Benjamin Damilano, S. Vézian, Eric Frayssinet, Flavien Cozette, et al.

### ▶ To cite this version:

Thi Huong Ngo, Rémi Comyn, Sébastien Chenot, Julien Brault, Maud Nemoz, et al.. Selective sublimation of GaN and regrowth of AlGaN to co-integrate enhancement mode and depletion mode high electron mobility transistors. Journal of Crystal Growth, 2022, 593, pp.126779. 10.1016/j.jcrysgro.2022.126779. hal-03741626

HAL Id: hal-03741626

https://hal.science/hal-03741626

Submitted on 18 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Selective sublimation of GaN and regrowth of AlGaN to co-integrate enhancement mode and depletion mode high electron mobility transistors

Thi Huong Ngo<sup>1</sup>, Rémi Comyn<sup>1</sup>, Sébastien Chenot<sup>1</sup>, Julien Brault<sup>1</sup>, Maud Nemoz<sup>1</sup>, Philippe Vennéguès<sup>1</sup>, Benjamin Damilano<sup>1</sup>, Stéphane Vézian<sup>1</sup>, Eric Frayssinet<sup>1</sup>, Flavien Cozette<sup>2</sup>, Nicolas Defrance<sup>3</sup>, François Lecourt<sup>4</sup>, Nathalie Labat<sup>5</sup>, Hassan Maher<sup>2</sup> and Yvon Cordier<sup>1\*</sup>

\*Corresponding author: yc@crhea.cnrs.fr

#### ABSTRACT.

In the present study, the selective sublimation of the p-GaN cap layer of Al(Ga)N/GaN HEMTs is developed to replace the commonly used dry etching with no risk of damage in the barrier layer in order to fabricate enhanced mode transistors. Thanks to this approach, enhancement-mode transistors are fabricated with a threshold voltage between 0V and +1.5V depending on the barrier layer aluminum molar fraction and thickness. Furthermore, we show the benefit of the combination of selective sublimation with the regrowth of AlGaN to reduce access resistance in these transistors which can be co-integrated with depletion-mode devices fabricated in the same process in areas where p-GaN has been totally evaporated.

**Keywords:** A1. Selective sublimation, A3. Local area epitaxy, B1. Group III-Nitrides, B3. High electron mobility transistors

#### Introduction

High electron mobility transistors (HEMTs) based on the AlGaN/GaN heterostructure have shown interests in many power applications that benefit from outstanding properties of GaN material such as high breakdown voltage, high electron velocity and good thermal conductivity [1]. To date, the main successes in GaN electronics have been obtained with depletion-mode (D-mode) devices [2-4]. Implementation of enhancement-mode (E-mode) transistors, which is much more difficult to achieve, is one of the biggest challenges to fulfilling the functionality of GaN HEMTs. After many intensive efforts, E-mode GaN

<sup>&</sup>lt;sup>1</sup>Université Côte d'Azur, CNRS, CRHEA, rue Bernard Grégory, 06560 Valbonne, France

<sup>&</sup>lt;sup>2</sup>Laboratoire Nanotechnologies Nanosystèmes, CNRS-UMI-3463, 3IT, Université de Sherbrooke, 3000 Bd de l'université, Sherbrooke, J1KOA5, QC, Canada.

<sup>&</sup>lt;sup>3</sup>CNRS-IEMN – Université de Lille, UMR8520, Av. Poincaré, 59650 Villeneuve d'Ascq, France

<sup>&</sup>lt;sup>4</sup>OMMIC, 2 rue du Moulin, 94450 Limeil-Brévannes, France

<sup>&</sup>lt;sup>5</sup>Laboratoire de l'Intégration du Matériau au Système, Université de Bordeaux, Talence, France

transistors have been attained through multiple approaches [5-11]. For example, fluorine implantation and gate recess are proposed to shift the threshold voltage  $V_{th}$  of AlGaN/GaN HEMTs from a naturally negative value towards a positive one, and then to produce an E-mode device [5-8]. However, the thermal stability of fluorine implantation remains questionable and the recess etching of the barrier layer is difficult without any electrical degradation impacting the device performance.

Using a thin AlN barrier, less than 2 nm, can prevent two-dimensional electron gas (2DEG) formation, and hence can shift the threshold voltage  $V_{th}$  to a positive value [10], however it also can induce a dramatic reduction of the device current because of large access resistances. The use of a p-type doped GaN cap layer to raise the conduction band is another efficient method to shift the threshold voltage towards positive values [11], but in that case the p-GaN should be present only just under the metal gate to allow the electrons to flow through the source and drain access regions of the transistors. This can be obtained by local area growth of the p-GaN gate with difficulties associated with regrowth interface contamination with n-type dopants like silicon [12]. For this reason, most of the developments are based on dry etching of the p-GaN cap layer grown planar on Al(Ga)N/GaN HEMT heterostructures. Again, dry etching of p-GaN necessitates a very careful process to limit electrical damages possibly induced at the surface or inside the Al(Ga)N barrier with an additional difficulty concerning the selectivity of etching with respect to Al(Ga)N. To circumvent those drawbacks, we propose to use an innovative technology consisting of selective evaporation [13,14] of p-GaN and the regrowth of AlGaN material. It will significantly reduce the electrical resistance in the E-mode transistor access regions [15,16] and provide elsewhere the negative threshold voltage desired for D-mode co-integrated devices.

#### **Process description**

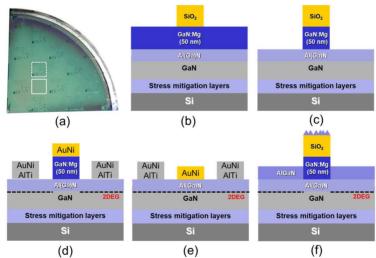

The main steps of the process are depicted in Fig.1. The Al(Ga)N/GaN HEMT epi-layers are first grown by molecular beam epitaxy (MBE) on a Si(111) substrate. After nucleation of an AlN layer and growth of an AlGaN/AlN stress mitigation stack, a 1.5 μm thick GaN buffer layer is grown followed by the Al(Ga)N barrier. In the present study, two kinds of barriers are grown: either a 15 nm thick Al<sub>0.26</sub>Ga<sub>0.74</sub>N barrier, or a thin 2 nm AlN barrier. These HEMTs structures are grown in a Riber Compact 21 reactor equipped with an ammonia source [17]. A 50 nm thick p-type doped GaN cap layer is regrown on these structures in another reactor, a Riber 32 equipped with a solid Magnesium source [18]. The epilayer is covered by a 100 nm thick SiO<sub>2</sub> mask layer deposited by plasma enhanced chemical vapour deposition (PECVD) at 350°C. Large patterns of 4x4 mm² squares are formed by using photolithography and reactive ion etching (RIE) to define the areas for fabrication of E-mode and D-mode operation HEMTs (Fig. 1a). To form the E-mode device, the SiO<sub>2</sub> mask is kept on areas where the p-GaN has to be protected from any evaporation, i.e. gate patterns (Fig.1b). Then the sample is transferred into the MBE reactor for GaN sublimation

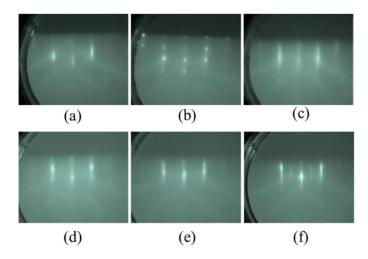

(Fig.1c). The selective evaporation is performed under ultra-high vacuum after heating the sample under ammonia and stopping the gas supply once the desired temperature between 850 and 900°C is reached. Evaporation proceeds at pressure below 10<sup>-7</sup> Torr via the formation of islands [13]. Reflection high energy electron diffraction (RHEED) is employed to detect when the evaporation reaches the Al(Ga)N layer and the spotty pattern recovers to streaky (Fig.2a-d). The evaporation is stopped due to the high thermal stability of AlN. Even when Ga and N could leave the surface of AlGaN, the latter could become Al-rich AlGaN or pure AlN which don't decompose. Then, a nominal ammonia flow of 200 sccm is restored and the sample is either cooled-down for E-mode (Fig.1d) and D-mode (Fig.1e) transistor fabrication or a 20 nm thick of Al<sub>0.7</sub>Ga<sub>0.8</sub>N barrier layer is regrown to form D-mode devices as well as source/drain access regions of the E-mode HEMTs (Fig.1f). As shown in Fig.2e, the streaky RHEED pattern is preserved attesting to a 2D growth of AlGaN with metal polarity evidenced by the surface reconstruction [19] shown in Fig.2f. The device process steps start with the SiO<sub>2</sub> mask removal with a buffered oxide etchant (BOE) followed by mesa isolation using Cl<sub>2</sub>/Ar/CH<sub>4</sub> RIE. Ohmic contacts of Ti/Al/Ni/Au are deposited, followed by a rapid thermal annealing at 750°C in a nitrogen atmosphere in 30s, consistently obtaining a contact resistance of 0.2-0.3 Ω.mm. For the aim of fabricating the D-mode and E-mode devices at the same time, gate contacts of Ni/Au sequences are evaporated simultaneously on the p-GaN layer of the E-mode devices and on the Al(Ga)N layer of the D-mode ones. Other metal stacks of Ni/Au are then deposited to form the pads of gate and Ohmic contacts for electrical measurements with the needle probes. The last step consists of the on-wafer electrical characterizations including Hall effect and DC I-V.

**Figure 1**. Schematic of the fabrication process enabling the co-integration: (a) photograph of the quarter wafer with SiO<sub>2</sub> patterned for E-mode transistors (area defined by a dashed line) and D-mode devices (area defined by a continuous line); (b) Definition of the E-mode gate pattern on the initial epi-layers covered with SiO<sub>2</sub>; (c) sublimation of the p-GaN cap; (d) fabrication of an E-mode transistor; (e) fabrication of a D-mode transistor; (f) alternative process with regrowth of AlGaN after p-GaN sublimation.

**Figure 2.** RHEED patterns of (a) the GaN surface at 900°C under NH<sub>3</sub>; (b) 1 min and c) 50 min after closing the NH<sub>3</sub> supply; (d) at 800°C under NH<sub>3</sub>; (e) after AlGaN regrowth and (f) at 500°C under NH<sub>3</sub>.

#### Structural analysis

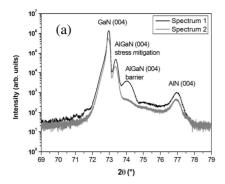

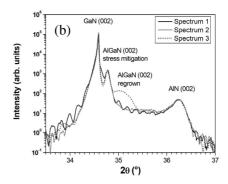

The crystalline quality of the epilayers was assessed by X-ray diffraction with a Panalytical X'PERT Pro MRD system. 2 theta-omega scans around (002) or (004) reflexions corresponding to planes perpendicular to the growth axis are reported in Fig.3. Spectra recorded on the HEMT structure with a 15 nm thick Al<sub>0.26</sub>Ga<sub>0.74</sub>N barrier and a 2 nm thick AlN barrier are reported in Fig.3a and Fig.3b respectively. In Fig.3b, the large difference of form factor and lattice parameter between AlN and GaN exacerbates the Pendellösung fringes generated by the presence of the 50 nm p-GaN cap (spectrum 1). The fringes totally disappear in spectrum 2 owing to the fact that the remaining p-GaN occupies a very limited fraction of the surface corresponding to the gate patterns of E-mode transistors. However, such process revealed a totally depleted structure not compatible with the fabrication of transistors, so that the regrowth of AlGaN has been achieved after sublimation of p-GaN on another piece of the original sample. Fig.3b clearly shows the rise of a new peak due to the regrown Al<sub>0.2</sub>Ga<sub>0.8</sub>N layer (spectrum 3) that covers almost the totality of the sample. Also, the AlGaN barrier peak present in spectrum 1 of Fig.3a almost disappeared since spectrum 2 has been recorded after the device process in which a large part was etched for device isolation. On the other hand, for both kinds of structures, negligible change is noticed for other features like peaks due to the thick GaN buffer, the AlGaN in the stress mitigating stack and the AlN nucleation layer.

**Figure 3.** X-ray diffraction 2 theta-omega scans (a) around the (004) reflexion for the initial HEMT with 15 nm thick Al<sub>0.26</sub>Ga<sub>0.74</sub>N barrier covered with p-GaN (spectrum 1) and after p-GaN selective sublimation (spectrum 2); (b) around the (002) reflexion for the initial HEMT with 2 nm AlN barrier covered with p-GaN (spectrum 1), after p-GaN selective sublimation (spectrum 2) and after AlGaN regrowth (spectrum 3).

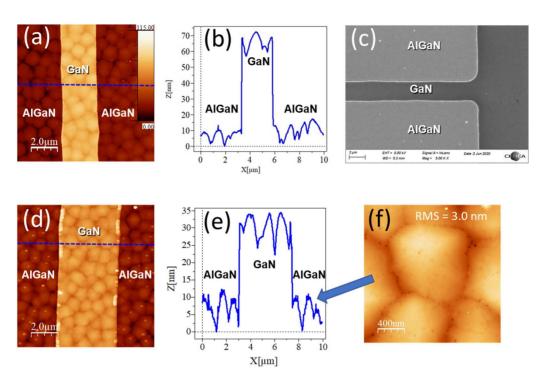

The selectivity of GaN sublimation against Al(Ga)N barrier was demonstrated with RHEED (Fig.2) and confirmed by scanning electron microscopy (SEM), atomic force microscopy (AFM) and cross-section transmission electron microscopy (TEM) as shown in the next section. Furthermore, the AFM analysis confirms that the gate pattern defined with SiO<sub>2</sub> is replicated into the p-GaN after sublimation (Fig.4a-c). The morphology of the p-GaN surface as well as that of the AlGaN revealed after GaN evaporation is similar and typical for ammonia-MBE grown materials. The mounds with a typical diameter of 1 µm generate a moderate roughness with a root mean square value (RMS) less than 5 nm [20]. We recall that the RHEED patterns of the corresponding samples are streaky and this morphology doesn't affect the electron mobility of the two-dimensional electron gas (2DEG) as shown in our previous studies [12-17]. Fig.4d-f show the gate region after the regrowth of AlGaN. Again, similar surface morphologies are obtained. As the AlGaN regrowth is not totally selective with respect to SiO<sub>2</sub>, the latter has to be sufficiently thick to allow the lift-off of crystallites eventually nucleated on it (Fig.1f). The few spots present on Fig.4d are due to an incomplete cleaning after the removal of SiO<sub>2</sub> into a BOE 7:1 solution. The RMS roughness of the regrown AlGaN is 3 nm and unchanged compared to the one measured before and after p-GaN sublimation (Fig.4a). The pits seem at the surface of AlGaN with a density estimated to a few 10<sup>9</sup>/cm<sup>2</sup> are due to threading dislocations. Such a defect density is typical for the epilayer stack grown for this study [17].

**Figure 4.** a) AFM view of a gate pattern after sublimation of the 50 nm GaN cap on the 15 nm AlGaN layer covered with SiO<sub>2</sub> mask; b) height profile of the gate pattern; c) SEM view of gate pattern; d) AFM view of a gate pattern after evaporation of the 50 nm GaN cap on the 2 nm AlN layer and regrowth of 20 nm AlGaN layer; (e) height profile of the gate pattern; (f) AFM view of the surface of the regrown AlGaN.

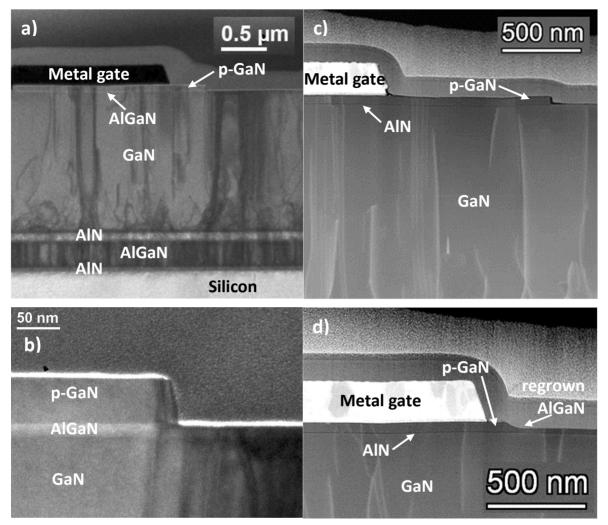

Cross-section TEM observations performed after device fabrication and electrical characterizations complement this analysis of the p-GaN gate pattern definition. The cross-section views at different magnifications of the gate edge region of a transistor with p-GaN on  $Al_{0.26}Ga_{0.74}N$  barrier are shown in Fig. 5a-b. The observations are performed along the (11-20) zone axis. The darker pattern located on the p-GaN layer corresponds to the metal Schottky gate contact. In Fig.5a, the image shows threading dislocations of a+c type as well as a type ones. The picture demonstrates the filtering of dislocations in the bottom region of the GaN buffer grown on the AlGaN/AlN stress mitigation stack. The location of threading dislocations is random and despite the large density estimated in the mid  $10^9/\text{cm}^2$ , their presence doesn't affect the evaporation selectivity nor the definition of the p-GaN gate edge with a rather steep slope. Similar behaviour is noticed for the 2 nm AlN barrier HEMT as shown in Fig.5c where dislocations and gate metal appear bright due to the dark-field imaging conditions. Furthermore, a perfect crystal continuity is noticed between the p-GaN at gate edge and the regrown  $Al_{0.2}Ga_{0.8}N$  layer as shown in Fig.5d.

**Figure 5**. Cross-section electron microscope views of p-GaN gate edge (a-b) on the 15 nm thick Al<sub>0.26</sub>Ga<sub>0.74</sub>N barrier, (c) on the 2 nm AlN barrier and (d) after regrowth of a 20 nm Al<sub>0.2</sub>Ga<sub>0.8</sub>N layer.

#### **Electrical characterizations**

The electrical properties of the 2DEG extracted from the Van der Pauw patterns fabricated on wafer areas where p-GaN was evaporated are summarized in Table I. It is clear from this table that a HEMT with a 2 nm AlN barrier can already produce an almost normally-off transistor as a sheet resistance around 1 MOhm/sq is measured. On the contrary, a 2.5 nm AlN barrier is enough to generate a 2DEG with a density of  $5 \times 10^{12}$ /cm² and a sheet resistance greater than 1 kOhm/sq. On the other hand, the HEMT with a 15 nm Al<sub>0.26</sub>Ga<sub>0.74</sub>N contains a 2DEG with a density between 4.3 and  $5 \times 10^{12}$ /cm² and a slightly lower resistance owing to a higher electron mobility. Such a mobility of 1500 cm²/V.s attests to the quality of the Al<sub>0.26</sub>Ga<sub>0.74</sub>N/GaN interface. Finally, after regrowth of Al<sub>0.2</sub>Ga<sub>0.8</sub>N the initially depleted HEMT with a 2 nm AlN barrier exhibits a 2DEG with a density of more than  $1.1 \times 10^{13}$ /cm² and a mobility greater than 1100 cm²/V.s resulting in a sheet resistance around 400 Ohm/sq.

**Table I.** Comparison of sheet resistances, 2DEG carrier densities Ns and electron mobility  $\mu$  deduced from Hall effect measurements performed on HEMT heterostructures grown with different barrier layers.

| Barrier layer                                          | Rsh (ohm/sq) | Ns (/cm²)              | μ (cm²/V.s) |

|--------------------------------------------------------|--------------|------------------------|-------------|

| 2 nm AlN                                               | 1 000 000    | n.a                    | n.a         |

| 2.5 nm AlN                                             | >1000        | $5x10^{12}$            | ~1000       |

| 15 nm Al <sub>0.26</sub> Ga <sub>0.74</sub> N          | 800-900      | $4.3-5 \times 10^{12}$ | >1500       |

| 20 nm Al <sub>0.2</sub> Ga <sub>0.8</sub> N + 2 nm AlN | 400-414      | >1.1 x10 <sup>13</sup> | >1100       |

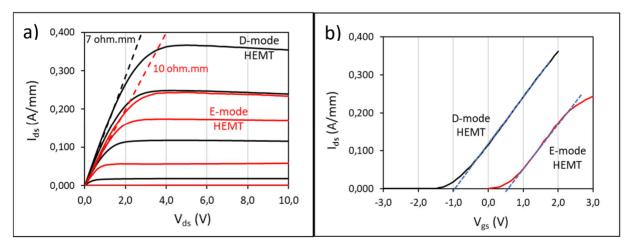

Figure 6 shows the output and transfer characteristics of co-integrated 2.5  $\mu$ m gate E-mode and D-mode transistors fabricated on the 15 nm Al<sub>0.26</sub>Ga<sub>0.74</sub>N barrier HEMT. The drain to source distance is 9.5  $\mu$ m. The sheet resistance deduced from the measurements on transmission line method (TLM) devices is in the same range as the one measured on Van der Pauw patterns and extrapolation of the resistances indicates contact resistances around 0.5 Ohm mm. At  $V_{gs} = 0$  V the maximum drain current of the D-mode transistor is  $I_{ds}$ =116 mA/mm and it reaches 360 mA/mm at  $V_{gs}$  = +2 V. The threshold voltage  $V_{th}$  defined at 1 mA/mm is around -1.5 V. A total resistance  $R_{on}$  of 7 Ohm.mm is deduced from the slope of the linear region of output characteristics  $I_{ds}$ - $V_{ds}$ . On the other hand, the total resistance  $R_{on}$  of the E-mode transistor is 10 Ohm.mm. The threshold voltage  $V_{th}$  is between 0 V and +0,7 V and for a gate bias  $V_{gs}$  of +2 V a drain current of 175 mA/mm is measured. Further increase of  $V_{gs}$  to +3 V allows to reach 245 mA/mm.

Figure 6. (a) Output and (b) transfer characteristics at  $V_{DS} = 6$  V for the 2.5  $\mu$ m gate E-mode and D-mode HEMTs with a 15 nm AlGaN barrier.

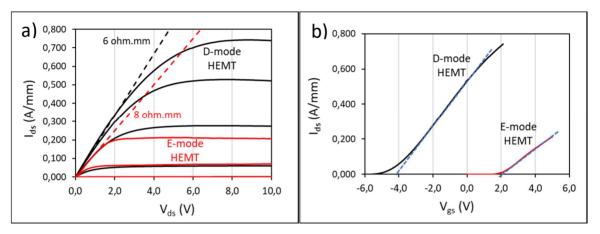

We failed to fabricate transistors on a 2 nm AlN barrier HEMT due to the high sheet resistance around 1 MOhm/sq. Only the regrowth of AlGaN allowed us to obtain contacts with an ohmic behaviour. Figure 7 shows the output and transfer characteristics of co-integrated E-mode and D-mode transistors fabricated on the 2 nm AlN barrier HEMT after the p-GaN sublimation and the 20 nm  $Al_{0.2}Ga_{0.8}N$  layer regrowth. The contact resistance extracted from TLM is 0.3 ohm.mm. The E-mode transistor exhibits a positive threshold voltage  $V_{th}$  slightly above 1.5 V and the drain current  $I_{ds}$  reaches 212 mA/mm at  $V_{gs}$  = +5 V. The regrowth of the  $Al_{0.26}Ga_{0.74}N$  layer onto the 2 nm AlN barrier allows a large number of electrons to populate the 2DEG at the AlN/GaN interface. It significantly reduces the electrical resistance in transistor access regions, hence results in the drain current  $I_{ds}$  of more than 200 mA/mm flowing between source and drain in the E-mode device. The total resistance  $R_{on}$  is around 8 Ohm.mm. Thanks to the regrown  $Al_{0.26}Ga_{0.74}N$  layer, the threshold voltage  $V_{th}$  of the D-mode co-integrated devices is shifted to a large negative value of -5.6 V. The total resistance  $R_{on}$  is 6 Ohm.mm and the drain current  $I_{ds}$  greater than 500 mA/mm at  $V_{gs}$  = 0 V, is beyond 700 mA/mm at  $V_{gs}$  = +2 V, which is almost twice the one previously achieved without AlGaN regrowth in the D-mode transistor fabricated on a 15 nm  $Al_{0.26}Ga_{0.74}N$  barrier.

Figure 7. (a) Output and (b) transfer characteristics at  $V_{DS} = 7$  V for the 2  $\mu$ m gate E-mode and D-mode HEMTs with a 15 nm AlGaN layer regrown on the 2 nm AlN barrier.

#### **Conclusions**

In this work, integration of E/D-mode GaN HEMTs has been demonstrated. Starting from an initial p-GaN/Al(Ga)N/GaN HEMT structure grown on Silicon substrate, the selective sublimation method is first used to pattern the p-GaN gate for the E-mode transistors. The process based on the evaporation of GaN under high vacuum in an MBE reactor makes it possible to co-integrate E-mode with D-mode transistors with balanced maximum drain currents for a structure with a 15 nm  $Al_{0.26}Ga_{0.74}N$  barrier layer. However, the threshold voltage  $V_{th}$  of the E-mode transistor remains limited below +0,7 V and the maximum drain currents are lower than 250 mA/mm, even for the D-mode transistor. For applications requiring both a more positive threshold voltage of the E-mode device and a higher maximum drain current of the D-mode one, we proposed to evaporate p-GaN grown on top of a 2 nm AlN barrier HEMT structure and to regrow a 20 nm  $Al_{0.2}Ga_{0.8}N$  barrier layer. The E-mode transistor exhibits a positive threshold voltage of more than 1.5 V and the drain current can exceed 200 mA/mm at  $V_{gs} = +5$  V. On the other hand, the D-mode device

exhibits a more negative pinch-off voltage of -5.6 V and a maximum drain current above 500 mA/mm at  $V_{gs}$ =0V. Beyond the feasibility of p-GaN sublimation to replace dry etching, this study shows that the necessary trade-off between the threshold voltage and the maximum drain current in the E-mode and in D-mode transistors is easier to achieve when the barrier layer design is combined with the regrowth of an additional barrier layer. Not only the regrowth allows the fabrication of co-integrated D-mode transistors, but it can significantly reduce the access resistances with resulting larger drain current in the E-mode devices.

#### **ACKNOWLEDGEMENTS**

This work was supported by French technology facility network RENATECH and the French National Research Agency (ANR) through the projects ED-GaN (ANR-16-CE24-0026) and the "Investissements d'Avenir" program GaNeX (ANR-11-LABX-0014). Prof. Borge Vinter is acknowledged for helpful reading of the manuscript.

#### References

- [1] R. Mitova, R. Ghosh, U. Mhaskar, D. Klikic, M.-X. Wang, and A. Dentella, "Investigations of 600-V GaN HEMT and GaN Diode for Power Converter Applications," IEEE Trans. Power Electron., vol. 29, no. 5, pp. 2441–2452, May 2014, doi: 10.1109/TPEL.2013.2286639.

- [2] W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M.Yamaguchi, "A 120-W Boost Converter Operation Using a High-Voltage GaN-HEMT", IEEE Electron Device Lett., vol. 29, no. 1, pp. 8-10, Jan. 2008, doi: 10.1109/LED.2007.910796.

- [3] P. Altuntas, F. Lecourt, A. Cutivet, N. Defrance, E. Okada, M. Lesecq, S. Rennesson, A. Agboton, Y. Cordier, V. Hoel and J.-C. De Jaeger, "Power Performance at 40 GHz of AlGaN/GaN High-Electron Mobility Transistors Grown by Molecular Beam Epitaxy on Si(111) Substrate," IEEE Electron Device Lett., vol. 36, no. 4, pp. 303–305, Apr. 2015, doi: 10.1109/LED.2015.2404358.

- [4] Y. Wen, M. Rose, R. Fernandes, R. V. Otten, H. J. Bergveld and O. Trescases, "A Dual-Mode Driver IC with Monolithic Negative Drive-Voltage Capability and Digital Current-Mode Controller for Depletion-Mode GaN HEMT" IEEE Trans. Power Electron., vol. 32, no. 1, pp. 423–432, Jan. 2017, doi: 10.1109/TPEL.2016.2537002

- [5] Z. H. Feng, R. Zhou, S. Y. Xie, J. Y. Yin, J. X. Fang, B. Liu, W. Zhou, Kevin J. Chen, S. J. Cai, "18-GHz 3.65-W/mm Enhancement-Mode AlGaN/GaN HFET Using Fluorine Plasma Ion Implantation", IEEE Electron Device Lett., vol. 31, no. 12, pp. 1386–1388, Dec. 2010, doi: 10.1109/LED.2010.2072901.

- [6] T. Oka and T. Nozawa, "AlGaN/GaN Recessed MIS-Gate HFET With High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications", IEEE Electron Device Lett., vol. 29, no. 7, pp. 668–670, Jul. 2008, doi: 10.1109/LED.2008.2000607.

- [7] Z. Xu, J. Wang, J. Liu, C. Jin, Y. Cai, Z. Yang, M. Wang, M. Yu, B. Xie, W. Wu, X. Ma, J. Zhang, Y. Hao, "Demonstration of Normally-Off Recess-Gated AlGaN/GaN MOSFET Using GaN Cap Layer as Recess Mask", IEEE Electron Device Lett., vol. 35, no. 12, pp. 1197–1199, Dec. 2014, doi: 10.1109/LED.2014.2359986.

- [8] H. Hahn, G. Lükens, N. Ketteniss, H. Kalisch, and A. Vescan, "Recessed-Gate Enhancement-Mode AlGaN/GaN Heterostructure Field-Effect Transistors on Si with Record DC Performance", Appl. Phys. Express, vol. 4, no. 11, p. 114102, Nov. 2011, doi: 10.1143/APEX.4.114102.

- [9] J. Kuzmik, C. Ostermaier, G. Pozzovivo, B. Basnar, W. Schrenk, J. Carlin, M. Gonschorek, E. Feltin, N. Grandjean, "Proposal and Performance Analysis of Normally Off GaN/InAlN/AlN/GaN HEMTs With 1-nm-Thick InAlN Barrier", IEEE Trans. Electron Devices, vol. 57, no. 9, pp. 2144–2154, Sep. 2010, doi: 10.1109/TED.2010.2055292.

- [10] D. F. Brown, K. Shinohara, A. Williams, I. Milosavljevic, R. Grabar, P. Hashimoto, P. J. Willadsen, A. Schmitz, A. L. Corrion, S. Kim, D. Regan, C. M. Butler, S. D. Burnham, and M. Micovic, "Monolithic Integration of Enhancement- and Depletion-Mode AlN/GaN/AlGaN DHFETs by Selective MBE Regrowth", IEEE Trans. Electron. Devices, vol. 58, no. 4, pp. 11063-1067, Apr. 2011, doi: 10.1109/TED.2011.2105268.

- [11] G. Greco, F. Iucolano, and F. Roccaforte, "Review of technology for normally-off HEMTs with p-GaN gate", Mater. Sci. Semicond. Process, vol. 78, pp. 96–106 (2018), http://doi.org/10.1016/j.mssp.2017.09.027

- [12] Y.Cordier, M.Azize, N.Baron, S.Chenot, O.Tottereau, J.Massies, "AlGaN/GaN HEMTs regrown by MBE on epi-ready semi-insulating GaN-on-Sapphire with inhibited interface contamination", J. Cryst. Growth 309, 1-7 (2007).

- [13] T. H. Ngo, R. Comyn, S. Chenot, J. Brault, B. Damilano, S. Vézian, E. Frayssinet, F. Cozette, C. Rodriguez, N. Defrance, F. Lecourt, N. Labat, H. Maher, and Y. Cordier, "Selective GaN sublimation and local area regrowth for co-integration of enhancement mode and depletion mode Al(Ga)N/GaN high electron mobility transistors", Semicond. Sci. Technol. 36 (2020) 024001, https://doi.org/10.1088/1361-6641/abcbd3.

- [14] B. Damilano, S. Vézian, J. Brault, B. Alloing, and J. Massies, "Selective Area Sublimation: A Simple Top-down Route for GaN-Based Nanowire Fabrication", Nano Lett (2016), 16, 1863-1868, https://doi.org/10.1021/acs.nanolett.5b04949.

- [15] W. Jiang, H. Tang and J. A. Bardwell, "Normally-off AlGaN/GaN high electron mobility transistors on Si substrate with selective barrier regrowth in ohmic regions", Semicond. Sci. Technol. 36 (2021) 05LT01, https://doi.org/10.1088/1361-6641/abecab.

- [16] H. Jiang, R. Zhu, Q. Lyu, C. W. Tang and K. M. Lau, "Thin-barrier heterostructures enabled normally-OFF GaN high electron mobility transistors", Semicond. Sci. Technol. 36 (2021) 034001.

- [17] N.Baron, Y.Cordier, S.Chenot, P.Vennéguès, O.Tottereau, M.Leroux, F.Semond, and J.Massies, "The critical role of growth temperature on the structural and electrical properties of AlGaN/GaN high electron mobility transistor heterostructures grown on Si(111)", J. Appl. Physics 105, 033701 (2009).

- [18] S. Brochen, J. Brault, S. Chenot, A. Dussaigne, M. Leroux, and B. Damilano, "Dependence of the Mgrelated acceptor ionization energy with the acceptor concentration in p-type GaN layers grown by molecular beam epitaxy", Appl. Phys. Lett., 103 (2013) 032102.

- [19] F. Semond, Y. Cordier, N. Grandjean, F. Natali, B. Damilano, S. Vézian, and J. Massies, "Molecular beam epitaxy of group-III nitrides on silicon substrates", Growth, Properties and Device Applications, Phys. Status Solidi A 188 (2001) 501-510.

- [20] S. Vézian, F. Natali, F. Semond, and J. Massies, "From spiral growth to kinetic roughening in molecular-beam epitaxy of GaN(0001)", Phys. Rev. B 69 (2004) 125329.