### ERTS 2022 proceedings

Philippe Cuenot, Marie de Roquemaurel, Kevin Delmas, Jean-Marc Gabriel, Adrien Gauffriau, Christophe Grand, Éric Jenn, Mohamed Kaâniche, Benoît Morgan

### ▶ To cite this version:

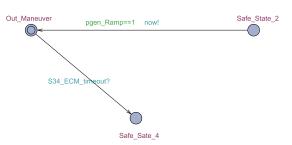

Philippe Cuenot, Marie de Roquemaurel, Kevin Delmas, Jean-Marc Gabriel, Adrien Gauffriau, et al.. ERTS 2022 proceedings. 2022. hal-03704287

### HAL Id: hal-03704287 https://hal.science/hal-03704287v1

Submitted on 10 Oct 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# EMBEDDED REAL TIME SYSTEMS

ORGANIZED BY

PROCEEDINGS

### Editors

| Mohamed Kaaniche     | LAAS-CNRS - France                        |

|----------------------|-------------------------------------------|

| Philippe Cuenot      | Continental Automotive, IRT Saint Exupéry |

| Marie de Roquemaurel | Airbus Defence & Space                    |

| Kevin Delmas         | Onera                                     |

| Jean-Marc Gabriel    | Renault Software Labs                     |

| Adrien Gauffriau     | Airbus                                    |

| Christophe Grand     | Onera                                     |

| Eric Jenn            | Thales Avionics, IRT St Exupéry           |

| Benoît Morgan        | IRIT                                      |

|                      |                                           |

# Contents

| Contents                                                                                                                                             | 3               |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Program Committee                                                                                                                                    | 7               |

| We.1.A - GPU                                                                                                                                         | 9               |

| Real-time high performance computing platform using a Jetson Xavier AGX PasTiS: building an NVIDIA Pascal GPU simulator for embedded AI applications | $\frac{11}{21}$ |

| We.1.B – Model Driven Engineering I                                                                                                                  | <b>31</b>       |

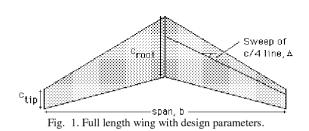

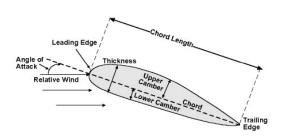

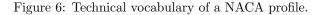

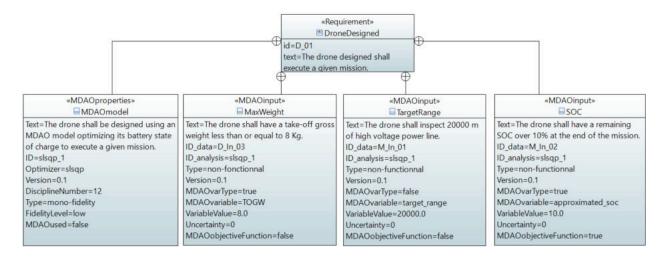

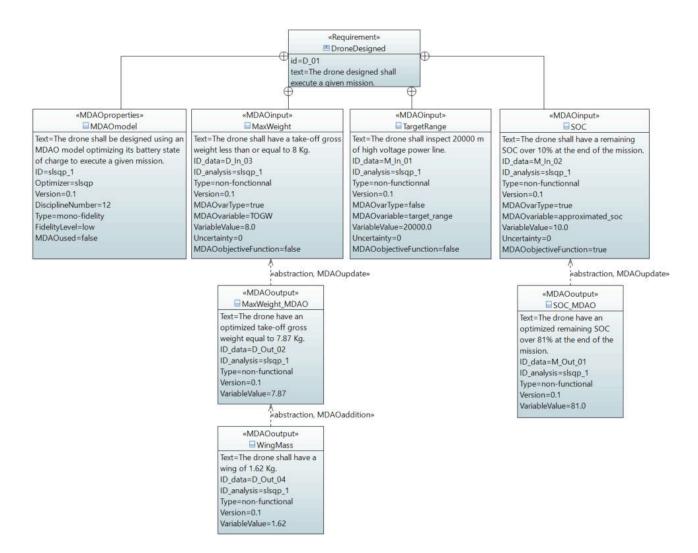

| Sizing a Drone Battery by coupling MBSE and MDAO                                                                                                     | 33              |

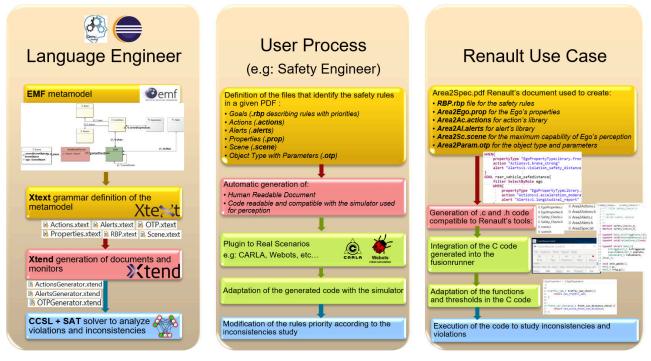

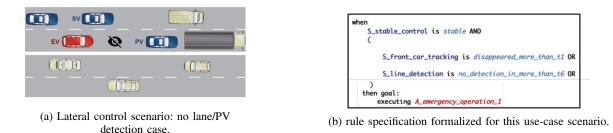

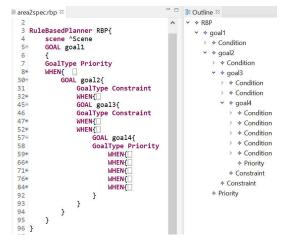

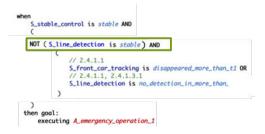

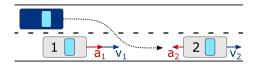

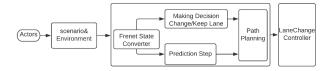

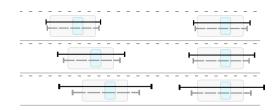

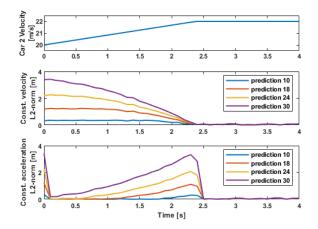

| tional safety in real scenarios                                                                                                                      | 45              |

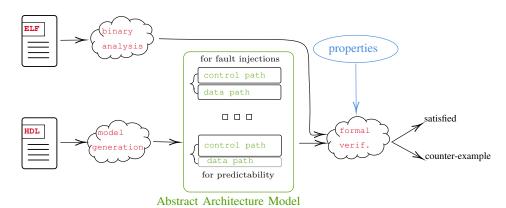

| We.1.C – HW Formal Verification                                                                                                                      | 53              |

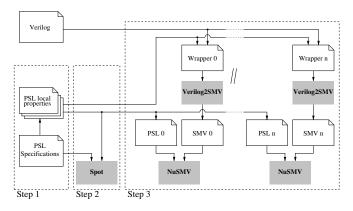

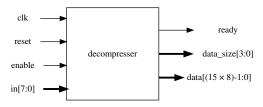

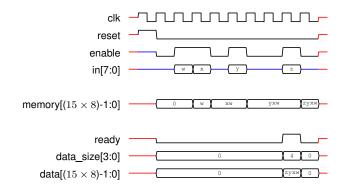

| Formal Hardware Modeling for Analyzing Safety and Security Properties An Automated Framework Towards Widespread Formal Verification of Complex       | 55              |

| Hardware Designs                                                                                                                                     | 65              |

| We.2.PO – Poster overview                                                                                                                            | 77              |

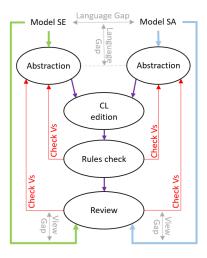

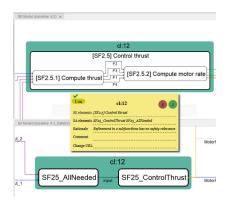

| Structural consistency of MBSE and MBSA models using Consistency Links Experimenting with Dynamic Cache Allocation to Improve Linux Real-Time Be-    | 79              |

| haviour                                                                                                                                              | 85              |

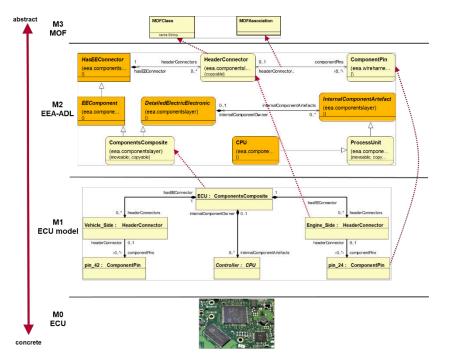

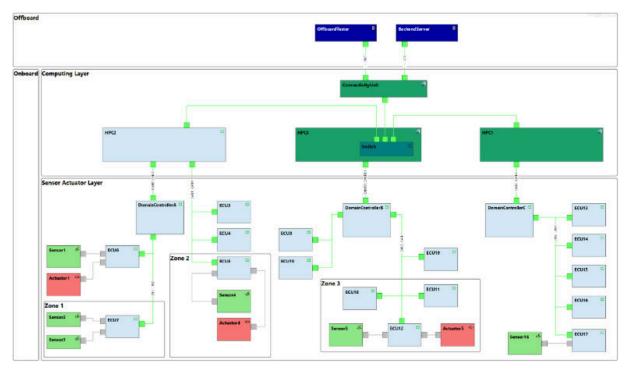

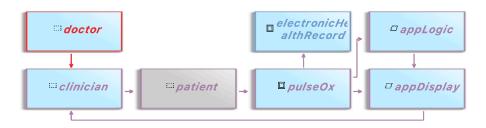

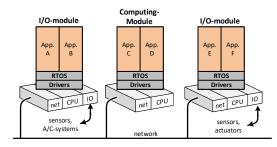

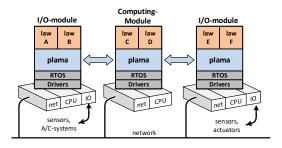

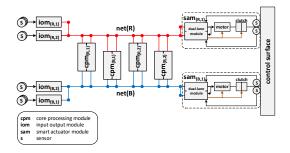

| Model-based design of high-performance computer-based architectures Towards Model-Based Support for STPA as a Capella Add-On                         | 89<br>95        |

| TICORE SCHEDULING ANALYSIS                                                                                                                           | 101             |

| COTS MPSoCs                                                                                                                                          | 107             |

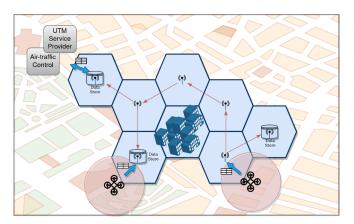

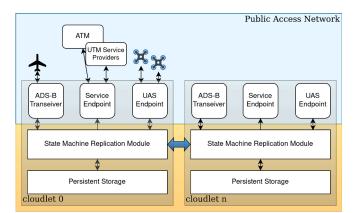

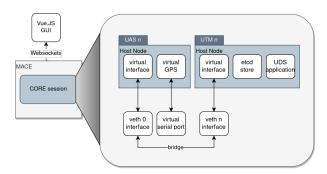

| Airspace                                                                                                                                             | 113             |

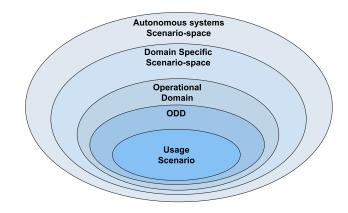

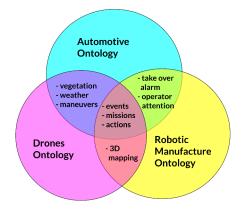

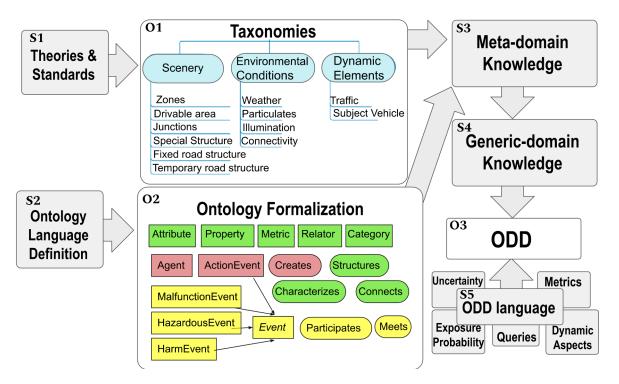

| A cross-domain framework for Operational DesignDomain specification                                                                                  | 119             |

| Towards Real-time Adaptive Approximation                                                                                                             | 123<br>129      |

| We.3.A – Memory Management                                                                                                                           | 133             |

| Dynamic Memory Management in Critical Embedded Software                                                                                              | 135             |

| Certifiable Memory Management System for Safety Critical Partitioned System<br>Whole-System Analysis for Memory Protection and Management            |                 |

| We.3.B | B – Model Driven Engineering II                                                                                                                           | 171          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|        | Automatic Test Generation - An Industrial Feedback                                                                                                        |              |

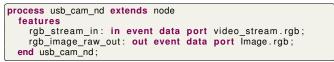

|        | ROS communications profiling for bus load analysis from AADL                                                                                              | 183<br>191   |

| We.3.C | C – Formal Methods                                                                                                                                        | 201          |

|        | Static Data and Control Coupling Analysis                                                                                                                 | 203          |

|        | Automatic Support for Requirements Validation                                                                                                             | 213<br>223   |

|        | work: a Case Study                                                                                                                                        | 223          |

| We.4.A | A – AI:Assurance & Testing I                                                                                                                              | <b>231</b>   |

|        | Programming Neural Networks Inference in a Safety-Critical Simulation-based Frame-                                                                        | -            |

|        | work                                                                                                                                                      | 233          |

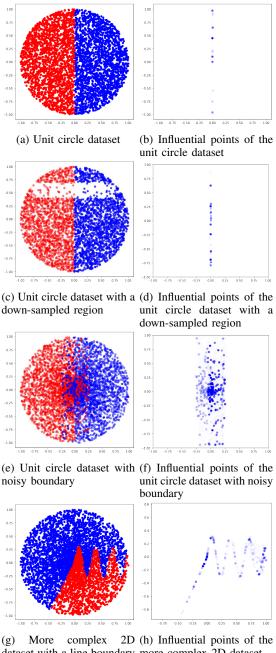

|        | Leveraging Influence Functions for Dataset Exploration and Cleaning Towards the certification of vision based systems: modular architecture for airport   |              |

|        | line detection                                                                                                                                            | 253          |

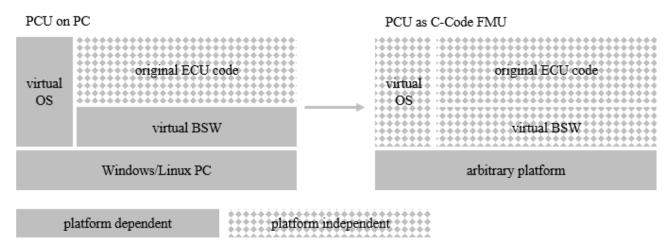

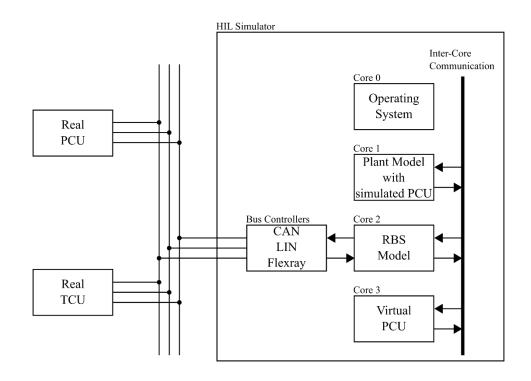

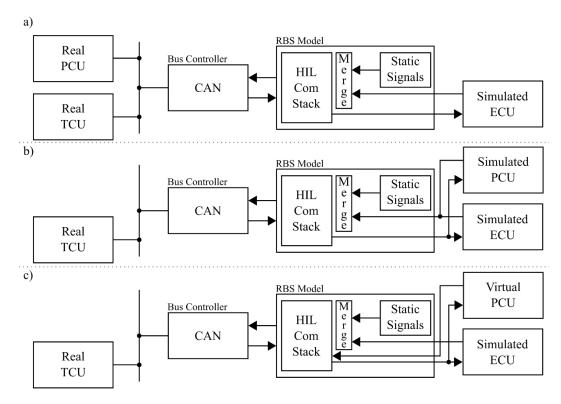

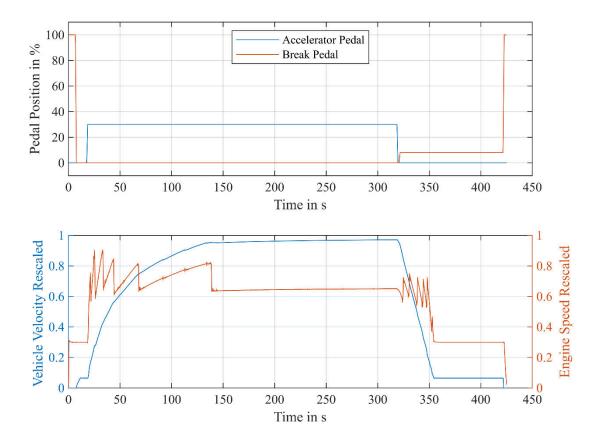

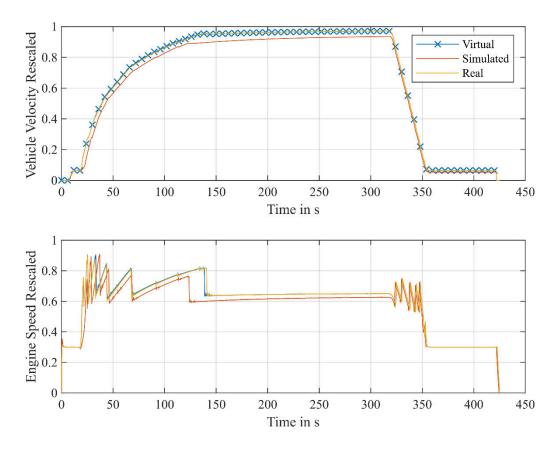

| We.4.B | <b>B</b> – <b>Simulation</b><br>Combining Real and Virtual Electronic Control Units in Hardware in the Loop                                               | 265          |

|        | Applications for Passenger Cars                                                                                                                           | 267          |

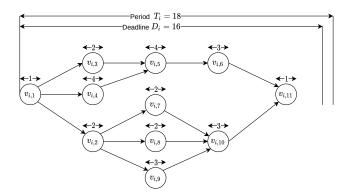

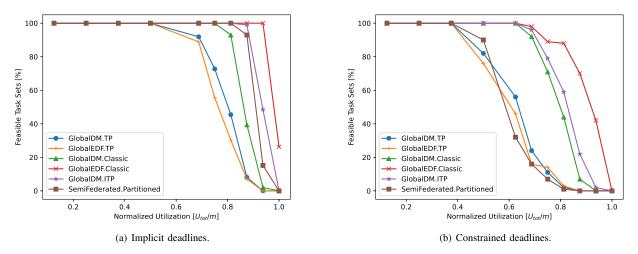

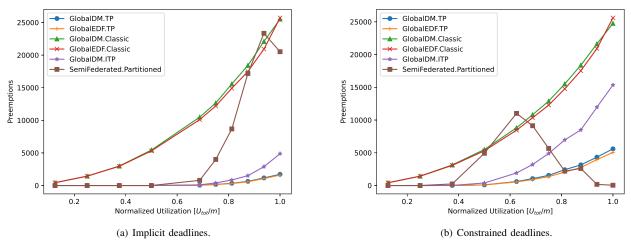

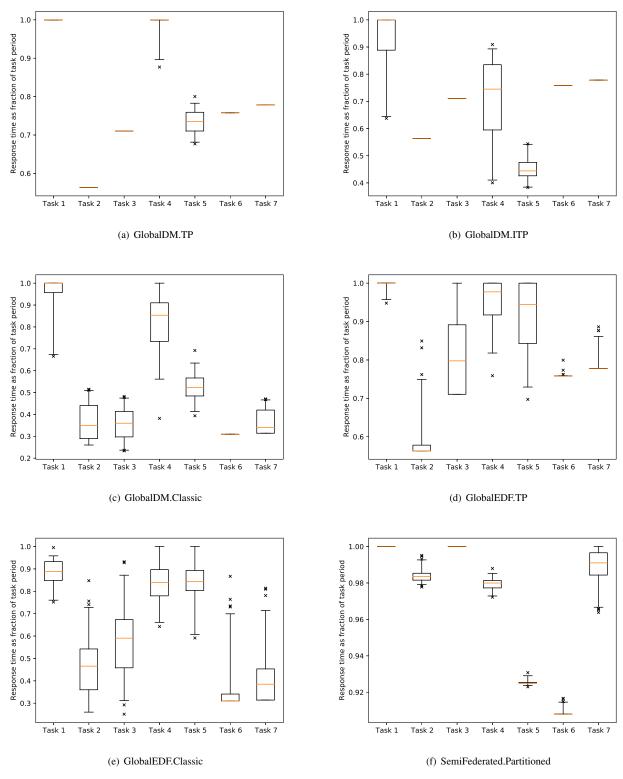

|        | Investigation of Scheduling Algorithms for DAG Tasks through Simulations                                                                                  | 277          |

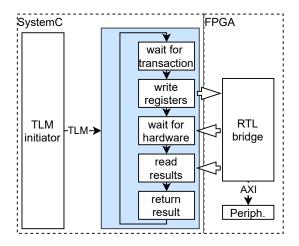

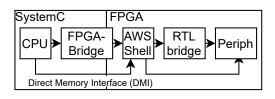

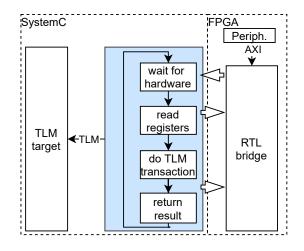

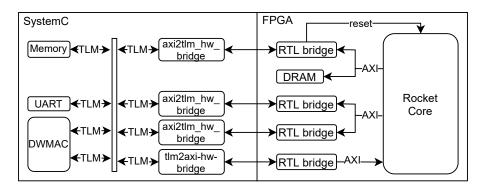

|        | SytHIL: A System Level Hardware-in-the-Loop Framework for FPGA, SystemC                                                                                   |              |

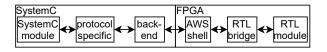

|        | and QEMU-based Virtual Platforms                                                                                                                          | 287          |

| We.4.C | C – Network                                                                                                                                               | 293          |

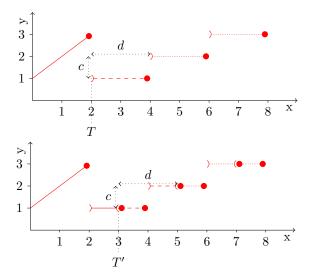

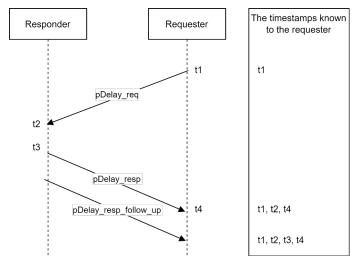

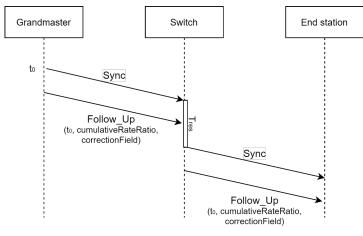

|        | Checking validity of the min-plus operations involved in the analysis of a real-time                                                                      | 005          |

|        | embedded network Assessing a precise gPTP simulator with IEEE802.1AS hardware measurements                                                                | $295 \\ 303$ |

|        | Smart Management of Virtualized Network Service Chains in 5G Infrastructure                                                                               | 313          |

| Th.1.A | – AI: Assurance & Testing II                                                                                                                              | 323          |

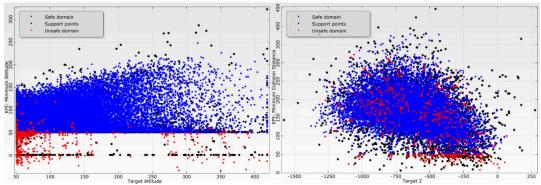

|        | A testing approach for safety-critical Machine Learning systems                                                                                           | 325          |

|        | Can we reconcile safety objectives with machine learning performances? $\ldots$ .                                                                         | 335          |

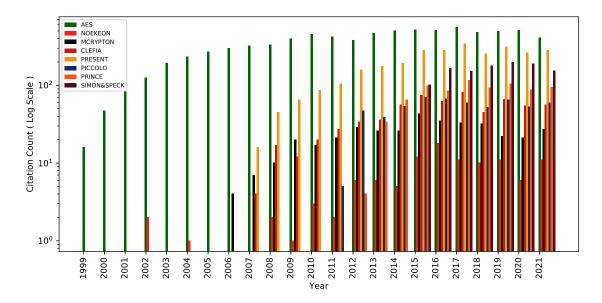

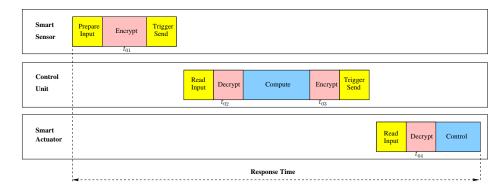

| Th.1.B | - Security                                                                                                                                                | 347          |

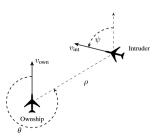

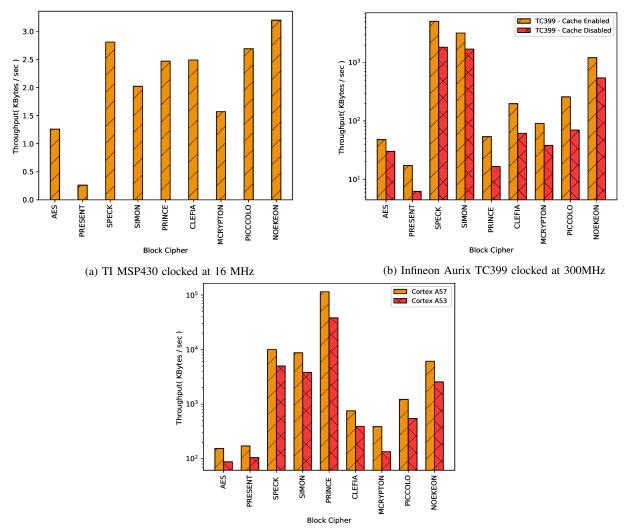

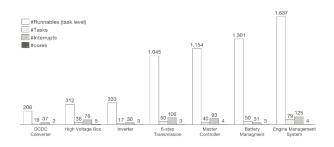

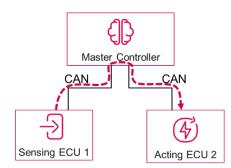

|        | Hijacking an autonomous delivery drone equipped with the ACAS-Xu system Practical Trust x Performance Metrics for Block Cipher Evaluation in Automotive   |              |

|        | Environments                                                                                                                                              | 359          |

|        |                                                                                                                                                           |              |

| Th.1.C | - Logical Execution Time                                                                                                                                  | 369          |

|        | A dynamic reference architecture to achieve planned determinism for automotive applications                                                               | 371          |

|        | The synchronous Logical Execution Time Paradigm                                                                                                           | 383          |

| Th.2.A | – Formal Methods & Certifification                                                                                                                        | 393          |

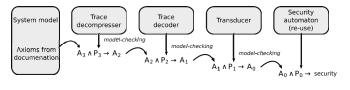

|        | A Bottom-Up Formal Verification Approach for Common Criteria Certification:                                                                               |              |

|        | Application to JavaCard Virtual Machine                                                                                                                   | 395          |

|        | Obtaining DO-178C Certification Credits by Static Program Analysis                                                                                        | 407          |

| Th.2.B | – Assurance By Design                                                                                                                                     | 419          |

|        | Architecture-Supported Audit Processor: Interactive, Query-Driven Assurance Automated Generation of Requirements for the Highly Fault-Tolerant System Be- | 421          |

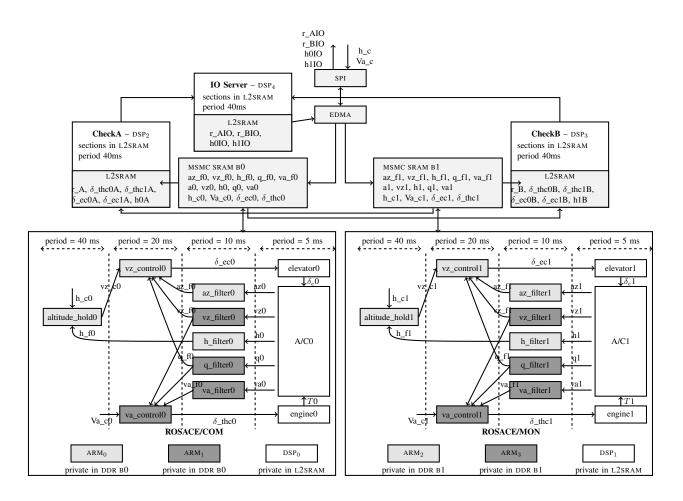

|        | haviour of a Distributed and Integrated Avionics Platform                                                                                                 | 431          |

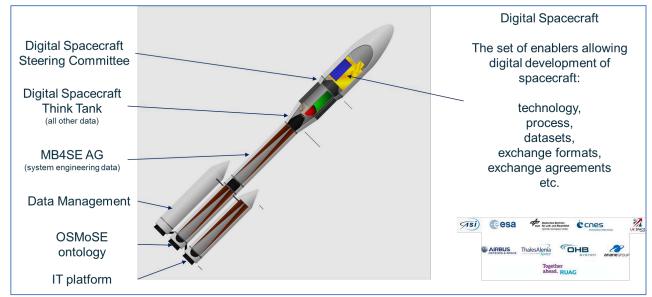

| Th.2.C – Space applications                                                                                                                                            | 441        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

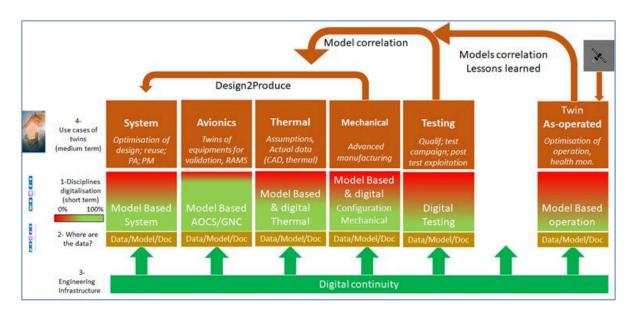

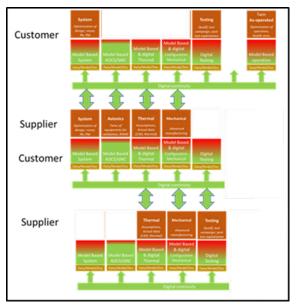

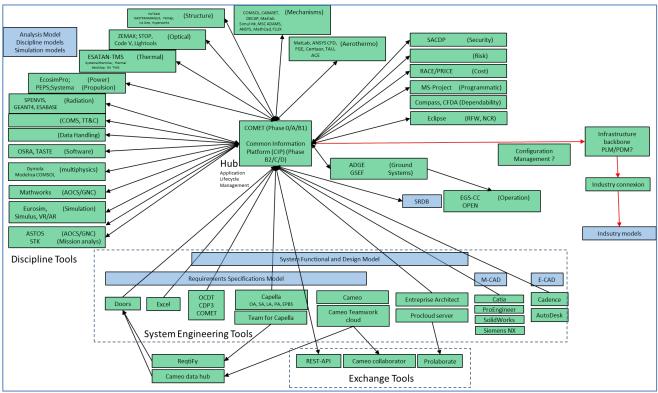

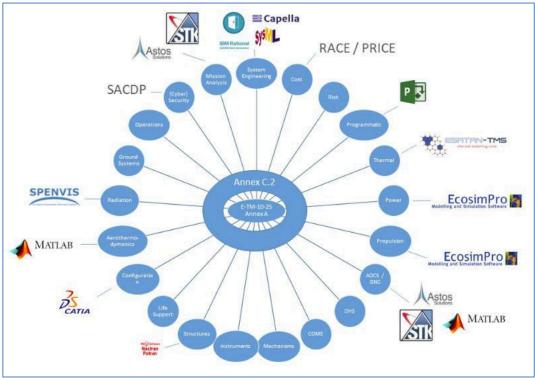

| Digital transformation in the European Space Industry                                                                                                                  |            |

| platform                                                                                                                                                               |            |

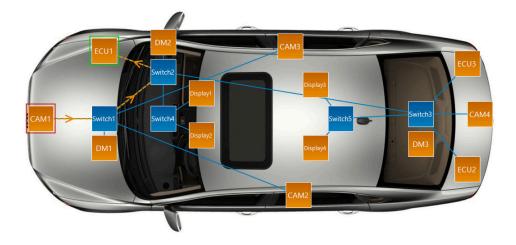

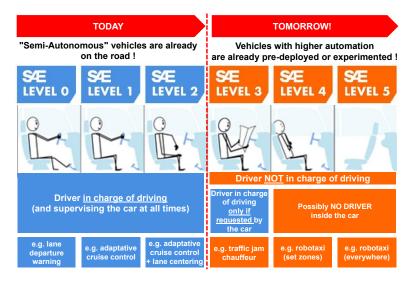

| Th.4.A – Autonomy                                                                                                                                                      | 465        |

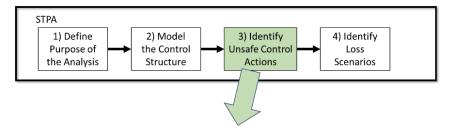

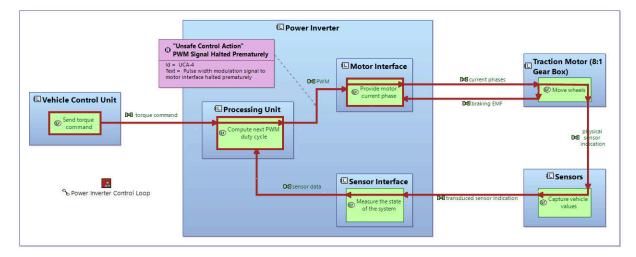

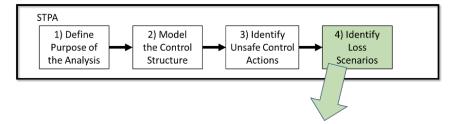

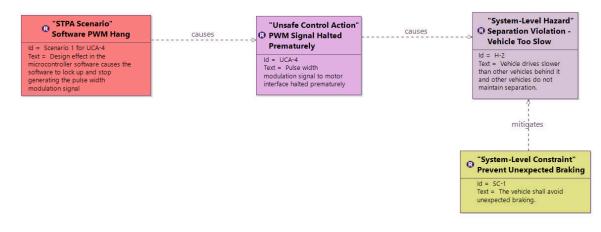

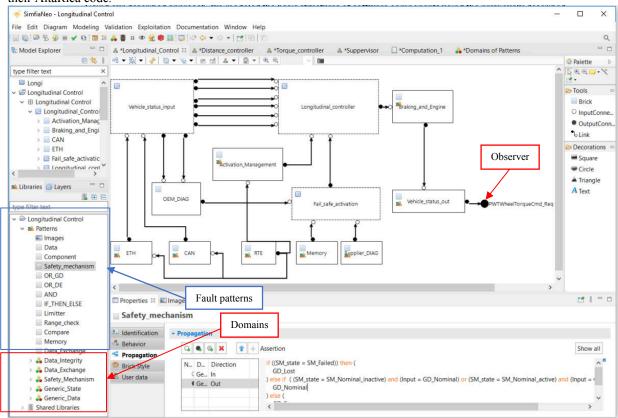

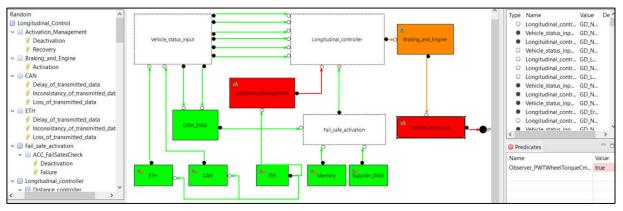

| Efficient Use of Systems Theoretic Process Analysis for Automated Driving System<br>Software fault propagation patterns for model-based safety assessment in autonomou |            |

| cars                                                                                                                                                                   |            |

| Pave the way for connected & autonomous driving at level crossings                                                                                                     | . 489      |

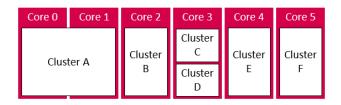

| Th.4.B - Multicore                                                                                                                                                     | 501        |

| MASTECS Multicore Timing Analysis on an Avionics Vehicle Management Comput<br>Using IA to estimate Memory Interference Impact on Avionics Software on Multi-           |            |

| core Platform                                                                                                                                                          |            |

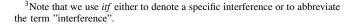

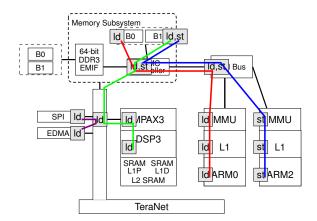

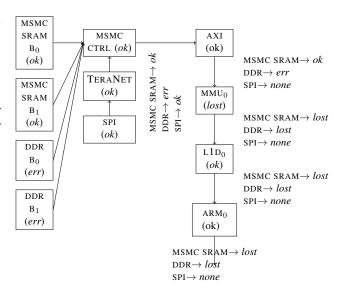

| Modelling and analyzing multi-core COTS processors                                                                                                                     | . 525      |

| Th.4.C – Assurance & Certification                                                                                                                                     | <b>537</b> |

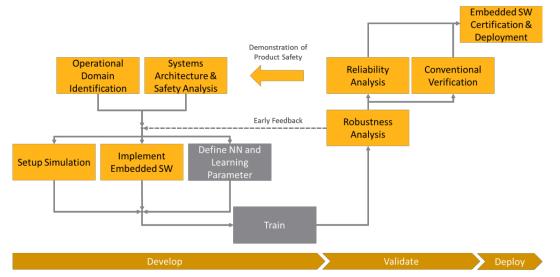

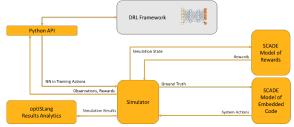

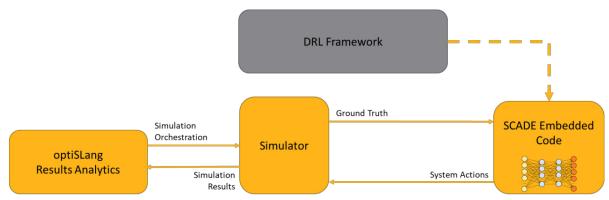

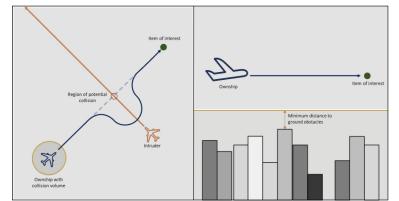

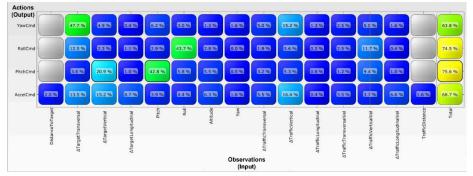

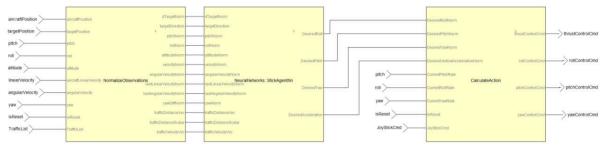

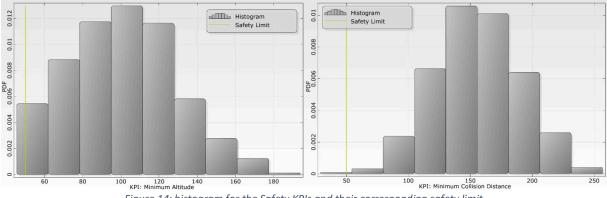

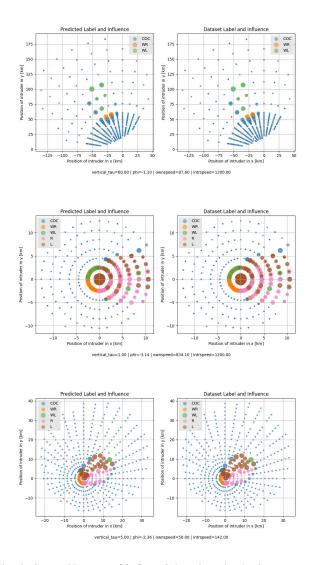

| Toward the certification of safety-related systems using ML techniques: the ACAS-                                                                                      |            |

| Xu experience                                                                                                                                                          |            |

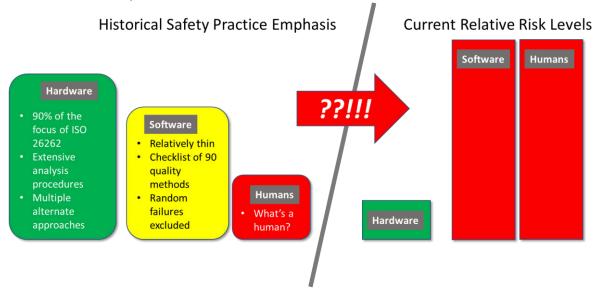

| Do salety standards need radical changes :                                                                                                                             | . 551      |

| Th.5.A - Monitoring                                                                                                                                                    | 561        |

| Multilayer Monitoring for Real-Time Applications                                                                                                                       |            |

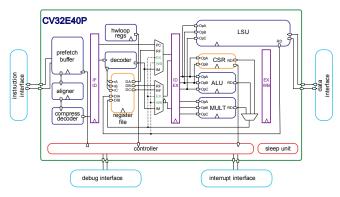

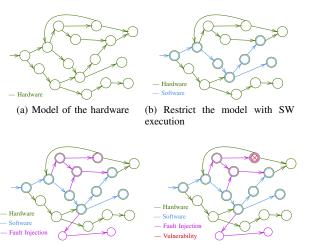

| Safety and Security monitoring convergence at the dawn of Open Hardware $\ldots$                                                                                       | . 571      |

| Th.5.B – Process modelling                                                                                                                                             | 583        |

| Towards an agile, model-based multidisciplinary process to improve operational diagnosis in complex systems                                                            |            |

| Authors index                                                                                                                                                          | 597        |

## **Program Committee**

Ahiad, Samia Ainhauser, Christoph Anguenot, Yves Armengaud, Eric Asselin, Eric Baron, Claude Baufreton, Philippe Belmonte, Fabien Bieder, Corinne Boissé, Sébastien Bover, Marc Braband, Jens Carsten, Thomas Cazorla, Francisco J Chave, Olivier Claraz, Denis Comar, Cyrille Cormery, Patrick Cuenot, Philippe Cunha, Alcino de Roquemaurel, Marie Delmas, Kevin Dreiseitel, Stefan Ducoffe, Mélanie Erts, Admin Faucou, Sebastien Florent, Meurville Frezouls, Benoit Fuerst, Simon Gabriel, Jean-Marc Gallina, Barbara Gauffriau, Adrien Grand, Christophe Guetta, Olivier Guiochet, Jérémie Habli, Ibrahim Hochgeschwender, Nico Jan, Mathieu Jean-Louis, Boulanger

France Germany France Austria France France France France France France France Germany Germany Spain France France France France France Portugal France France Germany France France France France France Germany France Sweden France France France France United Kingdom Luxembourg France

VALEO BMW AG Aerospace Valley Armengaud Innovate GmbH Collins Aerospace LAAS-CNRS, INSA, Toulouse Safran Electronics & Defense Alstom Transport SA ENAC Thales Group ONERA Siemens AG Siemens Barcelona Supercomputing Center TechnicAtome Vitesco Technologies France SAS Adacore ArianeGroup Continental University of Minho Airbus Defence & Space ONERA Continental Teves AG & Co. oHG Airbus NONE Université de Nantes Valeo CNES BMW Group Renault Mälardalen University Airbus ONERA Renault LAAS-CNRS University of York German Aerospace Center (DLR) CEA LIST certifer

France

Jenn, Eric Johnson, Chris Kaaniche, Mohamed Kuehne, Uwe Laarouchi, Youssef Lanusse, Agnes Le Calvez, Gilles Lecomte, Thierry Leconte, Bertrand Ledinot, Emmanuel Lonn, Henrik Mader, Ralph Maillet-Contoz, Laurent Malenfant, Jacques Mamalet, Franck Mangane, Laurent Mekki-Mokhtar, Amina Moreno, Christophe Morgan, Benoît Mouy, Patricia Mraidha, Chokri Nadjm-Tehrani, Simin Nanya, Takashi Navet, Nicolas Niemetz, Michael Pagetti, Claire Palanque, Philippe Parissis, Ioannis Paulitsch, Michael Pfeifer, Holger Picard, Celia Pinot, Frédéric Pons, Philippe Popa, Mircea Povet, Eric Prof. Dr. Mottok, Juergen Quéré, Philippe Rochange, Christine Rodríguez, Rafael Saez, Estelle Shagdar, Oyunchimeg Stea, Giovanni Terraillon, Jean-Loup Totel, Eric Trapp, Mario Traverse, Pascal Troubitsvna, Elena Van Der Linden, Frank Verdier, Damien Vigouroux, David Voget, Stefan Warns, Timo Wartel, Franck Zennou, Sarah

France United Kingdom France Germany France France France France France France Sweden Germany France France France France France France France France France Sweden Japan Luxembourg Germany France France France Germany Germany France France France Romania France Germany France France Spain France France Italy Netherlands France Germany France Sweden Netherlands France France Germany Germany France France

**IRT** Saint Exupéry Queen's University Belfast LAAS Airbus Defence and Space EDF R&D CEA LIST VALEO CLEARSY Airbus Operations SAS THALES Research & Technology Volvo Group Vitesco Technologies GmbH **STMicroelectronics** Sorbonne Université - LIP6 **IRT** Saint Exupery 3AF ANSYS Thales Alenia Space IRIT ANSSI CEA LIST Linköping university The University of Tokyo University of Luxembourg OTH Regensburg ONERA ICS-IRIT, University Toulouse 3 Univ. Grenoble Alpes - Grenoble INP Intel fortiss GmbH ENAC Hitachi rail STS Aerospace Valley Politehnica University of Timisoara Kalrav LaS<sup>3</sup>, OTH Regensburg Stellantis IRIT - Université de Toulouse GTD Sistemas de Información, S.A. LIEBHERR VEDECOM University of Pisa European Space Agency Supelec Fraunhofer AIRBUS KTH Philips Healthcare Vitesco Technologies France SAS **IRT** Saint-Exupery Continental Automotive GmbH Airbus AIRBUS Defence and Space Airbus

# Session We.1.A

# GPU

Wednesday 1st June 11:30 – Amphithéâtre

### Real-time high performance computing using a Jetson Xavier AGX

Cyril Cetre<sup>1, 2</sup>, Florian Ferreira<sup>2</sup>, Arnaud Sevin<sup>2</sup>, Rémi Barrere<sup>1</sup> and Damien Gratadour<sup>2, 3</sup>

<sup>1</sup>Thales Research & Technology

<sup>2</sup>LESIA, Observatoire de Paris, Université PSL, CNRS, Sorbonne Université, Université de Paris, 5 place Jules Janssen, 92195 Meudon, France

<sup>3</sup>RSAA, Australian National University, Cotter Road, Weston, ACT2600, Australia

#### Abstract

While general purpose graphics processing units now embark tremendous amount of computing power, their use in real time applications is still a challenge. The COSMIC platform, developed in the context of adaptive optics control for giant astronomical telescopes is a demonstrated solution to perform real time computations using discrete GPUs while maintaining a high level of abstraction and modularity. An implementation on embedded platforms with the goal to reach an acceptable level of time-determinism would enable new real-time use cases in other application domains. In this regard, NVIDIA is offering a broad range of embedded systems on chip delivering great performance and compatible with the CUDA ecosystem. However, specific hardware and software features bring uncertainties regarding real-time performance. The approaches presented in this paper rely on COSMIC recipes to expose part of the underlying unconventional GPU programming model to reach real-time performance. It shows how Jetson Xavier performs on sub-millisecond complex pipelines made of several compute kernels, considering the limitations engendered by missing CUDA features as compared to discrete devices, leveraging unified memory to work around these hurdles and enabling several strategies for implementing real-time workflows on embedded GPU platforms.

Keywords: Real-time systems, graphics processing units, High Performance computing, embedded software, CUDA

#### Introduction

#### Real-time computing for adaptive optics

Adaptive Optics (AO) systems are used to compensate aberrations in real-time on optical systems. They are a core component of extremely large telescopes for astronomy. They aim at making partial compensation of image distortions induced by atmospheric turbulence in real-time using a set of computer controlled actuators, under the reflective surface of so-called deformable mirrors, to observe astronomical objects at high angular resolution and high contrast. As distortions and external constraints on AO are fluctuating on very short time scales, AO controllers, working in closed loop, need to infere the best actuators commands with minimum and stable time-to-solution (in the range of 1 ms or less). In addition, the complexity of AO systems exacerbates the need for a modular solution which provides the ability to realize flexible computing pipelines.

The COSMIC [1] platform was designed to cover the requirements of a wide variety of AO instruments considering these constraints. This platform relies on off-the-shelf high performance libraries and a modular approach, in order to minimize implementation cost and complexity while maximizing performance and throughput of applications requiring efficient GPU computations. It provides abstraction layers handling data transfers, inter-process communications and synchronisations between computation units of a given pipeline. Each computation of the pipeline is turned into an independent process, allowing individual monitoring and real-time pipeline modifications. The multi-process mechanisms are thoroughly optimized to obtain the best possible performance given the hardware configuration.

While COSMIC was originally designed for AO, its application to other domains remains perfectly valid as it is aiming at providing a framework for real-time computation regardless the pipeline. Therefore, evaluating the use of its programming methods on embedded platforms is meaningful, although opening the door to new challenges. An embedded implementation will have to ensure that performance is preserved with scarce resources while proposing possible solutions to overcome technical limitations. A stable implementation on systems on chip (SoC) could prove useful to implement simpler pipelines with specific use cases such as smart cameras working as wavefront sensors.

#### Embedded systems and real-time computing

With the exponential growth of the use of deep learning in various domains, SoC with integrated GPU (iGPU) are becoming very popular thanks to their rather high performance per watt. In particular, NVIDIA provides a broad range of consumer products using custom ARM CPU and iGPU. These SoC have many interesting features such as supporting the CUDA ecosystem. This makes cross-platform programming pretty straightforward with few differences between SoC and discrete GPUs (dGPU) [2]. As opposed to a dGPU, which is a separate device from the processor with dedicated memory, one of the main features of iGPU is to share memory with the CPU, which allows to reduce

#### 2 ERTS 2022

the need for data transfers, although it opens the doors to a number of challenges as well considering the CPU activity may interfere negatively with the GPU computations.

In any case, achieving real-time GPU computing can be challenging since this technology offers very few safeguards on execution time determinism. That is why average jitter and Maximum Measured Execution Time (MMET) must be assessed carefully. Ensuring such features, combined with a high throughput is a significant hurdle to overcome before bringing GPU into time critical applications.

In addition, enabling workflows involving multiple processes on a GPU brings uncertainties regarding the end-toend response time. Some functionalities like CUDA Multi Process Service (MPS) are offered to allow kernels from different processes to execute concurrently. However, MPS and some other features are not available on embedded NVIDIA SoC, making multi-process application portability unpredictable on such platforms.

#### Unconventional programming model for GPU

Ensuring time-to-solution repeatability with very low jitter for a complex pipeline can be particularly tough when relying on multi-process asynchronous GPU computations. While achieving a high throughput is possible when taking into account intrinsic overheads of GPU computing, such as memory transfers, kernel launches or synchronizations between the host and the device, reaching low performance jitter usually requires unconventional programming approaches, such as using persistent kernels [3] [4]. As the name implies, these kernels are not terminated between each iteration and just wait on the arrival of more data to be triggered again. However, such technique heavily depends on hardware features and the CUDA grid/block dimensioning must be handled within the kernel. As a consequence, persistent kernels must be redesigned when either the pipeline or the targeted hardware changes. A proposed trade-off between persistent kernels and traditional programming models is the use of a combination of GPU busy wait kernels and look ahead jobs scheduling, relying on the GPU scheduler to launch new kernels while avoiding CPU/GPU synchronization overheads [1].

This paper exposes this approach through a set of out-ofthe box use cases, comparing the discrete and embedded behaviour in order to provide guidance about how to perform real-time multi-process computations with complex applications in an embedded environment.

#### Focus of this paper

This paper relies on previous work done with the COSMIC platform and extends the best practices implemented therein to provide a suitable solution for critical real-time applications running on embedded platforms in terms of average jitter, worst observed execution time and throughput.

Porting these recipes on Jetson Xavier AGX provides an overview of how architectural and software differences between embedded platforms and integrated GPUs can be worked around to achieve real-time performance. We highlight these differences and show why it could be a serious impediment to determinism. We also propose workarounds using multi-thread or multi-process implementations of GPU inter-process communication through busywaiting.

Finally, we evaluate through benchmarking the performance and overall behaviour obtained using different methods for efficient inter-process communication

#### **Related Work**

Using GPUs for real-time applications is not straightforward, as it has not necessarily been designed to minimise MMET, although modern GPUs are slowly overcoming technological limitations with increased features and capabilities. [5, 6].

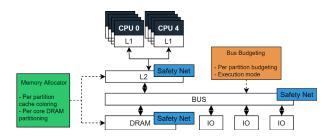

Unlike dGPUs, the CPU and the iGPU share the same SoC DRAM on Tegra devices. As a consequence, CPU activity may interfere negatively with GPU computation and conversely [7]. That is why some authors have proposed to improve determinism by protecting GPU applications from memory throttling through custom schedulers [8, 9]. In addition, several studies are aiming to unveil closed-source details of GPU schedulers to get a better understanding of their behaviour. [10, 11].

On a positive note, shared DRAM implies that data transfers from host to device are avoidable. In such circumstances, pinned host memory accessed from GPU will not have copy overheads and will be bounded by the same bandwidth as memory allocated from device code. Combined with CPU shared memory, it is used in this contribution as a workaround to bypass the lack of CUDA Inter-Process Communication (IPC) features. In addition, previous work has shown that using pinned host memory on embedded systems can be a way to increase determinism by reducing memory requirements of GPU programs [12].

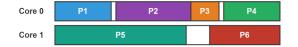

#### Real-time multi-process computing on GPU

Inherited from a project having strong requirements for scalability, maintainability and modularity [3], COSMIC was designed as a framework able to overcome the underlying limitations by supporting separate kernels that can run either concurrently or sequentially, with an efficient synchronization mechanism. However, a complex software architecture does not necessarily scale well when GPU computations are involved depending on the exact setting.

For instance, the default behaviour of CUDA is not suited for real-time multi-process applications. As every process has its own CUDA context only one context can run at the same time on the GPU, the device has to switch constantly between them, leading to extra jitter. In addition, running kernels with a small number of threads will lead to poor GPU performance as another kernel could have run concurrently. For a single process (and single context) application, the CUDA streams were created to overcome this issue and enable the overlapping of kernels executions.

In the case of multi-process applications, NVIDIA has made various tools available to improve the device management. In this regard, the next sub-section offers an overview of these CUDA features providing a good understanding of their implication and why they are critical for real-time.

#### CUDA MultiProcess Service (MPS)

CUDA MPS is a binary-compatible client-server runtime implementation of the CUDA API. MPS is especially useful when multiple processes are making use of the GPU, in particular when these processes underutilize GPU resources. Its main benefits are the following :

- Kernels and memcopy operations from different processes may overlap on the GPU.

- MPS handles only one GPU context and set of scheduling resources between its clients instead of one context for each process. This removes the need for context switching between two GPU kernels.

#### **CUDA Interprocess Communication**

Part of the CUDA Toolkit and available since compute capability 2.0, CUDA IPC enables sharing device buffers between multiple processes. While the COSMIC memory manager implementation relies on CUDA IPC to share device buffer between processes, these calls are not supported on Tegra device.

#### GPU busy wait synchronization

At some point, a process will have to wait for another to complete, thus needing to synchronize. Previous work on the COSMIC framework provided an assessment on which kind of synchronization gives the best response time in order to maximize performance [1]. From this study, it appears that busy wait synchronization (meaning different processes actively wait for data to be written on the GPU through memory polling) shows a significant latency improvement compared to a regular CPU based POSIX semaphore synchronization. It has several benefits :

- The pipeline processing is now fully asynchronous from the CPU, allowing the user to hide kernel launch latency by accumulating jobs on the GPU scheduler in advance.

- A CPU, even isolated is still more likely to get non preemptible interruption request from the OS kernel compared to a GPU which is dedicated to computations.

On the other hand, each busy wait process is using a GPU streaming multiprocessor to spin on a given location in memory which is increasing system occupancy and resource consumption.

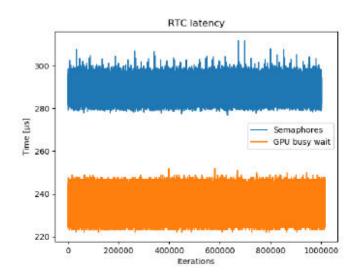

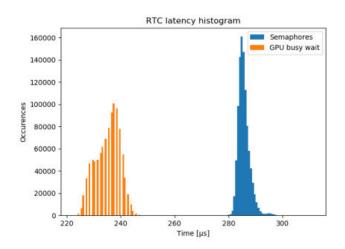

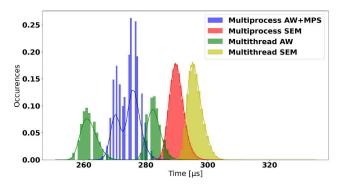

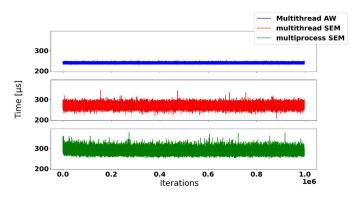

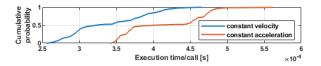

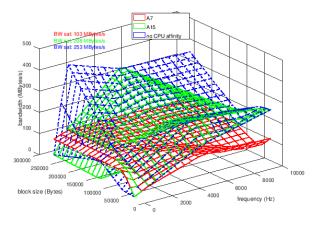

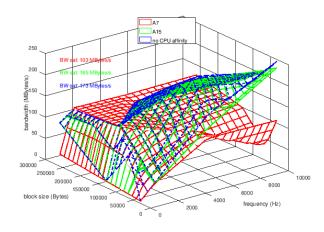

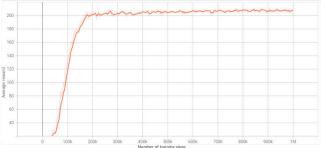

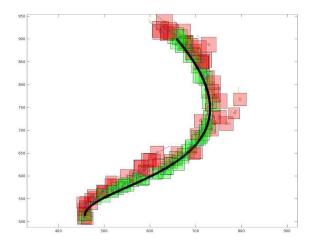

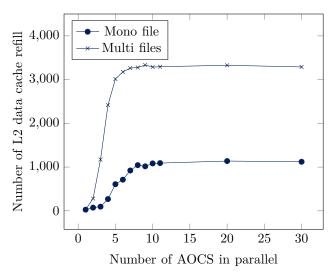

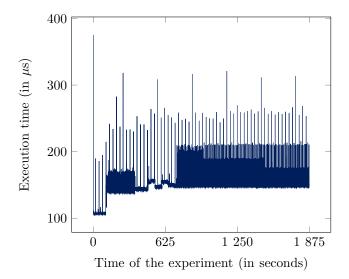

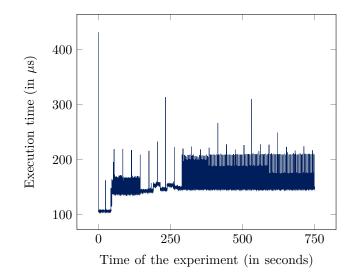

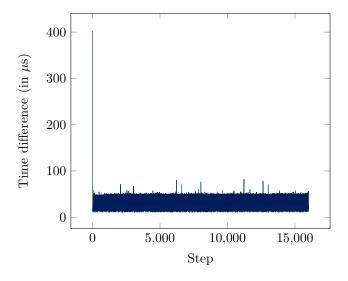

Figure 1 and 2 shows how busy waiting with CUDA MPS enabled performs compared to POSIX semaphore implementation, revealing non negligible latency improvement on a NVIDIA DGX server (286  $\mu$ s of average execution time for semaphore and 235  $\mu$  s for GPU Busy wait). Even though the semaphore synchronization shows a better average jitter (2.1  $\mu$ s for semaphore and 4.4  $\mu$ s for GPU busy wait), this synchronization process is more prone to jitter peaks (semaphore : 35  $\mu$ s of peak to valley and 30  $\mu$ s for GPU busy wait). In addition, the NVIDIA DGX server performs especially well to minimize this kind of interference, which tends

**Figure 1** Time-to-solution execution profiles obtained with COSMIC in the context of the AO application, using 2 different synchronization mechanisms over 1M iterations [1]

**Figure 2** Time-to-solution histogram obtained with COS-MIC in the context of the AO application, using 2 different synchronization mechanisms over 1M iterations [1]

to show higher peak to valley in the case of semaphore synchronization as compared to other GPU equipped servers. As a consequence, the GPU busy wait is preferable both in terms of latency and jitter stability.

Considering the sub-millisecond response time requirement, such gains represents a great asset and are hardly dispensable. Reproducing such results on an embedded SoC would bring us closer to hard real-time embedded GPU computing, although the road ahead is full of obstacles.

#### The challenge of embedded GPU computing

As GPUs are growing in complexity with features including dedicated cores for specific operations including tensor

#### 4 ERTS 2022

cores for matrix multiplication or RT cores for raytracing, NVIDIA is regularly proposing new SoCs featuring the latest innovations. As a consequence, each SoC has a specific hardware architecture (CPU and GPU) which makes it difficult to predict performance on the targeted board without comprehensive testing. That is why this paper will focus on NVIDIA Jetson Xavier AGX, which is providing some features (for instance I/O coherency) which were not available on previous NVIDIA boards.

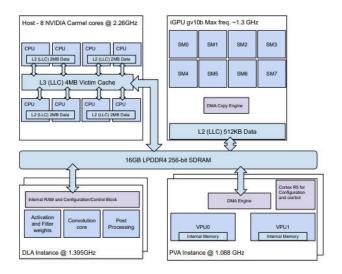

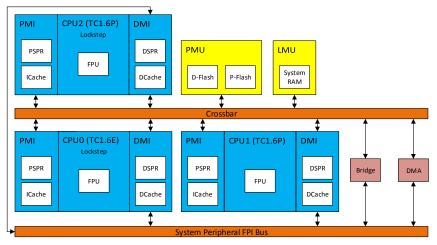

#### The Jetson Xavier AGX

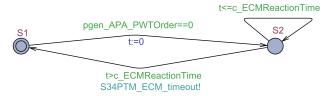

Released in 2018, the Jetson Xavier AGX is currently the most powerful embedded GPU platform available on the market. It is featuring within its Xavier Tegra SoC a Volta GPU with 512 CUDA cores and 8 streaming multiprocessors.

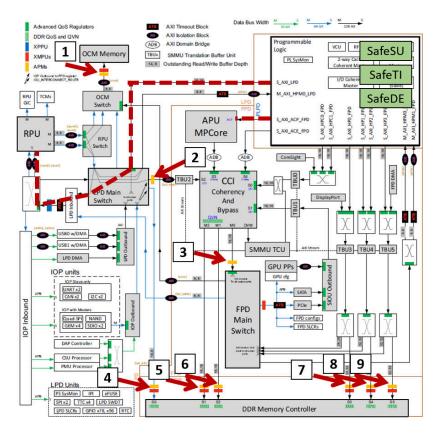

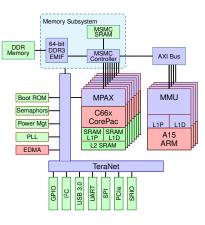

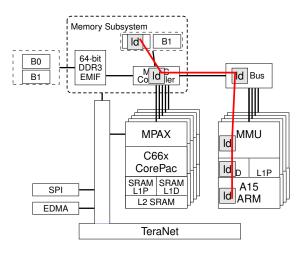

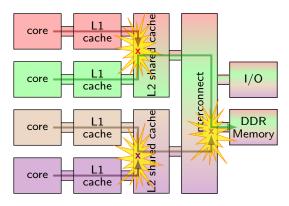

Figure 3 Block diagram of Jetson Xavier complex (credits : [13]

The CPU is composed of 8 ARM 8.2 architecture compliant cores. Regarding the cache hierarchy, it is important to notice that the CPU complex is composed of 4 islands. Although each core has its own private L1 cache, the CPU L2 cache is shared between two threads. Two cores from the same island will interfere if both are executing highly bandwidth dependant tasks. As a consequence, the combined bandwidth of two CPUs of the same island is worse compared to a single core doing heavy bandwidth computations paired with an idle one. [13].

This is why it is recommended to always isolate CPUs by island to avoid extra interference from shared L2 cache on this platform.

Unlike discrete GPU (dGPU), CPU and integrated GPU (iGPU) share 16GB of DRAM clocked at most at 2133 MHz, reaching a theoretical bandwidth of 137 GB/s.

#### Shared CPU/GPU memory

From a software point of view, shared memory does not mean that a CPU pointer is accessible from GPU and conversely. Depending on how memory is allocated, the cache behaviour differs and memory might not be accessible from both the host and the device. Similarly to dGPU, memory allocated with cudaMalloc is not accessible from the host and a buffer allocated with cudaMallocManaged will return a buffer accessible from both sides. The main difference with dGPU is that there is no hidden memory copies between the host and the device and the source code should be adapted to make copies only when unavoidable. NVIDIA provides detailed documentation about the cache behaviour depending on how the memory was allocated [2]. Starting with the Xavier architecture, Tegra boards are featuring I/O Coherency which allow I/O devices such as the GPU to read the latest updates in CPU caches. This is beneficial in our case as it allows to cache CPU pinned host memory and to register an existing host memory range for use by CUDA, which is crucial in our proposal to bypass the lack of CUDA IPC.

#### CUDA IPC/MPS unavailable on Jetson

At the time this paper was written, aforementioned multiprocess features are not available on NVIDIA embedded systems. As a consequence, multi-process GPU busy waiting is not viable as it is introducing strong jitter interference due to GPU context switching. We will see in the next sections various options we explored to get performance similar to the classical multi-process approach, followed by experimental results.

#### Multi-process real-time computing on Jetson embedded platforms

#### GPU buffer sharing on Jetson Xavier

When trying to reproduce complex GPU pipelines on Jetson, the first obstacle lies in being able to share GPU buffers among processes which is usually done on a discrete device through CUDA IPC. So far, this feature is not available on Tegra SoC although sharing device memory is a core feature of the platform.

Fortunately, on Tegra devices with I/O coherency [2] (starting with the Jetson Xavier, not applicable on previous devices) it is possible to register an existing host memory range for use by CUDA. The identified workaround takes advantage of the CPU and GPU unified memory to keep decent performance while using a mix of POSIX shared memory and zero-copy mechanism which allows a GPU to fetch pinned host data.

Using GPU kernels to access pinned host memory is coming with drawbacks. First, it will result in separated pointers for host and device calls, although using the same memory space. Second, pinned host memory accessed by the GPU will not be cached. As a consequence, user must take extra care when accessing memory to avoid any performance drop.

#### GPU busy-waiting efficiency on Jetson Xavier

Although the aforementioned shared GPU buffers enables GPU busy wait synchronization, results showed really poor performance using a straightforward implementation. Recording sub-milliseconds computations through a nonintrusive timer (meaning that it is using a separate process in order to avoid interference with the main pipeline) requires responsive measurements.

Unfortunately, measuring those events on GPU turns out impossible as the GPU timer is unable to start and stop at the right moment while performing sub-millisecond measurements. Considering that this timer has its own process and CUDA context, the GPU scheduler will not necessarily give the hand back to the timer process right after the computation process sends the stopping signal, thus providing misleading results.

Although CUDA preemption mechanism and context loading are not publicly disclosed, we know that the GPU is handling multiple clients (i.e., multiple processes requesting GPU resources) with a time-slicing behaviour. In addition, a GPU always serialise two kernels from different processes, even though the resources to run them in parallel are available.

As a consequence, the scheduler regularly interrupts the pipeline computations to perform GPU busy waiting from other computing units, leading to unintended performance and jitter degradation. Considering that multi-process busywait synchronization relies heavily on launching small kernels from different processes, it is impossible to achieve a satisfactory level of determinism in highly constrained environments using regular busy-waiting without CUDA MPS.

#### Possible workarounds

Thanks to unified memory, potential workarounds are available although they don't completely overcome the lack of CUDA MPS.

#### Multiple-context CPU active-wait strategy

It is possible to keep going with multiple CUDA contexts. In this case, the important aspect is to avoid doing active waits on GPU at all costs as explained in the previous subsection. Active waiting with CPU on a GPU data buffer is working, although forcing CPU thread spinning. This avoids a synchronization between the host and the GPU as notifications are sent through the device. However, the GPU won't be able to schedule kernels ahead of time as the CPU is now blocking the execution. Adding context switching, this strategy will introduce some overhead compared to straightforward GPU busy-wait.

#### Semaphore strategy

While having an overhead compared to active wait strategy, implementing POSIX semaphore based signals remains perfectly viable and will suffice in most cases.

#### Multi-thread strategy for real-time computing

After establishing that the principal constraint is to keep only one CUDA context to get best results when using the GPU busy waiting technique, it seems that an approach relying on both multi-thread and multiple streams is an approach to consider. CUDA streams were specifically designed to allow concurrency on a single process, which is a requirement for this kind of busy-wait.

On the positive side, a multi-threaded implementation removes software dependency to inter-process features (CUDA MPS and CUDA IPC). As a consequence, it is deployable on both discrete and integrated GPU environments as opposed to the multi-process approach.

However, it must be pointed out that the GPU behaviour is not strictly identical. For instance, considering the GPU busy-wait mechanism, it is very important to synchronize the CPU with the CUDA execution at some point. A CUDA context has a limited queue depth in terms of kernel scheduling. When this limit is reached, a forced synchronization occurs on the CPU before it can be able to enqueue more kernels. It is thus very easy to end up with a deadlock, with busy wait kernels exceeding the queue depth leading to the impossibility to send notifications. This limitation must be taken into account by the implementation.

The described behaviour may not be the only difference between multi-thread and multi-process strategies. Unfortunately, as for the multi-process preempting behaviour, CUDA stream scheduling is scarcely documented by NVIDIA although several studies are working toward exposing it in more details [14]. Thus, it is likely that new behaviour specificities will be empirically discovered in the future.

Regarding performance, results with a multi-thread implementation appeared to be very similar to regular MPS multi-processing, which is encouraging.

#### **Environment setup and results**

#### Use Case

For the sake of reproducibility and modularity, the decision was taken to implement a simplified pipeline while keeping only COSMIC core synchronization mechanisms. It allows us to propose multiple test cases, with both embedded and iGPUs whenever necessary.

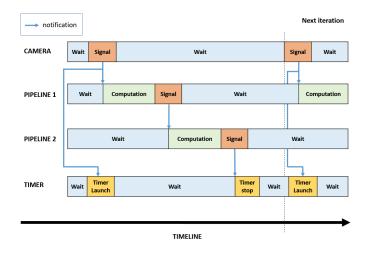

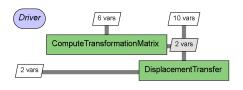

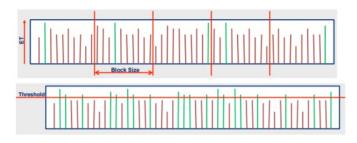

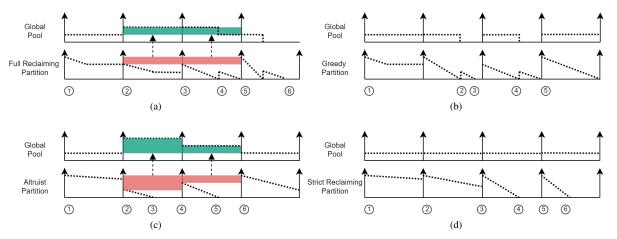

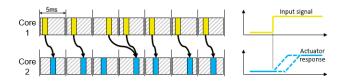

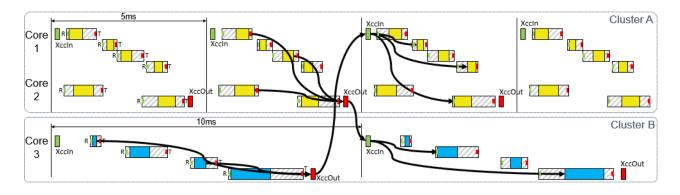

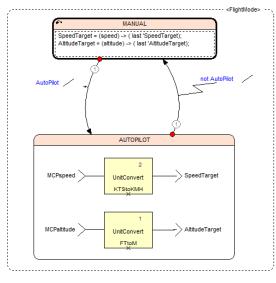

Figure 4 shows an example of how a given sample test behaves regardless of the synchronization approach and its kind of parallelization, being either multi-threaded or multi-processed. The basic architecture of the pipeline is the following :

- A camera emulator which sends notifications at a given framerate. The notification to start computation is sent to both the timer and the first computation unit.

- A pipeline that can be composed of one or more compute units. In our test environment, it essentially performs matrix vector multiplications (MVM). It sends a notification to the timer once it is done.

- A timer which gets notifications from the camera emulator to start and from the last computation unit to stop.

Each test is performed first in a multi-processed environment, meaning each unit (timer, camera, first MVM, second MVM and so on) are launched as separated processes. The

Figure 4 Timeline of a test with two computing units

only way these units have to communicate is through shared memory and signals to synchronize, which is done either through POSIX semaphores or GPU busy-wait. In a second experiment, the test is performed with the multi-threaded approach : the computation units are launched in the same process. However, each unit is given a distinct CUDA stream which allows kernel execution overlapping. Both synchronization methods are performed as well.

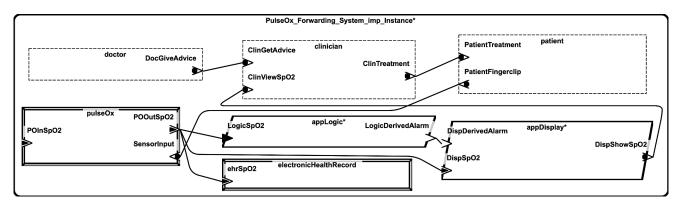

#### WCET and MMET

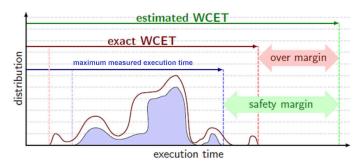

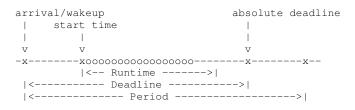

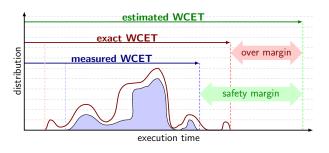

The Worst Case Execution Time is a term typically used in critical real-time systems where reliability and safety is paramount. As of today, it is very unlikely that an embedded environment such as a Jetson can allow a demonstrated WCET such as it is meant in avionics. In order to avoid misconception about the testing process, this paper is addressing Maximum Measured Execution Time (MMET), meaning the worst case measured in the test session with a representative number of executions (1 million). Figure 5 shows how MMET does not necessarily shows the worse possible case, compared to the WCET.

**Figure 5** This paper uses maximum measured execution time (MMET) figure credit : Thales Research Technology

#### **Timing measurement**

Timing events with asynchronous CPU and GPU interactions can be surprisingly difficult. In order to record overheads

between a computation unit sending a signal and another receiving it, the timer must stay in a separate thread. It is also a great asset as a timer needs to synchronize with CPU and GPU in order to get execution time, which is unavoidably introducing overhead. This kind of timer needs the first pipeline unit to send a notification to launch measurement and the last one to send a another one to stop it. The downside is that the timer is not bounded to computation anymore and might miss some iterations at some point if is not awaiting for a signal when a notification is sent.

Making the timer independent of computation units will not introduce interference to computation or forcing unintended CPU/GPU synchronization, ensuring measurement closest to the actual computation time.

The semaphore synchronization approach is measured through the C++ high\_resolution\_clock API while the GPU busy wait approach is using CUDA events.

Results will be shown through two different displays that highlights different kind of information :

- Histograms are helpful to get a grasp of an approach latency and jitter.

- Execution profiles include each iteration execution time. It is useful to show how an approach is affected by jitter. The wider the plot "line", the more jitter this approach gets. it also shows infrequent outliers, that would not appear on histograms.

#### Environment

Table 1 and 2 show both configuration used in the following tests.

| OS           | CentOS 8                                        |

|--------------|-------------------------------------------------|

| Linux kernel | 4.18.0-193.19.1.el8 2.x86 64                    |

| СРИ          | 15 Intel(R) Xeon(R) CPU E5-2698 v4 @<br>2.20GHz |

| CUDA version | 11.5                                            |

| GPU          | Tesla V100                                      |

Table 1 Benchmark environment setup with dGPU

| OS           | Ubuntu 18.04                  |  |

|--------------|-------------------------------|--|

| Linux kernel | 4.9.253-rt168-tegra           |  |

| CPU          | 8-core ARM v8.2 64-bit        |  |

| CUDA version | 10.2                          |  |

| GPU          | 512-core Volta integrated GPU |  |

**Table 2** Benchmark environment setup on Jetson Xavier

AGX

#### **Optimizations for real-time**

Several optimisations are done to achieve real-time performance. This includes :

- CPU isolation at boot.

- Processes scheduling set to FIFO with high priority.

- Running CUDA MPS server (for dGPU only).

In order to get comparable results across all experiments for a given setup (dGPU or Jetson), MVM are based on a fixed size. The framerate of the camera is set to always let the pipeline finish its job before notifying for the arrival of a new image.

To reach sub-millisecond computation time with both settings, the matrix size is reduced with the Jetson Xavier, giving the following sizes :

- 4096 X 12500 with the Tesla V100.

- 4096 x 1562 with the jetson Xavier.

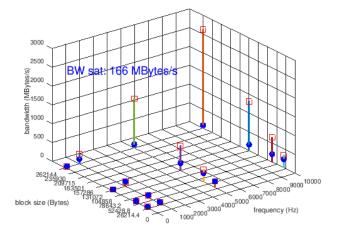

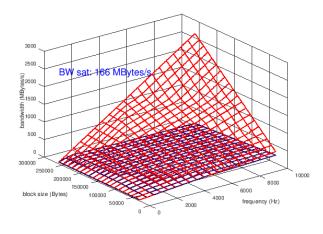

#### Experimental results with the Tesla V100

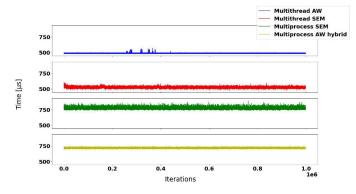

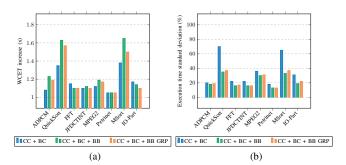

The first step requires to study how different implementations behave with dGPUs compared to known results (Multiprocess with Active wait synchronization and CUDA MPS). Figures 6, 7 and Table 3 shows an experiment with 1M iterations of the same test performed with different parallelization and synchronization techniques. The pipeline is the simplest possible, composed of one camera, one processing unit performing a matrix-vector multiplication (MVM) and a non intrusive timer.

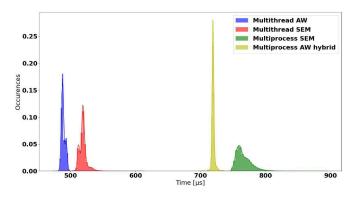

**Figure 6** Normalized histograms with their estimated probability density function (solid lines) of a pipeline composed of one MVM unit with various synchronization approaches (SEMaphore and Active Wait) over 1M iteration on DGX server

The best results in terms of latency come from active wait synchronization (AW) regardless if using multi-thread or multi-process approach with 274.3  $\mu s$  of Mean Execution Time (MET) for multi-process and 272.4  $\mu s$  for multi-thread. Even with this extremely simple pipeline, it still shows noticeable improvement regarding the worse case compared to semaphore based synchronization (gap < 25 $\mu$ s between MMET and MET). However, the histogram of both active

**Figure 7** Execution profiles over 1M iterations for various scheduling and synchronization approaches on the DGX server

| Compute<br>type          | Mean<br>execution<br>time (µs) | <b>ΜΜΕΤ</b><br>(μs) | Average<br>jitter (µs) | Jitter<br>Peak-to-<br>Valley<br>(µs) |

|--------------------------|--------------------------------|---------------------|------------------------|--------------------------------------|

| Multiprocess<br>AW + MPS | 274.3                          | 288.8               | 3.5                    | 25.6                                 |

| Multiprocess<br>SEM      | 290.0                          | 310.8               | 2.3                    | 29.2                                 |

| Multithread<br>AW        | 272.4                          | 294.9               | 10.7                   | 42.0                                 |

| Multithread<br>SEM       | 296.0                          | 334.3               | 2.3                    | 45.9                                 |

**Table 3** Summarised results of different synchronization approaches on DGX server

wait synchronization approaches shows that results are scattered across two Gaussian distributions. That is why the average jitter of multi-thread active wait is considerably higher compared to the three other approaches. This behaviour is not yet explained as it doesn't look like an external interference, which would have been highlighted with semaphore approach as well. The multi-thread approach shows slightly higher Peak-To-Valley jitter (P2V – MMET minus the minimum measured time) with 42.0  $\mu s$  with AW synchronization and 45.9  $\mu s$  with semaphore synchronization. The multi-process approach (25.6  $\mu s$  for AW and 29.2  $\mu s$ ) is slightly more stable.

With these considerations, the active-wait based synchronization is still outperforming semaphores in terms of latency and MMET and remains the preferred option with a dGPU. The multi-process approach shows slightly more stable results, although these gains are not sufficient to discard the multi-threaded approach.

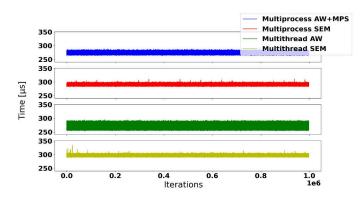

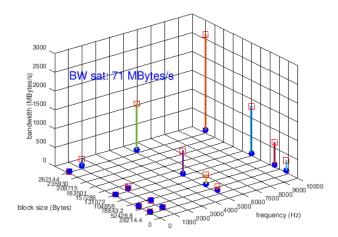

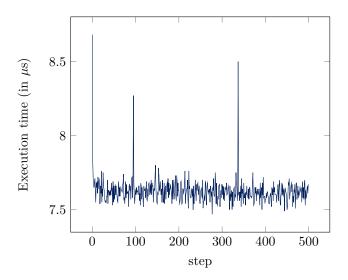

**Figure 8** Normalized histograms with their estimated probability density function of a pipeline composed of one MVM unit with various synchronization approaches (SEMaphore and Active Wait) over 1M iterations on the Jetson Xavier

**Figure 9** Execution profiles over 1M iterations for various scheduling and synchronization approaches on the Jetson Xavier

| Compute<br>type     | Mean<br>execution<br>time (µs) | <b>ΜΜΕΤ</b><br>(μs) | <b>Average</b><br>jitter (μs) | Jitter P2V<br>(µs) |

|---------------------|--------------------------------|---------------------|-------------------------------|--------------------|

| Multithread<br>AW   | 239.4                          | 252.5               | 4.4                           | 21.5               |

| Multithread<br>SEM  | 263.9                          | 346.4               | 4.8                           | 139.8              |

| Multiprocess<br>SEM | 277.4                          | 378.8               | 8.4                           | 129.7              |

**Table 4** Summarised results of synchronization techniques

on the Jetson Xavier

#### **Experimental results on Jetson Xavier**

As MPS is not available on Jetson Xavier, only 3 cases can be assessed. We performed the exact same experiment on this hardware and the results are presented in figures 8, 9 and

Table 4.

When comparing results obtained on both the dGPU and iGPU platforms, a noticeable difference is that semaphore synchronization approaches lead to less stable results on the iGPU case with a up to  $101.4\mu s$  gap between the MET and the MMET for multi-process and 82.5 for multi-threaded based approach. The multi-threaded active wait synchronization is performing best with only 13.1  $\mu s$  difference. The P2V jitter shows the same kind of outcome with 21.5  $\mu s$  for multi-thread AW, 139.8  $\mu s$  for multi-thread SEM and 129.7  $\mu s$  for multi-process SEM. Even though CPU cores are isolated on Jetson, semaphore synchronization is more prone to interference compared to the dGPU case. Multi-thread results are still considered satisfactory results, both in terms of MMET and average time to solution.

Regarding semaphore performance, it appears that multithread performs slightly better compared to multi-process. When comparing to the dGPU (Figure 6), the reverse occurs with multi-process semaphore delivering slightly better execution time. It may be caused by how CPU contexts are handled on both platforms (introducing CPU context switch) and probably some CPU interference, more pronounced on Jetson Xavier. We will investigate further such behavior in future work.

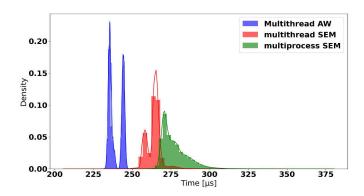

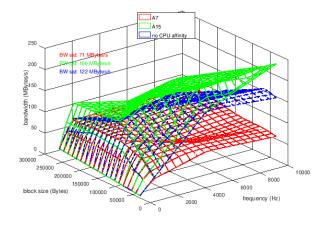

#### Multiprocess with hybrid active wait

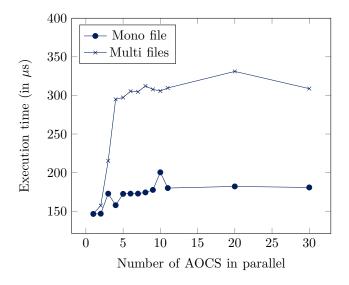

**Figure 10** Normalized histograms with their estimated probability density function of a pipeline composed of two MVM units with the proposed hybrid (CPU/GPU) active wait compared to other synchronization approaches (Semaphore and active wait) on the Jetson Xavier

As aforementioned, the way the GPU handles multiple processes and CUDA contexts is not suitable for GPU busy waiting synchronization. A proposed workaround is to take advantage of shared memory to avoid busy waiting with GPU threads.

This hybrid active-wait strategy relies on letting the CPU do the busy waiting on data shared with the GPU while notifications are sent through GPU kernels. This allows the GPU scheduler to stop constantly switching between multiple CUDA contexts requiring GPU usage.

Although this implementation should not benefit from the latency hiding obtained with look ahead kernel launch and

**Figure 11** Execution profiles over 1M iterations of the hybrid active wait compared to other synchronization approaches on the Jetson Xavier

| Compute<br>type           | Mean<br>execution<br>time (µs) | <b>ΜΜΕΤ</b><br>(μs) | Average<br>jitter (µs) | Jitter P2V<br>(µs) |

|---------------------------|--------------------------------|---------------------|------------------------|--------------------|

| Multithread<br>AW         | 488.9                          | 572.4               | 3.0                    | 93.2               |

| Multithread<br>SEM        | 519.0                          | 611.1               | 5.8                    | 116.9              |

| Multiprocess<br>SEM       | 766.16                         | 893.3               | 11.6                   | 158.9              |

| Multiprocess<br>AW hybrid | 719.3                          | 752.5               | 2.4                    | 56.1               |

**Table 5** Summarised results of hybrid synchronizationtechniques on Jetson

still partly suffers from context switching overheads, using the GPU for notification may help to reduce noxious interference coming from the CPU, plus avoiding some CPU/GPU synchronizations compared to semaphore approach.

It is important to note that such implementation is possible only with a sequential pipeline as concurrent kernels have to be implemented through CUDA streams, otherwise the resulting performance and determinism will be severely affected.

In this test case (Figure 9, 10 and Table 5), the new mechanisms described are implemented (results named Multiprocess AW hybrid), resulting in a new approach for multiprocess synchronization. In order to expose how different kinds of synchronization affect performance, two sequential computing units are instantiated thus reproducing exactly the setting for Figure 4. The first noticeable thing is that the gap between multi-threaded and multi-processed synchronization increases as the pipeline complexity grows. Regarding latency, the multi-thread approach shows best results regardless the kind of synchronization (488.9  $\mu$ s for active wait and 519.0  $\mu$ s for semaphore) where the multi-process approach is taking an extra 200  $\mu$ s for the exact same computations (766.16  $\mu$ s for semaphore and 719.3  $\mu$ s for the new hybrid synchronization). This brings to light the cost of GPU context switch which never happens in a multi-threaded application.

However, it also shows that synchronization on the GPU is an environment less prone to interference. The difference between the MMET and MET of the hybrid active wait approach is 33,2  $\mu$ s where the second best being multi-thread AW with a difference of 83,5  $\mu$ s. Finally, semaphore synchronization with multi-thread gives a difference of 92,1  $\mu$ s and the multi-process approach comes last with a 127,14  $\mu$ s difference. The P2V jitter confirms this result with 56.1  $\mu$ s for the multi-process hybrid AW, 93.2  $\mu$ s for multi-thread AW, 116.9  $\mu$ s for multi-thread SEM and finally 158.9  $\mu$ s for multi-process SEM.

As a consequence, the hybrid active waiting, although showing marginal latency improvement compared to using multi-process semaphore is still far from reaching multithreaded approaches performance and cannot be proposed as a universal replacement for active wait with CUDA MPS. Still, it is a great replacement for pipelines that need to communicate through multi-process and is a good solution in terms of determinism.

#### Conclusion

The best practices introduced in the COSMIC framework enable the realization of complex compute intensive pipelines while keeping a high level of modularity thanks to its efficient synchronization mechanism.

It delivers latency improvements while keeping a stable jitter with discrete GPUs, but its use on embedded platforms needs to be adapted in order to work around missing features on such hardware and supporting ecosystem. Best results are obtained when reproducing the same mechanism with a multi-thread implementation, instead of multiprocess. This allows the CUDA environment to keep a single context, avoiding both kernel preemption and context switching. However, the behaviour may differ between multiple processes and multiple streams implementations depending on how the scheduler handles kernels.

The embedded Jetson CUDA package is still missing some critical features of multi-process programming. However, it is possible to get it working using using the hybrid active wait strategy detailed in this paper. While the user needs to be aware of the corresponding performance trade-off, making sure only one context is executed at a given point in time, a pipeline can be built with processes sending notifications using the GPU by taking advantage of shared memory between CPU and GPU. Such approach performs better than synchronization through CPU semaphores both in terms of jitter and latency.

Future work will focus on further testing these new approaches to get a better understanding of embedded platforms behaviour in order to get closer to true GPU real-time determinism.

#### 10 ERTS 2022

#### Acknowledgements

This work is sponsored through a grant from project 873120, a.k.a. Rising STARS, funded by European Commission under program H2020-EU.1.3.3 coordinated in H2020-MSCA-RISE-2019.

#### References

- F. Ferreira. Hard real-time core software of the AO RTC COSMIC platform: architecture and performance. *Proceedings of SPIE - The International Society for Optical Engineering*, 2020.

- [2] NVIDIA. Cuda for tegra. https://docs.nvidia.com/cuda/ cuda-for-tegra-appnote/, 2021.

- [3] Julien Bernard. Design and performance of a scalable GPU-based AO RTC prototype. Proceedings of SPIE -The International Society for Optical Engineering, 2018.

- [4] Allen Todd. Improving Real-Time Performance with CUDA Persistent Threads (CuPer) on the Jetson TX2. Concurrent Real-Time White Paper, 2018.

- [5] Yang Ming. Avoiding Pitfalls when Using NVIDIA GPUs for Real-Time Tasks in Autonomous Systems. ECRTS 2018, 2018.

- [6] Paweł Czarnul. Investigation of parallel data processing using hybrid high performance CPU+GPU systems and CUDA streams. *Computing and informatics*, 2020.

- [7] Ali Waqar. Protecting Real-Time GPU Kernels on Integrated CPU-GPU SoC Platforms. *ECRTS* 2018, 2018.

- [8] Kenjić Dušan. One Solution for Deterministic Scheduling on GPU for Automotive Algorithms. 2021 Zooming Innovation in Consumer Technologies Conference, 2021.

- [9] Jason Baietto. Real-Time Linux: The RedHawk Approach. *Concurrent Real-Time whitepaper*, 2019.

- [10] Tanya Amert. Gpu scheduling on the NVIDIA TX2: hidden details revealed. *IEEE Real-Time Systems Symposium*, 2017.

- [11] Ignacio Sanudo Olmedo. Dissecting the CUDA scheduling hierarchy: a Performance and Predictability Perspective. *RTAS*, 2020.

- [12] Vance Miller. Determinism in GPU Programs, Real Time Applications on the NVIDIA Jetson TK1. *Senior Honors Thesis, University of North Carolina*, 2016.

- [13] Nicola Capodieci. Contending memory in heterogeneous SoCs: Evolution in NVIDIA Tegra embedded platforms. *IEEE Real-Time Systems Symposium*, 2020.

- [14] Nathan Otterness. Inferring Scheduling Policies of an Embedded CUDA GPU. Department of Computer Science, University of North Carolina, 2017.

## PasTiS: building an NVIDIA Pascal GPU simulator for embedded AI applications

Michaël Adalbert<sup>\*†</sup>, Thomas Carle<sup>†</sup>, Christine Rochange<sup>†</sup> \**IRT SystemX*, Palaiseau, France <sup>†</sup>*IRIT - Univ. Toulouse III - CNRS*, Toulouse, France, name.surname@irit.fr

Index Terms—GPU, cycle-accurate simulator, timing analysis

Abstract—We present PasTiS, a simulator for the NVIDIA Pascal GPU architecture family, with a focus on timing simulation. PasTiS supports a subset of the Pascal ISA, sufficient to simulate the execution of neural networks. We present this subset, as well as the underlying microarchitecture that we modelled using information available from NVIDIA, from scientific publications, and from our own experiments. We demonstrate the precision of the simulator by comparing it to measurements on the NVIDIA Jetson TX2 development board, on neural network applications.

#### I. INTRODUCTION

Real-time systems are increasingly embedding machine learning software which requires a huge computing power. For example, the control systems of autonomous vehicles rely on neural networks (NNs) to detect roads and objects, compute trajectories and plan the actions to be performed. These algorithms are computation-intensive and inherently parallel, which drives the industry to adopt massively parallel hardware such as many-core and GPU accelerators. In particular, GPUs have received a lot of attention these last years, both from the industry and from the real-time research community.

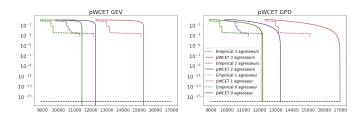

Scheduling tasks in a timing-critical system, so as to ensure that they will meet their timing constraints, requires being able to determine their respective worst-case execution time (WCET). Various approaches to WCET analysis exist and are based on static analysis techniques and/or measurements [10]. The estimated WCET can then be deterministic (i.e. expressed as a single upper bound) or probabilistic (i.e. several WCET values are produced, each associated to a probability of being exceeded) [9]. In this paper, we focus on systems where strict upper bounds on execution times are needed, and thus consider static WCET analysis approaches.

Static WCET analysis aims at determining invariants on the code of the task under analysis. Some invariants are related to the software (e.g. loop bounds), others to the state of the hardware (processor, cache memories, etc.). They are all used to build an integer linear program (ILP) that maximizes the execution time of the task over all the possible paths in the control flow graph (CFG) [17]. OTAWA is an open-source framework that offers many built-in facilities to generate WCET analysis tools [4].

Computing hardware-related invariants requires modeling the behaviour of the computing platform. This is usually done manually by translating the knowledge we have of the hardware (from documentation provided by the processor manufacturer or designer) into a formal model, although automatic translation from a VHDL specification of the processor (when available) has also been considered [24].

However, most of existing work considers CPU-only platforms. The very specific execution model of GPUs (Single Instruction Multiple Threads - SIMT) requires a substantial revisiting of hardware models. First, the lockstep execution of batches (*warps*) of threads requires rethinking the concept of basic block and instruction sequence due to possible branch divergence: all the threads in a warp do not necessarily follow the same control flow. Second, GPUs implement hardware scheduling schemes for warps and blocks of threads that must be accounted for in WCET estimations. Third, their memory system is noticeably different from that of standard CPUs and requires specific analyses.

The closed nature of most GPUs and the lack of official documentation on their micro-architecture have slowed down the understanding and modeling of their micro-architectural behaviour, which plays a crucial role in the execution time. These reasons explain that so far, no decent (industrial or academic) WCET analyzer for GPU-accelerated code is available.

As part of the French national *Confiance.ai*<sup>1</sup> program that brings together industry and academic researchers to build trustworthy Artificial Intelligence, we ambition to extend static WCET analysis techniques to GPUs. The work presented in this paper was mainly supported by the Labex CIMI<sup>2</sup> through the AVATAr project, and is a first step towards this objective: we show how we were able to conduct experiments to uncover some of the execution mechanisms and hardware parameters of an NVIDIA Pascal GPU and how we have built a cycle-level simulator that is able to run CUDA programs. We compare the execution times evaluated by the simulator to those measured on a Jetson TX2 board and demonstrate the accuracy of our model.

The insights provided in the paper can be used by industrial actors to assess the viability of using a GPU in their embedded systems: they give a clearer view of how a GPU program is actually executed and of the specificity with respect to CPU

This work was partially supported by the ANR LabEx CIMI (grant ANR-11-LABX-0040) within the French State Programme "Investissements d'Avenir."

<sup>&</sup>lt;sup>1</sup>https://www.confiance.ai/en/

<sup>&</sup>lt;sup>2</sup>https://cimi.univ-toulouse.fr/en/

execution. Although we focus on a particular NVIDIA GPU, the general mechanisms that we describe are common to all GPUs.

*Contributions:* In this paper, we present how we have proceeded to understand the behavior of an NVIDIA Pascal GPU and how we have used this knowledge to develop a cyclelevel simulator called PasTiS (Pascal Timing Simulator).

Section II describes the general organization and execution model of GPUs, with a focus on our target (NVIDIA Pascal architecture). In Section III, we detail two key aspects of the GPU behaviour (thread divergence and accesses to the shared memory), and how we proceeded to understand them. We then introduce the PasTiS simulator in Section IV, and evaluate its performance in Section V. Related work is discussed in Section VI. Section VII concludes the paper.

#### II. GPU ORGANIZATION AND EXECUTION MODEL

In this section we present the global organization and execution model of GPUs. We borrow the NVIDIA terminology which is widely accepted in the community, but similar concepts exist in GPUs from other manufacturers.

#### A. Heterogeneous computation

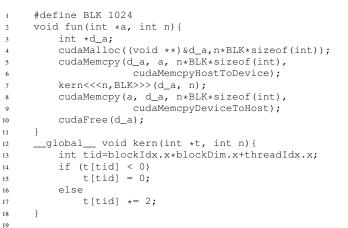

At the highest level, a GPU is an accelerator on which a CPU can offload functions called kernels. A kernel is specified in a particular language (or a language extension, such as CUDA or OpenCL) that enables the description of parallel computation. The offloading of a kernel to a GPU generates threads that all execute the same code. The number of threads is specified by the programmer, as a number of blocks and a number of threads per block, and should be as high as possible in order to fully benefit from the GPU's resources. This is illustrated in Figure 3. In this example, a CPU function (lines 2-11) modifies each element in an array, depending on its initial value. Instead of processing elements sequentially, it invokes a GPU kernel (line 7) for a number of threads equal to the array size (n  $\times$  BLK). The code of the kernel is given on lines 12-18. Each thread executing this code determines its identifier (line 13) – a value between 0 and  $n \times BLK$ , and according to the initial value of the element (line 14), it computes its new value (lines 15 and 17). The CPU and the GPU have distinct main memories and the GPU cannot access the CPU memory. For this reason, the CPU function has to allocate space in the GPU memory (line 4) and to transfer input data from the CPU memory to the GPU memory (line 5) and output data from the GPU memory to the CPU memory (*line* 8).

#### B. General organization

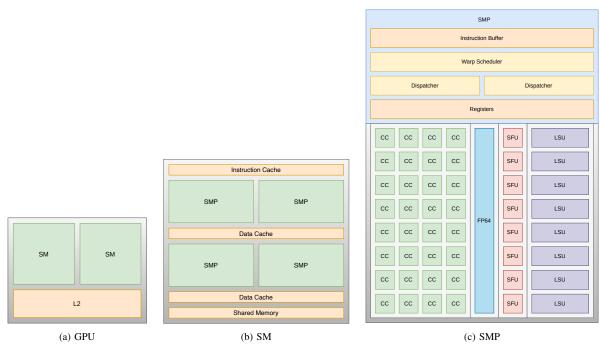

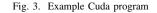

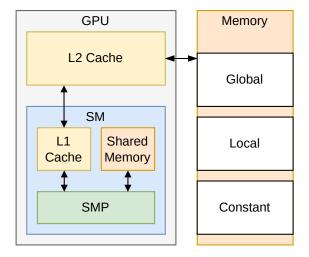

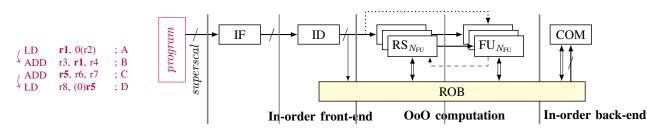

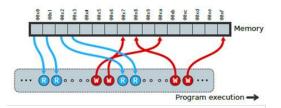

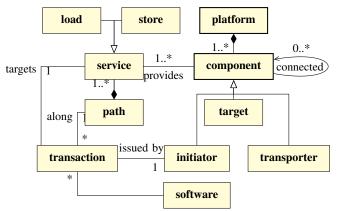

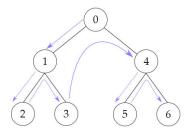

On the hardware side, a GPU is a collection of clusters called *Streaming Multiprocessors* (SMs). Figure 1.a shows that the NVIDIA Pascal GPU of the Jetson TX2 contains two SMs, that share an L2 cache. Each SM contains in turn four processing blocks, denoted SMPs, that share an L1 instruction cache and two L1 data caches (each shared by two SMPs), as well as a fast multi-banked memory referred to as the

shared memory (Figure 1.b). An SMP includes 32 *Cuda Cores* (CCs) that perform ALU and floating-point (32- and 16-bit) operations, a 64-bit FP unit, 8 Special Function Units and 8 Load/Store Units (Figure 1.c). It is then able to execute several operations in parallel, e.g. 32 integer instructions or 8 memory loads. In addition, the GPU contains resources to host thousands of active threads so that context switching is extremely fast.

When a kernel is offloaded to a GPU, each block of threads (e.g. 1024 threads in the example of Figure 3) is mapped to one SM. This mapping is performed by the hardware, following a heuristic that tries to maximize the use of the SMs [21].

#### C. Execution model

At the lowest level, GPUs implement the Single Instruction Multiple Threads (SIMT) execution model, which can be seen as a mix between simultaneous multithreading and the SIMD<sup>3</sup> model. A block of threads is organized into fixed pools of 32 threads called *warps*<sup>4</sup>. All the threads inside a warp are executed in lockstep: in a given clock cycle, they all execute the same instruction. This reduces the complexity of the instruction fetch and decoding logic since these operations are shared between the 32 threads of a warp.

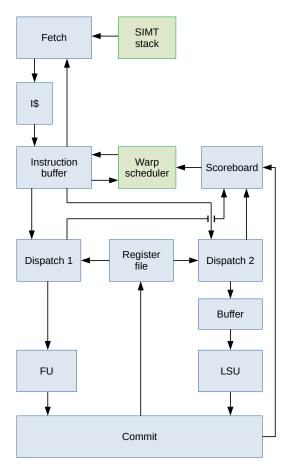

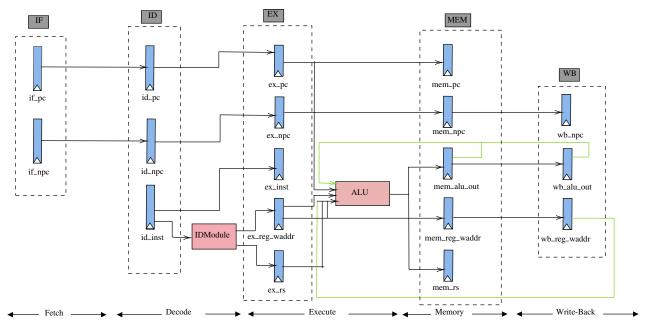

Warps are the smallest schedulable entities in a GPU. An SMP contains an instruction buffer for each active warp, which stores the next instructions to be executed by the warp. At each execution cycle, a hardware warp scheduler is responsible for electing a warp for execution among those that are ready, following a given scheduling policy [19]. A warp is ready for execution when all data dependencies have been resolved (which is checked using a scoreboard, as explained in Section II-D), when its next instruction is available in its instruction buffer and when the required functional units are available. The instruction to be executed by the elected warp is sent to a dispatch unit that pushes the instruction to the required functional units. Each SMP has two dispatch units: one for memory operations (which target LSUs) and one for the other instructions. The full processing of an instruction is depicted in Figure 2.

As long as all threads inside a warp agree on the control flow (i.e. they follow the same direction at conditional branches), the SIMT execution scheme is straightforward. However, when threads within the same warp disagree on whether or not to take a branch, both paths are executed *in sequence* one after the other, with only one part of the threads being active on each path. This phenomenon is known as *thread divergence* [8].We explain in Section III-A how thread divergence is handled in Pascal GPUs.

#### D. Scoreboard update and scheduling instructions

Recent NVIDIA GPUs handle pipeline hazards using a software programmed scoreboard: in a Pascal GPU program, the compiler inserts so-called *scheduling instructions* [11]

<sup>4</sup>The number of threads in a warp is not the same in all GPUs depending on the vendors. In NVIDIA GPUs, warps are always composed of 32 threads.

<sup>&</sup>lt;sup>3</sup>Single Instruction Multiple Data

Fig. 1. Architecture of a Pascal GPU

between each group of three successive instructions. These are responsible for updating the scoreboard with information needed to enforce data dependencies (minimum instruction latencies, setup of local fences).

#### E. Memory hierarchy

All the SMs share a *global memory* that can be used by their threads to communicate between SMs, and a constant memory which stores constants. The global memory is also used to communicate between the CPU and the GPU through the use of a hardware *copy engine* that transfers data and instructions between the CPU and GPU memory spaces. Threads can also access a private *local memory*, which is in practice an area of the global memory. The global, constant and local memories are accessed through a cache hierarchy composed of an L2 cache, shared by all the SMs, and L1 caches, local to each SM. The memory hierarchy of the Pascal GPU is displayed in Figure 4.

In addition, each SM features a so-called *shared memory*. In the GPUs terminology, shared memory refers to a fast memory local to each SM, that is shared by threads that belong to the same block. NVIDIA reports a 100x lower latency for shared memory accesses compared to uncached global memory accesses, making it a key factor in the acceleration of kernel execution. It is implemented as an interleaved multi-banked SRAM with 32 banks storing 32-bit words. In the ideal case, threads of a given warp access either words from different banks or the same word from a given bank. The hardware is optimized to serve such requests with minimal latency and maximal throughput by grouping them into a single transaction. However, whenever two or more threads

from the same warp try to access different addresses in the same bank at the same time, this results in a conflict. The bank then serves each request in sequence as part of a separated transaction, and all the threads in the warp wait until all requests have been served before executing the next instruction. This obviously degrades performance.

#### III. REVERSE ENGINEERING THE PASCAL GPU EXECUTION

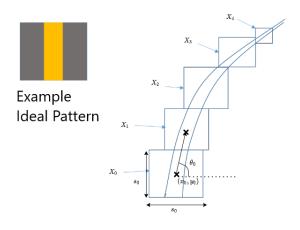

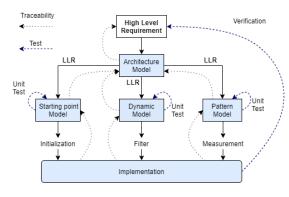

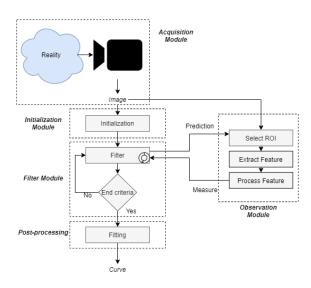

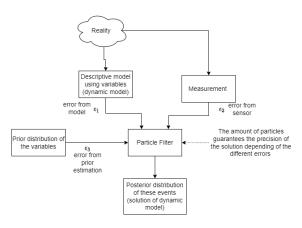

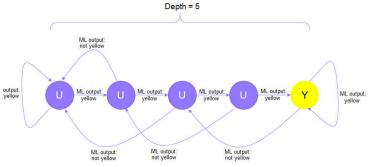

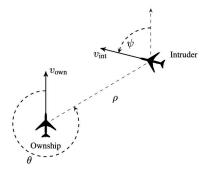

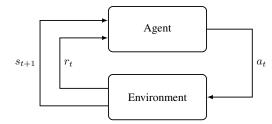

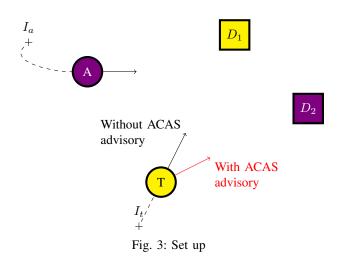

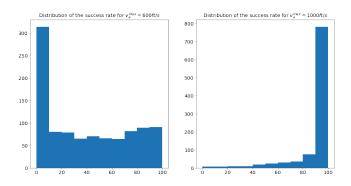

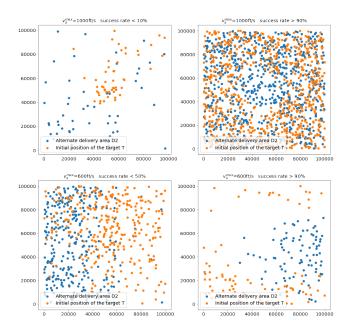

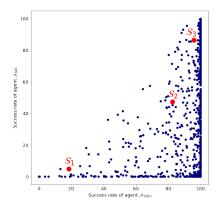

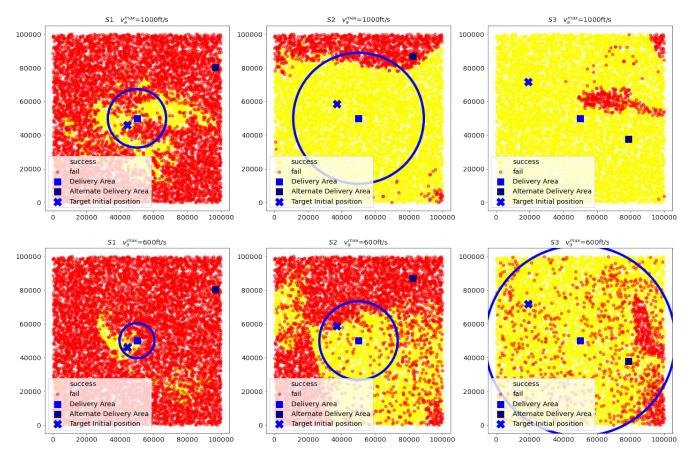

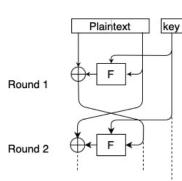

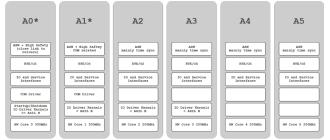

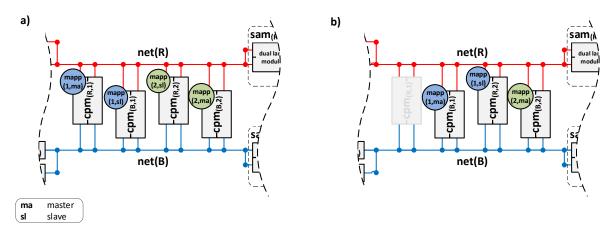

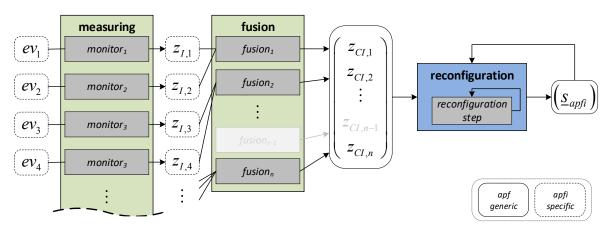

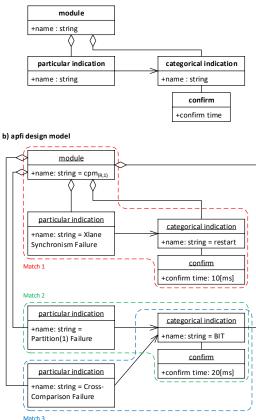

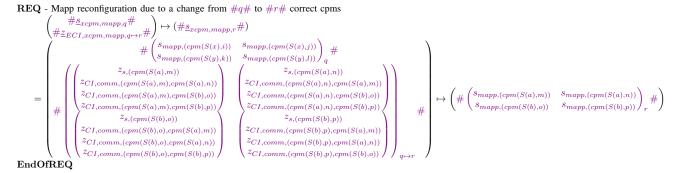

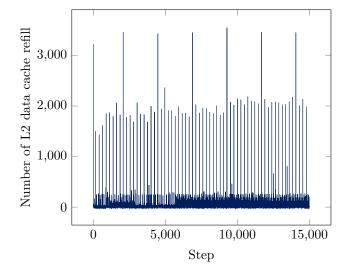

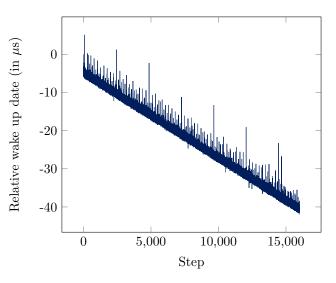

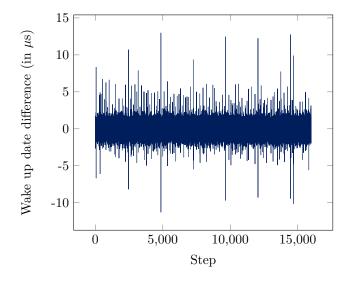

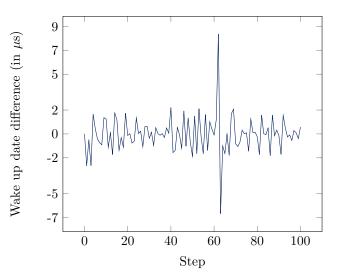

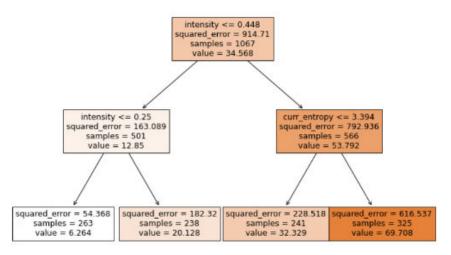

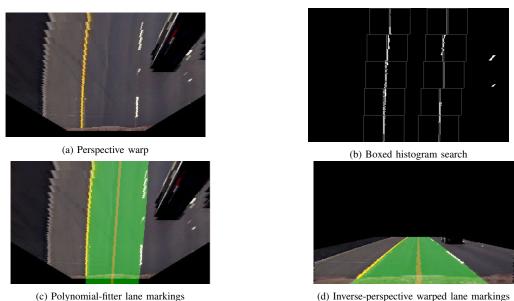

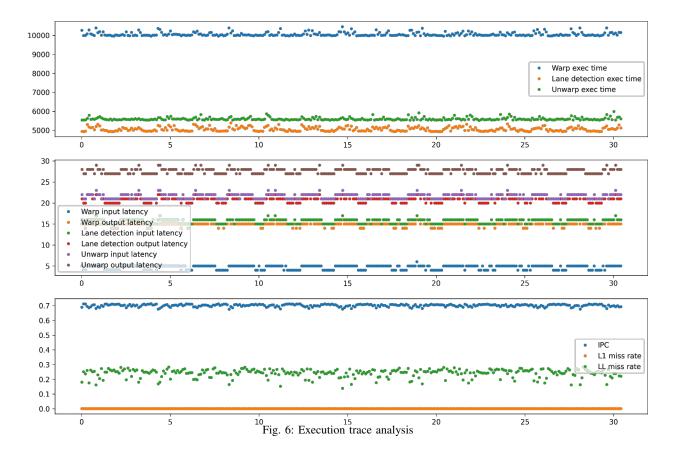

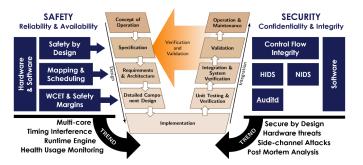

#### A. Thread divergence