# Extraction of small-signal equivalent circuit for de-embedding of 3D vertical nanowire transistor

Bruno Neckel Wesling, Marina Deng, Mukherjee Chhandak, Magali de Matos, Abhishek Kumar, Guilhem Larrieu, Jens Trommer, Thomas Mikolajick, Cristell Maneux

#### ▶ To cite this version:

Bruno Neckel Wesling, Marina Deng, Mukherjee Chhandak, Magali de Matos, Abhishek Kumar, et al.. Extraction of small-signal equivalent circuit for de-embedding of 3D vertical nanowire transistor. Solid-State Electronics, 2022, 194, pp.108359. 10.1016/j.sse.2022.108359. hal-03657781

HAL Id: hal-03657781

https://hal.science/hal-03657781

Submitted on 3 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Extraction of small-signal equivalent circuit for de-embedding of 3D vertical nanowire transistor

Bruno Neckel Wesling<sup>1</sup>, Marina Deng<sup>1</sup>, Chhandak Mukherjee<sup>1</sup>, Magali de Matos<sup>1</sup>, Abhishek Kumar<sup>2</sup>, Guilhem Larrieu<sup>2</sup>, Jens Trommer<sup>3</sup>, Thomas Mikolajick<sup>3</sup>, Cristell Maneux<sup>1</sup>

#### 1. Abstract

In this paper, we present an improved methodology to extract the small-signal electrical equivalent circuit of the parasitic elements using RF test structures for a 3D vertical nanowire transistor technology. The methodology is based on the extraction of the distributed parasitic elements from an open structure for which on-wafer S-parameter measurements were carried out up to 40 GHz. The electrical equivalent circuit of the passive device was then used for de-embedding of the transistor S-parameters for extraction of intrinsic small-signal parameters such as the gate capacitances.

#### 2. Introduction

In the context of emerging technologies for new computing paradigms such as neural networks, vertical nanowire field effect transistors (VNWFET) are a promising technology owing to their naturally 3D architectures [1]. For the circuit design using such a 3D emerging technology, it is necessary to build new and accurate compact models to capture the static and dynamic behavior of the device [2]. However, on-wafer test structures of the devices contain parasitic elements introduced by the RF pads and interconnects that are necessary to probe the devices under test (DUT). The standard procedure to characterize the parasitic effects of a device at high frequencies can be divided into two parts. Firstly, the measurement system needs to be calibrated so that the reference plane is at the probe tips. This can be done using standard calibration techniques such as SOLT (Short-Open-Load-Thru). At this point, all the parasitic elements associated with the pads and interconnects are still included in the measurements. In the second step, S-parameters of the open and short structures are measured which are then used to remove the parasitic elements external to the DUT, through a subtraction process known as de-embedding [3].

Although the process of parasitic extraction is widely used in technologies targeted for high frequency applications, this process can also be applied for technologies such as the VNWFET that are mainly designed for computing applications to improve the modeling accuracy, which normally just relies on DC measurements [1]. Moreover, an accurate modeling of the parasitic elements allows the designer to optimize the 3D layout of the logic circuits and interconnects, thereby improving performance metrics such as compactness and energy-delay product of the technology.

In this paper, we present an elaborate methodology for extracting the extrinsic interconnect parasitic network associated with the unconventional vertical and inherently 3D test structures of the VNWFETs. In the rest of the paper, results from the RF measurements and electro-magnetic (EM) simulations are used for the extraction

<sup>&</sup>lt;sup>1</sup> IMS, University of Bordeaux, UMR CNRS 5218, Bordeaux INP, Talence, France, email: bruno.neckel-wesling@u-bordeaux.fr

<sup>&</sup>lt;sup>2</sup> LAAS-CNRS, UPR 8001, CNRS, University of Toulouse, Toulouse, France

<sup>&</sup>lt;sup>3</sup>NaMLab gGmbH, 01187, Dresden, Germany

of parasitic elements of the electrical equivalent circuit of an open test structure. Finally, we show the small-signal capacitances of a VNWFET extracted using two different de-embedding processes.

#### 3. Methodology

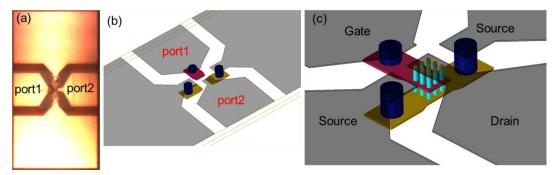

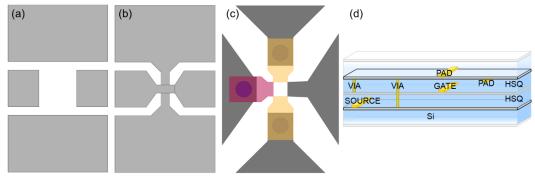

For de-embedding, open structures were fabricated using the same process and on the same wafer as the VNWFETs [4]. The open device consists of all interconnects except for the vertical nanowires. Fig. 1(a) shows the open structure containing the RF pads, where the absence of the active device can be observed. For the demonstration of the de-embedding process, a VNWFET consisting of 81 nanowires in parallel with a diameter of 17 nm each was selected. A drawing of a full transistor can be seen on Fig 1(c).

#### 3.1. On-wafer S-parameter measurements

The on-wafer S-parameters were measured using a Vector Network Analyzer (VNA) from Rohde & Schwarz up to 40 GHz, and a source monitor unit, Agilent 4142B, connected via a bias-tee. The DUTs were contacted using Ground-Signal-Ground (GSG) probes with a pitch of 100 µm following a SOLT calibration. A second test bench that allows S-parameter measurements up to 110 GHz, Agilent® E8361 PNA, was used for the open device to ascertain the credibility of the measurements.

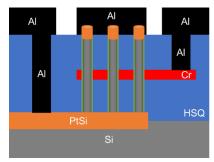

#### 3.2. Electromagnetic simulation

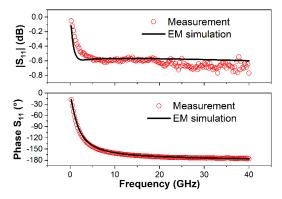

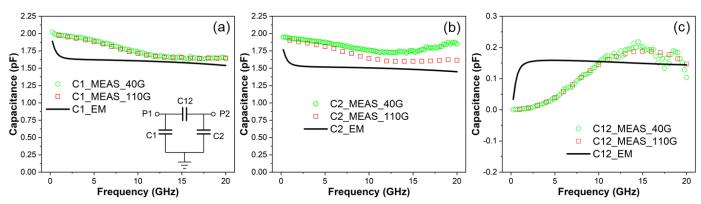

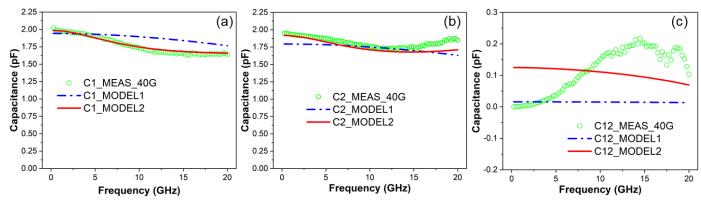

The 3D view of the open device constructed for EM simulations is shown in Fig. 1(b). The ADS-Momentum EM simulator was used for the computation of the S-parameters of the provided layout. To eliminate manual errors, the layout was imported into ADS using the same GDSII file that was used for the fabrication process. The electrical properties of the material layers were set based on the fabrication process [4]. A cross-section of the materials stack is shown in Fig. 1(c). In Fig. 3, a comparison between the measured and the EM simulated S-parameters of the open device is shown. The EM simulation results exhibit very good agreement with the measured data up to 40 GHz. Considering that an open structure can be represented by a  $\pi$ -network consisting of three capacitors, the values of these capacitances were extracted from the Y parameters, which were obtained using the standard S to Y parameter transformation method. The capacitances are presented in Fig. 4 for both measurements and EM simulation. The capacitances obtained from the second measurement setup that reaffirmed the measurement results are presented as C1\_MEAS\_110G, C2\_MEAS\_110G and C12\_MEAS\_110G respectively. The capacitance C1 extracted from the EM simulation showed good agreement with the measurements beyond 10 GHz. Below 10 GHz, discrepancies can be observed that might be related to the limitation of EM simulation in reproducing all the details of the fabricated structures. This indicated that the measurement of the open device below 10 GHz cannot be modeled as a simple  $\pi$ -network. A more complete and lumped model was then investigated taking into account the EM simulation of different sections of the complete open structure.

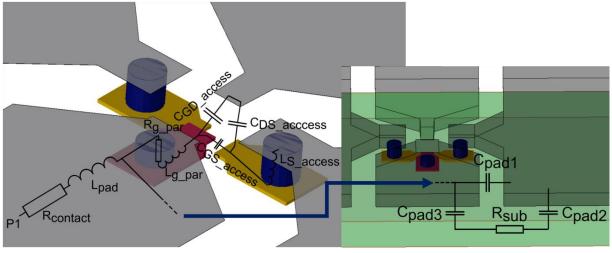

#### 3.3. Distributed equivalent circuit of the transistor interconnects

To construct the small-signal equivalent circuit (SSEC) of the open device, EM simulations of different sections of the complete structure were performed to estimate their individual contributions. The pad was considered as an LC network in series with a contact resistance and a  $\pi$ -network was used to model the coupling capacitances between the gate, drain, and the source accesses. The pad capacitance and impedance are estimated from the

EM simulations of the virtual OPEN\_PAD and SHORT\_PAD structures presented in Fig. 5 (a) and (b), respectively. The coupling capacitances are obtained from the OPEN\_DUT shown in Fig. 5 (c). A figure of the substrated used on ADS for the EM simulation is shown on Fig. 5 (d). The extracted elements are then combined to construct the distributed circuit 'model1'.

The capacitance C1\_MODEL1 in Fig. 6, extracted from 'model1', does not match well with the measurement data. This means that not all parasitic effects were accounted for, and a more detailed circuit is needed [5]. Analyzing the device layout and the fabrication process one can identify that substrate parasitic effects might be present due to (i) a low silicon substrate resistivity [4] and (ii) the absence of a ground shield metal underneath the signal pads [6]. The substrate parasitic elements introduce a lossy path, C<sub>pad2</sub>-R<sub>sub</sub>-C<sub>pad3</sub>, shown in Fig. 7 along with a fringe capacitance C<sub>pad1</sub> [7]. The final SSEC is presented in Fig. 7, denoted as 'model2'. The values of the components in the distributed circuit were a mix of values estimated mathematically from the physical dimensions and material properties of the device as well as from EM simulations. Finally, the capacitance C1\_MODEL2 extracted from the SSEC 'model2', presented in Fig. 6, shows an excellent agreement with the measurement.

#### 3.4. Transistor de-embedding

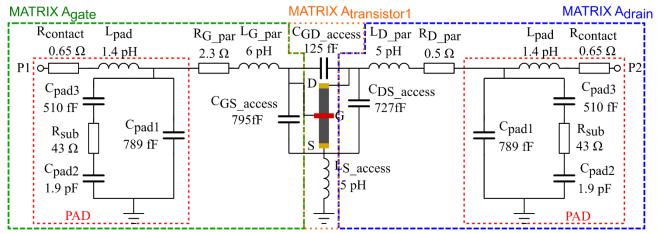

Two different de-embedding methods were used in this work. The first one is a simple open de-embedding process where the Y parameters of the open device are subtracted from those of the transistor, referred to as OPEN\_deemb. The second approach is based on the methodology described in [8], referred to as the access-modeling based de-embedding (AM\_deemb) henceforth. For this, ABCD matrices were used to remove the gate and drain parasitic access contributions, for which the matrix [A<sub>transistor\_meas</sub>] of the complete transistor measurement was multiplied by the inverse of MATRIX A<sub>gate</sub> and MATRIX A<sub>drain</sub>, obtained from the equivalent circuit in Fig. 8,

$$[A_{transistor1}] = [A_{gate}]^{-1} \times [A_{transistor\_meas}] \times [A_{drain}]^{-1}$$

(1)

The Y-parameters of the  $C_{GD\_access}$  (Fig. 8) were then subtracted from the Y parameters obtained from the ABCD-to-Y transformation of matrix  $[A_{transistor1}]$  in (1) as,

$$[Y_{transistor2}] = [Y_{transistor1}] - [Y_{C_{GD\_access}}]$$

(2)

Y-to-Z parameter transformation is then performed on  $[Y_{transistor2}]$  and subsequently the impedance  $L_{S\_access}$  (Fig. 8) was removed by subtracting its Z-parameters:

$$[Z_{transistor\_deemb}] = [Z_{transistor2}] - [Z_{L_{S\_access}}]$$

(3)

The final transistor S parameters were obtained from the transformation of the  $[Z_{transistor\_deemb}]$  parameters obtained from eq. (3).

### 4. De-embedding results

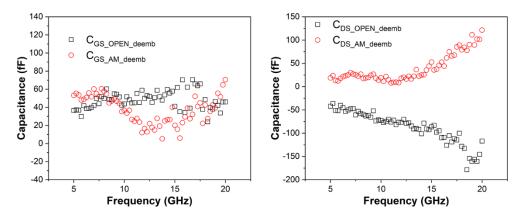

The gate and drain capacitances,  $C_{GS}$  and  $C_{DS}$ , obtained from the de-embedded Y-parameters of the transistor at a  $V_{GS}$  of -1 V and a  $V_{DS}$  of -0.1 V are shown in Fig. 9. The data was truncated at 20 GHz since the VNWFET has no RF gain at higher frequencies and the measurement noise becomes dominant. The  $C_{GS}$  obtained from the AM\_deemb has a mean value of 37 fF compared with 48 fF for the OPEN\_deemb. The  $C_{DS}$  shows a flat value between 5 and 12 GHz for the AM\_deemb, while an unphysical negative value was obtained from the OPEN\_deemb. The  $C_{DS}$  frequency increase above around 12 GHz is a indicator of the limitation in the de-

embedding method, even though the new proposed method provides more physical results compared with the conventional method.

#### 5. Conclusions

In this work, the small-signal equivalent circuit of the VNWFET interconnects was achieved by using the measurements from the open structure and predictive EM simulation. Adding the substrate parasitic network to the distributed SSEC is crucial for higher accuracy of de-embedding since the capacitance of the open device is more than the intrinsic capacitance of the transistor. The extraction of capacitances could be achieved up to 20 GHz, demonstrating a promising efficiency of our proposed method. In the future scope of this work, the extracted values of the gate capacitances will be verified from 3D TCAD simulation of the transistors.

#### Acknowledgments

This work was supported by the project FVLLMONTI funded by the European Union's Horizon 2020 research and innovation program under grant agreement №101016776, by LEGO project (Grant ANR-18-CE24-0005-01) and by the LAAS-CNRS micro and nanotechnologies platform, a member of the Renatech French national network.

- [1] C. Maneux et al., 'Modelling of vertical and ferroelectric junctionless technology for efficient 3D neural network compute cube dedicated to embedded artificial intelligence', IEEE IEDM, San Francisco, Dec. 11-15, 2021.

- [2] C. Mukherjee et al., 'Compact modeling of 3D vertical junctionless gate-all-around silicon nanowire transistors towards 3D logic design', Solid-State Electronics, vol. 183, p. 108125, Sep. 2021, doi: 10.1016/j.sse.2021.108125.

- [3] M. C. A. M. Koolen, J. A. M. Geelen, and M. P. J. G. Versleijen, 'An improved de-embedding technique for on-wafer high-frequency characterization', in Proceedings of the 1991 Bipolar Circuits and Technology Meeting, Minneapolis, MN, USA, 1991, pp. 188–191. doi: 10.1109/BIPOL.1991.160985.

- [4] G. Larrieu et al., 'Sub-15nm gate-all-around field effect transistors on vertical silicon nanowires', Solid-State Electronics, vol. 130, pp. 9–14, Apr. 2017, doi: 10.1016/j.sse.2016.12.008.

- [5] M.-J. Lee, H.-S. Kang, and W.-Y. Choi, 'Equivalent Circuit Model for Si Avalanche Photodetectors Fabricated in Standard CMOS Process', IEEE Electron Device Lett., vol. 29, no. 10, pp. 1115–1117, Oct. 2008, doi: 10.1109/LED.2008.2000717.

- [6] Sangwook Han, Jooyong Kim, and D. P. Neikirk, 'Impact of pad de-embedding on the extraction of interconnect parameters', in 2006 IEEE International Conference on Microelectronic Test Structures, Austin, TX, USA, 2006, pp. 76–81. doi: 10.1109/ICMTS.2006.1614279.

- [7] A. Aktas and M. Ismail, 'Pad de-embedding in RF CMOS', IEEE Circuits Devices Mag., vol. 17, no. 3, pp. 8–11, May 2001, doi: 10.1109/101.933786.

- [8] M. Deng et al., "Benefits and validation of 4-dummies de-embedding method for characterization of SiGe HBT in G-band," 2013 European Microwave Conference, 2013, pp. 1359-1362, doi: 10.23919/EuMC.2013.6686918.

**Figure 1:** (a) Open structure for S-parameters measurements, (b) a 3-D view of the open structure created using ADS MOMENTUM and (c) the drawing of the VNWFETs showing the nanowires.

Figure 2: Drawing of the cross-section of the transistor presenting the stack of materials.

**Figure 3:** Comparison of S-parameters from measurements and electromagnetic simulation for the open test structure.

**Figure 4:** Open structure capacitances extracted from measurements and EM simulation up to 20 GHz. (a) C1, (b) C2 and (c) C12. The inset in (a) shows the equivalent  $\pi$ -network.

**Figure 5:** Virtual structures for the EM simulation, a) OPEN\_PAD, b) SHORT\_PAD, c) OPEN\_DUT and (d) the substrate definition on ADS for EM simulation.

**Figure 6:** Capacitances as a function of frequency extracted from measurements and electrical simulation up to 20 GHz. (a) C1, (b) C2 and (c) C12.

**Figure 7:** 3D view of the distributed model.

**Figure 8:** Electrical equivalent circuit representing the parasitic elements obtained from the open test structure that is used for the de-embedding of VNWFET.

Figure 9: Small signal capacitances as a function of frequency for the de-embedded transistor at a  $V_{GS} = -1V$  and  $V_{DS} = -0.1V$ .