# A gm/ID Design Methodology for 28 nm FD-SOI CMOS Resistive Feedback LNAs

Sylvain Bourdel, Serge Subias, Mohamed Khalil Bouchoucha, Manuel J. Barragan, Andreia Cathelin, Carlos Galup

## ▶ To cite this version:

Sylvain Bourdel, Serge Subias, Mohamed Khalil Bouchoucha, Manuel J. Barragan, Andreia Cathelin, et al.. A gm/ID Design Methodology for 28 nm FD-SOI CMOS Resistive Feedback LNAs. 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2021), Nov 2021, Dubaï, United Arab Emirates. pp.1-4, 10.1109/ICECS53924.2021.9665492. hal-03640029

# HAL Id: hal-03640029 https://hal.science/hal-03640029v1

Submitted on 29 Jul 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A g<sub>m</sub>/I<sub>D</sub> Design Methodology for 28 nm FD-SOI CMOS Resistive Feedback LNAs

S. Bourdel<sup>1</sup>, S. Subias<sup>1</sup>, M. K. Bouchoucha<sup>1,2</sup>, M.J. Barragan<sup>3</sup>, A. Cathelin<sup>2</sup>, C. Galup<sup>4</sup>

<sup>1</sup>Université Grenoble Alpes, Grenoble INP, RFIC-Lab, 38000 Grenoble, France

<sup>2</sup>STMicroelectronics

<sup>3</sup>TIMA Laboratory, CNRS, Grenoble INP, Université Grenoble Alpes, 38000 Grenoble, France <sup>4</sup>Universidade Federal de Santa Catarina, Florianópolis - SC, 88040-900, Brazil

Abstract—This paper presents a simple and efficient methodology for Resistive Feedback LNAs (RF-LNAs) design which uses the inversion level of the transistor as a design parameter in order to optimize the energy efficiency. The method uses a simple 4 parameter-based model valid in all regions of operation and allows a preliminary sizing based on an analytical study. A practical design in a 28 nm FD-SOI technology shows that this methodology is well suited for design at low to moderate inversion level in an advanced technology for which simulation-based studies are often used by designer as early sizing stage. The designed LNA consumes 0.57 mW and achieves an 18.4 dB gain with 3.3 dB of NF.

Keywords—LNA; resistive feedback; low power; inversion coefficient; 28 nm FD-SOI

#### I. INTRODUCTION

The use of region based analytical models to achieve a first sizing of a topology is less and less accurate especially in a low power context and in advanced technologies where weak or moderate inversion gives the best compromise at RF frequencies [1]. This leads to an extensive use of simulations with numerous iterations to obtain the desired requirements.

With the advance of CMOS technologies which offer very high  $f_T$  and  $f_{MAX}$ ,  $g_m/I_D$  design methods introduced in the early 80's for low frequency design are more and more suited to RF application. Some works propose the use of a FOM such as  $g_m f_T / I_D$  [1] or  $g_m^2 / I_D$  [2] to determine the optimal operation region of a device for a RF application. In the case of specific RF building blocks design, some authors use the inversion level to optimize a particular FOM related to the studied function [3]. However, considering just a FOM could lead to non-optimal sizing when specific requirements are targeted. Other design methods have been proposed based on LUT in [4] or based on an abacus in [5]. Such approaches are efficient and accurate but the building of the LUT or the abacus is cumbersome. By replacing LUT or abacus by simple compact model such as EKV or ACM, a  $gm/I_D$  approach allows the designer to use the inversion level  $(i_f)$  as a design parameter to explore the design space as presented in [6].

In this trend we propose a simple analytical method for the sizing of a RF-LNA for Low Power applications such as IoT, in which the trade-off between gain, noise, and consumption has to be carefully optimized [7]. With this method the designer can choose, for a given gain and noise figure, the minimum inversion level to maximize the MOS efficiency and can size

the circuit components with no need for intensive simulations or optimizations. The method is experimentally validated with a practical implementation in silicon.

In the second section, the analytical equations of the RF-LNA used in the method are introduced. The following section presents the compact model [8] used is this work. Then, section IV describes the sizing method and section V details the implementation in the 28 nm FD-SOI technology and the measurement results. Finally, section VI summarizes our main contributions.

#### II. RESISTIVE FEEDBACK LNA

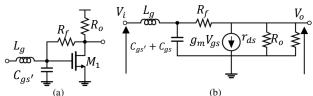

The studied topology is shown in Fig. 1(a) with its small signal equivalent circuit in Fig. 1(b).

Fig. 1: RF-LNA topology (a) and its small signal equivalent circuit (b).

The input impedance of the structure is given in (1)

$$Z_{in} = L_g p + (\frac{1}{(C_{gs'} + C_{gs})p} / / Z_p)$$

(1)

with  $L_g$  the input inductance,  $C_{gs}$  the input parasitic capacitances of the transistor  $M_1$ ,  $C_{gs'}$  a parallel capacitance added for matching purpose and  $Z_p$  the impedance seen at the gate due to the resistive feedback which can be expressed as follows:

$$Z_p = R_p = \frac{R_l + R_f}{1 + g_m R_l} \tag{2}$$

with  $R_l = r_{ds}//R_o$ . Hence the real and imaginary part of  $Z_{in}$  can be written as:

$$R_e(Z_{in}) = R_{in} = \frac{R_l + R_f}{(1 + g_m R_l)(1 + Q^2)}$$

(3)

and

$$I_m(Z_{in}) = L_g \omega_0 - \frac{Q^2}{(1 + Q^2)(C_{as'} + C_{as})\omega_0}$$

(4)

with

$$Q = R_p \left( C_{gs'} + C_{gs} \right) \omega_0. \tag{5}$$

Considering the circuits in Fig. 1(b), the voltage gain at the matching frequency is given by:

$$G_t = \left| \frac{V_o}{V_i} \right| = |G_v| \sqrt{1 + Q^2}$$

(6)

where  $G_{v}$  is the intrinsic gain of the RF-LNA topology given by:

$$G_{v} = \frac{V_{o}}{V_{as}} = -\frac{\left(g_{m} R_{f} - 1\right) R_{l}}{R_{l} + R_{f}} \tag{7}$$

For a resistive feedback topology, the maximum noise figure  $NF_{max}$  is obtained when the inductor input  $L_g$  is null (Q=0). By assuming  $R_g \ll R_f$  and  $\frac{1}{g_m} \ll R_f$  and considering  $gmR_g$  close to 1,  $NF_{max}$  is given by:

$$NF_{max} = 1 + \frac{\left(1 + g_m R_g\right)^2}{R_q R_f g_m^2} + \frac{\gamma}{R_q g_m} + \frac{1}{R_q R_l g_m^2}$$

(8)

where  $R_g$  is the source impedance and  $\gamma$  is the excess noise factor.

#### III. COMPACT MODEL FOR LNA SIZING

Several compact models exist to describe the MOS transistor in all regions of operation. The most used are the EKV and ACM models which are both charge based models using a similar set of equations. In this work, we use the ACM terminolgy and equation sets but the given methodolgy can be also dervied following the EKV formalism. For the sake of simplicity and with the aim of deriving simple analytical expressions which can be easily handled for design, we used the simplest model which is based on only 3 physical parameters: the slope factor n, the normalized specific current  $I_{SQ}$  and the threshold voltage  $V_t$ , and one empirical parameter: the Early voltage  $V_A$ . Given the very high available  $f_T$  of the 28 nm FD-SOI,  $L=40\ nm$  is chosen to increase the gain margin. The main parameters of the transistor are given in TABLE I.

TABLE I. 40 NM LVT-RF MOS CHARACTERISTICS

| n     | $I_{SQ}$ | $V_t$    |

|-------|----------|----------|

| 1.239 | 120.1 nA | 371.6 mV |

In a MOS transistor, the drain current can be expressed from the inversion level respectively in the drain  $(i_r)$  and in the source  $(i_f)$  as follows:

$$I_D = I_s(i_f - i_r) \tag{9}$$

with  $I_S$  the specific current which is technologically dependant and is defined as follows:

$$I_{S} = \mu C_{ox}' n \frac{\phi_{t}^{2} W}{2 L} = I_{SQ} \frac{W}{L}.$$

(10)

In saturation  $i_f \gg i_r$  and the ratio  $g_m/I_D$  only depends on the inversion level  $i_f$  as follows:

$$\frac{g_m}{I_D} = \frac{2}{n\phi_t(\sqrt{1+i_f}+1)} \tag{11}$$

which gives a very simple equation to use in design. In addition, in saturation region, for  $V_s = 0$ , the gate voltage is related to the inversion level  $i_f$  by:

$$V_g - V_t = n\phi_t \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right] \tag{12}$$

In saturation region  $(i_f \gg i_r)$ , based on (11) and (9), the MOS width is related to the inversion level  $i_f$  and the  $g_m$  as:

$$W(i_f) = \frac{L g_m n U_t}{2 I_{sa}(\sqrt{1 + i_f} - 1)}$$

(13)

#### IV. LNA SIZING

In this work, we target an intrinsic voltage gain  $|G_v| = 6.15$  and a NF = 2.5. The first step of the proposed sizing method is to define the inversion level needed to achieve a given gain. To this end, the intrinsic voltage gain is derived as a function of  $i_f$ . To do so, the ratio  $g_m/I_D$  is introduced in the gain expression (7) through the Early voltage  $(V_A)$  as follows:

$$G_{v} = -\frac{\left(g_{m} R_{f} - 1\right)}{1 + \frac{R_{f}}{R_{l}}}$$

$$= -\frac{k - 1}{1 + \frac{g_{m}}{I_{d}} \frac{\left(V_{DD} - V_{DS}\right)\left(V_{A} + V_{DS}\right)}{V_{DD} + V_{A}}}$$

(14)

where  $k = g_m R_f$ . For low values of  $V_A(i.e.\ V_{DD} \gg V_A)$  as it is the case in advanced technologies,  $G_v$  is maximum for  $V_{DSOPT} = (V_{DD} - V_A)/2$ . Hence, the maximum gain is obtained when:

$$r_{ds} = R_o = \frac{(V_{DD} + V_A)}{2I_D} \tag{15}$$

and is given by:

$$G_{\nu_{\text{max}}} = -\frac{k-1}{1 + \frac{k}{\frac{g_m}{I_D}} \frac{V_A + V_{DD}}{4}}$$

(16)

Note that, when  $V_{DD} \ll V_A$ , as it is often the case in large technology nodes,  $R_o$  must be maximized to maximize the gain.

With (11) we can express the gain as a function of  $i_f$  as follows:

$$G_{v}(i_{f}) = -\frac{k-1}{1 + \frac{2 n U_{t} k(\sqrt{1+i_{f}}+1)}{V_{A} + V_{DD}}}$$

(17)

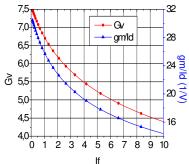

$G_v(i_f)$  and  $g_m/I_D(i_f)$  are plotted in Fig. 2 from (17) and (11) for a 40 nm LVTN-RF transistor of the 28 nm FD-SOI technology from STMicroelectronics which is used in this study. In our case, we have chosen k=20 to have sufficient headroom to comply with the gain requirement. As shown in Fig. 2, to perform a voltage gain of  $|G_v|=6.15$ , the maximum inversion level is  $i_f=2.1$  which corresponds to  $g_m/I_D=$

$22.6\,V^{-1}$ . Note that a lower  $i_f$  could be chosen to further improve the efficiency. However, this leads to a larger transistor which will reduce the bandwidth. Hence, the maximum inversion level is the one that gives the targeted gain with the largest bandwidth.

In a second step, the value of  $g_m$  is determined for a targeted  $NF_{max}$ . With (8) we can derive  $g_m$  as a function of  $NF_{max}$  as follows:

$$g_m \approx \frac{\gamma + \frac{1}{G_v}}{R_g(NF_{max} - 1)} \tag{18}$$

From (18), with  $\gamma = 0.808$ , the required  $g_m$  to perform a  $NF_{max} = 2.49$  is 13.1 mS.

Fig. 2:  $G_v(i_f)$  and  $g_m/I_D(i_f)$  for k=20,  $V_{DD}=1$ V,  $V_A=650$ mV, n=1.239

From that point, the sizing of the circuit is straight forward. Knowing  $g_m$  and  $g_m/I_D$ , the bias current can be evaluated, resulting in  $I_D=579~\mu A$ . Assuming that  $i_r=0$  in saturation region, the width of the transistor is obtained with (9) and (10) resulting in 78.5  $\mu m$  in our case study. From (15) the load resistance is  $R_o=1.43~K\Omega$  and the feedback resistance is  $R_f=1.6~K\Omega$  to have the chosen k factor (k=20). From (2) the equivalent input resistance seen at the gate is  $R_p=224~\Omega$ .

On the basis of (3), (4) and (5), the impedance matching is done as follows. Knowing  $R_p$ , the input Q factor needed to synthesize  $50~\Omega$  is calculated with (3) and is 1.86. The value of the capacitance added in parallel with  $C_{gs}(C'_{gs})$  is evaluated with (5) and the inductor needed to cancel the imaginary part is calculated with (4). With this approach, it is possible to match the LNA for different frequencies up to a maximum frequency given by:

$$f_{max} < \frac{Q}{(1+Q^2)R_{in}C_{gs}} \tag{19}$$

TABLE II gives  $\mathcal{L}_g$  and  $\mathcal{C}'_{gs}$  for different matching frequencies.

TABLE II. COMPONENT VALUES FOR TUNER MATCHING

| Freq (GHz) | $C'_{gs}$ (pF) | $L_g$ (nH) |  |  |

|------------|----------------|------------|--|--|

| 1          | 1.31           | 14         |  |  |

| 1.8        | 0.72           | 8.2        |  |  |

| 2.4        | 0.53           | 6.2        |  |  |

### V. IMPLEMENTATION AND MEASUREMENTS

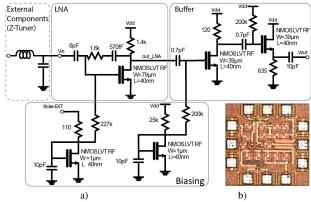

The LNA has been designed with the 28 nm FD-SOI technology from STMicroelectronics. The schematic and the die photograph of the complete circuit are given in Fig. 3. Given that the aim of this work is to validate a design method,  $L_g$  and  $C_{gs}'$  are not included in the test chip to facilitate the test at

multiple frequencies and a DC block capacitor of 6 pF has been included. An active output buffer is integrated for measurements under 50  $\Omega$  environment. The core area is 0.07 mm<sup>2</sup>.

Fig. 3: Schematic (a) and die photograph (b) of the implemented circuit

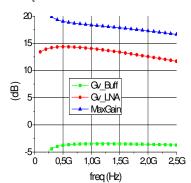

The post layout simulations of the gain of the integrated circuit are given in Fig. 4. The maximum gain (MaxGain) is the gain of the matched device at all frequencies. The DC gain of the LNA is in good agreement with the target stated in the analytical sizing. At 1 GHz a discrepancy of 1.5 dB is observed due to frequency behaviour which is not taken into account in the presented methodology. The simulated gain of the buffer is -3.5 dB and the maximum gain at 1 GHz is 18.4 dB which corresponds to  $G_t$ .

Fig. 4: Simulations of the buffer, the LNA and the maximum gain.

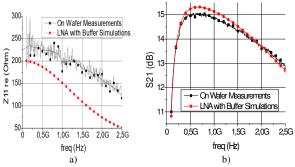

As shown in Fig. 5, on-wafer measurements show good agreement between simulation and measurements. The measured DC value of  $R_p$  is 225  $\Omega$  and the  $S_{21}=15$  dB at 1 GHz. The LNA consumes 570  $\mu A$  (instead of 579  $\mu A$  in simulation).

Fig. 5: On-wafer measurement of Re(Z11) a) and S21 b).

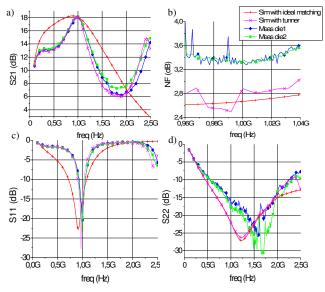

The circuit has been mounted on a FR4 PCB using a Chip On Board (COB) assembling technic. Measurements were performed with an impedance tuner (MAURY MICROWAVE 8045D) to synthesize  $L_g$  and  $C'_{gs}$ . Fig. 6 compares measurements with post layout simulations including a model of the die to PCB interconnection obtained with EM simulation and the measured S parameters of the impedance tuner. Simulations and measurements are in good agreement. The measured gain of the complete device is 18 dB which is close to the simulated maximum gain (18.4 dB). The bandwidth reduction comes from the impedance tuner and does not occur when lumped components are used as shown by simulation in Fig. 6a. This is confirmed by  $S_{11}$  simulation and measurement shown in Fig. 6c. The output buffer offers a wide matching bandwidth with a  $S_{22}$  lower than -10 dB from 595 MHz to 2.55 GHz. The measured noise figure is 3.3 dB and is slightly higher than the simulated one due to extra losses which has been underestimated in EM simulations. The IIP3 of the circuit is highly degraded by the buffer and is measured at -24.8 dBm. However, the simulation of the LNA without the buffer shows an IIP3 of -14.8 dBm.

Fig. 6: Simulations and measurements of the S21 (a), NF (b), S11 (c) and S22 (d) of the circuit matched at 1 GHz

Measurements have been achieved at 3 different matching frequencies and are reported in TABLE III where performances are summarized and compared with state-of-the-art resistive feedback LNAs. This circuit shows good power efficiency and achieves a reduced power consumption while maintaining an acceptable trade-off between gain and noise figure. A figure of merit (*FoM*) is used to compare the overall performance of the LNAs and it is given by:

$$FoM = \frac{G_{v[lin]}}{(F_{[lin]} - 1)I_{[mA]}}$$

(20)

#### VI. CONCLUSION

This work presents a simple design method using a  $g_m/I_D$  approach suited for low power LNA in advanced technologies. It allows a fast and first-time right design of the LNA, based on a simple analytical study by using a compact model of the MOS transistor valid in all regions of operation. Thanks to this

method, the designer can choose the inversion level that guarantees a given gain while ensuring a target NF. The method is validated through a practical design in an advanced technology for which a time-consuming CAD-based approach is generally used. Measurements show a good agreement between analytical sizing and experimental results demonstrating the robustness of the method in an industrial framework. As discussed in the paper, the method allows the exploration of the design space which gives the maximum inversion level needed to achieve the target performances. Lower inversion levels could also be used with the risk of lowering the bandwidth. Improving this method to take into consideration the effect of  $i_f$  on the bandwidth could be an interesting extension of this work.

TABLE III. PERFORMANCE SUMMARY AND COMPARISON OF RF-LNA

| Ref  | Frequency | S11  | Gain  | NF   | IIP3   | I <sub>de</sub> | Technology | External | Area               | FoM   |

|------|-----------|------|-------|------|--------|-----------------|------------|----------|--------------------|-------|

|      | (GHz)     | (dB) | (dB)  | (dB) | (dBm)  | (mA)            | (nm)       | Comp.    | (mm <sup>2</sup> ) |       |

|      | 1         | <-   | 18    | 3.31 | -24.86 |                 |            | _        |                    | 12.2  |

| This |           | 20   |       |      | -14.8* | 0.57            |            |          |                    |       |

| work | 1.3       | <-   | 17.84 | 3.5  | -24.63 |                 | 28 FD-SOI  | Yes      | 0.07               | 11.04 |

|      |           | 10   |       |      | -14.8* |                 |            |          |                    |       |

|      | 1.8       | -18  | 17.44 | 3.85 | -24.48 |                 |            |          |                    | 9.16  |

|      |           |      |       |      | -14.8* |                 |            |          |                    |       |

| [9]  | 1.57      |      | 18    | 2.5- |        | 2.14-           | 28 FD-SOI  | Yes      |                    | 4.77  |

|      |           |      |       | 3.8  |        | 3.28            |            |          |                    | 1.73  |

| [10] | 0.9       | -    | 13.87 | 0.98 | -12    | 4.36            | 130 CMOS   | Yes      | 0.047              | 4.47  |

|      |           | 16.6 |       |      |        |                 |            |          |                    |       |

| [11] | 2.4       | -11  | 24    | 2    | -22.4  | 4               | 130 CMOS   | No       | 0.6                | 6.77  |

|      |           |      |       |      | -11*   |                 |            |          |                    |       |

|      | 2.4       | -11  | 29    | 1.2  | -21.5  | 3.5             | 130 CMOS   | Yes      | 0.6                | 25.3  |

|      |           |      |       |      | -11*   |                 |            |          |                    |       |

| [12] | 0.1-7     | <-   | 12.6  | 5.5- | -6     | 1.5             | 90 CMOS    | No       | 0.23               | 1.12  |

|      |           | 10   |       | 6.5  | -9     |                 |            |          |                    | 0.82  |

| [3]  | 0.2-6     | <-   | 17    | 3    | 7.9    | 3.36            | 28 FD-SOI  |          |                    | 2.11  |

|      |           | 10   |       |      |        |                 |            | No       | 0.005              |       |

|      | 0.2-3.9   | <-   | 15.7  | 3.1  | 8.7    | 2.75            | 65 CMOS    |          |                    | 2.13  |

|      |           | 10   |       |      |        |                 |            |          |                    |       |

|      | 0.1-2.1   | <-   | 19.2  | 2.4  | 8.6    | 2.38            | 130 CMOS   |          |                    | 5.18  |

|      |           | 10   |       |      |        |                 |            |          |                    |       |

\*LNA only

## REFERENCES

- A. Shameli and P. Heydari, "Ultra-low power RFIC design using moderately inverted MOSFETs: an analytical/experimental study", *IEEE RFIC Symposium*, 2006. pp. 521–524.

- [2] I. Song et al., "A Simple Figure of Merit of RF MOSFET for Low-Noise Amplifier Design", in *IEEE Electron Device Letters*, vol. 29, no. 12, pp. 1380-1382, Dec. 2008.

- [3] G. Guitton, et al., "Design Methodology Based on the Inversion Coefficient and its Application to Inductorless LNA Implementations", in *IEEE TCAS I*, vol. 66, no. 10, pp. 3653-3663, Oct. 2019.

- [4] R. Fiorelli et al., "MOST Moderate-Weak-Inversion Region as the Optimum Design Zone for CMOS 2.4-GHz CS-LNAs", in *IEEE MTT*, vol. 62, no. 3, pp. 556-566, March 2014.

[5] J. Liu et al., "A Methodology for the Design of Capacitive Feedback LNA

- [5] J. Liu et al., "A Methodology for the Design of Capacitive Feedback LNA based on the gm/ID Characteristic," in *IEEE NEWCAS 2018*.

- [6] C. Enz, et al., "Nanoscale MOSFET modeling, Part 2: Using the inversion coefficient as the primary design parameter", in *IEEE SSC Magazine*, vol. 9, no. 4, pp. 73-81, 2017.

- [7] B. J. Thijssen et al., " 2.4-GHz Highly Selective IoT Receiver Front End With Power Optimized LNTA, Frequency Divider, and Baseband Analog FIR Filter," in *IEEE JSSC*, 2020.

- [8] M. C. Schneider and C. Galup-Montoro, "CMOS Analog Design Using All-Region MOSFET Modeling", Cambridge University Press, 2010.

- 9] K. Yamamoto et al., "26.5 A 0.7V 1.5-to-2.3mW GNSS receiver with 2.5 to-3.8dB NF in 28nm FD-SOI", 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2016, pp. 444- 445

- [10] A. Thakur and S. Chatterjee, "A 4.4-mA ESD-Safe 900-MHz LNA With 0.9-dB Noise Figure," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 29, no. 2, pp. 297-306, Feb. 2021.

- [11] S. Joo, T. Choi and B. Jung, "A 2.4-GHz Resistive Feedback LNA in 0.13-μm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 44, no. 11, pp. 3019-3029, Nov. 2009

- [12] M. Parvizi, K. Allidina and M. N. El-Gamal, "A Sub-mW, Ultra-Low-Voltage, Wideband Low-Noise Amplifier Design Technique," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 6, pp. 1111-1122, June 2015.