# Low doping in-situ strategy leading to polysilicon based TFTs exhibiting high stability under stress effects and enhanced electrical performances

Mariem Zaghdoudi, Régis Rogel, Tayeb Mohammed-Brahim

## ▶ To cite this version:

Mariem Zaghdoudi, Régis Rogel, Tayeb Mohammed-Brahim. Low doping in-situ strategy leading to polysilicon based TFTs exhibiting high stability under stress effects and enhanced electrical performances. Materials Research Express, 2022, 9 (2), pp.026405. 10.1088/2053-1591/ac5276 . hal-03629629v2

# HAL Id: hal-03629629 https://hal.science/hal-03629629v2

Submitted on 4 Apr 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

### PAPER • OPEN ACCESS

Low doping *in-situ* strategy leading to polysilicon based TFTs exhibiting high stability under stress effects and enhanced electrical performances

To cite this article: Mariem Zaghdoudi et al 2022 Mater. Res. Express 9 026405

View the article online for updates and enhancements.

### You may also like

- <u>Singularities on toric fibrations</u> C. Birkar and Y. Chen

- <u>Threefold extremal curve germs with one</u> <u>non-Gorenstein point</u> S. Mori and Yu. G. Prokhorov

- <u>On quotient surfaces of P<sup>2</sup> by a finite</u> <u>group</u>

V A Alekseev and I Ya Kolpakov-Miroshnichenko

This content was downloaded from IP address 129.20.30.54 on 04/04/2022 at 13:45

## **Materials Research Express**

# CrossMark

**OPEN ACCESS**

**RECEIVED** 9 November 2021

**REVISED** 29 January 2022

ACCEPTED FOR PUBLICATION 7 February 2022

PUBLISHED 18 February 2022

Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence.

Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

Low doping *in-situ* strategy leading to polysilicon based TFTs exhibiting high stability under stress effects and enhanced electrical performances

#### Mariem Zaghdoudi<sup>1,2</sup>, Régis Rogel<sup>2</sup> and Tayeb Mohammed-Brahim<sup>2</sup>

Laboratory of Nanomaterials and Systems for Renewable Energies (LaNSER), Center of Energy, Borj-Cedria Science and Technology Park, BP 95,2050 Hammam-Lif, Tunisia

<sup>2</sup> IETR/ Groupe Microélectronique, 263 avenue du general Leclerc, 35042 Rennes cedex, France

E-mail: mariem.zaghdoudi@isste.rnu.tn

Keywords: TFTs, LPCVD, field effect mobility, stress effect

#### Abstract

PAPER

In the present work, we investigate the effect of low phosphorus doped polysilicon thin films. These later are deposited on glass substrates by low pressure chemical vapor Deposition (LPCVD) technique and are in situ doped with phosphine adjunction to silane. Doping levels are reported by the phosphine to silane ratio  $\Gamma$  varying from 0 (undoped layer) to heavily doped layer almost 1.2  $\times$  10<sup>-3</sup>. Films are characterized by different techniques as Photothermal Deflection Spectroscopy (PDS), photoluminescence measurements and x-ray diffraction of polycrystalline layers. The last one reveals that doping concentration giving modification in crystallite size and presence of microstrain, so a clear reduction in the Eg value was observed for the slightest doped layer ( $\Gamma = 3.7 \times 10^{-7}$ ) by comparaison with the undoped one (( $\Gamma = 0$ ). Results give evidence of an optimum doping level to obtain higher polysilicon films quality. Polysilicon film quality has been correlated to phosphorus doping levels. Thin film transistors (TFTs) are fabricated on glass substrate using a top gate four mask process at low temperature (<600 °C). Electrical characterizations highlight significant improvements in the TFTs performances using slightly doped film instead of undoped one as active layer. Based on Levinson's model, density of states within the grain boundaries is also found to be the lowest. Stability under stress is enhanced too. For slightly doped films, electrical characterizations indicate that both threshold voltage V<sub>th</sub> and density of states N<sub>T</sub> within the grain boundaries have their lowest values. Although, the field effect mobility  $\mu$  records its highest values. Additionally, low doping levels enhances the TFT stability under stress. As a result, the *in situ* low doping strategy opens the way to manufacture polysilicon electronic devices exhibiting high electrical performances and a rather high stability under stress effects.

#### 1. Introduction

Polycristalline silicon thin films are used in the low cost fabrication of large area electronic devices as active matrix flat panel displays [1, 2]. Devices performances are strongly correlated with polysilicon films quality because electrical properties are strongly affected by the presence of defects in polysilicon layers [3]. High quality polysilicon films can be obtained using different methods as laser annealing [4], metal induced lateral crystallization [5] or using disilane as gas source [6] in order to increase grain size.

So many study [7] shows that the properties of the annealed phosphorus n-doped silicon films are dependent on the crystallization method used SPC crystallization technique [8, 9], increasing the phosphorus content favors the crystallization process in terms of an enhancement of the crystal growth rate for SPC. Crystallization step was performed at 600 °C for several hours by a rapid thermal annealing [10] or by laser excimer annealing [11]. Wherein a laser can be used to minimize the heating of the glass substrate [12]. Poly-Si TFTs have a higher carrier mobility and higher driving current, this characteristic allow the increase of the response speed of the

pixels [13, 14]. The TFTs processing give the possibility to integrate display circuit directly on the glass substrate [8, 15].

Mariem *et al* [16] presented that optical and electrical characterizations show lower defect density in slightly doped samples compared to the undoped material. Phosphorus passivation of the defects can be involved to explain this decrease of the defect density by doping. Then the increase of the electrical conductivity in slightly doped polysilicon is not due to doping effect but to the passivation of defects.

An attractive and low cost method proposed in this paper can consist in *in situ* doping polysilicon films with very low phosphorous atoms content. We present here a new technique for improving quality of polysilicon active layer of TFTs and the TFTs performance by slight phosphorus doping.

#### 2. Material characterization

#### 2.1. Optical characterization

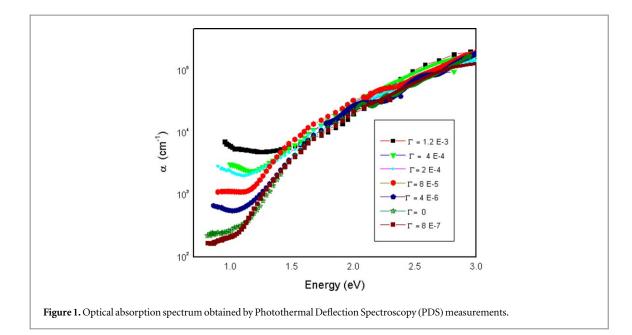

Silicon films are deposited by Low Pressure Chemical Vapor Deposition (LPCVD) on glass substrate capped with a 250 nm thick SiO<sub>2</sub> buffer layer. Films are deposited in an amorphous state at 550 °C and 90 Pa and are *in situ* doped using silane (SiH<sub>4</sub>) and phosphine (PH<sub>3</sub>) gases. Doping level is controlled by adjusting the phosphine on silane ratio  $\Gamma$  varying from 0 (undoped film) to  $1.2 \times 10^{-3}$  (highly doped film). Layers are then crystallized by solid phase crystallization performed at 600 °C under vacuum. Films are characterized using Photothermal Deflection Spectroscopy (PDS) technique to measure optical absorption in the range  $\alpha \leq 10^5$  cm<sup>-1</sup>. Photoluminescence measurements are also performed at 7 K using a liquid nitrogen cooled Ge detector. A krypton laser line (647 nm) with a power of 100 mW cm<sup>-2</sup> is used as the excitation source. Optical absorption spectrum obtained by Photothermal Deflection Spectroscopy (PDS) measurements is reported on figure 1. In the low energy region, results highlight a minimum value of the absorption coefficient for the slightest doped layer ( $\Gamma = 3.7 \times 10^{-7}$ ) compared to undoped ( $\Gamma = 0$ ) and Heavily doped films ( $\Gamma \ge 8 \times 10^{-6}$ ). Considering that defects in polysilicon are mainly located within grain boundaries, a decrease of their density can be correlated with a lower sub gap absorption coefficient. So, the trend observed can be interpreted as a decrease of the density of defects located deeply in the gap for a low phosphorus doping level. This result is the first evidence of a phosphorus passivation of defects.

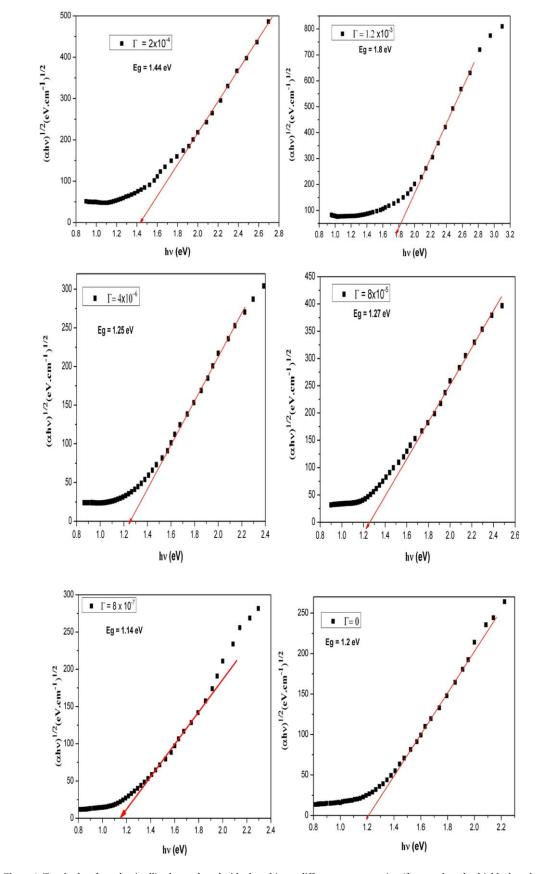

The graphs between ( $\alpha hv$ ) 1/2 and photon energy were plotted for all the samples as shown in figure 2

And results were confirmed by the calculation of the energy gap Eg for the polysilicon layers given above at differents concentration of phosphine. Optical band gaps of prepared polysilicon layers doped with phosphine have been estimated by using Tauc's relation given by the following equation:

$$(\alpha h \upsilon)^n = B(\alpha h - E_g)$$

Where *h* is the Planck's constant, v is the frequency (s-1) Eg is the optical energy band gap B is arbitrary constant, n is an index. For indirect band gap, the index is n = 2 [17].

The figure 3 shows the relation between  $(\alpha hv)^{1/2}$  for doped and slightly doped polysilicon layers with the photonic energy (hv).

Table 1. Numerical values of the optical gaps

obtained from the Tauc's plot.

| $\Gamma = \varphi \left( PH_3 \right) / \varphi (SiH_4)$ | Band gap (eV) |

|----------------------------------------------------------|---------------|

| $1.2 \times 10^{-3}$                                     | 1.80          |

| $2 \times 10^{-4}$                                       | 1.44          |

| $8 \times 10^{-5}$                                       | 1.27          |

| $4	imes10^{-6}$                                          | 1.25          |

| $8 \times 10^{-7}$                                       | 1.14          |

| 0                                                        | 1.20          |

The extrapolation of the curve to the value  $(\alpha h v)^{1/2} = 0$  can be used to determined the indirect band gap for the doped polysilicon samples.

The obtained results given in table 1 show a clear reduction in the Eg value for the slightest doped layer  $(\Gamma = 3.7 \times 10^{-7})$  by comparaison with the undoped one  $((\Gamma = 0)$ . The value increase with Heavily doped films  $(\Gamma \ge 4 \times 10^{-6})$  by increasing phosphorus dopant concentration. Ganesh Lal *et al* [18] showed a decrease of band gap energy with decreasing Zn concentration and Li doping in nanoferrites. On the contrary, K Kumari *et al* [19] and Kamal *et al* [20] observed that band gap decreases as the dopant concentration atom increase.where Eg increase from 1.20 for undoped to 1.80 eV for highly doped film  $(1.2 \times 10^{-3})$ .

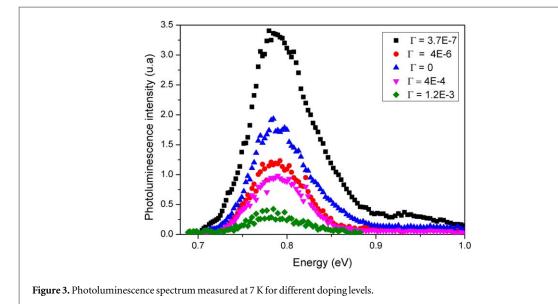

Photoluminescence spectrum for samples with different phosphorus doping levels is shown on figure 3. It gives evidence of an increase of the intensity peak at 0.78 eV from undoped layer to a maximum value obtained for a slightly doped layer, and then a decrease for high level doped layers. The deconvolution of this peak on several bands led to assume it as the D band, known in single crystalline silicon and attributed to the presence of dislocations within the material [21, 22]. Dislocations within grains in solid phase crystallized polysilicon are usually observed [23]. Based on Sauer's work [24], an increase of the intensity peak at 0.78 eV can be correlated to the relaxation of dislocations within grains. So, the maximum intensity of the peak reached for the slightly doped film indicates a better quality film. This trend correlates PDS measurements highlighting the passivation effect of a low doping level in polysilicon layers and the presence of an optimum doping level value. These results constitute an array of pieces of evidence for higher quality of slightly doped polysilicon films. Characterizations performed highlighted the beneficial effect of low phosphorus doping for the passivation of defects. As a result, TFTs are fabricated with different doping levels of the active layer to confirm these previous results.

#### 2.2. Structural analysis

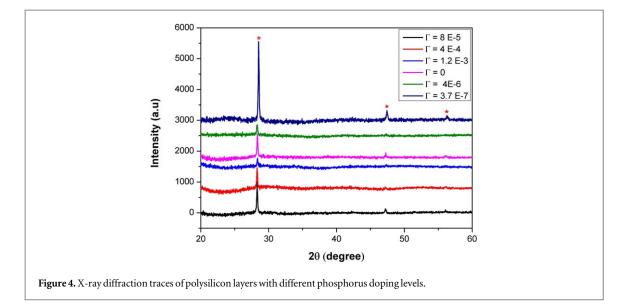

The x-ray diffraction traces of the layers are given in figure 3. Three peaks were observed at  $2\theta$  values of  $28.3^{\circ}$ ,  $47.42^{\circ}$  and  $56.3^{\circ}$ . These can be indexed respectively to the [[111], [220] and 311].

The broadening in the XRD peak is directly related with crystallite size through Debye-Sherer equation [25, 26].

Table 2. Details of crystallite polysilicon layers size and produced micro-strain for samples .

| $\Gamma = \varphi \left( PH_3 \right) / \varphi (SiH_4)$ | Crystallite size<br>(D) (nm) | Micro-strain (ε)<br>(x 10 <sup>-3</sup> ) |

|----------------------------------------------------------|------------------------------|-------------------------------------------|

| 4 E-4                                                    | 45.7                         | 3.20                                      |

| 8 E-5                                                    | 43.2                         | 3.10                                      |

| 4E-6                                                     | 36.0                         | 3.08                                      |

| 0                                                        | 35.8                         | 3                                         |

| 3.7E -7                                                  | 33.4                         | 2.8                                       |

$$D = \frac{k\lambda}{\beta\cos\theta} \tag{1}$$

Where k is a Scherer constant,  $\lambda$  is the wavelength of radiation used in according of XRD,  $\beta$  is the Full-Width at Half Maxima (FWHM) of particular XRD peak and  $\theta$  is the angular position of the particular XRD peak.

The contributions of crystallite size and strain are the properties of materials, which can be determined using OriginLab and excel sheet to find the following parameters from XRD data. The average crystallite sizes of these samples were estimated from the line width of the most intense and well resolved diffraction peaks using Scherrer formula. The calculated value of crystallite size and micro-strain for samples was given in table 2. The slightly doped sample 3.7E - 7 showed the lowest value of the crystallite size and the micro-strain by comparaison with the undoped and highly doped samples. It is noted that the micro-strain value of samples remains almost constant and no remarquable change was noticed.

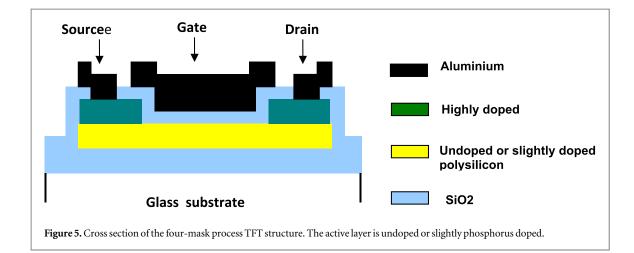

### 3. Devices

TFTs are fabricated through a four mask process at low temperature (<600 °C). First, a 250 nm thick SiO<sub>2</sub> buffer layer is deposited on glass substrate. Then, a 450 nm thick LPCVD amorphous silicon layer is deposited at 550 °C and 90 Pa with two different stacked regions: the lower region (300 nm thick) is slightly doped (or undoped) and the upper one (150 nm thick) is heavily phosphorus doped. Solid phase crystallization is then performed at 600 °C during 8 h. The heavily *in situ* doped layer is plasma etched to define the channel, source and drain regions. Then, a 70 nm thick silicon dioxide film is deposited by APCVD technique to be used as a gate dielectric layer. Source and drain contacts are opened by wet etching through gate insulator. Finally, 500 nm aluminium thick layer is thermally evaporated to form source, drain and gate contacts. Final structure is reported on figure 3.

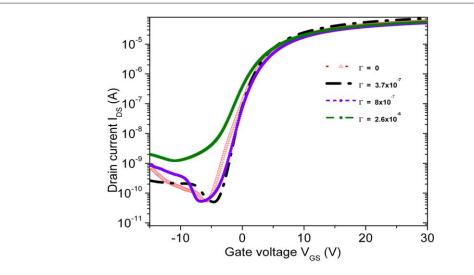

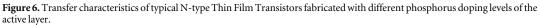

The transfer characteristics of N-type transistors with different phosphorus doping levels of the active layer are presented on figure 4. These characteristics are measured at room temperature using a HP 4155 B programmable parameter analyzer.

5

Table 3. Main electric parameters of the TFTs  $\frac{I_{on}}{I_{off}}$  ratio, field effect mobility  $\mu$ , threshold voltage  $V_{th}$  and subthreshold slope S for N-type TFTs fabricated with different doping levels  $\Gamma$ .

| $\Gamma = \varphi \left( PH_3 \right) / \varphi (SiH_4)$ | 0                 | $3.7 \times 10^{-7}$ | $8 \times 10^{-7}$ | $2.6 \times 10^{-6}$ |

|----------------------------------------------------------|-------------------|----------------------|--------------------|----------------------|

| $I_{on}/I_{off}$                                         | $7.5 \times 10^5$ | $6.8 \times 10^{5}$  | $1.7 \times 10^5$  | $2 \times 10^4$      |

| $\mu$ (cm <sup>2</sup> /V.s)<br>V <sub>th</sub> (V)      | 128<br>1.5        | 162<br>1.2           | 122<br>2           | 120<br>1.3           |

| S(V/dec)                                                 | 0.99              | 0.98                 | 1.23               | 2.2                  |

Table 4. Density of trap states within grain boundaries according to the Levinson's model.

| $\Gamma = \varphi(PH_3)/\varphi(SiH_4)$  | 0                 | $3.7 \times 10^{-7}$ | $8	imes10^{-7}$  | $2.6 \times 10^{-6}$ |

|------------------------------------------|-------------------|----------------------|------------------|----------------------|

| $N_{\rm T}({\rm cm}^{-2}.{\rm eV}^{-1})$ | $24\times10^{18}$ | $1-2 \times 10^{18}$ | $5\times10^{18}$ | $7\times10^{18}$     |

The main parameters extracted from these curves are reported in table 3. As we can see from table 3, the use of a slightly doped polysilicon film as active layer induces very significant improvements in the TFTs performances compared to classical TFTs made with an undoped active layer. Indeed, field effect mobility  $\mu$  exhibits a gain about 30% and a lower threshold voltage value is also obtained. From undoped to slightest doped layer,  $I_{on}/I_{off}$  ratio is quasi constant. With doping level increasing, polysilicon film conductivity increases inducing an efficient doping role for phosphorous atoms. As a consequence, the  $I_{on}/I_{off}$  ratio decreases. Using this simple and low cost method consisting in slightly doping polysilicon active layer, a very high mobility value can be obtained; reaching then the usual value obtained with LTPS (more expensive laser crystallization) TFTs.

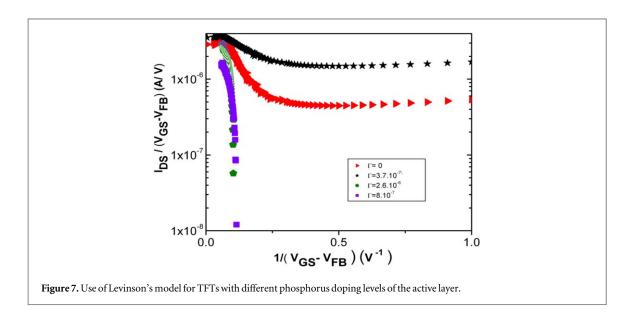

The high level mobility values obtained are due to the present process where both the active layer and the doped layer that constitutes the source and drain regions are deposited in the same run, removing the interface between active layer and source and drain regions [27]. Using Levinson's model [14], the drain current of the TFT can be expressed by the following equation (1):

$$I_{\rm DS} = \frac{W}{L} \mu_0 V_{\rm DS} C_{\rm ox} (V_{\rm GS} - V_{\rm th}) \exp\left(-\frac{q^3 N_{\rm T}^2 t}{8 \varepsilon K_{\rm B} T C_{\rm ox} (V_{\rm GS} - V_{\rm th})}\right)$$

(2)

Where W and L are width and length of the channel respectively,  $C_{ox}$  the surface oxide capacitance, e the channel thickness. This relation is valid when the electron concentration in the channel is greater than a critical concentration  $N^* = N_T L_G$  where  $N_T$  is the density of traps within grain boundaries and  $L_G$  the length of the grains. So, using a semi-logarithmic plot of the  $I_{DS}/(V_{GS} - V_{th})$  versus  $1/(V_{GS} - V_{th})$  we can obtain a linear function which slope is proportional to  $N_T$ . Results are shown on figure 5.

V<sub>th</sub> is defined at the minimum of the transfer characteristics. For each TFT, we can observe a linear behavior corresponding to the Levinson's model validity. As shown on figure 7, the linear region is more extended for TFTs with the slightest doped active layer and the slope is the lowest indicating a better material quality. Calculated values of the density of traps within grain boundaries are reported on table 4. Stress effect on the two types of TFTs (with an undoped active layer or the slightest phosphorus doped layer) was investigated.

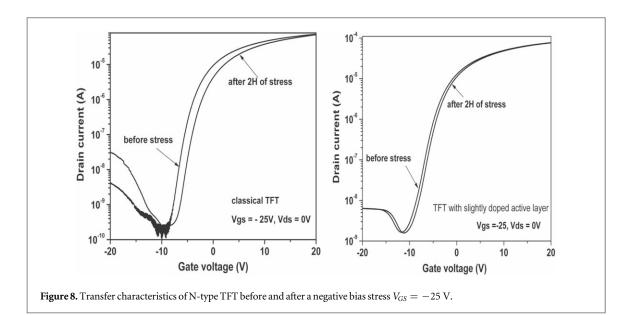

Figure 6 shows the transfer characteristics measured for a constant drain voltage  $V_{DS} = 1$  V before and after applying a negative stress bias  $V_{GS} = -25$  V during 2 h. The source and drain regions are short circuited during the gate bias stress in order to avoid any hot carrier effect. This stress induces a shift of the transfer characteristics for both types of TFTs. The gate bias stress may result in the state creation in the band gap of the channel material and at the  $Si - SiO_2$  interface, which is a disordered region [28]. As shown on figure 8, gate bias effect is strongly reduced when the active layer is slightly phosphorus doped.

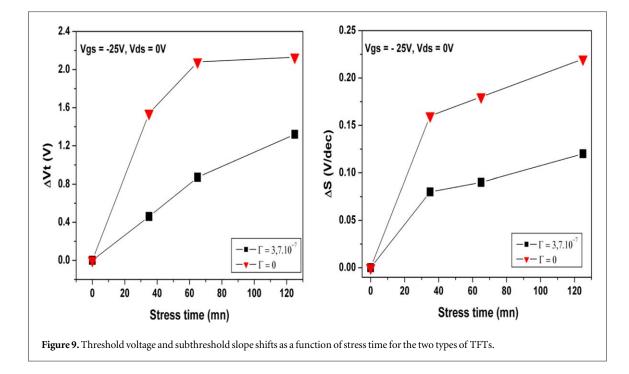

This trend may be explained by the higher polysilicon film quality obtained with slight phosphorous content. Better stability under stress is confirmed by the lower shift of the threshold voltage and the subthreshold slope for doped active layer TFT as shown on figure 9. This stress effect is another piece of evidence of the beneficial effect of a weak phosphorus doping function of stress time for the two types of TFTs.

#### 4. Conclusion

Effects of weak phosphorus doping in polysilicon layers were investigated. PDS and photoluminescence measurements highlighted the phosphorus passivation of defects giving evidence of an optimum doping level to obtain high quality polycrystalline silicon films. It is observed a clear reduction in the Eg value for the slightest doped layer ( $\Gamma = 3.7 \times 10^{-7}$ ) by comparaison with the undoped one ( $\Gamma = 0$ ). Two types of polysilicon TFTs were fabricated, with an undoped active layer and with a slightly phosphorus doped one. Electrical characterizations highlighted the beneficial effect of *in situ* doping the active layer. Optimal doping level induced high mobility ( $\geq 160 \text{ cm}^2 \text{ V}^{-1}.\text{s}^{-1}$ ) and a low threshold value. Stability under stress effect was also enhanced due to the higher quality of the *in situ* doped material. These enhancements gave evidence that control of weak phosphorus doping in polysilicon films is a new simple way to improve polysilicon based devices.

#### Data availability statement

All data that support the findings of this study are included within the article (and any supplementary files).

### **ORCID** iDs

Mariem Zaghdoudi https://orcid.org/0000-0001-8245-7407

#### References

[1] Matsuo T and Muramatsu T 2004 Proc. SID Int. Symp. 856-8

[2] Oana Y 1989 Technical developments and trends in a-Si TFT-LCDs J. Non-Cryst. Solids 115 27-32

- [3] Zaghdoudi M, Abdelkrim M M, Fathallah M, Mohamed-Brahim T and Rogel R 2006 Materials Science and Engineering 26 177-80

- [4] Despina C, Exarchos M A, Kouvatsos D N, Papaioannou G J and Voutsas A T 2008 Microelec. Eng. 85 1447–52

- [5] Jagar S, Chan M, Wang H, Poon V M C and Myasnikov A M 2001 Solid State Elect. 45 743–9

- [6] Rogel R, Gautier G, Coulon N, Sarret M and Bonnaud O 2003 Thin Solid Film 427 108–12

- [7] Pierson J F, Kim K S, Jolly J and Mencaraglia D 2000 J. Non-Cryst. Solids 270 91-6

- [8] Yoneda K, Yokoyama R and Yamada T 2001 Development trends of LTPS TFT LCDs for mobile applications Proc. VLSI Symp. Circuit. Dig. (Kyoto, Japan) 85–90

- [9] Little T W et al 1991 Low temperature poly-Si TFTs using solid phase crystallization of very thin films and an electron cyclotron resonance chemical vapor deposition gate insulator Jpn. J. Appl. Phys. 30 3724–8

- [10] Plais F et al 1995 Low temperature polysilicon TFTs: a comparsion of solid phase and laser crystallization Microelectron. Eng. 28 443-6

- [11] Girginoudi S, Girginoudi D, Thanailakis A, Georgoulas N and Papaioannou V 1998 Electrical and structural properties of poly-Si films grown by furnace and rapid thermal annealing of amorphous Si J. Appl. Phys. 84 1968–72

- [12] Kohno A, Sameshima T, Sano N, Sekiya M and Hara M 1995 High performance poly-Si TFTs fabricated using pulsed laser annealing and remote plasma CVD with low temperature processing IEEE Trans. Electron Devices 42 251–7

- [13] Brotherton S D et al 2003 High-speed, short-channel polycrystalline silicon thin-film transistors Appl. Phys. Lett. 84 293-5

- [14] Levinson J et al 1982 Conductivity behavior in polycrystalline semiconductor thin film transistors J. Appl. Phys. 53 1193–202

- [15] Nakajima Y, Kida Y, Murase M, Toyoshima Y and Maki Y 2004 Latest development of system-on-glass display with low temperature poly-Si TFT Proc. SID Int. Symp. Dig. Tech. Papers 864–7

- [16] Zaghdoudi M et al 2005 Mater. Sci. Forum 480-481 305-8

- [17] Khare P K and Bull S K J 2000 Mater. Sci. 23 17

- [18] Lal G, Punia K, Narain Dolia S, Alvi P A, Choudhary B L and Kumar S 2020 J. of Alloys and Compounds 828 154388

- [19] Kumari K, Aljawfi R N, Vij A, Chea K H, Hashim M, Alvi P A and Kumar S 2019 J. of Mat. Science, Mat in Elect 30

- [20] Khichar K K et al 2020 Polymer. Composites 41 2792-802

- [21] Fitzgerald E A, Curie M T, Samavedam S B, Langdo T A, Taraschi G, Yang V, Leitz C W and Bulsara M T 1999 Phys. Sta. Solid. 171 199

- [22] Giggs V, Lightowlers E C, Xie Y H and Silverman P J 1993 J. Appl. Phys. 73 1948–52

- [23] Stoemenos J, Economou H A, Haji L, Bonnel M, Duhamel N and Loisel B 1994 Sol. State phenom 37-38 287–90

- [24] Saurer R, Weber J, Stolz J, Weber E R, Kusterand K H and Alexander H 1985 App. Phys. Lett. 36

- [25] Kaushik A, Dalela B, Rathore R, Vats V S, Chaudhary B L, Alvi P A, Kumar S, Dalela S and Alloys J 2013 Compd 578 328

- [26] Kumara S, Sharma M, Aljawfi R N, Chae K H, Kumar R, Dalela S, Alshoaibi A, Ahmed F and Alvi P A 2020 J. Electron. Spectrosc. Relat. Phenom. 240 146934

- [27] Pichon L, Mourgues K, Raoult F, Mohammed-Brahim T, Kis-Sion K, Briand D and Bonnaud O 2001 Semicond. Sci. Technol. 16918-24

- [28] Tala-Ighil B, Rahal A, Mourgues K, Toutah A, Pichon L, Mohammed-Brahim T, Raoult F and Bonnaud O 1999 Thin solid Film 337 101–4