## Software Defined Radio Platforms for Wireless Technologies

Dereje M. Molla, Hakim Badis, Laurent George, Marion Berbineau

### ▶ To cite this version:

Dereje M. Molla, Hakim Badis, Laurent George, Marion Berbineau. Software Defined Radio Platforms for Wireless Technologies. IEEE Access, 2022, pp1-27. 10.1109/ACCESS.2022.3154364 . hal-03592937

### HAL Id: hal-03592937 https://hal.science/hal-03592937v1

Submitted on 1 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier xx.xxxx/ACCESS.xxxx.xxx

# Software Defined Radio Platforms for Wireless Technologies

### DEREJE M. MOLLA<sup>1</sup><sup>(0)</sup>, HAKIM BADIS<sup>1</sup><sup>(0)</sup>, LAURENT GEORGE<sup>1</sup><sup>(0)</sup>, AND MARION BERBINEAU<sup>2</sup><sup>(0)</sup>

<sup>1</sup>LIGM, ESIEE Paris, Gustave Eiffel University, CNRS, F-77454 Marne-la-Vallée, France (e-mail: dereje.molla@esiee.fr, hakim.badis@univ-eiffel.fr, laurent.george@esiee.fr)

<sup>2</sup>COSYS Department, Gustave Eiffel University, France (e-mail: marion.berbineau@univ-eiffel.fr)

Corresponding author: Dereje M. MOLLA (e-mail: dereje.molla@esiee.fr).

The authors acknowledge funding from I-Site Future in the framework of the Western project. One of the authors acknowledge partial funding by the regional project SMARTIES in the framework of the ELSAT 2020 program co-financed by the European Union with the European Regional development fund, the French state and Hauts de France Regional council.

ABSTRACT Wireless connectivity standards have been developed to meet the requirements of various applications. To support a wireless standard, a wireless transceiver should be equipped with a Radio Frequency (RF) transceiver. Traditional RF transceivers are designed and implemented on a radio chip or an embedded module in a System-on-a-Chip (SoC), ensuring small size, high performance, low power consumption, and cost. However, this traditional implementation design limits directly or indirectly the programmability and flexibility of the RF transceivers. An alternative solution is to implement RF transceivers using Software Defined Radio (SDR) platforms. In the market, SDR platform hardware exists with different configurations, performance, cost, size, etc., making it hard to select the minimum SDR platform necessary to satisfy the wireless standard requirements. This paper aims to provide a list of wellknown General Purpose Processor (GPP) based SDR platforms satisfying the minimum specifications of selected wireless standards. To this end, we first review the characteristics of selected wireless technologies. Then, we investigate existing SDR platform architecture and their maximal performance in terms of the frequency range, bandwidth, symbol rate, bitrate, and latency support. Finally, we intersect the wireless standard requirements with the corresponding SDR platform parameters and provide a list of GPP-based SDR platforms for some existing wireless technology implementations. While investigations related to frequency, bandwidth, symbol rate and bitrate are supported by theoretical results, latency is obtained from experiments by benchmarking existing implementations.

**INDEX TERMS** General Purpose Processor, Software Defined Radio, Transceivers, Wireless Technologies.

### I. INTRODUCTION

THE number of wireless devices used by various wireless application domains such as Wireless Sensor Networks (WSNs) [1], Internet of Things (IoT) [2], cellular base stations [3], etc., has increased tremendously in the past decade. Several wireless technologies are standardized to enable the interconnection between the different wireless devices including NFC, RFID, IEEE 802.15x, IEEE 802.11x, LoRa, Sigfox, 3GPP 3G/4G/5G, etc., [3]–[5]. A wireless device can incorporate one or multiple wireless transceivers supporting distinct wireless technologies. Each transceiver performs all the physical (PHY) and a portion of the Media Access Control (MAC) layer operations through integrated analog and digital circuit blocks. Indeed, most of the PHY layer analog operations are implemented on a dedicated and integrated analog hardware such as amplifiers, radio frequency (RF) synthesizers, filters, etc. On the other hand, some PHY layer digital baseband and time critical MAC layer functions are fully implemented on a digital hardware such as Application Specific Integrated Circuits (ASICs), a Programmable Digital Signal Processor (PDSP), Application Specific Instruction Set DSP (DSP ASIP) or a mixed solution using ASIC hardware accelerators with PDSP or with DSP ASIP [6]. This traditional implementation considerably limits directly or indirectly the programmability and flexibility of the transceivers for upgrading or handling multiple wireless standards. Moreover, processors of wireless transceivers are mostly proprietary which prevent programmers and researchers from access to reprogram the instruction code.

An alternative solution to allow programmers and researchers to easily control the hardware and program the software of wireless transceivers is to use an implementation based on general-purpose processor (GPP) based Software Defined Radio (SDR) platforms, which is a reconfigurable and reprogrammable radio transceiver. In such platforms, the PHY layer digital baseband and MAC layer operations are implemented on a GPP, and the PHY layer analog RF/IF front-end operations are controlled using an analog device board supporting a wide range radio spectrum. This solution have been explored by many researchers to investigate the architecture, challenges and compare the performance of several SDR platforms [7]-[9]. In addition, as the PHY and MAC layers are performed in software by GPP host and due to the reconfigurability and reprogrammability of the radio transceiver, the SDR platform can be used to implement multiple wireless technologies. Such benefit has been exploited in many recent research works such as [10], [11]. These benefits conjugated with the continuous advancement in processing performance (hardware and software) and decreasing price of GPPs made GPP-based SDR platforms gain much attention for implementing and testing wireless technologies [12]-[16]. Moreover, it is also used to build testbeds and/or perform experimentation to study different features of communication systems and suggest performance improvement [17]-[19].

Currently, several SDR platforms are available in the market and research community. To implement a desired wireless technology, an appropriate SDR platform need to be selected. Previous research works such as [7] and [9] have presented the challenges during SDR platform selection process and compared the performance of SDR platforms in the general context. However, they abstain from addressing the specific considerations required by SDR platforms based on the requirement of wireless technologies. This problem is slightly addressed by other researchers and developers in two different perspectives, by designing a custom SDR architecture suited to a specific implementation such as [20]-[22], and/or providing list of recommended requirements to implement a certain wireless technology. Regarding the latter case, the recommendations are usually provided by SDR platform software implementations such as Software Radio Systems (SRS) [14], OpenAirInterface Software (OAI) [23], gr-IEEE-802.15.4 [15], gr-LoRa [24], etc. However, these recommendations are essentially formulated after multiple experimental tests. Nevertheless, as the experimental tests are not exhaustive, the recommended SDR platforms may be over-dimensioned and thus the minimal necessary configuration (carrier frequency and bandwidth, clock rate, communication interface support, GPP cores, GPP processing power, software architecture, etc.), can be exceeded.

The aim of this paper is to provide a list of possible GPPbased SDR platforms in terms of hardware components satisfying the minimum specifications of well-known wireless technologies. This is achieved by analyzing what a wireless technology requires at minimum in terms of frequency range, bandwidth, symbol rate, bitrate and latency, and the performance offered by GPP-based SDR platform components. The contributions of this paper can be summarized as:

- we present a detailed study of the architecture of GPPbased SDR platforms, and analyze their capabilities in terms of the performance metrics;

- we drive the minimum performance requirements of the most relevant wireless technologies. We use these requirements to draw mapping conditions in order to determine which GPP-based SDR platform is appropriate to successfully perform a targeted wireless technology;

- we identify existing wireless technology implementations from the literature that use GPP-based SDR platforms, examine their performance metrics, and suggest a list of other possible SDR platforms to implement the use-cases described in the literature.

Thus, the in-depth analysis of selected wireless technologies and SDR platforms allows researchers from both academia and industry to easily understand required parameters, software and hardware components of SDR platforms. We believe this paper will help researchers (SDR platform users and SDR software developers) looking for the appropriate SDR platform to implement a given wireless technology. To the best of our knowledge, this paper is the first to perform mapping several wireless technologies with GPP-based SDR platforms.

This paper is organized as follows: Section II provides classification and characteristics of well-known wireless connectivity technologies. Section III discusses the architecture of GPP-based SDR platforms and provides general background on the hardware and software components. Section IV provides a detailed study on the performance parameters of GPP-based SDR platforms and presents numerical results using selected GPP-based SDR platforms. Section V presents a mapping between SDR platform performance and wireless technology requirements. Open research challenges and future directions are given in section VI. Finally, section VII provides conclusions to this paper.

### **II. WIRELESS CONNECTIVITY TECHNOLOGIES**

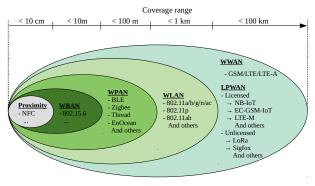

The interconnection between different wireless devices is enabled by a wide range of wireless technologies that can cover from very short distance (in centimeter range) to several kilometers. Thus, wireless connectivity technologies can mainly be classified into three groups based on the range they cover [25]: i) short-range wireless technologies, ii) Wireless Local Area Networks (WLANs), and iii) Wireless Wide Area Networks (WWANs). Within each of these categories, several wireless technologies are standardized, as shown in Fig. 1. The subsequent subsections present the main PHY and MAC layer characteristics of major wireless technologies. We note that, the frequency requirement of wireless technologies stated in the tables is given based on their standard. However,

IEEE Access<sup>•</sup>

the specific frequency band used by a wireless technology depends on its allocation for global and regional use and also countries regulation [26].

FIGURE 1: Wireless technologies.

### A. SHORT-RANGE WIRELESS TECHNOLOGIES

Short-range wireless technologies include proximity communication, Wireless Body Area Networks (WBANs) and Wireless Personal Area Networks (WPANs). They are mainly characterized by their short-range coverage operating under the unlicensed industrial, scientific and medical (ISM) frequency bands. International Organization for Standardization(ISO)/International Electrotechnical Commission (IEC) defines the PHY and MAC layer requirements for proximity technologies, and IEEE defines for WBAN and WPANs. Some of the most prominent wireless technologies are Near Field Communication (NFC), Radio Frequency Identification (RFID), IEEE 802.15.6 (NB PHY, UWB PHY and HBC PHY), IEEE 802.15.1, and IEEE 802.15.4. IEEE also defines the PHY and MAC layer for Low-Rate WPAN to meet the limited resource requirement of IoT and WSN devices. Among these standards are IEEE 802.15.4 and Bluetooth Low Energy (BLE), which are developed for networks with low power consumption, low deployment cost and less complexity. Table 1 gives the PHY and MAC layer characteristics of some of the short-range wireless technologies.

### B. WIRELESS LOCAL AREA NETWORK - WLAN

WLAN is mostly designed for wireless connectivity covering less than one kilometer range. Different standards falling under this group include IEEE 802.11b, IEEE 802.11a/g, IEEE 802.11n, IEEE 802.11ac/ax, IEEE 802.11ah and IEEE 802.11p. The first four standards (IEEE 802.11a/b/g/n/ac) are the most popular wireless standards used by WiFi [32], [33]. They are high bandwidth technologies that supports the communication of bandwidth-intensive applications like streaming video, and enable wireless gateways with a highspeed interface to relay traffics requiring large bandwidth and IP connectivity [34]. Other standards promising for IoT and WSN deployment due to their low power and long range wireless communication support are IEEE 802.11ah (WiFi-HaLoW) [35] and IEEE 802.11p [36]. IEEE 802.11ah defines PHY and MAC layer specification for large scale sensor networks and extended range hotspot. It operates in the sub-GHz ISM bands. IEEE 802.11p is an amendment of 802.11 standard that operates in the 5.9 GHz band and offer wireless connectivity between mobile vehicles (and/or vehicles and roadside units) and designed to guarantee low latency [36]. Table 2 enlists their PHY and MAC layer characteristics.

### C. WIRELESS WIDE AREA NETWORK - WWAN

WWANs are meant for large area coverage in the order of kilometers. The wireless communication technologies standardized for such wide coverage have mainly two groups: cellular networks such as 2G, 3G, 4G and 5G; and Low Power Wide Area Networks (LP-WANs). The latter also has two groups: licensed and unlicensed. The licensed LP-WAN consists of Narrow-Band IoT (NB-IoT), Enhanced Coverage-GSM IoT (EC-GSM-IoT) and Long Term Evolution for Machine Type Communication (LTE-M). They are upgrades of cellular communication technologies for IoT applications.

TABLE 1: Characteristics of short-range wireless technologies.

| Standards                                |                                           |                                   | PH                            | IY layer                                                        |                     |                                                                         | MAC layer                                          |                             |

|------------------------------------------|-------------------------------------------|-----------------------------------|-------------------------------|-----------------------------------------------------------------|---------------------|-------------------------------------------------------------------------|----------------------------------------------------|-----------------------------|

|                                          | Frequency<br>Band (MHz)                   | Channel size<br>(Bandwidth (MHz)) | Max. symbol<br>rate (MSym/s)  | Modulation<br>Bit-to-Sym mapper                                 | Subcarriers         | Max. bitrate<br>(kbit/s)                                                | Latency (ms)                                       | Access scheme               |

| ISO/IEC 18092:2013<br>(NFC) [27]         | 13.56                                     | 1                                 | 0.106, 0.424,<br>1.696        | ASK (OOK) FSK                                                   | 1                   | 106, 212, 424                                                           | 5.340                                              | Electromagnetic<br>coupling |

| ISO/IEC 18000 (JTC1<br>SC31) (RFID) [28] | 0.125,13.5,433,<br>subGHz,<br>2.4G, UWB   | 10, 14, 1.74, 7, 8                | -                             | BPSK                                                            | 1                   | 640                                                                     |                                                    | FDMA/TDMA                   |

| NB PHY [29]                              | 0.4 - 2.4                                 | 0.3, 0.32, 0.4, 1                 | 0.6                           | DBPSK, $\pi/4$ -DQPSK, $\pi/8$ -D8PSK, GMSK                     | 1                   | 0.0759 - 0.9714                                                         | pSIFS*= 75                                         | CSMA/CA,<br>slotted ALOHA   |

| UWB PHY (IR-UWB,<br>FM-UWB) [29]         | 3.493 - 9.984                             | 499.2                             | 15.6                          | On-OFF modulation,<br>BPSK/QPSK, CP-BFSK,<br>WB-FM, DBPSK/DQPSK | 1                   | 15.6                                                                    | pSIFS = 75                                         | CSMA/CA,<br>slotted ALOHA   |

| HBC PHY [29]                             | 0.021                                     | 5.25                              | 0.328                         | Based on NFC (OOK, DSSS)                                        | 1                   | 1.3125                                                                  | pSIFS = 75                                         | CSMA/CA,<br>slotted ALOHA   |

| IEEE 802.15.1 [30]                       | 2.4G                                      | 1, 2                              | 2                             | FHSS based GFSK,<br>DQPSK                                       | 1                   | 2000                                                                    | IFS = 150                                          | TDMA                        |

|                                          |                                           |                                   |                               |                                                                 |                     |                                                                         | aTurnaroundTime = 192;<br>macAckWaitDuration = 864 | Unslotted<br>CSMA/CA        |

| IEEE 802.15.4 [31]                       | sub-GHz<br>and 2.4G 0.4, 0.6, 2, 5 0.0625 | 0.0625                            | 25 DSSS based BPSK,<br>O-QPSK |                                                                 | 20, 40, 100,<br>250 | aTurnaroundTime = 192;<br>aTurnaroundTime +<br>aUnitBackoffPeriod = 512 | Slotted<br>CSMA/CA                                 |                             |

|                                          |                                           |                                   |                               |                                                                 |                     |                                                                         | macTsTxAckDelay = 1000                             | GTS allocation              |

SIFS: Short Inter-Frame Space.

VOLUME x, xxxx

| Standards        |             |                   |                        | PHY layer     |                       |             |              | MAC layer          |         |

|------------------|-------------|-------------------|------------------------|---------------|-----------------------|-------------|--------------|--------------------|---------|

|                  | Frequency   | Channel size      | Symbol duration        | Max. symbol   | Modulation            |             | Max. bitrate | Latency (µs)       | Access  |

|                  | Band (GHz)  | (Bandwidth (MHz)) | + GI <sup>*</sup> (µs) | rate (kSym/s) | Bit-to-Symbol mapper  | Subcarriers | (Mbit/s)     | Latency ( $\mu$ s) | scheme  |

| IEEE802.11b [32] | 2.4         | 22                | 0.7273                 | 1375          | CCK,QPSK              | 1           | 11           | SIFS = 10; ACK     | CSMA/CA |

|                  |             |                   |                        |               |                       |             |              | timeout = 30       |         |

| IEEE802.11a/g    | 5/2.4       | 20                | 4                      | 250           | BPSK,QPSK, (16,64)QAM | 52          | 54           | SIFS=16/10;        | CSMA/CA |

| [32]             |             |                   |                        |               |                       |             |              | ACK timeout =      |         |

|                  |             |                   |                        |               |                       |             |              | 25/19              |         |

| IEEE802.11n [32] | 2.4/5       | 20/40             | 4                      | 250           | BPSK,QPSK, (16,64)QAM | 56/114      | 72.2, 150    | SIFS = 10; ACK     | CSMA/CA |

|                  |             |                   |                        |               |                       |             |              | timeout = 19       |         |

| IEEE802.11ac     | 5           | 20/40/80/160      | 4                      | 250           | BPSK,QPSK, (16, 64,   | 56/114/242/ | 86.7 - 6000  | SIFS = 16; ACK     | CSMA/CA |

| [33]             |             |                   |                        |               | 256)QAM               | 484         |              | timeout = $25$     |         |

| IEEE802.11ah     | subGHz (0.7 | 1/2/4/8/16        | 40                     | 25            | BPSK,QPSK, (16, 64,   | 32/56/114/  | 0.1 – 347    | SIFS = 160         | CSMA/CA |

| [35]             | - 0.9)      |                   |                        |               | 256)QAM               | 242/484     |              |                    |         |

| IEEE802.11p [36] | 5.8/5.9     | 10                | 8                      | 125           | BPSK,QPSK, (16,64)QAM | 52          | 3 – 27       | SIFS = 32          | CSMA/CA |

### TABLE 2: Characteristics of WLAN standards.

GI is long Guard Interval (8 $\mu$ s for 802.11ah, 1.6 $\mu$ s for 802.11p and 0.8 $\mu$ s for others).

TABLE 3: Characteristics of WWAN standards.

|          | Standards |                    |                   |                 | PHY layer     |                   |               |              | MAC layer   |                 |

|----------|-----------|--------------------|-------------------|-----------------|---------------|-------------------|---------------|--------------|-------------|-----------------|

|          |           | Frequency Band     | Channel size      | Symbol duration | Max. symbol   | Modulat           | ion           | Max. bitrate | Latency     | Access scheme   |

|          |           | (MHz)              | (Bandwidth (MHz)) | + GI (µs)       | rate (kSym/s) | Bit-to-Sym mapper | Subcarriers** | (bit/s)      | (ms)        | Access scheme   |

|          | GSM/      | 800/900, 1800/1900 | 0.2               | 3.69            | 271           | GMSK, QPSK,       | 1             | 171k (GPRS), | slot time   | TDMA/FDMA       |

| Cellular |           |                    |                   |                 |               | 8PSK, 16QAM       |               | 384k(EDGE)   | = 0.577     |                 |

| Centular | 3GPP LTE  | LTE bands [40]     | 1.4,3,5,10,15,20  | 66.66           | 15            | QPSK, 16QAM,      | 73/181/301/   | 50.42M (UL), | 4           | SC-FDMA,        |

|          |           |                    |                   |                 |               | 64QAM             | 601/901/1201  | 100.8M (DL)  |             | OFDMA           |

|          | NB-IoT    | LTE bands          | 0.18              | 66.66           | 15            | BPSK, QPSK,       | 12            | 250k         | 20          | SC-FDMA/ FDMA,  |

| Cellular | [41]      |                    |                   |                 |               | 16QAM             |               |              |             | OFDMA           |

| for IoT  | EC-GSM-   | GSM bands          | 0.20              | 3.69            | 271           | GMSK, 8PSK        | 1             | 240k         | slot time   | TDMA            |

| 101 101  | IoT       |                    |                   |                 |               |                   |               |              | = 0.577     |                 |

|          | LTE-M     | LTE bands          | 1.4               | 66.66           | 15            | QPSK, 16QAM       | 73            | 1M           | end-end     | SC-FDMA,        |

|          |           |                    |                   |                 |               |                   |               |              | = 100       | OFDMA           |

|          | LoRa®     | 433/868(EU),       | 0.125,0.25,0.5    | 1024,512,256    | 3.91          | LoRa, FSK         | 1             | 50k          | 24          | Proprietary CSS |

| LP-WAN   |           | 915(US), 430(Asia) |                   |                 |               |                   |               |              |             |                 |

| LI-WAIN  | Sigfox    | 868(EU), 902(US)   | 0.0001(UL),       | 10,000/60,000   | 0.1, 0.6      | DBPSK(UL),        | 1             | 100(UL),     | $\sim 2000$ | Proprietary     |

|          |           |                    | 0.0006(DL)        |                 |               | GFSK(DL)          |               | 600(DL)      |             | UNB/FHSS        |

Spreading factor (SF) = 7. \*\* Subcarriers are shown only for the downlink.

Unlicensed LP-WAN includes Long Range (LoRa), Sigfox, etc., [37]. LP-WAN technologies are designed for Machine-to-Machine (M2M) and IoT applications that need to forward small payload data at low data rate and low power consumption [38], [39]. The cellular technologies (2G, 3G, and 4G), on the other hand, consume a lot of device energy which may cause a negative impact on low-power IoT devices. However, they are useful for IoT gateways or IoT devices running bandwidth-intensive applications. Table 3 quantifies the requirements of cellular and LP-WAN technologies.

### **III. GPP-BASED SDR PLATFORM ARCHITECTURE**

The implementation design of conventional wireless transceivers, in general, lacks reprogrammability, flexibility and scalability. Therefore, upgrading the software, changing the logic of the dedicated hardware or reusing the transceiver to implement a wireless standard other than the one the transceiver was designed for is limited or non-existent. Moreover, conventional wireless transceivers are mostly proprietary which prevent developers and researchers from access to reprogram the assembly instruction set. An alternative solution to mitigate these limitation is using SDR platforms. In addition to the programmability feature, the SDR platform also serve as a multi-technology gateway by performing multiple wireless technologies using a common set of radio transceiver [10], [11]. It also allows to reuse software across multiple radio devices and download software over-the-air to implement new standards and fix bugs [8]. Furthermore, it is

recently being used to mitigate cross-technology interference problem faced by conventional technologies [42].

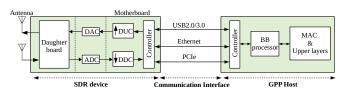

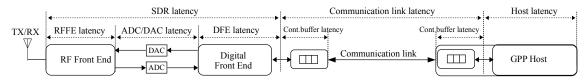

An SDR platform is a class of radio transceivers which controls the analog RF/IF part using an open-source analog device board, named SDR device, and implements all the digital part using programmable host processor. The programmable host processor can be GPP, DSP ASIP or FPGA. The scope of our study is limited to GPP-based SDR platforms due to its easy programmability using a high-level language and its flexibility for reconfiguration and handling complex algorithms [9]. The general architecture of GPP-based SDR platform is illustrated in Fig. 2. It is mainly sectioned into three parts as **SDR device**, **communication interface** and **GPP host**. Each component of the platform has its communication parameters that contribute to the overall performance of the SDR platform. This section investigates the GPP-based SDR platform.

FIGURE 2: GPP-based SDR platform general architecture.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2022.3154364, IEEE Access

D.M. Molla et al.: Software Defined Radio Platforms for Wireless Technologies

### A. SDR DEVICE

An SDR device is a small handheld type of device which is capable of transmitting and receiving signals at different frequencies. It typically consists of software controllable analog RF/IF and digital IF front-ends. The former is called as daughterboard and the latter as motherboard. This subsection describes their respective tasks and characteristics.

### 1) Daughterboard

The daughterboard is essentially responsible to perform analog RF/IF processing functions such as filtering, amplification, conversion of signals from RF to IF and vice-versa, etc. It is mainly characterized by the frequency band it covers, the analog bandwidth, RF performance, number of channels, channel's capability (only RX or TX/RX), mode of operation as a half (HD) or full (FD) duplex, etc. Mainly, the operating frequency range, width of analog bandwidth and channel's capability determines the scope of the daughterboard to implement a wide range of wireless technologies using SDR device. The daughterboard interfaces the antenna with the motherboard. Indeed, most daughterboards integrate multiple input/output circuits to connect multiple separated antennas enabling simultaneous transmission and reception capability [43], [44]. Also, daughterboards integrate analog inputs/outputs to connect motherboard ADCs and DACs. In the market, daughterboards are either stand-alone component or integrated with a motherboard forming a single board. Table 4 lists few commercially available daughterboards.

TABLE 4: List of selected daughterboards.

| Daughterboard        | Frequency<br>Band (MHz) | Bandwidth<br>(MHz) | TX/Rx/Mode | Туре        | SDR family     |

|----------------------|-------------------------|--------------------|------------|-------------|----------------|

| UBX                  | 10-6000                 | 40/160             | Tx/Rx/FD   |             |                |

| CBX                  | 1200 - 6000             | 40/120             | Tx/Rx/FD   | Stand-alone |                |

| SBX                  | 400 - 4400              | 40/120             | Tx/Rx/FD   | Stand-atone |                |

| WBX                  | 50 - 2200               | 40/120             | Tx/Rx/FD   |             | USRP [43]      |

| B210                 | 70 - 6000               | 56                 | Tx/Rx/FD   | Integrated  | 1              |

| HackRF FE [45]       | 1 - 6000                | 20                 | TX/RX/HD   | Integrated  | HackRF         |

| WARP Radio RF [46]   | 2400-2500,              | 40                 | TX/RX/FD   | Stand-alone | Used by Sora   |

|                      | 4900-5875               |                    |            |             | -              |

| LMS7002M FPRF [47]   | 0.1 - 3800              | 60                 | Tx/Rx/FD   | Integrated  | LimeSDR        |

| AD-FMCOMMS2-EBZ [44] | 70 - 6000               | 56                 | Tx/Rx/FD   | Integrated  | Analog Devices |

### 2) Motherboard

Motherboard is mainly responsible to perform digitization, channelization and sample rate conversion (digital up/down conversion [DUC/DDC]). To achieve these operations, motherboards integrate ADCs/DACs and a DSP processor that can be implemented using ASIC, DSP ASIP or FPGA. It also integrates one or more communication interfaces to connect with GPP host. It is mainly characterized by the maximum ADC and DAC sample rates, ADC and DAC resolution, DSP processor design and the supported communication interface. Table 5 provides characteristics of motherboards of selected SDR devices.

The motherboard, in SDR devices, interfaces daughterboard with a GPP host. It exchanges baseband samples with GPP host and IF analog signals with daughterboards. Actually, a received IF analog signal from a daughterboard is first digitized by ADC to get IF digital samples and then downsampled through DDC to obtain baseband digital samples.

VOLUME x, xxxx

TABLE 5: Characteristics of motherboards of SDR devices.

| SDR family            | DSP processor                        | Sample | e rate (MS/s) | Resolu | tion (bits) | Comm. Interface | Type       |  |

|-----------------------|--------------------------------------|--------|---------------|--------|-------------|-----------------|------------|--|

| 3DK family            | D3r processor                        | ADC    | DAC           | ADC    | DAC         | Comm. Interface | Type       |  |

| HackRF One [45]       | NXP LPC43XX ARM<br>Cortex-M4 MCU     | 20     | 20            | 8      | 8           | USB 2.0         | Integrated |  |

| USRP B210 series [43] | Xilinx Spartan-6 FPGA                | 61.44  | 61.44         | 12     | 12          | USB 3.0         | Integrated |  |

| USRP X310 series [43] | Xilinx Kintex-7-410T<br>FPGA         | 200    | 800           | 14     | 16          | Ethernet        | Separate   |  |

| Microsoft Sora [48]   | Virtex-5 FPGA                        | 44     | 40            | 12     | 12          | PCIe            | Separate   |  |

| LimeSDR [47]          | Altera Cyclone IV<br>EP4CE40F23 FPGA | 160    | 640           | 12     | 12          | USB 3.0, PCIe   | Integrated |  |

Finally, the baseband samples are transmitted to the GPP host through an integrated communication interface. On the reverse direction, received baseband samples are first upsampled through DUC to get IF digital samples and then converted to IF analog signal by DAC. Finally, the IF analog signal is forwarded to the daughterboard [49]. In the market, motherboards are either separate boards containing slots to plug daughterboards or a board integrating daughterboards.

### **B. COMMUNICATION INTERFACE**

Data is transferred from GPP Host to SDR device and viceversa using wired communication interfaces. These are based on commonly used data transfer communication interfaces like Universal Serial Bus (USB 2.0, USB 3.0, etc.), Ethernet (standard, fast, gigabit, etc.) and Peripheral Component Interconnect Express (PCIe 1.x, PCIe 2.x, etc). They consist of controllers such as Network Interface Controller (NIC), installed in both GPP host and SDR motherboard, to implement the communication interface standard. The communication interface technology implemented by the controller has specific characteristics defined by standards such as the maximal supported rate, maximal payload size, maximal cable length, etc., [50]-[52]. To allow more flexibility in data transfer speeds, some SDR devices include multiple communication interfaces (see Table 5). The controllers of both SDR device and GPP host should implement the same interface standard but not necessarily the same version. Indeed, different versions of the same standard may create connection between the two ends but they need to be synchronized for efficient data exchange. In such cases, the communication standard with the lowest rate will be agreed by auto-negotiation (as for Ethernet [51]) or backward compatibility (for example between USB 2.0 and USB 3.0) or manually [53].

### C. GPP HOST

A GPP host is a programmable device that can perform computational tasks based on instructions given by software programs using either high or lower level programming languages. As such a GPP host combines hardware and software, and is responsible to handle their interaction. The subsequent sections review these components highlighting the parts that impact the processing speed of a GPP host.

### 1) Hardware

The GPP host components are, mostly, assembled in a singleboard. This board contains SoC internal components such as GPP, internal memories, co-processors (GPU, DSP ASIP, etc.), and possible controllers for communication interfaces (see section III-B) and SoC external components such as external memories, expansion slots, etc.

A GPP, which can be either microprocessor or microcontroller, is responsible for performing the digital PHY, MAC, and upper layer operations. Unlike the conventional transceivers, it has the advantage of either high or low level programmability without modifying the hardware. Although it offers high user flexibility, the high-level programmability usually results in performance degradation of the processor to satisfy the requirements of intensive computation signal processing tasks [54]. Indeed, the performance (processing speed) of GPP is largely determined by a clock, where lower clock speed implies a slow processor and less energy consumption [55].

The GPP may be of single core or multi-core processor. However, most GPPs currently are based on multi-core (Dual-core, Quad-core, etc.,) processors on a single physical Central Processing Unit (CPU) [7]. Each core, in a multi-core single CPU system, represents a single processor or execution unit capable of executing processes concurrently with other processors. This increases the number of instructions to be processed per clock cycle. In addition to clock speed and number of cores, system bus architecture (bus width, its clock frequency, the number of data it can transfer per clock cycle, etc.,) significantly affects the speed of processing [55]. The size and level of cache a CPU has also affects the speed of its processing. Other parameters that could affect overall processing speed of GPP are number of threads, memory size, number of ALUs, hyper-threading support, size of Single Instruction Multiple Data (SIMD) units, etc. The SIMD units allow a processor to perform simultaneously the same instruction (operation) on multiple data units [56]. Recent GPPs support SIMD architecture to improve performance capabilities [57]. Table 6 provides few examples of GPP host hardware. To achieve more computing performance, GPPs are usually complemented with co-processors like GPU, FPGA and DSP ASIP as accelerators [56], [58], [59].

| TABLE 6: | List of | well-known | GPP H | lost hardware. |

|----------|---------|------------|-------|----------------|

|          |         |            |       |                |

| GPP Characteristics | Desktop computer   | Laptop              | Smartphones      | Embedded<br>computer boards |

|---------------------|--------------------|---------------------|------------------|-----------------------------|

| -                   |                    |                     |                  |                             |

| Processor           | Intel x86, AMD,    | Intel x86, AMD,     | ARM, Intel, MIPS | ARM, 8051 cores,            |

|                     | ARM, MIPS          | ARM, MIPS           |                  | microMIPS                   |

| SIMD support        | Yes                | Yes                 | Yes              | Yes                         |

| Comm.Interface      | USB,Ethernet,PCIe  | USB, Ethernet, PCIe | USB              | USB, Ethernet               |

| controller          |                    |                     |                  |                             |

| Computing power     | Low to High        | Low to High         | Low to Medium    | Low to Medium               |

| Size/Weight         | Large              | Medium              | Small            | Small                       |

| Example             | Dell, Apple, HP,   | Dell, Apple, HP,    | iPhone, Samsung, | Raspberry Pi, Ar-           |

|                     | Lenovo, Acer, etc. | Lenovo, Acer, etc.  | Huawei, etc.     | duino, NXP, etc.            |

### 2) Software

The software part of GPP host controls the operation of the processor, input/output traffic of communication controllers and the SDR device. It is generally layered into three on top of the hardware processor as instructions set, kernel space and user space. The instruction set is defined as a group of instructions a processor can execute. Thereby, an instruction code (object code) generated by a compiler or an assembler

can only contain instructions from this set. The instruction set is one of two types of instruction set architecture (ISA) designs: Reduced Instruction Set Computers (RISC) or Complex Instruction Set Computers (CISC) [60]. The ISA of GPPs can be based on CISC or RISC. To exploit the advantages of both instruction sets, modern GPPs are more based on hybrid ISA (using CISC instructions externally, but RISC techniques internally) [61]. Moreover, the use of RISC architecture can also be enhanced by adding Very Long Instruction Word (VLIW) extensions, a technique that offer instruction level parallelism [62].

The middle layer of the software system architecture is the kernel. It is the heart of an operating system (OS), linking the user space with the hardware processor [63]. To interact with the hardware, the kernel includes hardware drivers such as processor driver, hard disk driver, network controller driver, etc. To interact with user space, the kernel includes Application Program Interface (API) allowing programs in user space to access system resources (e.g., file systems, GPP time, virtual memory, etc.,) and services (e.g., scheduling, swapping, interrupt request (IRQ) handling, context switching, etc). It is precisely these services that impact the kernel space performances in terms of latency and overhead. To reduce the latency, additional functions such as the IRQ handler, process scheduling, reducing number of context switches, etc., are required. On the other hand, kernel overhead is the time due to managing resources such as GPP time, memory, disk, etc. The increased overhead often results in reducing the GPP time occupation and consequently the GPP throughput. As reducing the kernel latency requires additional functions, the kernel overhead will increase. It is obvious that a trade-off between kernel latency and GPP throughput exists, and a balance should carefully be designed as per user need.

At the top of software system architecture is the user space that consists of a portion of memory in which user applications are executed. Hereby, the user applications are PHY and MAC functions of the wireless technologies. The user applications are mostly written using high-level programming languages like C, C++, Java, Python, Matlab, etc. It is also possible to generate the user applications code via data flow textual/graphical programming languages like G programming, Python, C++, etc. These programming languages (high-level and data-flow) are generally included in software development toolkits such as GNU Radio [64], LabVIEW [65], Matlab [66], etc. The toolkits provide DSP libraries for DSP functions, libraries for runtime and compilation, graphical tools for creating signal flow graphs and generating flow-graph source code, etc.

The user application compiler is an element of most importance in assisting the processor to achieve high performance in speed and execution time. It is responsible for generating the instruction code using the ISA of the target processor. When a large variety of target processors are supported, the compiler is said to be general (like the GNU Compiler Collection (GCC) [67]). The general compilers also implement optimizations to improve the GPP performance by increasing the parallelism levels through three mechanisms: instructionlevel parallelism (ILP) which allows multiple instructions to be executed at the same time, thread-level parallelism (TLP) which allows multiple threads to run simultaneously or pseudo-simultaneously on single/multiple cores, and datalevel parallelism (DLP) which enables performing multiple data-elements simultaneously. This entails an optimal source code generation in size and execution time, according to the target processor. Examples of optimizations are automatic vectorization [68], automatic parallelization [68], [69], inter-procedural optimization [70], and SIMD intrinsics (assembly-coded functions [71]). Table 7 lists well-known software implementation toolkits.

TABLE 7: Software development toolkits.

| Implementation<br>tools | programming language |           | High Level<br>programming | Scheduler | Optimization type   | License     |

|-------------------------|----------------------|-----------|---------------------------|-----------|---------------------|-------------|

|                         | Textual              | Graphical | language                  |           |                     |             |

| GNU Radio               | C++/python           | GRC       | C++/python                | yes       | SIMD (VOLK) [72]    | open-source |

| Labview [73]            | C/MathScript         | G/DFIR    | С                         | yes       | Auto (DFIR/LLVM)    | Commercial  |

| Matlab/                 | Matlab(.m            | Simulink  | С                         | yes       | Manual or Auto [69] | Commercial  |

| Simulink                | code)                |           |                           |           |                     |             |

| C/C++                   | X/X                  | X/X       | C/C++                     | Hard code | Manual or compiler  | open-source |

### **IV. SDR PLATFORM PERFORMANCE ANALYSIS**

To implement a wireless technology on SDR platforms or use existing implementations, it is necessary that the selected SDR platform (SDR device, communication interface and GPP Host) performance should meet at least the requirements of the target wireless technology. These requirements are mainly given in terms of operating frequency band, bandwidth, symbol rate, bitrate, latency, etc. In this section, a thorough theoretical analysis of these performance parameters in GPP-based SDR platform architecture is presented along with the minimal/maximal values offered by the components.

### A. FREQUENCY BAND

The frequency band of SDR platforms is the operating frequency range covered by the SDR device. This is determined at the daughterboards from the local oscillator (LO) signals generated by the frequency synthesizer, such as Phase-Locked Loop (PLL) synthesizer. Large frequency band needs large LO frequency range, and consequently wideband frequency synthesizers. Daughterboard's datasheet usually lists the operating frequency band of SDR devices (see Table 4 for well-known daughterboards). To cover the range of frequency bands supported by daughterboards, SDR device's need to use appropriate type of antenna [74].

### **B. BANDWIDTH**

Any analog or digital signal has a bandwidth defined as the occupied range of frequencies carrying most of its energy. This range varies at each stage of the signal chain. Hence, it can be expressed differently (but related) according to the signal processing stage. Indeed, at the RF front end stage, it is expressed as the analog bandwidth or RF channel width. At the ADC/DAC stage, it is expressed as the DAC/ADC sample rates. When the signal is processed at the digital front end

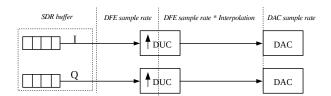

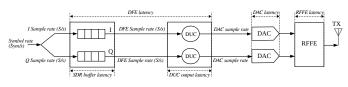

(DFE) stage, its bandwidth is expressed as the DFE sample rate. On the communication link between the DFE and GPP, the bandwidth is limited by the communication interface speed. At the GPP host, the bandwidth is expressed as the symbol rate. Fig. 3 illustrates the main points in the signal chain where the bandwidth of SDR platform is characterized. In this section, we examine the analog bandwidth, ADC/DAC and DFE sample rates. Sections IV-C, IV-D and IV-E will address the interface speed, symbol rate and bitrate.

FIGURE 3: Bandwidth at each block of SDR-GPP signal chain.

### 1) Analog bandwidth

This bandwidth, measured in Hz, is determined by the RF front end (daughterboard) of the SDR device. It is configured mainly by the analog baseband low pass filter (LPF) to vary from 0 Hz to the specified cut-off frequency,  $f_{cut}$ . Thus, in a direct-conversion (Zero IF) I/Q modulator [75] both at the transmitter and receiver side, the analog bandwidth at RF front end is determined by the LPF and its  $f_{cut}$ . It is equal to twice  $f_{cut}$  for Ideal LPFs that completely eliminate (attenuate) all frequencies above the  $f_{cut}$ . The excess bandwidth, defined as the transition band in LPF datasheets [76], of an Ideal LPF is null, and hence its Roll-off factor (ratio between passband and transition band) is null. In real-world, practical LPFs are not perfect and have a transition region where some high frequencies above the  $f_{\text{cut}}$  can pass. Consequently, the real analog bandwidth is greater than twice  $f_{cut}$  and can be formulated as follows:

Real Analog bandwidth =  $(2 \times f_{cut}) \times (1 + \text{Roll-off factor})$  (1)

where the Roll-off factor is in the range [0,1]. Equation (1) assumes signals spectra that would occur after theoretical cut-off point. Thus, the Roll-off factor shifts the bandwidth towards the transition band so that we can minimize loss of information.

Most of the LPFs are programmable and can take different  $f_{cut}$  values where each  $f_{cut}$  is assigned a roll-off factor. The maximal real analog bandwidth is achieved by the highest  $f_{cut}$  scaled by [1 + Roll-off factor]. Table 8 summarizes the analog bandwidth as theoretically computed from (1) and the maximal ideal analog bandwidth (twice  $f_{cut}$ ) as indicated on the daughterboard's datasheet.

### 2) ADC/DAC sample rate

The DAC sample rate, given on Samples per Second (S/s), allows to determine the time interval between two samples applied to the input of a DAC. The ADC sample rate determines the time interval between two samples at the output of an ADC. Both sample rates are related to the input signal spectrum by the Nyquist-Shannon sampling theorem [77].

| SDR                 | Max.cutoff | Max. Ideal Analog | Roll-off | Max. real Analog |

|---------------------|------------|-------------------|----------|------------------|

|                     | frequency  | bandwidth (MHz)   | factor   | bandwidth (MHz)  |

| HackRF [45]         | 10         | 20                | 0        | 20               |

| UBX-40, SBX-40,     | 20         | 40                | 1.5      | 100              |

| CBX-40, WBX-40 [43] |            |                   |          |                  |

| SBX-120, CBX-120,   | 60         | 120               | 0.667    | 200              |

| WBX-120 [43]        |            |                   |          |                  |

| UBX-160 [43]        | 80         | 160               | 0.25     | 200              |

| USRP-B2x0 [43]      | 28         | 56                | 0.097    | 61.44            |

| Microsoft Sora [46] | 10         | 20                | 1        | 40               |

| LimeSDR [47]        | 80         | 160               | 0        | 160              |

### TABLE 8: Maximal analog bandwidths of SDR devices.

Theoretically, for a given ADC/DAC sample rate, the maximum frequency that can be reproduced is half the sample rate (Nyquist frequency) to avoid aliasing effect. As the maximum frequency of an equivalent complex baseband (a complex valued representation of the real baseband) is [real analog bandwidth / 2], the sample rate needs to be greater than the real analog bandwidth (see (1)). The more sample rate is greater than the real analog bandwidth, the more the band gap increases between the real analog bandwidth copies repeated at multiples of sample rate resulting on zero-loss on bandwidth. This band gap has an amount of [ADC sample rate – real analog bandwidth] Hz.

In motherboard of SDR devices, the integrated ADC/DAC can support one or multiple sample rates where one at a time can be selected. The highest sample rate value determines the largest analog bandwidth. Table 9 shows the supported sample rates by well-known SDR devices. This table also shows whether the SDR device has fixed or selective sample rates. Using selective sample rate is preferable than fixed rate to adapt the real analog bandwidth to the necessary bandwidth asked by applications' rate requirement and expressed by the DFE sample rate (see section IV-B3). When the nearest sample rate is greater than the DFE sample rate, an adjustment through interpolation and decimation process is necessary [49].

| SDR device     | Ideal Analog<br>bandwidth | Clock rate<br>(MHz) | Supported ADC<br>sample rates (MS/s) | Supported<br>DAC sample | Selective/<br>Fixed |

|----------------|---------------------------|---------------------|--------------------------------------|-------------------------|---------------------|

|                | (MHz)                     | (MHZ)               | sample rates (MIS/S)                 | rates (MS/s)            | Fixed               |

| HackRF [45]    | 20                        | 20                  | 20                                   | 20                      | Fixed               |

| USRP-X3x0      | 160                       | 200,                | 195.31K - 200M;                      | 800                     | Selective           |

| (UBX-160) [43] |                           | 184.32              | 180.0K - 184.32M                     |                         |                     |

| USRP-B2x0 [43] | 56                        | 5-61.44             | 61.44                                | 61.44                   | Selective           |

| Microsoft Sora | 20                        | 40, 44              | 40, 44                               | 40                      | Selective           |

| [48]           |                           |                     |                                      |                         |                     |

| LimoSDD [47]   | 160                       | 640                 | 20 160                               | 80 640                  | Salaatiwa           |

TABLE 9: Analog bandwidth and ADC/DAC sample rates.

### 3) Digital Front End (DFE) sample rate

This rate, given on Samples per second (S/s), defines the constant speed by which I/Q samples are exchanged between the DUC/DDC (interpolation/decimation) stages and the interface controller. It can be specified either explicitly by the user or implicitly from the real analog bandwidth of the channel. The sample size (in bits) is determined by the DAC/ADC resolution. At the transmitter side of an SDR device, arriving I and Q data samples from the GPP host (in a format configured by the user, e.g., 32-bit float) join their corresponding queue waiting for service by the DFE. The arrival rate at the queue is constant over time and is determined by the bitrate of GPP host. The interpolation stage of the DFE retrieves samples from the queue at DFE sample rate, which is the service rate of the queue system. As the DFE sample rate can take very high values, it is extremely important that the arrival and service rates should be equal after normalization to avoid waiting for the queues to become non-empty (underflow). Then, the interpolation stage increases the DFE sample rate of input samples to higher output rate equal to the DAC sample rate (see Fig. 4). The applied interpolation factor is equivalent to the ratio of the DAC sample rate to the DFE sample rate.

FIGURE 4: DFE sample rate (Digital Up Converter).

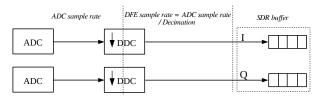

At the receiver side of an SDR device, as shown in Fig. 5, the DFE receives samples at a speed of ADC sample rate. It performs decimation to decrease the input ADC sample rate to a lower rate equal to the DFE sample rate. The applied decimation factor is equivalent to the ratio of ADC clock rate to the DFE clock rate. The output samples are, then, inserted into the I/Q queues waiting to be transmitted to the GPP host. A queue overflow occurs when the GPP host cannot retrieve samples as fast enough. As in the transmitter side, it is extremely important that the DFE sample rate be close to the bitrate of GPP host.

FIGURE 5: DFE sample rate (Digital Down Converter).

From the above discussion, as the DFE sample rate should be close to the bitrate of GPP host, it can be used to define the necessary channel bandwidth required by user application in the GPP host. Since the necessary channel bandwidth is included in the real analog bandwidth (see section IV-B1), the DFE sample rate should be smaller than the real analog bandwidth. Also, the DFE sample rate should be increased or reduced to fulfill the DAC and ADC clock rates. Some SDR devices require a strictly-integer interpolation and decimation factors, and it is strongly desirable for that factors to be even and it's much better if the factors are in power of two [78]. Thus, specifying appropriate DFE sample rate is another requirement to be considered by the user. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2022.3154364. IEEE Access

D.M. Molla et al.: Software Defined Radio Platforms for Wireless Technologies

### 4) The maximal GPP-based SDR platform bandwidth

Since GPP-based SDR platform's bandwidth is concave, it takes the lowest value between analog bandwidth, ADC/DAC sample rate and DFE sample rate. The maximal DFE sample rate is achieved when its value reaches to ADC sample rate and DAC sample rate at unity decimation and interpolation factor, respectively. However, as stated above, DFE sample rate cannot be greater than real analog bandwidth. Consequently, the maximal GPP-based SDR platform bandwidth (in Hz) is the minimum from maximal DFE sample rate and analog bandwidth.

### C. COMMUNICATION INTERFACE SPEED

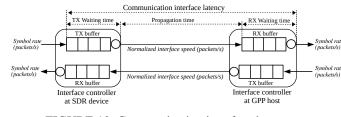

This speed, given in bit per second (bit/s), refers to the PHY layer net bitrate of the wired interface between GPP host and SDR device. The PHY layer net bitrate defines the amount of transferred bits, excluding the PHY layer protocol overhead, per second over a communication link. Obviously, its value (specified by the standard) is less than the real transmission rate defined at the PHY layer gross bitrate that includes the PHY layer overhead (channel coding, modulation, physical framing, guard interval, etc). For example, the PHY layer net bitrate of the Gigabit Ethernet is 1 Gbit/s and the real transmission rate is 1.25 Gbit/s due to the 8B/10B encoding [79]. Since I/Q samples, exchanged between GPP host and SDR device, are encapsulated in frames of the used interface, their rate is limited by the communication interface speed. In the upcoming discussion, the I/Q sample rate is the equivalent of DFE sample rate defined in bit/s and related by [DFE sample rate  $\times$  I/Q symbol format].

The communication interface speed, despite it excludes the PHY layer protocol overhead, it includes upper layer protocols head such as link layer head, network layer head, etc. Based on this remark, the peak (maximum achievable) rate of encapsulated I/Q samples (useful data rate) is limited by the communication interface speed weighted by a factor of [payload size / data link frame size], known as the link efficiency. Higher the link efficiency, closer the peak I/Q sample rate to the communication interface speed. The peak I/Q sample rate is an instantaneous rate that doesn't consider link occupancy. Consequently, its value will be very large to be taken as an acceptable upper bound, otherwise the real I/Q sample rate will be under-constrained. Thus, it is necessary to include the link occupancy on the upper bound to get the maximal acceptable I/Q sample rate (or maximal acceptable DFE sample rate). To do so, the peak I/Q sample rate weighted by the link occupancy, expressed as [peak I/Q sample rate  $\times$  link occupancy], will give us the maximal acceptable I/Q sample rate. Henceforth, we limit the I/Q sample rate or DFE sample rate by the maximal acceptable I/Q sample rate.

The maximal acceptable I/Q sample rate is affected by three factors: the communication interface mode, GPP host application mode and SDR device capability. The communication interface between the GPP host and SDR device motherboard can work in either half or full duplex modes. With full-duplex interface mode, the communication link can simultaneously be fully occupied in both directions (Host $\rightarrow$ SDR and SDR $\rightarrow$ Host) allowing to benefit from fullspeed on each direction. In this case, the transmit and receive links have independent occupancy of up to 100% each at any time. With half-duplex interface mode, the communication link is used to either exclusively transmit or receive. In this case, the link occupancy is shared so that transmitting and receiving occupancies are 100%'s complement. One could think that full-duplex interfaces always achieve highest performance but in reality it depends on the GPP host application and SDR motherboard capability (half or full-duplex transceiver). Indeed, half and full duplex interfaces can have similar performance when:

- The GPP host application is one-way communication. So, using either half or full duplex is the same, as the communication needed is only to transmit or receive. This implies the link occupancy of the used direction can attain 100%, allowing a maximal acceptable TX or RX I/Q sample rate equal to the peak rate (on the used direction) and always null on the other direction. Thus, using only half-duplex interface is sufficient when the GPP host application is one-way communication;

- The GPP host application is non-overlapped two-way communication. Both directions between SDR device and GPP host cannot be used simultaneously since transmission and reception are separated in time. So, the occupied time for transmission doesn't consume the time of reception and vice versa. Consequently, the sum of TX and RX link occupancies can go to 100% allowing a maximal acceptable TX rate of [peak rate × TX link occupancy] and maximal acceptable RX rate of [peak rate × (1 TX link occupancy)]. Thus, using only half-duplex interface is sufficient when GPP host user application is non-overlapped two-way;

- The SDR device is half-duplex. As SDR device can either receive or transmit, only single direction on the link between SDR device and GPP host is solicited. Such SDR device capability is suitable for GPP host user applications using one-way communication or twoway communication without temporal overlap between transmission and reception. Since only single direction is being used, its link occupancy can go to 100% allowing a maximal acceptable rate equal to the peak rate (null for the unused direction). Hence, using only half duplex interface is sufficient for one-way and nonoverlapped two-way communications when SDR device is half duplex.

Full-duplex interfaces become necessary when the GPP host user application is temporally overlapped two-way communication. In addition, SDR devices should also be full-duplex. In this scenario, TX and RX link occupancies are independent and can simultaneously go to 100%. Now, the maximal acceptable TX and RX rate can attain the peak I/Q sample rate. Table 10 shows the maximal supported I/Q

| Interface Host - SDR | Speed (Mbit/s)            | Interface mode      | Link efficiency | Host application        | Max TX. r                | ate (Mbit/s)  | Max. RX ra                            | te (Mbit/s)    |

|----------------------|---------------------------|---------------------|-----------------|-------------------------|--------------------------|---------------|---------------------------------------|----------------|

| Interface Host - SDR | Speed (Wold's)            | interface mode      | Link enterency  | Host application        | Half Dup.SDR             | Full Dup.SDR  | Half Dup.SDR                          | Full Dup.SDR   |

|                      |                           |                     |                 | TX 1-way Comm.          | 473                      | 478.59        |                                       |                |

| USB2 0 [50]          | USB2.0 [50] 480 Half dup. |                     | 0.9970          | RX 1-way Comm.          |                          | 0             | 478.59                                |                |

| 0302.0 [50]          |                           |                     | 0.9970          | Non-overlap 2-way Comm. |                          | K link Occup. | 478.59× (1 − T                        | X link Occup.) |

|                      |                           |                     |                 | Overlap 2-way Comm.     | not supported            | not supported | not supported                         | not supported  |

|                      |                           |                     |                 | TX 1-way Comm.          | 502                      | 1.91          | 0                                     |                |

| USB3.0 [50]          | 5120                      | Full dup.           | 0.9808          | RX 1-way Comm.          |                          | 0             | 5021.91                               |                |

| 00005.0[50]          | 5120                      | r un dup.           | 0.9000          | Non-overlap 2-way Comm. | 5021.91 × TX link Occup. |               | $5021.91 \times (1 - TX link Occup.)$ |                |

|                      |                           | Overlap 2-way Comm. | not supported   | 5021.91                 | not supported            | 5021.91       |                                       |                |

|                      |                           |                     | 0.9881          | TX 1-way Comm.          | 98                       | 8.1           | 0                                     |                |

| Gig.Eth [51]         | 1000                      | Full dup.           |                 | RX 1-way Comm.          | 0                        |               | 988                                   |                |

| Olg.Eur [51]         | 1000                      |                     |                 | Non-overlap 2-way Comm. | 988.1× TX link Occup.    |               | 988.1× (1 – T2                        | K link Occup.) |

|                      |                           |                     |                 | Overlap 2-way Comm.     | not supported            | 988.1         | not supported                         | 988.1          |

|                      |                           |                     |                 | TX 1-way Comm.          | 98                       | 81.0          | 0                                     |                |

| 10Gig.Eth [51]       | 10000                     | Full dup.           | 0.9881          | RX 1-way Comm.          |                          | 0             | 988                                   |                |

| 1001g.Etti [51]      | 10000                     | Full dup.           | 0.9881          | Non-overlap 2-way Comm. | 9881.0× TX               | Iink Occup.   | 9881.0× (1 − T                        | X link Occup.) |

|                      |                           |                     |                 | Overlap 2-way Comm.     | not supported            | 9881.0        | not supported                         | 9881.0         |

|                      |                           |                     |                 | TX 1-way Comm.          | 626                      | 17.75         | 0                                     |                |

| PCIe 4.X (x4 link)   | 63015.38                  | Full dup.           | 0.99369         | RX 1-way Comm.          |                          | 0             | 62617.75                              |                |

| [52]                 | 05015.50                  | run dup.            | 0.99369         | Non-overlap 2-way Comm. | 62617.75× TX link Occup. |               | 62617.75× (1 – TX link Occup.)        |                |

|                      |                           |                     |                 | Overlap 2-way Comm.     | not supported            | 62617.75      | not supported                         | 62617.75       |

TABLE 10: Maximal I/Q sample rates of selected communication interfaces between GPP host and SDR transceivers.

sample rates of Host-SDR interface solutions for both full and half-duplex SDR transceivers.

### D. SYMBOL RATE

This rate, given in Symbol per second (Sym/s), refers to the constant rate at which symbols occur. One symbol can carry one or more bits according to the digital modulation format. For example, in a BPSK system, each symbol represents one bit; in a 64-QAM system, each symbol represents 6 bits. Symbol rate is determined from the symbol duration as [1 / symbol duration], where symbol duration is the sum of the useful symbol duration and the potential guard interval expressed as [useful symbol duration + guard interval]. The guard interval is used between two successive symbols to reduce inter-symbol interference that results from multi-path fading or band-limited channels [80]. It is given by the wireless technology specification. The useful symbol duration is the time used to carry the useful data and is related to the number of samples per symbol and the sampling interval time. It can be formulated as [number of samples per symbol  $\times$  sampling interval]. The sampling interval parameter is the inverse of the DFE sample rate, [1 / DFE sample rate]. As the DFE sample rate for quadrature sampling systems is equal to the occupied baseband bandwidth, the sampling interval will be the inverse of the occupied baseband bandwidth. The number of samples per symbol parameter can be computed from the frequency domain based on the total number of spectral lines [80].

The number of samples per symbol is equal to the number of spectral lines in quadrature sampling systems and twice in direct-sampling systems. The number of spectral lines is related to the number of carrier/sub-carrier frequencies. Considering quadrature sampling system, when a conventional single-carrier modulation is applied (like in IEEE 802.15.4, ...), the number of spectral lines is equal to one and hence the number of samples per symbol will be one. When multiple sub-carrier modulation technique is used (like in IEEE 802.11ac, ...), the number of spectral lines is equal to the total number of used and unused sub-carriers. In general, the total number of sub-carriers is specified by the used FFT size [80]. To summarize, the useful symbol duration is expressed as [number of spectral lines / occupied baseband bandwidth].

In some wireless systems spread spectrum techniques such as Frequency-Hopping Spread Spectrum (FHSS), Direct Sequence Spread Spectrum (DSSS), Time-Hopping Spread Spectrum (THSS) and Chirp Spread Spectrum (CSS) are used to prevent interference by transmitting symbols at low power density over a wide band. This band is named as spread occupied baseband bandwidth. The spreading process is achieved by multiplying the symbols with a spreading code, known as chip sequence, having a faster rate than the input symbol rate (symbol rate before spreading). Thus, the spread occupied baseband bandwidth is larger than the original baseband bandwidth by a factor of chip sequence size, [original occupied baseband bandwidth  $\times$  chip sequence size]. The spread occupied baseband bandwidth is always given as the channel size of wireless systems using spread spectrum techniques. The spreading process has no effect on the useful symbol duration. However, as the given channel size is the spread baseband bandwidth and not the original occupied baseband bandwidth, the useful symbol duration needs to be relied on the spread baseband bandwidth and the chip sequence size. Based on the fact that the symbol duration before spreading is [number of spectral lines / original occupied baseband bandwidth] and the original occupied bandwidth is [spread baseband bandwidth / chip sequence size], the output symbol duration can be written as [number of spectral lines  $\times$  chip sequence size / spread occupied baseband bandwidth]. It is obvious that the input and output useful symbol duration are the same.

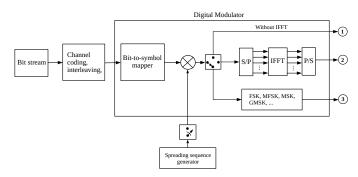

In general, the useful time duration with/without spreading process can be formulated as [number of spectral lines  $\times$  chip sequence size / channel size]. Fig. 6 depicts an example of possible single/multiple carrier and spreading/non-spreading cases of digital baseband transmitter. Table 11 provides equations of the symbol rate for each path-end. By applying these equations, users can generate the symbol rate for their desired wireless technology and can also be verified from the corresponding specifications [31], [33], [35], [39]–[41].

The software programmer at user space should consider both symbol rate and symbol format. The symbol rate can be either explicitly set or implicitly driven from the DFE

D.M. Molla et al.: Software Defined Radio Platforms for Wireless Technologies

FIGURE 6: Digital baseband transmitter paths.

| TABLE 11: Symbol | rate of transmitter | paths in Fig. 6. |

|------------------|---------------------|------------------|

|                  |                     |                  |

| Path-end | Spreading | Symbol rate                                                                                                                                       |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|          | No        | $\frac{1}{\frac{1}{\text{occupied baseband bandwidth}} + \text{guard interval}}$                                                                  |

| (1)      | Yes       | chip sequence size<br>spread occupied baseband bandwidth +guard interval                                                                          |

|          | No        | $\frac{1}{\frac{\text{number of spectral lines}}{\text{occupied baseband bandwidth}} + guard interval}$                                           |

| (2)      | Yes       | $\frac{l}{\frac{\text{number of spectral lines } \times \text{ chip sequence size}}{\text{spread occupied baseband bandwidth}} + guard interval}$ |

|          | No        | $\frac{1}{\frac{1}{\text{occupied baseband bandwidth}} + \text{guard interval}}$                                                                  |

| (3)      | Yes       | chip sequence size<br>spread occupied baseband bandwidth +guard interval                                                                          |

sample rate and the number of used subcarriers. The symbol format, on the other hand, should be explicitly specified (e.g., complex int16, complex int32, etc). When using a complex int16, the I and Q samples of each symbol are coded each by 16 bits, and so 32 bits per I/Q sample are transmitted to the communication interface. This transmission has a rate of [symbol rate  $\times$  symbol format]. The communication interface considers the received data as a data payload and performs its operation related to its technology.

### 1) Maximal symbol rate at SDR devices

From the equations depicted in Table 11, the theoretical maximal symbol rate at SDR device can be attained when the channel width (bandwidth) is at its maximal value, and the number of spectral line, guard interval and chip sequence size are at their lowest values. The highest channel width can be set to the maximal bandwidth of SDR device; the lowest number of spectral lines can be set to one; the lowest guard interval can be set to zero (without guard interval) and the lowest chip sequence size can be set to one (i.e., without spreading). Consequently, the maximal symbol rate takes the maximal bandwidth of the SDR device. On the other hand, as symbols should traverse the communication interface between the GPP host and the SDR device and vice versa, the maximal symbol rate at the SDR device is bounded by the communication interface speed (after normalization). This latter value is given by [(interface speed  $\times$  link efficiency  $\times$  link occupancy) / symbol format] in Sym/s. Since, we have two theoretical upper bounds, the maximal symbol rate will take the minimum value between them, i.e., minimum (maximal bandwidth of SDR device, [(interface speed  $\times$  link

VOLUME x, xxxx

efficiency  $\times$  link occupancy) / symbol format]). See Table 13 in subsection IV-D3 for the maximal theoretical upper bound of the symbol rate at SDR devices.

### 2) Maximal symbol rate at GPP host

In GPP-based SDR platforms, all symbols are either generated or consumed by GPP host. Therefore, GPP host can impact the maximal symbol rate supported by the platforms. To determine the maximal speed at which symbols are generated or consumed at a GPP host, a continuous data transmission/reception without MAC operations, physical framing, channel coding and spreading is considered. Consequently, the executed physical layer in software should incorporate only bit generator and digital modulator blocks at the transmission side (baseband TX path); or bit sink and digital demodulator blocks at the receiving side (baseband RX path). Hence, only Bit stream and Digital Modulator blocks in Fig. 6 are used to determine the upper bound of symbol rates supported at GPP hosts.