# An Overview of Hardware Implementation of Membrane Computing Models

Gexiang Zhang, Zeyi Shang, Sergey Verlan, Miguel Á. Martínez-Del-Amor, Chengxun Yuan, Luis Valencia- Cabrera, Mario Pérez-Jiménez

# ▶ To cite this version:

Gexiang Zhang, Zeyi Shang, Sergey Verlan, Miguel Á. Martínez-Del-Amor, Chengxun Yuan, et al.. An Overview of Hardware Implementation of Membrane Computing Models. ACM Computing Surveys, 2021, 53 (4), pp.90. 10.1145/3402456. hal-03550487

# HAL Id: hal-03550487 https://hal.science/hal-03550487v1

Submitted on 1 Feb 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# An Overview of Hardware Implementation of Membrane Computing Models

GEXIANG ZHANG\*, Chengdu University of Technology, China and Southwest Jiaotong University, China ZEYI SHANG, Southwest Jiaotong University, China and Université Paris-Est Créteil Val de Marne, France SERGEY VERLAN, Université Paris-Est Créteil Val de Marne, France

MIGUEL Á. MARTÍNEZ-DEL-AMOR, Universidad de Sevilla, Spain

CHENGXUN YUAN, Southwest Jiaotong University, China

LUIS VALENCIA-CABRERA, Universidad de Sevilla, Spain

MARIO J. PÉREZ-JIMÉNEZ, Universidad de Sevilla, Spain

The model of membrane computing also known under the name of P systems is a bio-inspired large-scale parallel computing paradigm having a good potential for the design of massively parallel algorithms. For its implementation it is very natural to choose hardware platforms that have important inherent parallelism, like field-programmable gate arrays (FPGAs) or compute unified device architecture (CUDA)-enabled graphic processing units (GPUs). This paper performs an overview of all existing approaches of hardware implementation in the area of P systems. The quantitative and qualitative attributes of FPGA-based implementations and CUDA-enabled GPU-based simulations are compared to evaluate the two methodologies.

CCS Concepts:  $\bullet$  Hardware  $\rightarrow$  Simulation and emulation; Transaction-level verification; Semi-formal verification.

Additional Key Words and Phrases: Membrane Computing, P Systems, Hardware Implementation, Field Programmable Gate Array (FPGA), Compute Unified Device Architecture (CUDA), Graphic Processing Unit (GPU)

#### **ACM Reference Format:**

Authors' addresses: Gexiang Zhang, Chengdu University of Technology, No.1, Dongsan Road, Erxianqiao, Chenghua District, Chengdu, 610059, China, Southwest Jiaotong University, 999 Xián Rd, Chengdu, 611756, China, zhgxdylan@126.com; Zeyi Shang, Southwest Jiaotong University, 999 Xián Rd, Chengdu, 611756, China, Université Paris-Est Créteil Val de Marne, 61 av. du général de Gaulle, Créteil, 94010, France, zeyi.shang@lacl.fr; Sergey Verlan, Université Paris-Est Créteil Val de Marne, 61 av. du général de Gaulle, Créteil, 94010, France, verlan@u-pec.fr; Miguel Á. Martínez-del-Amor, Universidad de Sevilla, Avda. Reina Mercedes S/N, Seville, 41012, Spain, mdelamor@us.es; Chengxun Yuan, Southwest Jiaotong University, 999 Xián Rd, Chengdu, 611756, China, 502220232@qq.com; Luis Valencia-Cabrera, Universidad de Sevilla, Avda. Reina Mercedes S/N, Seville, 41012, Spain, lvalencia@us.es; Mario J. Pérez-Jiménez, Universidad de Sevilla, Avda. Reina Mercedes S/N, Seville, 41012, Spain, marper@us.es.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2020 Copyright held by the owner/author(s). Publication rights licensed to ACM.

0360-0300/2020/6-ART \$15.00

https://doi.org/10.1145/nnnnnn.nnnnnnn

<sup>\*</sup>Corresponding author

#### 1 INTRODUCTION

With the arising of *protocells* 3.84 billion years ago in hydrothermal vent precipitates [26], the evolution of unicellular organisms led to the apparition of multicellularity [83]. The biological cell structure defined by the membranes has evolved and was optimized for billions of years. As a consequence, a biological cell is a powerful parallel processing unit that can perform sophisticated biologic behaviors. Inspired by the structure of biological membranes and by internal bio-chemical reactions, Gheorghe Păun initiated the area of membrane computing in 1998 as a theoretical computer science model borrowing many concepts from the cell biology [84]. The model, also called P systems, features a nested membrane-like structure delimiting regions that host objects (modeling cell chemicals) which are transformed locally or communicated to other regions by different types of rules that mimic cell chemical transformations. The evolution of the state of the system is performed by transition steps doing a synchronous parallel execution of all rules. Since a typical model contains hundreds and even thousands of such parallel executions, P systems feature an inherent massive parallelism and the global behavior of the system is emerging from many simple interactions provided by rules application. There exist numerous variants of the model depending on the manipulated objects, used types of rules and the parallel execution strategy.

Membrane Computing is a computing paradigm inspired from the structure and functioning of living cells, and the organization of cells in tissues and other structures, including the brain. It provides distributed parallel computing devices called, generically, P systems. Membrane computing models are an extension of DNA computing, a possible source of novel/useful/interesting computing models. If one wants to model (1) discrete, (2) distributed, (3) parallel, (4) cell-like or tissue-like system, (5) dealing with multisets, (6) evolving by rewriting-like rules, then P systems are obligatory/unavoidable and the unique models dealing with all these features [85]. As unconventional computing devices within natural computing, P systems have proved to overcome the well-known limitations imposed by the conventional techniques based on electronic technology. More specifically, the relevance of these computing models can be non-exhaustively summarized in the following points. From a theoretical view, a novel methodology to tackle the famous P versus NP problem has been given [76]. The main focus in the area was the introduction of (biologically-inspired) variants of P systems and the further study of their computational power, in particular of their computational completeness, see [87] resuming hundreds of articles on this topic. From a practical view, the theoretical investigation led to a series of successful applications in different areas ranging from image processing [25, 114], meta-heuristic algorithms for optimization problems [116, 117, 119], robot controllers [14, 109] and path planning [79, 81, 110] and fault diagnosis for electrical power systems [90, 107, 108]. Due to its historical background, membrane computing was also used as a modeling framework for biological and ecological subjects such as artificial life [94], photosynthesis [75], p53 protein signaling pathway [95], myxobacterial colony [68], biopolymer duplication [56]. Please see a recent overview in [118].

For twenty years many applications of P systems have arisen, not only in Theoretical Computer Science, but also in Computational Modelling, Robotics, Optimization, etc., as mentioned above. The interest in this area is increasing, given that this unconventional, massively-parallel approach has been demonstrated to provide a powerful, flexible and expressive framework. One example is the 2016 report of the National Research Council of Canada where Membrane Computing appears to be mentioned several times as prominent parts of bio-computing [112]. Therefore, there is a need for simulators in order to build model validation tools, assistants for formal verification, environments for virtual experimentation, model calibration tools, etc. So far, most of the simulation software aim at reproducing only the computation of the devices. However, there have been also a research line concerning the implementation of P system parallelism in real parallel platforms. The main

hardware employed for this is FPGAs and GPUs, given their efficiency, fast shared memory system and scalability. The objective is twofold: on the one hand, provide efficient simulation tools where the massive, natural P system parallelism do not get serialized and is instead harnessed in order to speed up the simulations; and on the other hand, to explore how this special parallelism can be mapped in current modern computing architectures. It is known that the future of computer architecture will go through non-Von Neumann architectures [12]. Natural Computing models can provide solutions where the instructions are closed to, or along with, the data. P systems are just an alternative, like artificial neural networks, for this. We want to shed a light into this alternative from the perspective of efficient implementation, analysing all the challenges and current solutions. In addition, a number of these applications mentioned above only theoretically profit from the potential speed-up promised by the model as there are no truly parallel implementations available. On the other hand, the inherent large scale parallelism of the model has the profound potential for the progress of extreme data processing, especially taking into account that there are not so many widely investigated massively parallel computational paradigms. Thus, an interesting topic is the implementation of membrane computing models on contemporary silicon integrated circuits. This allows to exploit the desirable parallel computational capability of P systems to explore a new orientation for high performance computing (HPC) [51, 54].

As pointed out in [43] "some unmistakable trends in hardware design indicate that uniprocessor (or implicitly parallel) architectures may not be able to sustain the rate of realizable performance increments in the future". The augmentation of electronic ingredients' density had been subject to the well-known Moore's law for decades. After extraordinary exponential growth of many years, the number of transistor in chips cannot follow this law, at least it cannot be doubled within two years [2]. With transistors shrunk to nanoscale, quantum effects stand out [66] and the behavior of circuits is not up to expectations. Moreover, even with the further increase of the density, the computational capability growth is not linearly proportional to it [111]. Another knotty problem is the heat dissipation, which would melt the silicon substrate with density level increasing. Traditional semiconductor scaling is predicted to reach an end by about 2024 on the foundation of prior arts [1]. Parallel computing has the potential to further uplift computing power provided that the density of transistor is constant [101] with multicore and multithread architecture, although heat dissipation and interconnect issues would be challenges [8].

All these observations give strong arguments in favor of investigation of parallel computing platforms. Before claiming that the era of parallel computing has dawned, one essential question should be clarified: what does parallel computing mean? Though not rigorous, parallel computing implies computing based on the decomposition of the task into a set of concurrently executable operations and the assignment of these operations to multiple parallel processing nodes. The evolution of computer processor scheme, from single-core single central processing unit (CPU) to multiple-core single CPU and multiple-core multiple-CPU frame is an instance of parallel computing. The inherent parallelism of P systems place them in the class of multiple processing nodes computing devices. The mapping of constituents to processing nodes gives rise to different implementation strategies. A common practice in the area of natural computing is to observe natural processes and somehow mimic the corresponding behavior. The way how living cells allocate, organize and coordinate processing nodes has evolved for billions of years. Investigating this magnificent course might help us to handle the multiple cores computing, which has cut a striking figure in the contemporary parallel computing realm.

The large scale distributed parallel processes occurring in vesicle compartments and the vesicle division functionality enlightened from mitosis of living cells are two of the most outstanding advantages of membrane computing. They allow to underlie the foundation for the construction of highly parallel computation platform whose performance, flexibility and scalability outperforms

traditional sequential counterparts substantially [118]. As a parallel computing paradigm inspired by the structural and functional features of biological membranes, only parallel computing platforms are suitable for the implementation of P systems. More precisely, the limited parallelism of general computers realized by the communication mechanism among the multiple cores of CPU and GPU cannot make full use of the large scale parallelism, non-determinism and other particular attributes that impart an enormous computing potential like creation and dissolution of inner membranes, the self-replication or *autopoiesis* [29] of the whole cell-like entirety that works as a computing unit, the communication by *symport* and *antiport* of objects [4], etc. We would like to remark that programming membrane computing algorithms with high level general purpose languages and executing them on the computer represents just a simulation and not a real implementation of P systems [85].

Several software-based and hardware-based parallel computing platforms have been developed to implement P systems. The first software-based parallel computing platform was constructed using a cluster of computers [22]. This platform achieves good performance and flexibility. Nonetheless, when the size of target P system is increased, the consumption of CPU time and resources caused by the communication between different computers rises dramatically. Moreover, the underlying hardware (a cluster of computers) of this platform cannot be miniaturized closing the way to corresponding membrane computing algorithms to be used in embedded chips and compact controllers which can be employed in robots, automobiles, machine tools, etc. This disadvantage limits the range of applications of such platforms for membrane computing.

Hence, it is important to propose hardware implementations of P systems as specific architectures that do not have the drawbacks related to the traditional ways of implementation. There are two main directions for such research using (1) Field-programmable gate arrays (FPGA) and (2) graphical processing units (GPUs) relying on Compute unified device architecture (CUDA) platform. In the first case a completely new parallel circuit is specially designed to implement some variants of P systems. In the second case the pre-defined CUDA parallel platform is used to simulate P systems. The achieved performance and correspondence is smaller in this case, but the development effort is much lower, so finally it becomes an interesting compromise between traditional computers implementations and a highly parallel one using specialized circuits. Also, when implementing membrane computing models in hardware, the main difficulty comes from the fact that there exists a big number of variations of the basic model of P systems having quite distinct characteristics [88]. This poses a great challenge for the conception of a general computational architecture to implement these various models.

The computation in a P system is a sequence of transitions between configurations. The core problem for implementations is the *object distribution problem* (ODP) that computes one of the multisets of applicable rules to the current configuration and whose application permits to reach the next configuration. This problem is a particular variant of a more general problem that computes the whole applicable set of multisets of rules for a given configuration and it is known to be NP-complete [21]. Known algorithms and heuristics do not parallelize well, so special heuristics were developed in order to quickly compute the desired multiset of rules. We decided to present these heuristics uniformly in terms of multi-criteria optimization, see Sections 4, 5. Another problem for implementations is that in the general case the model is non-deterministic, so an equitable choice among different possibilities should be provided. However, this is very difficult to achieve and in most of the cases this property is not satisfied.

This paper is organized as follows: Section 2 gives a brief description of the capabilities and of the architecture of hardware used, Section 3 recalls the definition of the most general model of P systems, based on the formal framework [35]. Next Section 4 expresses object distribution problem (ODP) in terms of multi-criteria optimization and integer linear programming. Section 5

presents an overview of different simulation approaches, including the Direct Non-deterministic Distribution algorithm (DND) algorithm which is the base for handling non-determinism. Next Sections 6, 7 and 8 give more details on existing simulation approaches. At the end, conclusions and future research directions are discussed.

#### 2 THE SELECTION OF HARDWARE

#### 2.1 FPGA hardware

The FPGA is a reconfigurable hardware allowing to prototype digital circuits. The modification of circuits for FPGA is performed by altering the interconnections between circuit elements using a hardware description language, the most common ones being VHSIC Hardware Description Language (VHDL) and Verilog. The design can be performed on several levels of abstraction, ranging from the switch/transistor level until the behavioral level (corresponding to a Mealy machine [67]).

From structural point of view, an FPGA is an array of configurable logic blocks (CLB) inlaid in the matrix of interconnects. The CLBs work as containers for slice-organized logic cells, which are composed of look-up tables (LUTs) and flip-flops (FFs). The LUTs are used to implement different combinatorial circuits such as basic gates, decoders, encoders and multiplexers. The FFs are the sequential logic components acting as a memory element in the circuit. In order to produce a circuit, the interconnects of CLBs should be reconfigured. The interconnection in FPGA is performed by switch boxes routing signals between its logic blocks. Modern FPGAs use one of the following interconnect technologies: static RAM, flash memory and anti-fuse. The first one dominates the current FPGAs implementations. With the re-programmability, FPGAs comply with the model-oriented hardware implementation quite well.

# 2.2 CUDA-enabled GPU hardware

The multiple computing cores architecture originates from mainframe computers where it was used to improve the clock speed. Nowadays, it is hard to find a PC equipped with only one core. On the other side, the component integration scale of some High-end GPUs has outpaced the CPUs for the booming demand of graphics processing (advanced rendering and 3D vision) [52]. Currently, the GPU is a computing element as powerful as the CPU. Different from FPGAs, there are manufactured parallel architectures in GPUs. The advantage is that developers should just concern about the efficient utilization of these architectures and the drawback is that these frameworks are un-reconfigurable.

Nevertheless, the GPU is not a general processing unit which can handle other computing assignments except for graphics processing. The predicament has changed for the arise of *compute unified device architecture*, known as *CUDA*, from the leading chip vendor-NVIDIA corporation. CUDA is a technology that enables *general-purpose computing on graphics processing units (GPGPU)*. Usually, when referring to CUDA, what is referred is not the parallel computing framework but a GPU supporting CUDA. A CUDA-enabled graphics processing unit is an universal parallel computing device which is suitable for the implementing of parallel algorithm models. The parallel computing behavior of CUDA is based on the execution of multiple compute *kernels* on the GPU. These compute kernels are without physical construction, but based on an abstract parallel programming model. In other words, CUDA does not alter the physical structure of GPU. CUDA programming model is based on *heterogeneous computing*, where the CPU (*host*) is the master node that controls the execution flow and launches kernels on the GPU (*device*) when massive parallelism is required [52]. A kernel is executed by a *grid* of (thousands of) *threads*. The grid is a two-level hierarchy, where *threads* are arranged into *thread blocks* of equal size. Each block and each thread is unequivocally identified by an identifier. In this way, threads and blocks can be distributed easily

to different portions of data, or to compute different instructions. Threads from the same block can be synchronized using *barriers*, while those belonging to different blocks can only be synchronized by the end of the execution of the kernel.

A GPU contains a *global memory*, which has the biggest size, but has the longest access time and a *shared memory*, which is smaller but faster [52]. Although current GPUs contain cache memories, in order to accelerate memory accesses, best performance is achieved when doing it manually. Global memory is accessed by all threads launched in all grids, and also by the host, but shared memory is only accessible by threads in a block. Threads also have fast access to their own registers for single variables, and local memory (which is normally outsourced to global memory). Accesses to memory have to be carefully programmed, so that contiguous portion of data is read by consecutive threads (providing so called *coalesced access*), since this increases the memory bandwidth utilization.

Nowadays the architecture of GPUs is upgraded to *Streaming Multiprocessors* (*SMs*) which are composed of an array of *Streaming Processors* (*SPs*), working as computing cores. A thread set consisting of 32 threads named *warp* is the basic unit which a SM fulfills in its executions. A SM can manage multiple warps which are based on *Single-Instruction Multiple-Thread* (*SIMT*) model in effect. Each thread in a warp should commence its processing at the identical program address concurrently, although after beginning, threads can execute independently abiding by a sequential manner. The parallelism of CUDA is terminated when a warp branches or the memory stalls [61].

#### 2.3 Other hardware

There were attempts to simulate certain types of P systems on micro-processor based architectures [47]. Although the performance of micro-processors is low, they are economical alternatives suitable for the developing of prototypes and verifying the design methods. The drawback is that in most of the cases the parallel nature of P systems is not exploited at all, often leading to inefficient implementations. It could be interesting to use out-of-order (OoO) execution [93] processors to tackle this problem, but this possibility was not investigated yet.

Custom application specific integrated circuits (ASIC) can also be employed to implement P systems. However, no such attempts exit at the moment of the writing of this paper. One of the main reasons is that the flexibility of the hardware platform constructed on ASIC is quite insufficient to adapt to the different variants of P systems. However, such attempts could still be meaningful as they would allow to simulate features of P systems on some tailored circuits with different properties, like low power consumption. Another possible direction is to use ASIC for particular commonly occurring computational cores and combine them with software execution [28, 103].

# 3 THE MODEL OF P SYSTEMS

We suppose the reader to have a knowledge of basic notions from formal language theory and membrane computing. We refer to [37, 87] and [91] for missing details. We will also closely follow [35, 105] for the definitions.

We recall that a multiset can be seen as a set whose elements can have greater than one multiplicity. We will use the string notation for multisets, *i.e.*, a multiset M will be represented by a string where the number of occurrences of each letter, corresponds to its multiplicity in M. We will denote by |M| the size of the multiset M and by  $|M|_a$  the number of elements a in M.

There exist many variants of P systems, see e.g. [85]. In this paper the presentation will be given in terms of the *formal framework for P systems* introduced in [35], see also [104, 105]. This framework is based on the model of *network of cells* specifying the structure and rules to be executed as well as on a set of 4 functions giving the semantics of the system. Different combinations of these parameters allow in most of the cases to construct for a given P system a network of cells that strongly bisimulates it (i.e. one step in the one system is simulated by one step in the other

one). Moreover, in many cases there is a one-to-one correspondence between rules applied in each system, meaning that they are mostly indistinguishable. Hence, the framework for P systems can be seen as a common language to compare different P systems as well as to express notions related to this area. Moreover, other multiset rewriting-based models (like Petri nets) can be easily expressed into this framework giving a possibility to compare corresponding models. Finally, we would like to remark that in what follows we will use the variant of the framework supposing that the system structure does not change in time. An extension of the framework that permits to take into account notions related to P systems with dynamically evolving structure is given in [34], but corresponding definitions are too complex for the purpose of this paper.

#### 3.1 Network of Cells

As pointed out in [33, 35, 104, 105], most types of (static structure) P systems can be seen as variants of parallel multiset rewriting (by using the algorithm called *flattening*). Since multiset rewriting level is not practical for system description and understanding, a higher-level concept called *network of cells* was introduced in [35]. This model augments multiset rewriting with the notion of spatial locations (*cells*) as well as the corresponding operations and it can be seen as a particular interpretation of the symbols. The works [35, 104, 105] define some basic building blocks in terms of network of cells and give several examples of the construction of widespread notions and types of rules in membrane computing using these blocks.

Below, we provide the definition of *network of cells*, taken from in [35]. We remark that the definition from [34] is slightly different, however both models coincide when the structure of the system does not evolve.

*Definition 3.1 ([35]).* A network of cells of degree  $n \ge 1$  is a construct

$$\Pi = (n, V, w, Inf, R)$$

where

- (1) *n* is the number of cells;

- (2) V is an alphabet;

- (3)  $w = (w_1, \ldots, w_n)$  where  $w_i \in V^{\circ}$ , for all  $1 \le i \le n$ , is the finite multiset initially associated to cell i:

- (4)  $Inf = (Inf_1, ..., Inf_n)$ , where  $Inf_i \subseteq V$ , for all  $1 \le i \le n$ , is the *set of symbols occurring infinitely often in cell i* (in most of the cases, only one cell, called the *environment*, will contain symbols occurring with infinite multiplicity);

- (5) *R* is a finite set of rules of the form

$$(X \rightarrow Y; P, Q)$$

where  $X=(x_1,\ldots,x_n), Y=(y_1,\ldots,y_n), x_i,y_i\in V^\circ, 1\leq i\leq n$ , are vectors of multisets over V and  $P=(p_1,\ldots,p_n), Q=(q_1,\ldots,q_n), p_i,q_i, 1\leq i\leq n$  are finite sets of multisets over V. We will also use the notation (omitting  $p_i,q_i,x_i$  or  $y_i$  if they are empty)

$$(1,x_1)\ldots(n,x_n)\to (1,y_1)\ldots(n,y_n);[(1,p_1)\ldots(1,p_n)];[(1,q_1)\ldots(n,q_n)].$$

The above rule is applied as follows: objects  $x_i$  from cells i are rewritten into objects  $y_j$  produced in cells j,  $1 \le i$ ,  $j \le n$ , if every cell k,  $1 \le k \le n$ , contains all multisets from  $p_k$  and does not contain any multiset from  $q_k$ .

By taking for each rule the set of cells that are involved a hypergraph relation, called the *structure* of the system, is induced. Commonly, tree-like (for P systems) or graph-like (for tissue P systems) relations are considered.

The configuration C of  $\Pi$  is defined as an n-tuple of multisets over  $V(u_1, \ldots, u_n)$  satisfying  $u_i \cap Inf_i = \emptyset$ ,  $1 \le i \le n$ .

In order to define the *computation* in network of cells according to some derivation mode  $\delta$  the following functions should be specified:

- $Applicable(\Pi, C, \delta)$  the function taking a system  $\Pi$ , a configuration C and a derivation mode  $\delta$  and yielding the set of multisets of rules of  $\Pi$  that can be applied to C.

- $Apply(\Pi, C, R)$  the function allowing to compute the configuration obtained by the parallel application of the multiset of rules R to the configuration C.

- $Halt(\Pi, C, \delta)$  a predicate that yields true if C is a halting configuration of the system  $\Pi$  (in some derivation mode  $\delta$ ).

- $Result(\Pi, C)$  a function giving the result of the computation of the P system  $\Pi$  when the halting configuration C has been reached.

Then the computation is a sequence of transitions where each transition step  $C \Rightarrow C'$  is defined as  $C' = Apply(\Pi, C, R)$ , for some  $R \in Applicable(\Pi, C, \delta)$ . As usual, this sequence starts with the initial configuration and ends with the final configuration for which the halting predicate Halt yields true. In more formal terms, the result of the computation of a network of cells  $\Pi = (n, V, w, Inf, R)$  working in the derivation mode  $\delta$  is defined as follows (we refer to [35] for more technical details):

$$Result(\Pi) = \{Result(\Pi, z) : w \Rightarrow^* z, Halt(\Pi, z, \delta) = true \text{ and } Halt(\Pi, x, \delta) = false \text{ for any } x : w \Rightarrow^* x \Rightarrow^+ z\}$$

We remark that [35] gives an algorithm to compute the set of multisets of applicable rules, denoted as  $Applicable(\Pi, C, asyn)$ , the algorithm to compute  $Apply(\Pi, C, R)$  and several definitions for Halt and Result functions. The most common way of halting is the total halting, which means that there are no more applicable rules and the most common way of getting the result is to consider the multiset of objects present in the halting configuration at some predefined cell.

At each step, the set of multisets of applicable rules  $Applicable(\Pi, C, asyn)$  can be restricted using a *derivation mode*, denoted by  $\delta$ , which specifies which sub-multisets are chosen for the next step application. The most common example is the maximally parallel derivation mode (max) which is defined as follows:

$$Applicable(\Pi, C, max) = \{R \subseteq Applicable(\Pi, C, asyn) \mid \nexists R' \in Applicable(\Pi, C, asyn) : R' \supseteq R\}.$$

The filter condition states that only non-extensible multisets are considered in this derivation mode. We remark that there might be several such multisets, hence for the application a non-deterministic choice is used to take one of them. We also refer to [105] for a description of several other derivation modes.

*Example 3.2.* Consider the system  $\Pi=(O,w_1,R)$ , having the alphabet  $O=\{a,b,c\}$  and the set of rules  $R=\{r_1:(1,ab)\to(1,abc);r_2:(1,bbc)\to(1,abb)\}$ . Consider the configuration  $C=(1,a^3b^4c^2)$ . Then,  $Applicable(\Pi,C,asyn)=\{r_1,r_1^2,r_1^3,r_2,r_2^2,r_1r_2,r_1^2r_2\}$ . The maximally-parallel set of multisets of rules is the following:

$$Applicable(\Pi, C, max) = \left\{r_1^3, r_2^2, r_1^2 r_2\right\}$$

The application of the multiset of rules  $r_1^2 r_2$  on C yields  $(1, a^4 b^4 c^3)$ .

Example 3.3. Consider the system  $\Pi = (O, w_1, w_2, R)$ , with  $O = \{a, b, c\}$  and  $R = \{r_1 : (1, a)(2, b) \rightarrow (1, b)(2, a); r_2 : (1, b) \rightarrow (2, b)\}$ . Consider the configuration  $C = (1, a^4)(2, b)$ . It is easy to observe that at each step only a single rule is applicable ( $r_1$  or  $r_2$  alternatively). The only possible sequence of rule applications is  $(r_1r_2)^4$  after which no rule is applicable anymore. This sequence moves all

symbols a from cell 1 to cell 2. We remark that the above rules do not rewrite objects, but only move them in the structure.

# 3.2 Examples of P systems

Here we will give the formal framework description of some main variants of P systems that were targeted for an implementation.

*Transitional (cell-like) P systems* [77]. This model considers that cells are organized in a tree structure and uses rules of following type:  $(i, u) \to (i, u')(j, u'')(k_1, v_1) \dots (k_m, v_m)$ , where j is the parent of i and i is the parent of  $k_1, \dots, k_m, m \ge 0$ . When |u| > 1 corresponding rules are called *cooperative*.

Symport/antiport P systems. This variant considers that objects are not transformed but rather moved in a tree-like or graph-like structure. This corresponds to rules of form  $(i, u)(j, v) \to (i, v)(j, u)$  or  $(i, u) \to (j, u)$ .

*Populational Dynamics P (PDP) systems* [13, 92]. The structure of this model corresponds to several trees that have their roots linked together. There are two types of rules: (1) working inside some tree:  $(i, u)(j, v) \rightarrow (i, u')(j, v')$ , where i is parent of j and (2) communication between tree roots:  $(r_i, x) \rightarrow (r_1, x_1) \dots (r_k, x_k)$ , where  $r_1, \dots, r_k$  are the numbers of the corresponding tree roots. Moreover, each rule has a probability associated to it, so the derivation mode is maximally parallel, followed by a probabilistic choice between rules having the same left-hand-side.

Spiking Neural P systems [24, 49]. This model has a graph structure and restricts the alphabet of the system to be a single letter, however permitting and forbidding conditions are replaced by a regular expression check. The rules are of form  $(i, a^k) \to (k_1, a^{x_1}) \dots (k_m, a^{x_m})$ ; (i, E), where E is the regular expression checking for the contents of cell i, a is the single symbol used in the alphabet and  $k_1, \dots, k_m$  are the cells linked to cell i. The derivation mode is sequential at the level of each cell (only one rule per cell is applied) and maximally parallel at the level of all cells.

(Enzymatic) Numerical P Systems [78, 86]. A multiset M can also be seen as a function  $M:V\to\mathbb{N}$ . The model of numerical P systems extends the notion of multiset to  $M:V\to\mathbb{R}^n$ . Hence, the configuration is a vector of real-valued variables and rules are equations describing how to update each variable during each step.

*P Systems with Active Membranes* [36]. This model corresponds to transitional P systems with an additional rule allowing to create new child cells.

# 4 REDUCTION OF THE COMPUTATION STEP TO MULTI-CRITERIA OPTIMIZATION

The computation in P systems corresponds to a finite sequence of transitions between configurations. Each transition  $C \Rightarrow C'$  can be seen as a sequence of 4 steps: (1) computing the set of multisets of applicable rules  $(Applicable(\Pi, C, asyn))$ , (2) restricting it according to the derivation mode  $\delta$   $(Applicable(\Pi, C, \delta))$ , (3) choosing one element from it R and (4) applying R to the configuration C yielding  $C' = Apply(\Pi, C, R)$ . The first step is the most time consuming, as the corresponding problem is generally NP-hard. As we show below that in some cases it is possible to reduce the first 3 steps (the computation of an element from  $Applicable(\Pi, C, \delta)$ ) to a multi-criteria optimization problem. This will allow us to express different algorithms used to compute this step by different authors in a common language for a better comparison. Another theoretical advantage of such reduction is an extensive standard vocabulary and a plethora of solving methods existing in the optimization area, that could be possibly applied for large-scale P systems. We would like to remark

one more time that the presented reductions are not possible in the general case, however they are possible for many concrete cases.

#### 4.1 Preliminaries

A *multi-criteria* optimization problem (MCOP) is an optimization problem that involves multiple objective functions. In mathematical terms it can be stated as

$$\max(f_1(x), f_2(x), \dots, f_m(x))$$

subject to  $x \in X$

where  $m \ge 2$  and X is the set of *feasible* vectors (or solutions). This set is usually defined by some constraint functions. We can also consider the objective function as a vector:  $f: X \to \mathbb{R}^m$ ,  $f = (f_1, \ldots, f_m)$ . For a feasible solution x, the vector z = f(x) is called an objective vector or an outcome [50, 53].

When corresponding functions as well as  $f_i$ ,  $1 \le i \le m$  are linear, we speak about a multicriteria *linear* optimization problem. We also remark that as for classical optimization problems the objective functions are minimized; the other cases like maximization or hybrid min/max can be easily reduced to the minimization one. When further  $X \subseteq \mathbb{N}^k$ , k > 0 and  $f: X \to \mathbb{N}^m$  we speak about an *integer* multi-criteria linear optimization problem (IMCLOP).

In multi-criteria optimization, typically there is no feasible solution that minimizes all objective functions simultaneously. Hence, the main attention is focused on solutions that cannot be improved in any of the objectives without degrading some other objective(s). Such solutions are called *Pareto-optimal*. Formally, they are defined as preimages of maximal elements of the outcomes, which are also called *Pareto front*.

Definition 4.1. A vector  $x \in X$  is Pareto-optimal for a MCOP (defined as above) iff there is no other vector  $y \in X$  for which f(x) < f(y), where u < v iff  $u_i \le v_i$ ,  $1 \le i \le k$ , and  $\exists j, 1 \le j \le m$  such that  $u_j < v_j$ .

Example 4.2. Consider the following problem:

$$\max(r_1, r_2)$$

subject to  $r_1 \le 5$   $r_1 + 2r_2 \le 6$   $r_2 \le 3$   $r_1 \in \mathbb{N}, \quad r_2 \in \mathbb{N}$

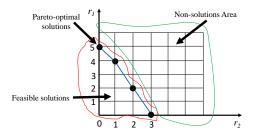

The corresponding feasible solutions and Pareto-optimal solutions are shown in Fig. 1. We note that Pareto-optimal solutions are (5,0), (4,1), (2,2) and (0,3).

Fig. 1. Feasible and Pareto-optimal solutions from Example 4.2.

#### 4.2 Rule choice as IMCLOP

It is not difficult to see that the problem of the computation of elements from  $Applicable(\Pi, C, max)$  can be reduced to IMCLOP. For the first time it was noticed in [5], but without any further development. For simplicity, we consider that  $\Pi$  is a transitional P system and has only one membrane (and no environment). If this is not the case, we can apply the flattening procedure reducing it to one membrane [33, 35]. So  $\Pi = (O, w_1, R)$ .

Let  $R = \{r_1, \dots, r_m\}$  and  $O = \{a_1, \dots, a_n\}$ . Consider that  $r_i : (1, u_i) \to (1, v_i), 1 \le i \le m$ . Let C be the current configuration and let  $C_a = |C|_a, a \in O$ .

We will consider a set of variables  $x_i$ ,  $1 \le i \le m$ , that indicate the cardinality of corresponding rules in some parallel multiset  $\mathcal{M} \in Applicable(\Pi, C, asyn)$ ,  $|\mathcal{M}|_{r_i} = x_i$ ,  $1 \le i \le m$ . Then the feasible set X of (asynchronous) solutions is defined by the following inequalities:

$$\sum_{i=1}^{m} |u_i|_a x_i \le C_a, \quad \forall a \in O, \tag{1a}$$

$$x_i \in \mathbb{N}, \quad 1 \le i \le m,$$

(1b)

Inequalities (1a) state that the sum of all consumed objects is included in C. Technically, for each object  $a \in O$  it is verified that the weighted sum (by the number of symbols a in the left-hand-side) of rule cardinalities is smaller or equal than the number of objects a in C. We remark that system (1) can be also seen as a system of Diophantine equations and corresponding solutions are exactly describing the set X of feasible solutions.

The IMCLOP corresponding to the computation of  $Applicable(\Pi, C, max)$  is defined by:

$$\max(x_1, \dots, x_m)$$

subject to  $(x_1, \dots, x_m) \in X$

It should be clear that Pareto-optimal solutions represent exactly the multiplicities of rules for some maximally parallel solution.

Example 4.3. Consider the system  $\Pi = (O, w_1, R)$ , with  $O = \{a, b, c\}$  and  $R = \{r_1 : (1, ab) \rightarrow (1, abc); r_2 : (1, bbc) \rightarrow (1, abb)\}$ . Consider the configuration  $C = (1, a^5b^6c^3)$ . Then, the constructed IMCLOP corresponds to the one given in Example 4.2

So this system has 4 Pareto-optimal solutions: (5,0), (4,1), (3,3) and (0,3), corresponding to multisets of rules  $r_1^5$ ,  $r_1^4r_2$ ,  $r_1^2r_2^2$  and  $r_2^3$ , which are exactly the maximal multisets of rules applicable to C.

# 4.3 Tentative solutions

One of the traditional approaches to solve multi-criteria optimization problems is called *scalarization*. It consists in reducing the corresponding MCOP to a single objective optimization problem by using a real-valued scalarizing function involving the objective functions and additional scalar or vector parameters and variables. This can also imply additional restrictions to the feasible set based on the newly introduced variables.

One of the "simplest" methods to solve multi-criteria problems is the weighted sum method, where we solve the following single objective optimization problem

$$\max_{x \in X} \sum_{k=1}^{m} \lambda_k f_k(x) \tag{3}$$

The weighted sum problem (3) is constructed using the scalar vector product of the vector of objective functions f and the vector of non-negative weights  $\lambda \in \mathbb{R}^m$  as a parameter. It is known that it allows to compute all Pareto-optimal solutions for convex problems by varying  $\lambda$  [27].

In the literature on P systems some simple variants of the weighted sum method can be found. In [3, 89] the vector  $\lambda = (1, ..., 1)$  is considered (so the objective function is the sum of all variables). However, in this case only maximally parallel rulesets having a maximal number of rules are obtained. In terms of the formal framework [35] this corresponds to  $max_{rules}max$  derivation mode.

Another attempt was done in [20, 21] where the parameters  $\lambda_k$  correspond to the size of the left-hand-side of rules ( $\lambda_k = |u_k|, r_k : u_k \to v_k$ ). Such optimization problem finds only maximally parallel solutions involving the maximal number of objects, corresponding to  $max_{objects}max$  mode in terms of the formal framework.

In [71] the set of maximally parallel multisets of rules is expressed as solutions of a system of Diophantine equations (roughly equations (1a)) with an additional constraint to be satisfied on a solution, expressed as another system of Diophantine equations.

Finally, in [9] the set of maximally parallel multisets of rules can be expressed as solutions to a system of equations defining some Diophantine sets. While the construction is similar to the one we give below, it is not trivial to manipulate Diophantine sets and it is not clear how to express the constraints as a single system of equations. Below, we show how to handle this problem by using same construction as for handling multiple "either-or" constraints in integer linear programming.

As above we consider that  $\Pi$  has only one membrane (and no environment). So,  $\Pi = (O, w_1, R)$ . Let  $R = \{r_1, \dots, r_m\}$  and  $O = \{a_1, \dots, a_n\}$ . Consider that  $r_i : (1, u_i) \to (1, v_i), 1 \le i \le m$ . Let C be the current configuration and let  $C_a = |C|_a, a \in O$ .

In addition to the  $\lambda$  vector above we introduce an integer parameter  $M \in \mathbb{N}$  having a value that is sufficiently big (in fact it should be greater than the maximal possible value of any variable  $x_i$ ,  $1 \le i \le m$  of any feasible solution). We remark that in general case of maximal parallelism it is impossible to limit the maximal values of variables, however, for practical applications, it is often possible to find such a bound.

We will modify the system (1) to construct a system of inequalities whose integer solutions will be maximally parallel multisets of rules for the configuration C.

$$\sum_{i=1}^{m} |u_i|_a x_i \le C_a, \quad \forall a \in O, \tag{4a}$$

$$\sum_{i=1}^{m} |u_i|_a x_i + |u_k|_a + M z_a^k \ge C_a + 1, \quad 1 \le k \le m, a \in O, |u_k|_a > 0, \tag{4b}$$

$$\sum_{a \in O} z_a^i = N_i - 1, \quad 1 \le i \le m, \ N_i = \sum_{a \in O} \operatorname{sgn}(z_a^i)$$

(4c)

$$x_i \in \mathbb{N}, \quad 1 \le i \le m,$$

(4d)

$$z_a^i \in \{0, 1\}, \quad 1 \le i \le m, a \in O.$$

(4e)

Inequalities (4a) are the same as (1a) and they state that the sum of all consumed objects is included in C.

Inequalities (4b) state the maximality property of the rule set defined by  $x_1, \ldots, x_m$ . It verifies that for each rule there exist at least one object whose remaining quantity is not sufficient to apply this rule. They are based on multiple "either-or" constraints representation in ILP. The big value of M and the inequalities (4c) ensure that only one constraint from (4b) will be considered (the other ones will be satisfied because of the big value of M).

Hence, any solution  $x_1, \ldots, x_m$  satisfying the system of inequalities (4) corresponds to a Paretooptimal solution of (3), hence to a maximally parallel rule set  $\mathcal{M} = r_1^{x_1} \ldots r_m^{x_m}$  applicable to

configuration C. We also remark that from the construction given above, it immediately follows

that system (4) is Diophantine.

Example 4.4. Consider the system  $\Pi = (O, w_1, R)$ , with  $O = \{a, b, c\}$  and  $R = \{r_1 : (1, abc) \rightarrow (1, ab); r_2 : (1, a) \rightarrow (1, bb); r_3 : (1, b) \rightarrow (1, cb)\}$ . Consider the configuration  $C = (1, a^2b^3c^2)$ . Then, we construct an ILP according to the rules above (we recall that M is a big integer number):

Derived from (4a):

$$x_1 + x_2 \le 2$$

$$x_1 + x_3 \le 3$$

$$x_1 \le 2$$

Derived from (4b) for  $r_1$ :

$$x_1 + x_2 + 1 + Mz_a^1 \ge 3$$

$$x_1 + x_3 + 1 + Mz_b^1 \ge 4$$

$$x_1 + 1 + Mz_c^1 \ge 3$$

Derived from (4c) for  $r_1$ :

$$z_a^1 + z_b^1 + z_c^1 = 2$$

Derived from (4b) for  $r_3$ :

$$x_1 + x_2 + 1 \ge 3$$

Derived from (4b) for  $r_3$ :

$$x_1 + x_3 + 1 \ge 4$$

It is not difficult to see that this system has 3 solutions: (2, 0, 1), (1, 1, 2) and (0, 2, 3), corresponding to multisets of rules  $r_1^2 r_3$ ,  $r_1 r_2 r_3^2$  and  $r_2^2 r_3^3$ , which are exactly the maximal multisets of rules applicable to C.

We remark that all solutions of (4),(3) might be tedious to obtain. For the simulation purposes, only one such solution is necessary.

As previously mentioned, using the weighted sum scalarization technique it is theoretically possible to reach any single point from the Pareto front by choosing appropriate values of the parameter vector  $\lambda$ . However, by using equations (4b) it becomes much easier to chose corresponding parameters as the feasible set is restricted only to Pareto-optimal values. For example, using max  $x_1$  as objective function with the constraints from Example 4.4, would yield the solution (2,0,1). By using  $\min(x_1+x_2+x_3-5)$  as the objective function, the solution (0,2,3) is obtained (the above constraint allows to consider only multisets of rules of size 5).

In the literature on P systems, there are other examples of the construction of a single Paretooptimal solution having certain properties. One of them is the DND algorithm introduced in [71] for the FPGA simulations that we discuss below.

In what follows, we explain briefly the functioning of the DND algorithm in the view of equations (1). First a random rule permutation is computed (corresponding to a random permutation of variable indices). Next, during the forward step a random value (bounded by the number of possible applications) for the number of each rule applications is taken. This corresponds to finding the values of  $x_i$ , satisfying the constraints (1a). Finally, during the backward step, the frequency of each rule is increased until it cannot be applied anymore. This step corresponds to the elimination of the dominated, *i.e.* smaller, solutions for the system (1) yielding only Pareto-optimal ones.

The described procedure can also be seen as a combination of scalarizing and of the lexicographic method, which is a method from the family of a priori methods for multi-criteria optimization. More precisely, it corresponds to a solution of a series of optimization problems, each of them bounded by the parameter corresponding to the choice of the maximal rule multiplicity for the forward step. The backward step also corresponds to a series of optimization problems that just reach the maximum for each component (like in the lexicographical method).

A simpler variant of the DND algorithm that does not perform the initial rule permutation can be found in [60, 98, 100]. Other variations of DND algorithm were used for CUDA-based simulations and are discussed later. A different approach is used in [106]. It supposes that for a P system  $\Pi$  working in the derivation mode  $\delta$  there exists an easily computable function  $NBVariants(\Pi, C, \delta)$  that for any configuration C gives the number of solutions of (4). Next, it also supposes that there exists an easily computable function  $Variant(\Pi, C, \delta, n)$  that for each integer n (up to the corresponding value) yields the corresponding solution (the used method is similar to the decoding of a number in the combinatorial number system). It is clear that such functions do not exist for any variant of P system. The papers [88, 106] give some sufficient relations between rules that allow to construct the above functions for a P system working in set-maximal (smax) derivation mode.

#### 5 IMPLEMENTATION OF P SYSTEMS USING HARDWARE

The discussion about the hardware implementation of membrane computing concerns mainly the simulation of concrete variants (sometimes even examples) of P systems using a dedicated hardware (for ASIC and FPGA) or firmware (for CUDA). In most of the cases a (single) particular class of P systems is simulated. The simulator is composed from two parts: (1) the hardware simulator for a concrete system and (2) the software generator of hardware simulators, which based on input parameters (rules, membranes, initial configuration etc.) generates the code for the dedicated hardware simulator. In this section we will mainly discuss the structure of the corresponding hardware simulators, as the generator part is more-or-less following standard compiler construction techniques. We will concentrate on three points, which are the most important for a hardware implementation: (a) the representation of the configuration (multisets of objects and the membranes), (b) the representation of rules and their parallel application and (c) handling of the non-determinism.

#### 5.1 Data organization

Membranes. We remark that there are no compartments in silicon circuits, hence the notion of membranes is relatively difficult to represent directly. Nevertheless, according to [85], a membrane is just an idealized concept without internal structures. The main functionality of membranes is to perform a topological division of the space allowing P systems to compute in a distributed manner (based on an correspondence between the membrane and its contents). Hence, the spatial placement and size of membrane are not important, only the inter-relationship among them matters. Moreover, it is known that any membrane structure can be reduced (flattened) to just a single membrane, see [33, 35] for more details. The existing hardware simulators adapt in most cases this last point of view, where the membrane structure is not physically implemented on the device. As exceptions from this rule we cite [82] and [73] (region-based), which implicitly implement the membrane topology by using dedicated buses and message passing in the corresponding circuits.

Configuration. The representation of the configuration in all cases is done as a vector of non-negative integers (stored in the memory/registers of the device). We remark that this vector corresponds to a flattened system, so it is relatively big and sparse, as it encodes each object/membrane pair. For performance reasons, it is physically split in several places to be closer to the processing units (as routing is relatively expensive). In the case of [73, 82] it can be argued that corresponding

parts are internalized into the corresponding region circuit, as the access to corresponding values is not direct and it is done by message passing. In CUDA, only the portions of the array representing the configuration in the corresponding membranes to be processed are loaded by the cores.

Evolution Rules. As it can be seen from definition 3.1 in the simple case (without permitting and forbidding) rules can be defined by 2 integer vectors indicating the multiplicities of corresponding objects in the left-hand-side and right-hand-side of each rule. This gives a natural rule representation as two vectors stored in the memory/registers. Then a specific circuit/module verifies the applicability of rules and performs their application. Most variants of hardware implementations use this idea, however in [70, 72, 82] each rule is encoded in hardware as a specific circuit that verifies the needed resources and performs the rule application. In the case of P systems with active membranes, there might be several cells with the same label, so the corresponding CUDA simulator uses a split representation: 2 integer vectors, as above, for all rules, and an index array with one position per rule giving for each cell the rules it contains.

# 5.2 Object Distribution Problem and Non-Determinism

The hardware implementation of P systems faces the problem of the computation of the applicable rule set according to some derivation mode (usually maximally parallel). More precisely, an efficient way to compute and represent an element from  $Applicable(\Pi, C, \delta)$  is required [88, 106]. The difficulty of the problem is that rules can compete for same objects, so increasing the number of occurrences for one rule, may decrease the application possibilities for another one. Another important problem is to ensure that a non-deterministic choice among all possibilities is performed. In [41, 44, 57, 60], hardware architectures aiming at parallel processing and communication, and the application of rules are developed. In [11], a formal exposition of non-deterministic evolution in transition P systems was suggested.

We call the first problem as *object distribution problem* (ODP). It consists in the computation of the set  $Applicable(\Pi, C, \delta)$  (or of an element from this set). As discussed in Section 4 in terms of multi-criteria optimization this corresponds to the computation of the corresponding Pareto front (or an element of it).

In [71] different algorithms solving ODP are classified in *direct* and *indirect* ones. In the direct approach, the corresponding multiset is directly constructed by the algorithm. In terms of MCOP this corresponds to a particular fixed scalarization. The indirect approaches are based on the observation that the solution number is finite because the solution space is bounded by the size of the configuration. Hence, a heuristic or brute-force approach can be used to explore this bounded space. However, since it is an overestimation, there might be visited elements that are not valid solutions. Hence, the algorithms are iterative and explore the whole space until a valid solution is encountered. In terms of MCOP this corresponds to different searches through the space limited only by the maximal values for each axis.

Sometimes it is not easy to classify an algorithm in one of these categories. We will classify an algorithm as a direct approach if its main goal is to construct a valid multiset of rules. Otherwise, if an algorithm is exploring different solutions until it reaches a valid one, it will be classified as indirect. We will use this classification to overview different strategies for ODP solution known in the literature.

Indirect approaches. Generally, the enumeration of all possible solutions and their verification one by one until a correct solution is obtained is the simplest method for the indirect approach [31]. Before the first correct solution is obtained, some invalid solutions should be rejected. This approach is called *indirect straightforward approach* [71]. Taking into account that it is not viable to enumerate all possible solutions for many problems, the feasibility of the approach is low. However,

the performance of the algorithm suggests its use as to compute the floor values for the object distribution problem. Another indirect approach discussed in [71, 73] called *indirect incremental approach* investigates a strategy generating possible solutions in rounds. Other attempts based on a similar idea but with different rule elimination strategies were done in [30, 39, 46, 48, 98, 99]

*Direct approaches.* In contrast to indirect approaches, the direct approach fabricates a solution straightforwardly rather than identifying a number of possible solutions before a solution is confirmed.

The simplest approach is the *direct straightforward approach*. As defined in the paper [71], in this approach "all the solutions to the object distribution problem are given as input, and one of these solutions is simply selected at random". While in the same paper it is argued that such approach is infeasible for an arbitrary configuration and rule types, it can still be applied in a big number of cases. As shown in [88, 106], if at each step the number of solutions can be expressed as a the number of words of some length in a regular language, then it becomes possible to compute the solution only based on its number. In [106] it is shown that the corresponding class of P systems is quite large and also that this method is particularly interesting for bounded derivation modes like the set-maximal derivation mode (called also flat mode) where the rules are chosen in a set-maximal way (instead of the multiset maximal way).

Another variant of the direct approach is the *Direct Non-deterministic Distribution algorithm* (DND) proposed in [71]. A similar algorithm can also be found in [38, 40]. This algorithm works in 2 phases. At the first phase all rules (initially randomly shuffled) except one are selected to be applied a random number of times below its maximal applicability value. In the second phase, all the rules are taken in the converse order (with the first one being the rule excluded at the previous step) and their applicability is increased up to the maximal still possible value. A variant of DND, named DND-P, became popular in the simulation of Population Dynamics P (PDP) systems [65]. Together with another algorithm Direct distribution based on Consistent Blocks Algorithm (DCBA) [63] it was employed for the engine of the PDP system simulator on CUDA [62].

Non-determinism. One of the difficulties of the above approaches is the handling of the non-determinism. From the formal point of view, the non-determinism corresponds to a random equiprobable choice of an element from the set of all applicable multisets of rules ( $Applicable(\Pi, C, \delta)$ ). In the case of indirect approaches, due to the iterative nature of the algorithms, it is not easy to argue that each possibility has the same probability to occur. We would state that solutions containing a smaller number of different rules have a higher chance to be selected. In the case of DND algorithm and related variants, it looks like the obtained solution tends to be an equiprobable choice. However, the corresponding articles do not give such a proof and there are some unclear points, which do not allow us to affirm this fact. Up to now, the only algorithm that is performing a truly non-deterministic choice is the one described in [88, 106]. However the corresponding implementation is limited to some particular derivation modes and particular classes of P systems.

#### 6 AN OVERVIEW OF EXISTING FPGA SIMULATIONS

With the advent of reconfigurable hardware which realizes the idea of modifying the hardware circuits by programming, conceiving a novel circuit simulating an innovative processing paradigm is no longer an exceedingly hard task. The first attempt to use FPGA reconfigurable hardware to simulate P systems dates back to 2003 [82]. Since then two simulation approaches emerged, considering regions or rules as basic processing units.

# 6.1 Region-based Simulations

In the region-based simulation approach rules and objects from different membranes are physically located in different places of the circuit, while those from the same membrane are physically close and well connected. The biggest problem is to ensure the correct communication of objects between membranes as this requires a global level synchronization. As advantage, the obtained system is highly scalable and robust. Below, we give two examples of region-based simulations.

In contrast, the rule-based implementation approach discussed later explicitly represents the evolution rules as processing units and multisets of objects as register arrays, while membranes and regions are represented implicitly as logical constructions existing between those processing units and data structures.

6.1.1 Petreska and Teuscher simulation. Petreska and Teuscher designed the first FPGA circuit simulating membrane computing (more precisely transitional P systems) [82]. They could realize several interesting features like communication to inner membranes, priorities between rules and proposed ideas how to simulate membrane creation and dissolving mechanism in integrated circuits. This work inspired the successors to engage in this challenging and breathtaking field to advance the development of hardware simulation of P systems. In their simulation they made two strong assumptions: the application of evolution rules in each membrane is not done in a maximally parallel but in a sequential manner (but still keeping a parallelism at the system level); the non-deterministic evolution of configuration is substituted by a deterministic transition following a predetermined order. Such computational step corresponds to an ILP with the subject function as a weighted sum of variables with predefined fixed weights.

In theory, membranes are borders without internal structures and material consistence. In this implementation, the membrane structures represent regions on the circuit containing the enclosed substances, i.e., the multisets of objects, evolution rules and children membrane architectures. The objects exchange among membranes is a kind of bi-directional traversing behavior. In case of the possible objects exchange between regions, the communications are made by data buses connecting to different parts of hardware representing inner membranes. To avoid the multiple buses used to connect the parent membrane to its plural children membranes, a single bus links all the children membranes before it connects to the parent membrane. Hence, the communication is limited to parent-child membranes and there is no object exchange among children membranes or non-immediate contained membranes.

The representation of the multisets of objects is implemented by using registers. Different registers just preserve different multiplicities of objects. A register does not store the objects but only a number indicating the multiplicity of each object. The order of these registers is in accordance with the lexicographic order of the alphabet of objects. The recognition of an object is indirectly realized by examining the position of the register storing the multiplicity of this object. An evolution rule defined here is in the form of  $u \to v(v_1, in_i)(v_2, out)$ , where  $v_1$  is the string to be sent into lower-immediate membrane labeled  $i, v_2$  will be sent to upper-immediate membrane. The treatment employed to deal with the formulation of evolution rules is storing the rule's left-hand side and right-hand side into different registers separately. A particular module is designed to determine whether a rule is applicable. This module compares the left-hand side of a rule u with the multiset of objects w present in the current membrane. If and only if  $u \le w$ , this rule is applicable and this module will generate a signal Applicable = 1. Input all the Applicable signals to an OR gate, the result of this logical gate can used as a monitor to identify whether the evolution reaches halt configuration.

The transition of configurations of P system is realized deterministically and sequentially, which is different from the general model. The consecutive transformation of configurations is regarded as

the evolution process. This evolution process is decomposed into micro-steps and macro-steps. The application of rules enclosed by membranes is performed in terms of a predefined sequential order. This deterministic execution of rules is conducted in micro-steps sequentially. If a selected rule is applicable, the left-hand side of the rule u will be removed. Then the right-hand sides v,  $v_1$  and  $v_2$  is stored in corresponding registers. The objects from the upper immediate membrane will be preserved in another register. Although the micro-steps are carried out deterministically, they are performed simultaneously in all membranes, until there are no applicable rules. The micro-steps terminates when there are no applicable rules, i.e. the halt condition is reached. All the registers are updated in line with associated rules in macro-steps.

This implementation considered and respected the priorities of applicable rules at the beginning of each micro-step. By labeling the applicable rules with higher priorities and storing the corresponding labels, applicable rules are executed in accordance with their respective priorities. Besides, two additional features of P system, the dissolution and creation of membranes, are simulated. When a rule with membrane dissolving function is applied, its contents are owned by its upper immediate membrane, setting the membrane *Enable* signal of the relevant membrane to "0". However, the connections and registers defining the dissolved membrane still exist. This scheme gives rise to a disadvantage that the hardware resources cannot be released. The creation of new membranes is executed in the initialization process of the P system since all the information about new membrane is known from the specification of the system. The created membranes are inactive until membrane creating rules invoke them.

6.1.2 Nguyen simulation. In this implementation, a parallel computing platform simulating membrane computing based on FPGA named Reconfig-P is developed [69, 74]. Reconfig-P is fabricated on the basis of the region-oriented idea that regions work as the computational entities communicating objects through message passing. The functionality of these regions is extended by the included set of evolution rules. P Builder, the software component of Reconfig-P, specifies the P system concerned in software, converts the specification of P system written in Java to Handel-C (a hardware description language) source code. Software simulation of the circuits to be constructed is supported by P Builder to test the functionality of circuits before mapping the code to hardware circuits.

The execution of a evolution step is divided into two phases: object assignment phase and object production phase [69]. The maximal instance of each rule in a region is determined in the object assignment phase. The update of multiplicity of objects is accomplished in the object production phase. The maximal instance of the rules with higher priorities is computed before the rules with lower priorities. Note that the consumption of objects for rules with higher priorities performed during the object assignment phase to save clock cycles. It is assumed that all rules are assigned relative priorities. The priority between rules is implemented as the temporal order which should be respected by region processing units in the assignment phase. Rules with same priority are executed concurrently. The temporal order is determined at compile-time. The rules are applied according to their priorities in rounds until no rules are applicable using the indirect iterative approach. Under this circumstance, the applicability of each rule is non-stationary because of the existence of priorities. To avoid processing inapplicable rules, the applicability status of each rule is checked at the outset of the assignment phase and immediate after a applicable is applied to consume some objects.

The objects traversing behavior is the origin of communication between regions. The update of multiplicity of objects caused by rules with and without traversing behavior is completed in the object production phase. When different region processing units update the multiplicity value of the same object at the same time, a conflict occurs. To handle this conflict, in [69] two solution

strategies, the *space-oriented strategy* and the *time-oriented strategy* are proposed. Table 1 and 2 summarize the different strategies of two resource conflict resolutions and their modifications in the rule-based and region-based design [70, 72]. In order to simplify the exposition of processes of rule-based and region-based implementations of P systems, tables are designed to delineate the relevant details, which will be given below.

Table 1. The comparison of the time-oriented and space-oriented conflict resolution

| Strategy                | Resource conflict resolution                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Time-oriented strategy  | (a) construct a conflict matrix in which each row is a quadruple $(p,q,r,s)$ . $p$ is the object competed by multiple rules. $q$ is the region where $p$ is produced or consumed. $r$ is the set of the conflicting rules, $s$ is the size of set $s$ . (b) insert delay statement among conflict rules such that the updating operations of multiplicity of $s$ 0 can be executed in distinct clock cycles. The number of delays is equal to $s$ 1. |  |

| Space-oriented strategy |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

Table 2. The differences of the conflict resolutions adopted in two design modes

| Item                   | Time-oriented strategy                                                                                                                                                                                                                                                                      | Space-oriented strategy                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rule-oriented design   | The interleaving operation can be determined at compile-time and it can be hard-coded into the HDL source.                                                                                                                                                                                  | Need a multiset replication coordinator to coordinate the multiplicities stored in the copy registers.                                                                                                                                                                                                                                                                                                                              |

| Region-oriented design | as external objects, otherwise the objects are internal objects. The interleaving merely caused by the production of internal objects can be identified at compile-time. To retain the independence of region processing units, the interleaving induced completely or partially by the re- | The role of the multiset replication coordinator in rule-<br>oriented design is played by the region processing units.<br>The existing register storing the multiplicity received<br>from the associated communication channels in the<br>considered region can be assigned to those processing<br>units which sending objects to the considered region<br>to write the new values of of the objects competed by<br>multiple rules. |

The extensibility of the region-based design is the consequence of the representation of membranes as processing units interacting with two region processing units corresponding to inner and outer regions. This allows to achieve a strong separation of the processing logic inside different membranes and the independence of the communication. Thus, adding additional elements to the system does not lead to the redesign of the remaining part of the system.

#### 6.2 Rule-based simulations

Rule-based approaches consider evolution rules as processing units performing the update of multiplicities and of the membrane structure.

6.2.1 Nguyen simulation. Every rule in all regions of the P system is represented as a processing unit synchronized by a global clock that implements the parallel processing. However, a processing unit does not correspond a concrete hardware component but rather to a potential infinite while loop which contains the code related to the rule application using Handel-C. The information associated to execution and synchronization is contained in processing units as well. Each rule processing unit in a region is linked to the array of registers containing multisets of objects. The membrane inclusion relationships can be described with the connections between processing units and arrays. Generally speaking, a rule processing unit in a region is linked to the objects array located in the same region with the rule processing unit. If there are objects traversing regions which imply the containment, connecting the rule processing unit to the object array to which

the rule will send objects contained in different region. This procedure permits to represent the membrane inclusion. The rule execution is split into *preparation phase* and *updating phase*. We compare the two designs (the rule-based and the region-based) of Nguyen's implementation in Table 3.

Table 3. The comparison of the rule-based and region-based design of Nguyen's implementation

| Object                                     | Rule-based Design                                                                                                                                                                                                                                                                                                                                                                                                                          | Region-based Design                                                                                                                                                        |