# GaN Schottky diode on sapphire substrate for THz frequency multiplier applications

Giuseppe Di Gioia, Mohammed Samnouni, Vinay Kumar Chinni, Priyanka Mondal, Jeanne Treuttel, Malek Zegaoui, Guillaume Ducournau, Mohammed Zaknoune, Yannick Roelens

# ▶ To cite this version:

Giuseppe Di Gioia, Mohammed Samnouni, Vinay Kumar Chinni, Priyanka Mondal, Jeanne Treuttel, et al.. GaN Schottky diode on sapphire substrate for THz frequency multiplier applications. Superlattices and Microstructures, 2022, 164, pp.107116. 10.1016/j.spmi.2021.107116. hal-03542163

HAL Id: hal-03542163

https://hal.science/hal-03542163

Submitted on 22 Jul 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

GaN Schottky diode on sapphire substrate for THz frequency multiplier applications

# Giuseppe Di Gioia<sup>1\*</sup>, Mohammed Samnouni<sup>1</sup>, Vinay Chinni<sup>1</sup>, Priyanka Mondal<sup>2</sup>, Jeanne Treuttell<sup>2</sup>, Malek Zegaoui<sup>1</sup>, Guillaume Ducournau<sup>1</sup>, Mohammed Zaknoune<sup>1</sup>, Yannick Roelens<sup>1</sup>.

<sup>1</sup> University of Lille, CNRS, Centrale Lille, Univ. Polytechnique Hauts-de-France, UMR 8520 - IEMN Institut d'Electronique de Microélectronique et de Nanotechnologie, Lille, France

<sup>2</sup> LERMA, Laboratoire d'Études du Rayonnement et de la Matière en Astrophysique et Atmosphères

\* giuseppe.di-gioia@iemn.fr

# <u>Abstract</u>

Gallium Nitride, because of its high breakdown field, and peak and saturated electron drift velocity, high chemical stability and high thermal conductivity, is a very promising material as candidate for Schottky varactor diodes for next-generation high-power frequency multipliers. Similarly to the huge interest in the field of HEMT for high frequency and power application, GaN Schottky diodes is of a high interest for the next technological step for frequency multipliers for THz generations, replacing GaAs Schottky diodes. Due to a lack of research focused on GaN Schottky diodes for frequency multiplication, the design and fabrication of GaN frequency multipliers remains a technological challenge. In this paper, we present GaN Schottky diodes fabricated on a heteroepitaxial GaN on sapphire. The barrier height obtained is around 0.53 eV, and it increases up to 0.73 eV after Schottky contact annealing; and the ideality factor is equal to 1.1 before annealing and 1.2 after annealing. The resulting series resistance is very low,  $7\Omega$  and  $1\Omega$ , before and after annealing, respectively.

Keywords: GaN, Schottky diode, frequency multiplier, THz

## 1. Introduction

In the field of THz frequency generation, the only technology that has proven its potentials relies on the frequency multiplier principle [1]. A GaAs-based frequency multiplier chain delivers state of the art performance with an output power of 18  $\mu$ W obtained at 2.58 THz [2] and about 1 mW at 1 THz [3]. However, due to the technological limitations of GaAs (intrinsic electric field breakdown limitation and low thermal conductivity), this impressive technology cannot yet reach the requirements for mass-market applications. Gallium Nitride (GaN) was proposed as candidate to substitute GaAs, due to its higher breakdown electric field combined with its high thermal conductivity [4]. These two advantages are expected to yield a power handling capability of a GaN Schottky diode almost one order of magnitude larger than its GaAs counterpart [5].

Though great progress has been made in the last two decades [6–8], obtaining high frequency performances from a vertical device such as a GaN Schottky diodes remains still a great technological challenge [1]; the reason to this may be attributed to the technological difficulties of obtaining defect-free crystalline GaN and to the lack of basic research oriented toward the optimization of GaN Schottky diodes for frequency multiplier circuits.

In this article, we report a quasi-vertical GaN Schottky diode with low series resistance and high breakdown voltage, as well as its electrical characterization.

#### 2. Material and device fabrication

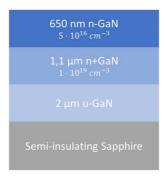

The GaN epitaxial layers used in this study (Figure 1) were grown by MOCVD on c-plane sapphire substrate. Given that the optimization of the process is characterized by a high consumption of material, it has been decided to first develop the process with a "low-cost" substrate such as Sapphire. With respect to the application, silicon carbide (SiC) substrate is the substrate of choice for thermal management. Therefore, after the present process development on Sapphire is completed, it is planned to transpose these works on SiC substrate. A 2  $\mu$ m unintentionally doped GaN was grown first then 1.1  $\mu$ m thick n<sup>+</sup> GaN layer highly doped at 1×10<sup>19</sup>.cm<sup>-3</sup> was grown to achieve low specific contact resistance and low series resistance and a 650 nm n<sup>-</sup> GaN (5×10<sup>16</sup>.cm<sup>-3</sup>) acted as active layer. All the lithographic steps in the process were performed through e-beam lithography.

After laser cutting, the sample was thoroughly cleaned with IPA and acetone and ultra-sonication. Then, a  $SiO_2$  layer was deposited on the GaN surface in order to be used as a hard mask for mesa etch.  $SiO_2$  is patterned using negative resist; after developing, the mask was transferred to the  $SiO_2$  layer by  $SF_6$  dry etch. The remaining resist was subsequently removed by  $O_2$  plasma. Next, using  $Cl_2$ -based ICP dry etching, the diode mesa was defined up to the  $n^+$  GaN layer with a total etch of 750 nm The ohmic metallization is deposited 100 nm inside of the  $n^+$  GaN layer doped at  $1 \times 10^{19}$ .cm<sup>-3</sup> in order

Figure 1. Schematic view of GaN epitaxy used in this study

to ensure a low specific contact resistance.

The ohmic contact was then fabricated with standard lift-off technique. Before metallization, the sample was treated with an HF solution to remove oxidation and contaminants. Then, a multilayer of Ti/Al/Ni/Au was evaporated onto the sample and lifted-off. Afterwards, the sample was annealed with a rapid thermal annealing (RTA) at 850°C.

Before Schottky contact definition, the remaining  $SiO_2$  was removed and the interested semiconductor surface was treated with BOE solution and plasma etching. Then, a Pt/Au contact was deposited through e-beam evaporation.

This process allows the fabrication of planar Schottky diodes with diameters ranging from 1400 down to 44  $\mu$ m.

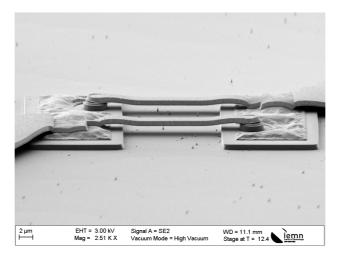

Figure 2. Sub-micronic anti-parallel diodes

Quasi – vertical submicronic diodes are being fabricated under the same process flow layout: after Schottky contact deposition, negative resist is used to define the isolation patterns. After developing, the sample is dry etched ( $Cl_2$ -based plasma) with about 1  $\mu$ m down to the undoped GaN layer, resulting in an isolation of the diodes. Subsequently, vias are opened to deposit metal pads. The last step consists in the realization of the air-bridge (Ti/Au, 200/600 nm) that will connect the Schottky and ohmic contacts to their respective metal pads. The choice of the air-bridge is fundamental because this approach allows to minimize parasitic resistances and capacitances.

Two different samples were fabricated and characterized: sample A, with Schottky contact "as deposited", i.e., with no thermal annealing performed, and sample B, with annealing of the Schottky contact at  $400^{\circ}$ C for 5 minutes. On both samples, three diodes with different diameter were characterized (140, 70 and 44.28 µm).

#### 3. Results and discussion

3.1 C-V Characteristics

The capacitance of a meal-semiconductor junction as a function of voltage is described by

$$\frac{A^2}{C^2} = \frac{2 \cdot \left(V_{bi} - V - \frac{k_B T}{q}\right)}{q \cdot \varepsilon_s \cdot \varepsilon_0 \cdot N_d}$$

where A is the contact area,  $V_{bi}$  is the built-in voltage, V is the applied voltage,  $N_d$  is the donor concentration,  $\varepsilon_s$  is the dielectric constant of the semiconductor and  $k_B$ , T,  $\varepsilon_0$  and q are Boltzmann constant, the temperature, the dielectric vacuum constant, and the elementary charge, respectively.

A plot of  $C^{-2}$  vs V should yield a straight line and the carrier concentration can be extracted from its slope. From intercept on the x-axis we can extrapolate the barrier height by:

$$\phi_B = V_x + \frac{k_B T}{q} + \frac{k_B T}{q} \ln\left(\frac{N_c}{N_d}\right)$$

where  $V_x$  is the x-axis intercept, and  $N_c$  is the density of states in the conduction band edge.

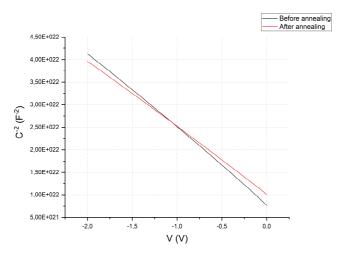

The  $C^{-2}$  vs V plot for both samples can be seen in Figure 3.

Figure 3.  $C^{-2}$  vs V plot of a 140 $\mu$ m diameter diode for both samples measured at 1MHz

From our measurements, the barrier height and doping concentration were calculated to be, respectively, 0.67eV and  $4.15 \cdot 10^{16}cm^{-3}$  for sample A and  $0.78\,eV$  and  $4.42 \cdot 10^{16}cm^{-3}$  for sample B. The doping density is close to the initial value for both samples, with minor differences that can be attributed to the annealing of the Schottky contact (i.e., better interface conditions). The barrier height is, in both cases, slightly higher than the value extrapolated from DC measurements. This difference originates from the fact that DC measurements are affected by non-idealities effects such as image force lowering, which in turn have little if not zero effect on C-V measurements. In practice, the capacitance-voltage method yields what is called the flatband barrier height, whereas the current-voltage method yields the zero-bias barrier height. In general, the flatband barrier height is a better measure of the barrier height than the zero-bias barrier height

The capacitance-voltage measurements were carried out at 1 MHz in order to avoid interface states and traps contribution to the measurement [9]. When a small voltage is applied to a Schottky diode, various defect energy levels sweep through the quasi-Fermi level, which produce an oscillation in the charge density. If the frequency is higher than the level response time, it cannot respond.

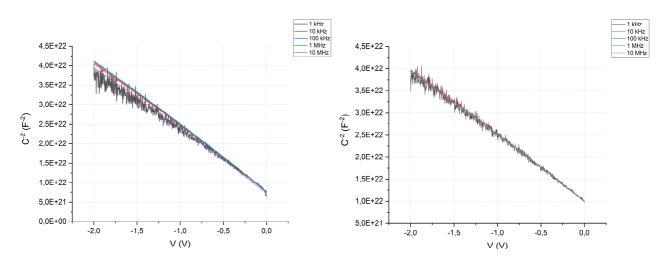

The frequency dependent capacitance measurements are showed in Figure 4.

Figure 2. Frequency-dependent capacitance for sample A (left) and sample B (right)

The capacitance measured at virtually all frequencies is the same, meaning that our sample is characterized by a low concentration of trap states, as opposed to some example in the literature [10,11].

A small deviation is observed at 1 kHz, supposedly because at that frequency, the time constant of the ac signal is low enough for the traps to follow.

#### 3.2 DC Characteristics

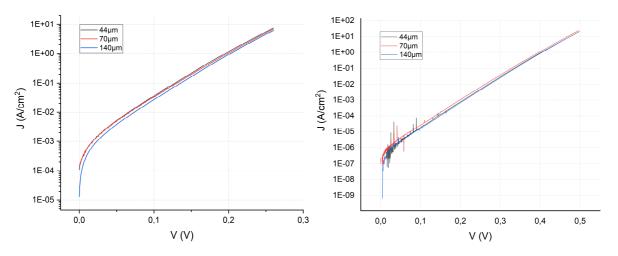

The current-voltage characteristics of the Schottky diode were studied at room temperature, in order to extract first-order parameters to validate the technological process and, in a second time, low and high temperature DC characterization was carried out. The I-V characteristics at room T are shown in Figure 5.

Figure 3. Forward characteristics of measured diodes of sample A (left) and sample B (right)

It is clear from the plot in Figure 5 that both diodes are affected by leakage current at lower voltages. This leakage can be attributed to defect states in the bulk and/or the surface. One of the main technological limitations in GaN electronic devices stems from the epitaxy: since the semiconductor is not lattice matched to the substrate, the material suffers from defect and dislocations that greatly affect its electronic properties [12–16]. Moreover, most Schottky diodes suffer from the presence of a thin insulating layer at the metal-semiconductor interface due to unwanted oxidation and/or contamination, unless it is fabricated in vacuum; in the case of I-V measurements, a thin interfacial layer of a few angstrom can be a major cause of deviation of the electrical diode characteristics from their ideal behavior [9,17]. An annealing of the Schottky contact improves the characteristic, namely by reducing the leakage current [17].

The classic diode model for thermionic emission is given by following equation [18]:

$$I = I_0 \left[ \exp\left(\frac{qV}{nk_BT}\right) - 1 \right] \tag{1}$$

where  $I_0$  is the saturation current, and n is the ideality factor. The saturation current is (under the assumption that the series resistance of the diode is negligibly small):

$$I_0 = A^* T^2 \exp\left[\frac{-q\phi_b}{nk_B T}\right] \tag{2}$$

where  $A^*$  is the Richardson constant and  $\phi_b$  the barrier height of the diode.

By performing a fit of the linear part of the semi-logarithmic I-V plot, we are able to extract the barrier height and the ideality factor, which for T=300K corresponds to  $0.64\,eV$  and 1.16, respectively. This value of the ideality factor reflects good agreement with thermionic emission

theory, proving in a first moment, that this is the main conduction mechanism for the diode at that temperature.

The values of the barrier height and ideality factor extracted with this method were compared to the one extracted using Cheung's method [19]:

$$V = R_S A J + n \phi_B + \frac{n}{\beta} \ln \left( \frac{J}{A^* T^2} \right) \tag{3}$$

$$\frac{dV}{d(\ln(I))} = R_S A I + \frac{n}{\beta} \tag{4}$$

where n is the ideality factor,  $\phi_B$  is the barrier height, R<sub>S</sub> is the series resistance, A is the electrically active area,  $A^*$  is Richardson constant (24.6 A  $cm^{-2}K^{-2}$  for GaN) and  $\beta = \left(\frac{k_BT}{q}\right)^{-1}$ .

A plot of  $dV/d(\ln(J))$  vs J yields a straight line whose slope and intercept with the y-axis are  $R_SA$  and  $n/\beta$ .

Using an auxiliary function H(J), it is possible to evaluate  $\phi_B$  and the series resistance:

$$H(J) = V - \frac{n}{\beta} \ln \left( \frac{J}{A^* T^2} \right) \tag{5}$$

$$H(J) = R_S A J + n \phi_B \tag{6}$$

Using the n value determined from Eq. 5, a plot of H(J) vs J leads to a straight line, with slope  $R_SA$  and intercept with the y-axis  $n\phi_B$ . The slope of this curve allows a second evaluation of the series resistance that can be used as a consistency check of the approximation with its first value.

The results for both samples are listed in Table 1.

|           | TE fit [18]  |      | Cheung [19]  |      |                            |

|-----------|--------------|------|--------------|------|----------------------------|

|           | $\phi_B(eV)$ | n    | $\phi_B(eV)$ | n    | $R_{S}\left(\Omega\right)$ |

| (A) 44.28 | 0.54         | 1.21 | 0.53         | 1.28 | 7.02                       |

| (A) 70    | 0.55         | 1.18 | 0.54         | 1.19 | 7.91                       |

| (A) 140   | 0.56         | 1.09 | 0.56         | 1.13 | 5.88                       |

| (B) 44.28 | 0.73         | 1.16 | 0.71         | 1.23 | 3.08                       |

| (B) 70    | 0.72         | 1.15 | 0.72         | 1.18 | 3.05                       |

| (B) 140   | 0.75         | 1.09 | 0.73         | 1.16 | 0.90                       |

Table 1. Extracted valued of barrier height and ideality factor for both samples

The ideality factor for both samples is between 1.1 and 1.2, which confirms that the main electrical conduction mechanism is thermionic emission (an ideality factor of 1 indicates pure thermionic emission in the ideal case), although there is the presence of other, non-ideal, mechanisms, such as tunneling. The barrier height undergoes an improvement with annealing (sample B), by increasing of about 0.20 eV, an improvement due to the fact that the thermal treatment allowed a structural rearrangement of Pt and Ga at the metal/semiconductor interface [20], which possibly eliminated any eventually native oxides present on the semiconductor surface and/or surface roughness induced during the fabrication process [17] . Moreover, the thermal annealing is not detrimental to the ideality factor. The series resistance, as calculated with Cheung's method, is of about 7  $\Omega$  for sample A and between 1 and 3  $\Omega$  for sample B. This reduction in series resistance proves that thermal

annealing of the Schottky contact was effective in promoting a structural reorganization at the metal/semiconductor interface, reordering the lattice structure in its most stable configuration [17].

TLM measurements of the Ohmic contact yielded a contact resistance of  $0.27~\Omega \cdot mm$ , a specific contact resistivity of  $4.3 \cdot 10^{-6} \Omega \cdot cm^2$ , as well as a sheet resistance of  $169.7~\Omega/\text{sq}$  for the n<sup>+</sup> GaN layer.

Table 2 presents a comparison of the barrier height and ideality factor for the samples analyzed in this paper with a few of the literature references found on GaN Schottky diodes grown on sapphire substrate.

| Epitaxy thickness    | $N_d$                  | $\phi_B$ (eV) | n           | $R_{S}\left( \Omega \right)$ | Reference |

|----------------------|------------------------|---------------|-------------|------------------------------|-----------|

| 650 nm (Sample<br>A) | 5 x 10 <sup>16</sup>   | 0.53 – 0.56   | 1.13 – 1.28 | 5.8 - 7                      | This work |

| 650 nm (Sample B)    |                        | 0.71 - 0.73   | 1.16 – 1.23 | 1 - 3                        |           |

| 100-400 μm           | 6.6 x 10 <sup>16</sup> | 0.84 - 0.94   | 1.03        | NA                           | [21]      |

| 3 μm                 | 1 x 10 <sup>16</sup>   | 0.79 – 0.96   | 1.16 – 1.8  | NA                           | [22]      |

| 4 μm                 | 1 x 10 <sup>17</sup>   | 0.845         | 1.18        | 65                           | [23]      |

| 150 nm               | 5-7 x 10 <sup>16</sup> | 1.10          | 1.05        | 120                          | [24]      |

Table 2. Comparison of parameters for various GaN Schottky diodes

The lower barrier height of the samples presented in this work as compared to the examples found in the literature (Table 2) can have complex origins, such as the presence of contaminants at the metal-semiconductor interface, or a high density of dislocation defects [15]. Moreover, the barrier height extracted from DC measurements is also affected by image-force lowering and other types of barrier inhomogeneities such as the presence of a thin oxide layer at the metal/semiconductor interface, tunneling currents. generation/recombination currents within the space-charge region [25].

The series resistance, in turn, result to be very low (about 6  $\Omega$  for sample A and between 1 and 3  $\Omega$  for sample B) when compared to the literature [23,24]. This result in particular acquires a new light when thinking that the series resistance of GaN Schottky diodes, which is typically higher than its GaAs counterpart, is a key parameter in the design of GaN Schottky diode frequency multipliers [5,26].

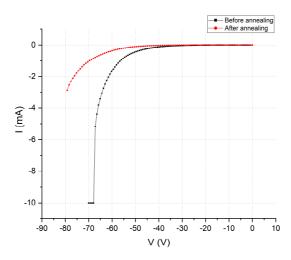

Figure 6 shows the reverse characteristics of the measured diodes, before and after thermal annealing. The breakdown voltage at  $10\mu A$  was measured to be -22.4 V before annealing, and -36 V after annealing. The breakdown voltage at the destruction for the diodes before annealing resulted to be between 60-70 V, while the diodes that underwent annealing yielded an improved breakdown voltage between 75-80 V.

Figure 6. Reverse characteristics of a 70 µm diode before and after annealing

The annealed sample shows a reduction in reverse leakage current, which, along with the increased barrier height, can be attributed to a reduction of nonstoichiometric defects in the metal-semiconductor interface [27].

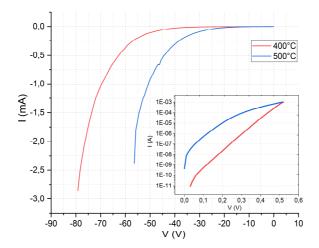

Figure 7. Comparison of different thermal annealings for a 70 µm diode. Inset: forward characteristics

An annealing at 500°C was performed as well (Figure 7): the resulting breakdown voltage was of about -56.4V (as opposed to the corresponding breakdown voltage for the sample annealed at 400°C, which was of about -79.2V). This degradation of the characteristic can be attributed to the formation of intermetallic compounds and to the migration of nitrogen gas to the surface [28]. In the literature is typically reported that Pt degrades as a Schottky contact to GaN in a range of temperatures between 600°C and 800°C, with a fairly dependence on the annealing time [17,28–30].

#### 4. Conclusions

In conclusion, GaN Schottky diodes on sapphire substrate were fabricated in the general optics of realizing varactor-based frequency multipliers for THz generations. Thus, an experimental investigation of the diodes basic parameters was conducted. Two samples (sample A, with no surface treatment and no annealing, and sample B, with no surface treatment and annealing at 400°C for 5 minutes) were studied and analyzed.

The capacitance-voltage characteristics were studied to identify the role of traps and contaminants to the overall performance of the diodes. The extracted barrier height and effective doping density from 1 MHz measurements are 0.67eV and  $4.15 \cdot 10^{16}cm^{-3}$  for sample A and  $0.78\,eV$  and  $4.42 \cdot 10^{16}cm^{-3}$  for sample B.

The current-voltage characteristics were studied to extract first order parameters such as the barrier heights, ideality factors and series resistances. The ideality factor for both samples is between 1.1 and 1.2. The barrier height is around 0.55 eV, a value that increase up to 0.72 eV when the diodes undergo annealing at 400°C. The series resistance is of about 7  $\Omega$  for sample A and between 1 and 3  $\Omega$  for sample B; this last result in particular is promising in the optics of GaN Schottky diode frequency multipliers design and realization, since the series resistances obtained in this work are considerably small compared to the literature. The two samples presented a breakdown voltage of about -56.4 V and -79.2 V, respectively for sample A and sample B.

#### Acknowledgments

This work was supported by the French ANR (Agence Nationale de la Recherche), under the CE24 'SchoGAN' project. This work was also supported by the CPER "Photonics for Society", and the Hauts de France Regional council and the French Network RENATECH.

#### References

- [1] G. Chattopadhyay, Technology, Capabilities, and Performance of Low Power Terahertz Sources, IEEE Trans. Terahertz Sci. Technol. 1 (2011) 33–53. https://doi.org/10.1109/TTHZ.2011.2159561.

- [2] A. Maestrini, I. Mehdi, J. V. Siles, J.S. Ward, R. Lin, B. Thomas, C. Lee, J. Gill, G. Chattopadhyay, E. Schlecht, J. Pearson, P. Siegel, Design and characterization of a room temperature all-solid-state electronic source tunable from 2.48 to 2.75 THz, IEEE Trans. Terahertz Sci. Technol. 2 (2012) 177–185. https://doi.org/10.1109/TTHZ.2012.2183740.

- [3] A. Maestrini, J.S. Ward, J.J. Gill, C. Lee, B. Thomas, R.H. Lin, G. Chattopadhyay, I. Mehdi, A frequency-multiplied source with more than 1 mW of power across the 840-900-GHz band, IEEE Trans. Microw. Theory Tech. 58 (2010) 1925–1932. https://doi.org/10.1109/TMTT.2010.2050171.

- [4] J. V. Siles, J. Grajal, Physics-based design and optimization of Schottky diode frequency multipliers for terahertz applications, IEEE Trans. Microw. Theory Tech. 58 (2010) 1933–1942. https://doi.org/10.1109/TMTT.2010.2050103.

- [5] J. V. Siles, J. Grajal, Capabilities of GaN Schottky Multipliers for LO Power Generation at Millimeter-Wave Bands, Proc. 19th Int. Symp. Sp. Terahertz Technol. (2008) 28–30.

- [6] C. Jin, M. Zaknoune, D. Ducatteau, D. Pavlidis, E-beam fabricated GaN schottky diode: High-frequency and non-linear properties, IEEE MTT-S Int. Microw. Symp. Dig. (2013). https://doi.org/10.1109/MWSYM.2013.6697734.

- [7] S. Liang, Y. Fang, D. Xing, Z. Zhang, J. Wang, H. Guo, L. Zhang, G. Gu, Z. Feng, GaN planar Schottky barrier diode with cut-off frequency of 902 GHz, Electron. Lett. 52 (2016) 1408–1410. https://doi.org/10.1049/el.2016.1937.

- [8] S. Liang, X. Song, L. Zhang, Y. Lv, Y. Wang, B. Wei, Y. Guo, G. Gu, B. Wang, S. Cai, Z. Feng, A 177–183 GHz High-Power GaN-Based Frequency Doubler With Over 200 mW Output Power, IEEE Electron Device Lett. 41 (2020) 669–672. https://doi.org/10.1109/LED.2020.2981939.

- [9] K. Suzue, S.N. Mohammad, Z.F. Fan, W. Kim, O. Aktas, A.E. Botchkarev, H. Morkoç, Electrical conduction in platinum-gallium nitride Schottky diodes, J. Appl. Phys. 80 (1996) 4467–4478. https://doi.org/10.1063/1.363408.

- [10] M.A. Kadaoui, W.B. Bouiadjra, A. Saidane, S. Belahsene, A. Ramdane, Electrical parameters of Au/n-GaN and Pt/n-GaN Schottky diodes, Superlattices Microstruct. 82 (2015) 269–286. https://doi.org/10.1016/j.spmi.2015.02.007.

- [11] M.R. Huque Khan, T. Detchprohmt, P. Hacke, K. Hiramatsu, N. Sawaki, The barrier height and interface effect of a au-n-gan schottky diode, J. Phys. D. Appl. Phys. 28 (1995) 1169–1174. https://doi.org/10.1088/0022-3727/28/6/021.

- [12] A.Y. Polyakov, I.H. Lee, Deep traps in GaN-based structures as affecting the performance of GaN devices, Mater. Sci. Eng. R Reports. 94 (2015) 1–56. https://doi.org/10.1016/j.mser.2015.05.001.

- [13] W. Götz, N.M. Johnson, H. Amano, I. Akasaki, Deep level defects in n-type GaN, Appl. Phys. Lett. 65 (1994) 463–465. https://doi.org/10.1063/1.112337.

- [14] F.A. Ponce, Defects and interfaces in GaN epitaxy, MRS Bull. 22 (1997) 51–57. https://doi.org/10.1557/S0883769400032577.

- [15] S.J. Pearton, J.C. Zolper, R.J. Shul, F. Ren, GaN: Processing, defects, and devices, J. Appl. Phys. 86 (1999) 1–78. https://doi.org/10.1063/1.371145.

- [16] L. Liu, J.H. Edgar, Substrates for gallium nitride epitaxy, Mater. Sci. Eng. R Reports. 37 (2002) 61–128. https://doi.org/10.1016/S0927-796X(02)00008-6.

- [17] S.N. Mohammad, Contact mechanisms and design principles for Schottky contacts to group-III nitrides, J. Appl. Phys. 97 (2005). https://doi.org/10.1063/1.1856226.

- [18] S.M. Sze, K.K. Ng, Physics of Semiconductor Devices, John Wiley & Sons, Inc., Hoboken, NJ, USA, 2006. https://doi.org/10.1002/0470068329.

- [19] S.K. Cheung, N.W. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics, Appl. Phys. Lett. 49 (1986) 85–87. https://doi.org/10.1063/1.97359.

- [20] J. Wang, D.G. Zhao, Y.P. Sun, L.H. Duan, Y.T. Wang, S.M. Zhang, H. Yang, S. Zhou, M. Wu, Thermal annealing behaviour of Pt on n-GaN Schottky contacts, J. Phys. D. Appl. Phys. 36 (2003) 1018–1022. https://doi.org/10.1088/0022-3727/36/8/312.

- [21] P. Hacke, T. Detchprohm, K. Hiramatsu, N. Sawaki, Schottky barrier on n-type GaN grown by hydride vapor phase epitaxy, Appl. Phys. Lett. 63 (1993) 2676–2678. https://doi.org/10.1063/1.110417.

- [22] F. Iucolano, F. Roccaforte, F. Giannazzo, V. Raineri, Temperature behavior of inhomogeneous Pt/GaN Schottky contacts, Appl. Phys. Lett. 90 (2007) 1–4. https://doi.org/10.1063/1.2710770.

- [23] B. Akkal, Z. Benamara, H. Abid, A. Talbi, B. Gruzza, Electrical characterization of Au/n-GaN Schottky diodes, Mater. Chem. Phys. 85 (2004) 27–31. https://doi.org/10.1016/j.matchemphys.2003.11.007.

- [24] S.N. Mohammad, Z. Fan, A.E. Botchkarev, W. Kim, O. Aktas, A. Salvador, H. Morkoç, Near-ideal platinum-GaN Schottky diodes, Electron. Lett. 32 (1996) 598. https://doi.org/10.1049/el:19960354.

- [25] J.H. Werner, H.H. Güttler, Barrier inhomogeneities at Schottky contacts, J. Appl. Phys. 69 (1991) 1522–1533. https://doi.org/10.1063/1.347243.

- [26] J. V. Siles, J. Grajal, Physics-based design and optimization of Schottky diode frequency multipliers for terahertz applications, IEEE Trans. Microw. Theory Tech. 58 (2010) 1933–1942. https://doi.org/10.1109/TMTT.2010.2050103.

- [27] Y. Sun, H. Yang, X.M. Shen, J. Wang, D.G. Zhao, G. Feng, Y. Fu, S.M. Zhang, Z.H. Zhang, Z.H. Feng, Y.X. Bai, Thermal annealing behaviour of Ni/Au on n-GaN Schottky contacts, J. Phys. D. Appl. Phys. 35 (2002) 2648–2651. https://doi.org/10.1088/0022-3727/35/20/326.

- [28] E.A. Preble, K.M. Tracy, S. Kiesel, H. Mclean, P.Q. Miraglia, R.J. Nemanich, R.F. Davis, M. Albrecht, D.J. Smith, Electrical, structural and microstructural characteristics of as-deposited and annealed Pt and Au contacts on chemical-vapor-cleaned GaN thin films, J. Appl. Phys. 91 (2002) 2133–2137. https://doi.org/10.1063/1.1432127.

- [29] Q.Z. Liu, L.S. Yu, S.S. Lau, J.M. Redwing, N.R. Perkins, T.F. Kuech, Thermally stable PtSi Schottky contact on n-GaN, Appl. Phys. Lett. 70 (1997) 1275–1277. https://doi.org/10.1063/1.118551.

- [30] Q.Z. Liu, S.S. Lau, A review of the metal-GaN contact technology, Solid. State. Electron. 42 (1998) 677–691. https://doi.org/10.1016/S0038-1101(98)00099-9.