## Carrier injection engineering in nanowire transistors via dopant and shape monitoring of the access regions

Salim Berrada, Marc Bescond, Nicolas Cavassilas, Laurent Raymond, Michel Lannoo

### ▶ To cite this version:

Salim Berrada, Marc Bescond, Nicolas Cavassilas, Laurent Raymond, Michel Lannoo. Carrier injection engineering in nanowire transistors via dopant and shape monitoring of the access regions. Applied Physics Letters, 2015, 107 (15), pp.153508. 10.1063/1.4933392. hal-03517633

HAL Id: hal-03517633

https://hal.science/hal-03517633

Submitted on 7 Jan 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Carrier injection engineering in nanowire transistors via dopant and shape monitoring of the access regions

Salim Berrada, Marc Bescond, Nicolas Cavassilas, Laurent Raymond and Michel Lannoo IM2NP UMR CNRS 7334, Aix-Marseille Université, Marseille, France

### Abstract

This work theoretically studies the influence of both the geometry and the discrete nature of dopants of the access regions in ultra-scaled nanowire transistors. By means of self-consistent quantum transport simulations we show that discrete dopants induce quasi-localized states which govern carrier injection into the channel. Carrier injection can be enhanced by taking advantage of the dielectric confinement occurring in these access regions. We demonstrate that the optimization of access resistance can be obtained by a careful control of shape and dopant position. These results pave the way for contact resistance engineering in forthcoming device generations.

The continuous race to fulfill the International Technology Roadmap for Semiconductors (ITRS) requirements gave rise to ultra-scaled Metal-Oxide-Semiconductor Field-Effect-Transistors (MOSFETs) with channel length of only few nanometers. At this scale electro-static control of the channel potential becomes difficult with conventional top gate geometry [1], leading to unsuitable short channel effects. Various novel MOSFET geometries [2] have been then proposed to circumvent these effects among which the gate-all-around NanoWire transistor (NWFET) represents an efficient solution [3–5]. NWFETs with channel length down to 5 nm have already been demonstrated experimentally [6] and are thus considered as one of the most promising devices to reach the end of the ITRS [7]. In such narrow devices, the resistance of access regions (AR) may appear as the main contributor to the global resistance of the source-channel-drain system. In particular the shape of the doped source and drain reservoirs as well as the number and the positions of dopants in the AR can have a strong impact on the variability of the transistor [8, 9].

At this scale, quantum tunneling and quantum confinement also play an important role [10]. Sophisticated quantum transport simulations are then required to assess the impact of the AR and to optimize NWFET design. On the other hand, in most of the reported simulations charge resulting from dopant ionization is assumed to be continuously distributed over the whole source and drain regions. However, if one considers a NWFET with a square cross-section of  $2\times2$  nm<sup>2</sup>, a concentration of  $10^{20}$ cm<sup>-3</sup> corresponds on average to less than two dopants in a 4 nm long wire. Therefore, the continuous doping assumption is no longer justified and the discrete nature of dopants should be taken into account. Ionized dopants give rise to an attractive Coulomb potential which creates quasi-localized states in the conduction band. Many investigations dealing with the presence of discrete dopants showed that the impurity level degrades the ON-current, while the sub-threshold behavior could be affected [8, 11–15]. It is important to mention that these studies either used a mode-space approach, or did not take into account electron-phonon interaction when realspace representation was considered. Indeed, phonons are known to play an important role in the ON-state current degradation [16, 17] or in the broadening of quasi-localized states, thus modifying the carrier's lifetime [18].

Among the few studies dealing with discrete dopants, most of them considered NWFETs with constant cross-sections in source and drain regions. However, realistic AR are usually thicker than the channel region. It has been theoretically shown for double-gate MOSFETs

that drain current versus gate to source voltage  $(I_D - V_{GS})$  characteristics are weakly affected by AR geometry when a continuous doping profile is assumed in those regions [19]. Our results first demonstrate that NWFETs exhibit similar behavior. However, the picture is quite different when a discrete doping profile is assumed. Indeed, Diarra *et al.* demonstrated that the impurity level in NW of radius R<3 nm is strongly affected by the dielectric confinement [20, 21]. Consequently the energy of dopant level depends on the AR geometry.

The aim of this work is then to emphasize the importance of considering both realistic AR and discrete dopants when modeling ultra-scaled NWFETs. We will find an optimal configuration to enhance carrier injection when the dopant position is carefully chosen. Since it is possible nowadays to precisely place dopants in nanowires [22, 23], these informations can be of a great interest to NWFET designers to minimize access resistance and boost the performance of the ultimate devices.

To tackle this problem, we developed a self-consistent Non-Equilibrium Green's Function (NEGF) solver that allows to consider AR with different shapes and geometries. The electrons of the six  $\Delta$ -valleys of silicon conduction band are described using an effective mass hamiltonian in real-space representation [24]. The effective mass values have been fitted on full-band tight-binding calculations [25]. Electron-phonon interaction is included using the Self-Consistent Born Approximation (SCBA) [26]. Both intravalley and intervalley scattering are taken into account through the self-energy expressions given in reference [18]. The values of deformation potentials and interaction matrix elements, for both optical and acoustic phonons, can be found in reference [26]. Electron-electron interaction is treated in the Hartree approximation. One solves for the mean field given by Poisson equation self-consistently with the charge resulting from NEGF calculations. In our model, each discrete dopant occupies the volume of the unit mesh (2×2×2 ų) as shown in Ref.[18]. The resulting screening of this positive electron charge will give rise to the long range Coulomb potential of the impurity.

In order to capture only the influence of the AR, all considered devices in this study possess the same gated region. All transistors have then the same channel squared cross-section of  $2\times2$  nm<sup>2</sup>, gate length  $L_G=8$  nm and equivalent oxide thickness of 1 nm. Beyond the AR, we always consider external source and drain regions of 4 nm long, which are assumed to be continuously doped at  $N_D=10^{20}$  cm<sup>-3</sup> to ensure continuous injection into the AR.

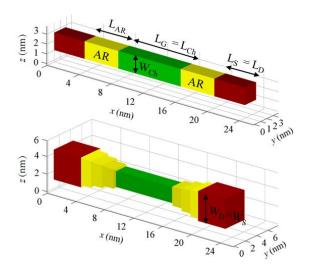

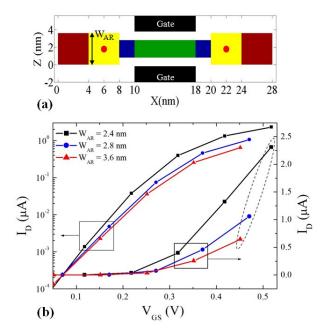

FIG. 1: 3D view of the considered gate-all-around NWFETs. UN device (top panel) has a uniform cross-section of  $2\times2$  nm<sup>2</sup>, while NUN device (down panel) has a non-uniform cross-section. A Channel width  $W_{Ch}=2$  nm (green) is assumed for all devices. Same gate and channel lengthes  $L_G=L_{CH}=8$  nm are assumed for both UN and NUN. The gate insulator has an equivalent oxide thickness of 1 nm. Source and drain (red) are uniformly doped at  $N_D=10^{20}$  cm<sup>-3</sup> and are  $L_S=L_D=4$  nm long. Access regions are  $L_{AR}=4$  nm long and represented in yellow. Square source and drain cross-sections for NUN have  $W_S=W_D=3.6$  nm width. For all the simulations  $V_{DS}=0.3$  V and T=300 K.

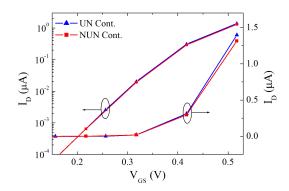

To illustrate the importance of discrete doping in realistic AR, we considered two NWFET structures that we shall call UNiform (UN) and Non-UNiform (NUN) (Fig. 1). The UN device has a uniform cross-section of  $2\times2$  nm<sup>2</sup> from source to drain. The NUN device has a larger cross-section of  $3.6\times3.6$  nm<sup>2</sup> in source and drain, and an AR with a non-uniform cross-section that linearly connects source and drain to the channel of  $2\times2$  nm<sup>2</sup>. Both devices have AR of  $L_{AR}=4$  nm represented in yellow. Figure 2 represents  $I_D-V_{GS}$  characteristics when continuous doping in AR is assumed for both devices. Logarithm curves (left scale) show a small change in sub-threshold voltage  $(V_{th})$  of 14 meV and identical sub-threshold slope  $(S_{s-th})$ . Linear curves (right scale), after  $V_{th}$  adjustment, show only a 6% degradation of  $I_{ON}$  for the NUN device with respect to its UN counterpart. Therefore, we can conclude that the geometry has little impact when continuous doping is assumed for AR. This result is in accordance with the results previously obtained for double-gate devices [19]. We then replace the continuous doping of AR by a single impurity. For the NUN device we consider

FIG. 2:  $I_D - V_{GS}$  characteristics for UN (triangles) and NUN (squares) devices with continuously doped AR at  $N_D = 10^{20}$  cm<sup>-3</sup> in linear and logarithm scales.  $V_{DS} = 0.3$  V.

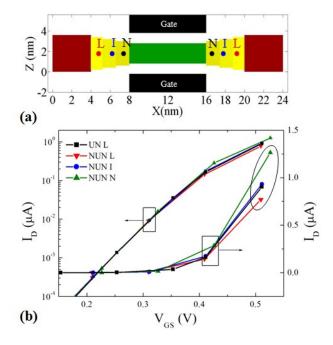

three configurations as depicted in Fig. 3a. Let's start by the comparison of the NUN L-configuration with a UN device in which the impurity is placed exactly at the same position along the channel symmetry axis. The corresponding  $I_D - V_{GS}$  plotted in Fig. 3b show that  $I_{ON}$  in NUN L is 20% lower than in the UN L. This first result pinpoints the importance of having a discrete dopant description when a more realistic geometry of AR is considered. On the other hand, subthreshold behavior is poorly affected by this change.

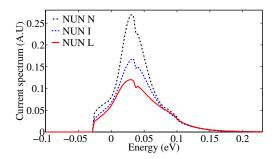

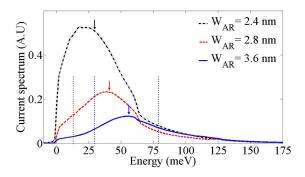

In order to see if the current degradation in NUN could be overcome, we now consider the I and N configurations as depicted in Fig. 3a. One can see in the corresponding  $I_D - V_{GS}$  (Fig. 3b) that the obtained  $I_{ON}$  is all the better for impurities localized in the narrower cross-section, close to the channel. Fig. 4 shows the current spectra at source contact for the three NUN-configurations at given bias. We notice that we have a better injection at the source for the N-configuration, followed by I-configuration, while the worst injection is obtained for L-configuration. This surprising result shows that  $I_{ON}$  is higher when the impurity is located just at the entrance of the channel. Besides the dopant position along the AR, carrier injection efficiency may also depend on the AR cross-section.

To understand this dependence, we considered three devices with abrupt constrictions defined by constant AR cross-sections of width's  $W_{AR}$  of 3.6 nm, 2.8 nm and 2.4 nm (Fig. 5a). A spacer of 2 nm was added to the AR to prevent AR and gate overlap. One impurity is then placed in each AR at exactly the same position along the channel symmetry axis. The corresponding  $I_D - V_{GS}$  characteristics for the three devices are shown in Fig. 5b. Once again, we notice that the smaller is the cross-section of the AR, the better is the

FIG. 3: (a) View of the transverse section in the middle of the NUN device. Square source and drain (red) cross-sections for NUN have  $W_S=W_D=3.6$  nm width and are uniformly doped at  $N_D=10^{20}$  cm<sup>-3</sup>. Each AR (yellow) contains one impurity. We consider 3 configurations labelled L (large), I (intermediate) and N (Narrowest) which correspond to the positions of one impurity of each side in cross-section of  $3.2\times3.2$  nm<sup>2</sup>,  $2.8\times2.8$  nm<sup>2</sup> and  $2.4\times2.4$  nm<sup>2</sup> respectively. (b) Corresponding  $I_D - V_{GS}$  characteristics at  $V_{DS}=0.3$  V in both linear and logarithmic scales. For comparison, we plot  $I_D - V_{GS}$  for the UN L device where the impurity is placed exactly at the same position along the channel symmetry axis as NUN L.

FIG. 4: Current spectra at source contact for the three NUN-configurations defined by circled points in Fig. 3b. Reference in energy is taken at the Fermi level of the source ( $E_{FS}$ =0 eV).

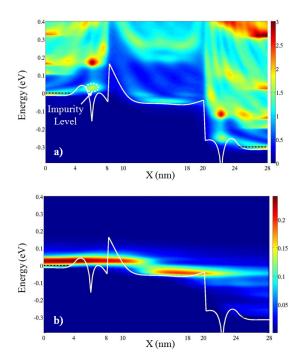

obtained  $I_{ON}$ . Figure 6 shows the current spectra for the three devices at the bias points circled in Fig. 5b. The reference in energy is taken at the bottom of the first subband of each device at the source and the corresponding Fermi levels at the source  $(E_{FS})$  are plotted in dashed lines. The maximum of injection occurs above  $E_{FS}$  for  $W_{AR}$ =3.6 nm and 2.8 nm, and below  $E_{FS}$  for  $W_{AR}=2.4$  nm. This shows that the injection in this type of device is not governed by the position of  $E_{FS}$  relatively to the first subband but rather by the energy of the impurity level in the AR of the source (indicated by vertical arrows). This behavior is explained on Figure 7 which shows LDOS and current spectrum along the source-drain axis for  $W_{AR}$ =2.8 nm. We see the attractive impurity potentials in each AR as well as the subband mismatch resulting from the abrupt reduction of the cross-section in the channel. The current injection maximum clearly coincides with the impurity level energy in the source AR which promotes transport through the tunneling barrier resulting from the variation of cross-section. We also find that the more we confine the impurity, the lower is its impurity level energy relatively to the Fermi level of the source and the more efficiently it can promote the carrier transport. This is due to the so-called dielectric confinement in ultrascaled NWFETs [20, 21]. Indeed, the mismatch of the dielectric constants of Si and SiO<sub>2</sub> creates an electric field at the interfaces which lowers the impurity level energy in narrow cross-section. Therefore, we can conclude that the higher  $I_{ON}$  obtained for the NUN device in N-configuration - and the corresponding higher injection - is due to an enhanced injection through the impurity level thanks to the higher dielectric confinement of the impurity inside the narrowest cross-section.

In conclusion, we have used quantum simulations to show the importance of considering the discrete aspect of dopants in realistic ultra-scaled NWFETs. In real devices, the leads are thicker than the channel, leading to a subband mismatch that acts as a tunnel barrier for carriers crossing the access region that connects the leads to the channel. In this work, we demonstrate the importance of the impurity levels in enhancing injection by providing states inside this tunnel barrier. Thanks to the dielectric confinement, carrier injection is enhanced when the impurities are placed in the narrowest cross-section of the access region. The low drive current being a major drawback of NWFETs scaling, this result could be of great help to experimentalists to boost the injection in ultra-scaled NWFETs.

FIG. 5: (a) View of the transverse section in the middle of the devices with abrupt constrictions. Square source and drain (red) are 4 nm long uniformly doped at  $N_D = 10^{20}$  cm<sup>-3</sup>. Each AR (yellow) contains one impurity at its center (red circle). The widths of AR for the three considered devices are  $W_{AR} = 3.6$  nm, 2.8 nm and 2.4 nm. Blue regions are 2 nm long spacer of intrinsic silicon to minimize the influence of the gate on the AR. (b) Corresponding  $I_D - V_{GS}$  characteristics in both logarithmic and linear scales.

FIG. 6: Current spectra at source contact for the circled points in Fig. 5b. Reference in energy (E=0 eV) is taken at the bottom of the first subband for each device. For each configuration the corresponding Fermi levels at the source  $(E_{FS})$  are represented by vertical dotted lines and the energy of the impurity levels of the source AR are represented by vertical arrows.

FIG. 7: a) LDOS and b) current spectrum corresponding to the circled point of Fig. 5b for  $W_{AR}$ =2.8 nm. The horizontal dashed lines define the Fermi levels of source and drain while the white lines describe the profile of the first electronic subband. The current transmission through the first quasi-localized state of the source AR impurity is clearly visible.

### Acknowledgement

This work is supported by the NOODLES contract (ANR-13-NANO-0009) funded by the ANR-French National Research Agency. This work was granted access to the HPC resources of Aix-Marseille Universit financed by the project Equip@Meso (ANR-10-EQPX-29-01) of the program d'Investissements d'Avenir supervised by the Agence Nationale pour la Recherche.

<sup>[1]</sup> J.-P. Colinge, Solid-State Electron. 48, 897 (2004).

<sup>[2]</sup> I. Ferain, C. A. Colinge and J.-P. Colinge, Nature **479**,310 (2011).

<sup>[3]</sup> J.-P. Colinge, M.H. Gao, A. Romano-Rodriguez, H. Maes and C. Claeys, *Technical Digest. of the International Electron Device Meeting (IEEE)*, 595 (1990).

<sup>[4]</sup> P.Nguyen, S. Barraud, C. Tabone et al, IEEE International Electron Device Meeting, 16.2.1

- (2014).

- [5] G. Larrieu, and X.-L. Han Nanoscale 5, 2437 (2013).

- [6] T.-Y. Liow, K. M. Tan, R. Lee, M. Zhu, B. L.-H. Tan, G.S. Samudra, N. Balasubramanian and Y.-C. Yeo, Symposium on VLSI Technology, 36 (2008).

- [7] M. Luisier, M. Lundstrom, D. A. Antoniadis, and J. Bokor, IEEE International Electron Device Meeting, 11.2.1 (2011).

- [8] N. Seoane, A. Martinez, A.R. Brown, J.R. Barker, and A. Asenov, IEEE Trans. Electron Devices 56, 1388 (2009).

- [9] Y. He, Y. Wang, G. Klimeck and T. Kubis, Appl. Phys. Lett. 105, 213502 (2014).

- [10] Bescond, M. and Nehari, K. and Autran, J.L. and Cavassilas, N. and Munteanu, D. and Lannoo, M. Technical Digest. of the International Electron Device Meeting (IEEE), 617 (2004).

- [11] N. D. Akhavan, I Ferain, R. Yu, P. Razavi, J. P. Colinge, J. Comp. Electron., 11, 249 (2012).

- [12] A. Martinez, N. Seoane, A.R. Brown, J.R. Barker and A. Asenov IEEE Trans. Electron Devices 57, 1626 (2010).

- [13] V.P. Georgiev, E.A. Towie and A. Asenov, International Conference on Simulation of Semiconductor Processes and Devices, 416 (2013).

- [14] A. Asenov, F. Adamu-Lema, X. Wang and S. M. Amoroso, IEEE Trans. Electron Devices 61, 2745 (2014).

- [15] M. Bescond, M. Lannoo, L. Raymond, F. Michelini, J. Appl. Phys. 107, 093703 (2010).

- [16] M. Anantram, M. Lundstrom and D. Nikonov, Proc. IEEE **96**, 1551 (2008).

- [17] R. Rhyner, and M. Luisier, Phys. Rev. B 89,235311 (2014)

- [18] H. Carrillo-Nuez, M. Bescond, N. Cavassilas, E. Dib, M. Lannoo, J. Appl. Phys. 116, 164505 (2014).

- [19] R. Venugopal, S. Goasguen, S. Datta and M. S. Lundstrom, J. Appl. Phys. 95, 292 (2004).

- [20] M. Diarra, Y.-M. Niquet, C. Delerue, G. Allan, Phys. Rev. B 75, 045301 (2007).

- [21] M. Diarra, C. Delerue, Y.-M. Niquet, G. Allan, J. Appl. Phys. 103, 073703 (2008).

- [22] P. M. Koenraad, M. E. Flatte, Nat. Mater. 10, 91 (2011)

- [23] B. Weber, Y.-H Matthias Tany, S. Mahapatra et al, Nat. Nano 9, 430 (2014).

- [24] A. Martinez, M. Bescond, J.R. Barker, A. Svizhenko, M.P. Anantram, C. Millar, A. Asenov, IEEE Trans. Electron Devices 54, 2213 (2007).

- [25] K. Nehari, N. Cavassilas, F. Michelini, M. Bescond, J.-L. Autran, M. Lannoo, Appl. Phys.

Lett. **90**, 132112 (2007).

$[26]\,$  M. Bescond, C. Li, H. Mera, N. Cavassilas, M. Lannoo, J. Appl. Phys.  ${\bf 114},\,153712$  (2013).