# GaN-based power devices: Physics, reliability, and perspectives

Matteo Meneghini, Carlo de Santi, Idriss Abid, Matteo Buffolo, Marcello Cioni, Riyaz Abdul Khadar, Luca Nela, Nicolò Zagni, Alessandro Chini, F Medjdoub, et al.

#### ▶ To cite this version:

Matteo Meneghini, Carlo de Santi, Idriss Abid, Matteo Buffolo, Marcello Cioni, et al.. GaN-based power devices: Physics, reliability, and perspectives. Journal of Applied Physics, 2021, 130 (18), pp.181101. 10.1063/5.0061354. hal-03421528

## HAL Id: hal-03421528 https://hal.science/hal-03421528v1

Submitted on 9 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# GaN-based power devices: physics, reliability and perspectives

Matteo Meneghini<sup>1</sup>, Carlo De Santi<sup>1</sup>, Idriss Abid<sup>2</sup>, Matteo Buffolo<sup>1</sup> Marcello Cioni<sup>5</sup>, Riyaz Abdul Khadar<sup>3</sup>, Luca Nela<sup>3</sup>, Nicolò Zagni<sup>5</sup>, Alessandro Chini<sup>5</sup>, Farid Medjdoub<sup>2</sup>, Gaudenzio Meneghesso<sup>1</sup>, Giovanni Verzellesi<sup>4</sup>, Enrico Zanoni<sup>1</sup>, Elison Matioli<sup>3</sup>

<sup>1</sup>University of Padova, Department of Information Engineering, via Gradenigo 6/B, 35131 Padova, Italy

<sup>2</sup>IEMN (Institute of Electronics, Microelectronics and Nanotechnology), Avenue Poincaré, 59650 Villeneuve d'Ascq, France

<sup>3</sup>École Polytechnique Fédérale de Lausanne, ELD 012 (Bâtiment ELD), CH-1015 Lausanne

<sup>4</sup>University of Modena and Reggio Emilia, Dipartimento di Scienze e Metodi dell'Ingegneria, via Amendola 2 - Pad. Morselli, 42122 Reggio Emilia, Italy

<sup>5</sup>University of Modena and Reggio Emilia, Dipartimento di Ingegneria "Enzo Ferrari", Via P. Vivarelli, 10, 41125 Modena, Italy

#### Abstract:

Over the last decade, gallium nitride has emerged as an excellent material for the fabrication of power devices. Among the semiconductors for which power devices are already available on the market, GaN has the widest energy gap, the largest critical field, the highest saturation velocity, thus representing an excellent material for the fabrication of high speed/high voltage components.

The presence of spontaneous and piezoelectric polarization allows to create a 2-dimensional electron gas, with high mobility and large channel density, in absence of any doping, thanks to the use of AlGaN/GaN heterostructures. This contributes to minimize resistive losses; at the same time, for GaN transistors switching losses are very low, thanks to the small parasitic capacitances

and switching charges. Device scaling and monolithic integration enable high frequency operation, with consequent advantages in terms of miniaturization.

For high power/high voltage operation, vertical device architectures are being proposed and investigated, and 3-dimensional structures – fin-shaped, trench-structured, nanowire-based – are demonstrating a great potential. Contrary to silicon, GaN is a relatively young material: trapping and degradation processes must be understood and described in detail, with the aim of optimizing device stability and reliability.

This tutorial paper describes the physics, technology and reliability of GaN-based power devices: in the first part of the article, starting from a discussion of the main properties of the material, the characteristics of lateral and vertical GaN transistors are discussed in detail, to provide guidance in this complex and interesting field. The second part of the paper focuses on trapping and reliability aspects: the physical origin of traps in GaN, and the main degradation mechanisms are discussed in detail. The wide set of referenced papers and the insight on the most relevant aspects gives the reader a comprehensive overview on present and next-generation GaN electronics.

## 1 Table of Contents

| 2 | Intro | luction                                                   | 6  |

|---|-------|-----------------------------------------------------------|----|

| 3 | Galli | ım nitride: properties and physical parameters            | 11 |

| 4 | Polar | zation charges in GaN                                     | 17 |

| 5 | Band  | diagrams and charge density in AlGaN/GaN heterostructures | 25 |

| 6 | Later | al GaN transistors: technology and operation              | 36 |

|   | 6.1   | Lateral GaN device architectures                          | 37 |

|   | 6.2   | Approaches for normally-off operation                     | 42 |

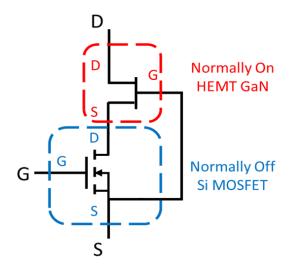

|   | 6.2.1 | Cascode configuration                                     | 43 |

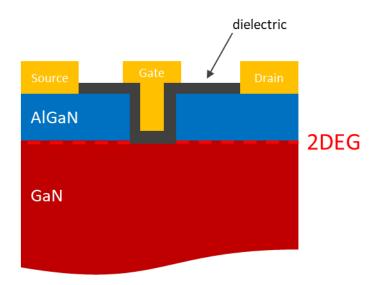

|   | 6.2.2 | Recessed gate MISHEMT                                     | 44 |

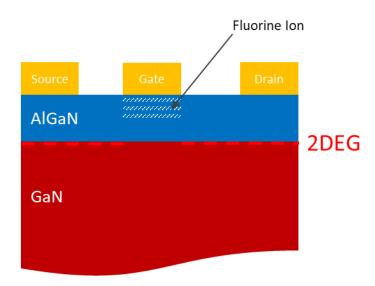

|   | 6.2.3 | The "fluorine gate" HEMT                                  | 45 |

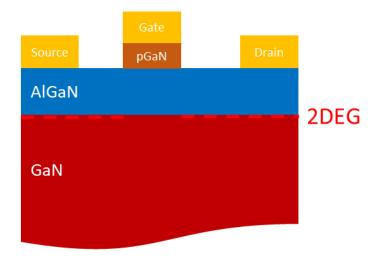

|   | 6.2.4 | P-GaN Gate                                                | 45 |

|   | 6.3   | Breakdown mechanisms                                      | 48 |

|   | 6.4   | Ways to improve the breakdown voltage                     | 50 |

|   | 6.4.1 | Buffer optimization: Super-lattice buffer                 | 50 |

|   | 6.4.2 | Local substrate removal                                   | 52 |

|   | 6.4.3 | AlN-based power devices                                   | 55 |

|   | 6.5   | Future perspectives                                       | 57 |

|   | 6.5.1 | Multi-channel devices                                     | 58 |

|   | 6.5.2 | Super Junctions                                           | 60 |

| 7 | Verti | eal GaN device structures                                 | 62 |

|   | 7.1   | Why Vertical GaN?                                         | 62 |

|   | 7.2   | Choice of substrate:                                      | 63 |

|   | 7.3   | Vertical device architectures:                            | 65 |

|   | 7.3.1 | Development of vertical devices on sapphire and bulk GaN  | 65 |

|   | 7.4   | Open Challenges:                                          | 93 |

| 8 | Char  | ge-trapping processes in GaN transistors                  | 96 |

|   | 8.1  | Traj   | ps and deep levels in GaN                                              | 97    |

|---|------|--------|------------------------------------------------------------------------|-------|

|   | 8.2  | Traj   | pping mechanisms                                                       | . 105 |

|   | 8.3  | Sur    | face traps in the gate-drain access region                             | . 107 |

|   | 8.4  | Bar    | rier traps                                                             | . 108 |

|   | 8.5  | Buf    | fer traps                                                              | . 109 |

|   | 8.6  | Gat    | e-dielectric traps                                                     | . 111 |

|   | 8.7  | Traj   | pping effects                                                          | . 112 |

|   | 8.7. | .1     | RF current collapse                                                    | . 112 |

|   | 8.7. | .2     | Dynamic R <sub>ON</sub> increase                                       | .114  |

|   | 8.7. | .3     | Threshold-voltage instabilities in isolated-gate and p-GaN transistors | .116  |

|   | 8.7. | .4     | "Kink" effect                                                          | .118  |

|   | 8.8  | Traj   | ps characterization techniques                                         | .119  |

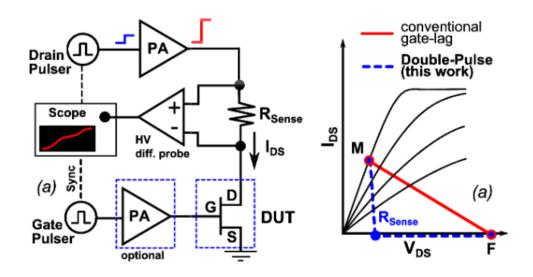

|   | 8.8. | .1     | Pulsed IV                                                              | .119  |

|   | 8.8. | .2     | DLTS/DLOS                                                              | .120  |

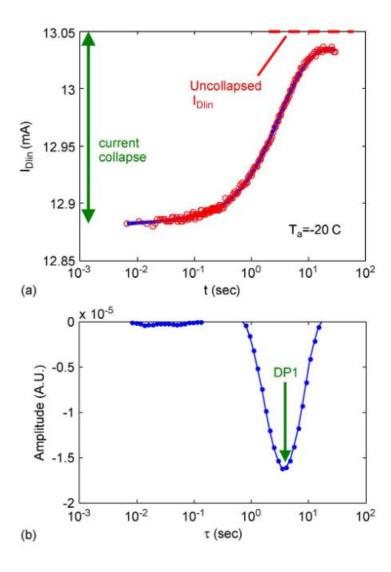

|   | 8.8. | .3     | Current transients                                                     | . 122 |

|   | 8.8. | .4     | On-the-fly characterization                                            | . 127 |

|   | 8.8. | .5     | Interface trap characterization by means of C-V and G-V measurements   | . 127 |

|   | 8.8. | .6     | Photoluminescence (PL)                                                 | . 129 |

| 9 | Deg  | gradat | tion processes in GaN devices                                          | . 130 |

|   | 9.1  | ON-    | state                                                                  | . 130 |

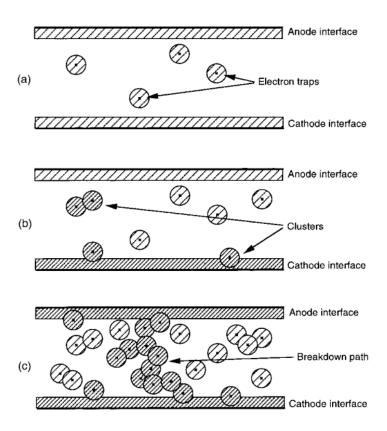

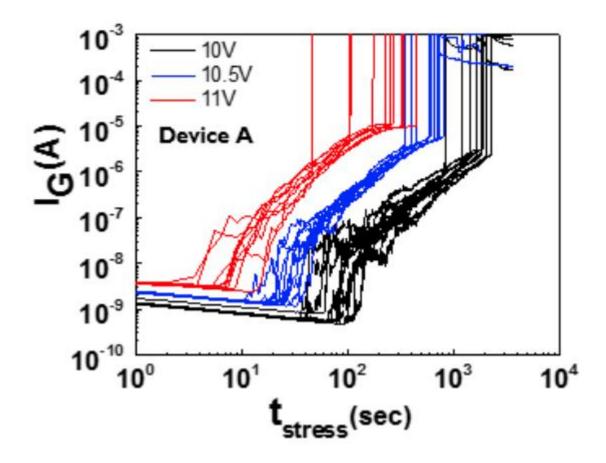

|   | 9.1. | .1     | Extrinsic degradation: the role of dielectrics                         | . 130 |

|   | 9.1. | .2     | Degradation of p-GaN gate stacks                                       | . 134 |

|   | 9.1. | .3     | Vertical devices                                                       | . 137 |

|   | 9.1. | .4     | RF stress                                                              | . 139 |

|   | 9.2  | OFF    | -state                                                                 | . 140 |

|   | 9.2. | .1     | Extrinsic degradation: the role of dielectrics                         | . 140 |

|   | 9.2. | .2     | Degradation of GaN stacks                                              | . 143 |

| 9  | 0.3             | SEM   | ⁄II-ON-state                                    | 153 |  |

|----|-----------------|-------|-------------------------------------------------|-----|--|

| 9  | 0.4             | Elec  | ctrostatic discharges and electrical overstress | 156 |  |

| 9  | 0.5             | Rad   | diation hardness                                | 160 |  |

|    | 9.5.            | 1     | Proton irradiation                              | 160 |  |

|    | 9.5.            | 2     | Neutron irradiation                             | 161 |  |

|    | 9.5.            | 3     | Electron irradiation                            | 162 |  |

|    | 9.5.            | 4     | Gamma ray irradiation                           | 162 |  |

|    | 9.5.            | 5     | Other ionizing species                          | 162 |  |

| 10 | C               | onclu | usions                                          | 164 |  |

| 11 | Acknowledgments |       |                                                 |     |  |

| 12 | Reference       |       |                                                 |     |  |

#### 2 Introduction

Over the past decade, gallium nitride has emerged as an excellent material for the fabrication of power semiconductor devices. Thanks to the unique properties of GaN, diodes and transistors based on this material have excellent performance, compared to their silicon counterparts, and are expected to find wide application in the next-generation power converters. Owing to the flexibility and the energy efficiency of GaN-based power converters, the interest towards this technology is rapidly growing: the aim of this tutorial is to review the most relevant physical properties, the operating principles, the fabrication parameters, and the stability/reliability issues of GaN-based power transistors. For introductory purposes, we start summarizing the physical reasons why GaN transistors achieve a much better performance than the corresponding silicon devices, to help the reader understanding the unique advantages of this technology.

The properties of GaN devices allow the fabrication of high-efficiency (near or above 99 %) [1]–[5], kW-range power converters. Such converters can have switching frequencies above 1 MHz [6], [7], and – through proper design, integration and/or hybrid GaN/CMOS manufacturing – frequencies as high as 40-75 MHz can be reached [8], [9]. High frequency operation permits to substantially reduce the size and weight of inductors and capacitors, thus resulting in a compact converter design. Further innovation will come from the design of monolithically integrated all-GaN integrated circuits: specific platforms, such as GaN on silicon-on-insulator (SOI) can be used for the fabrication of fully integrated power converters, containing smart control, pulse width modulation (PWM) circuitry, dead time control and half bridge [10], [11]. Such solutions, that can be tailored for switching in the 1-10 MHz range, can reach very short turn on/off times, which are considerably smaller than in discrete gate drivers [11]. The availability of fast, small, efficient and light-weight power converters can be particularly beneficial in the fields of portable/consumer electronics, automotive, and avionics.

GaN is a wide-bandgap semiconductor, and has an energy-gap of 3.4 eV [12]. This allows GaN devices to be operated at extremely high temperatures, thus substantially increasing the maximum power density that can be dissipated on a device, or permitting the use of light and small heat sinks. Over the last decades, several report on high temperature and stable operation of GaN HEMTs have been published. Temperatures above 400-500 °C [13]–[15] have been reached and, for

selected InAlN/GaN devices, up to 900 °C [15]. Operation at high temperature is a first, substantial, advantage of GaN devices, compared to silicon-based Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs), that are typically rated for maximum operating temperature of 125-150 °C.

A second advantage of GaN arises from its high breakdown field (3.3 MV/cm [12]), which is 11 times higher than that of silicon (0.3 MV/cm). The direct consequence of such high critical field is that for withstanding a given voltage, a layer of GaN can be 11 times thinner than its silicon counterpart, with consequent beneficial impact on resistivity. As a consequence, the use of GaN switches can substantially reduce the resistive losses in switching mode power supplies (SMPSs).

A third aspect to be considered is the high mobility of the channel: as will be discussed in the following sections, GaN transistors are typically heterostructure devices. A high mobility (up to 2000 cm/Vs [12]) channel can be obtained through the formation of a 2-dimensional electron gas (2DEG) at the heterointerface between the AlGaN barrier and the GaN channel layer. Such high mobility, along with the large saturation velocity (2.5x10<sup>7</sup> cm/s), further contributes to reduce the resistivity of the devices. FETs based on AlGaN/GaN heterostructures are usually referred to as high electron mobility transistors (HEMTs), or heterojunction field effect transistors (HFETs).

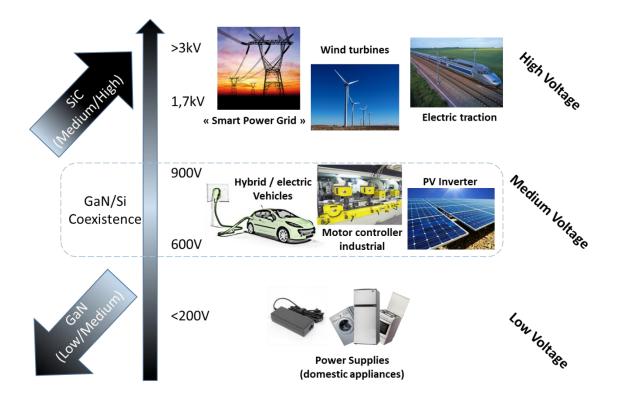

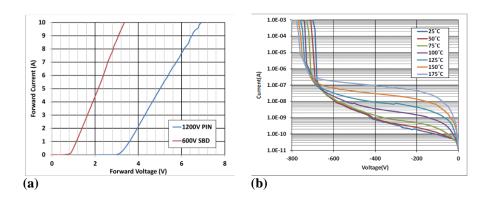

At present, GaN devices are commercially available, and several products have been proposed, in three main voltage ranges: a) low/mid-voltage (V<sub>DS,max</sub><200 V) devices find application in dc-dc power converters, motor drives, wireless power transfer, LiDAR and pulsed power applications, solar micro-inverters, class-D audio amplifiers, robotics, and synchronous rectification. Such devices can have on-resistances below 2 mΩ (for drain currents up to 90 A) [16], or up to 100-200 mΩ (for operating currents in the range 0.5-5 A), depending on the final application [17], [18]. b) high voltage (V<sub>DS,max</sub> up to 650 V), that find application in telecommunication servers, industrial converters, photovoltaic inverters, servo motor control [19], lighting applications, power adapters, converters for consumer electronics [20], class D amplifiers [21], datacenter SMPS [22], [23]. c) devices with ultra-high voltage (V<sub>DS,max</sub> above 1 kV). At present, no kV-range transistor based on GaN is commercially available. The commercial transistors with highest voltage rating have a maximum voltage of 900 V, and are expected to find application in data communication systems, industrial application, motor control, and photovoltaic inverters. As will be discussed in the article, several research papers demonstrated the feasibility of GaN transistors with breakdown voltages

above 1 kV [24]–[26], and proposed possible fabrication processes to target this voltage range. kV-range GaN transistors will compete with SiC-based devices, in the industrial, automotive and photovoltaic application environments.

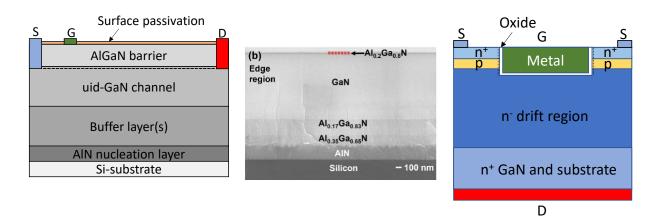

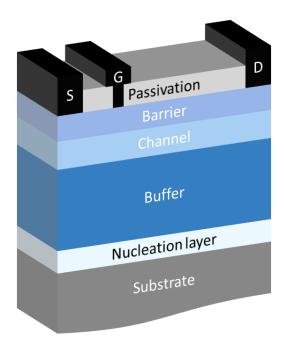

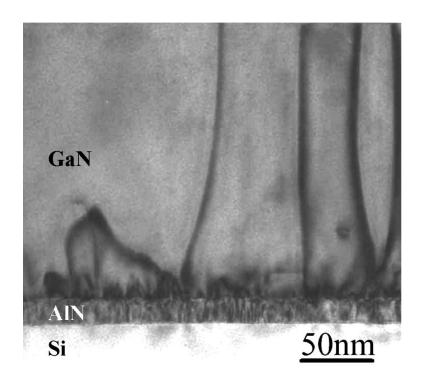

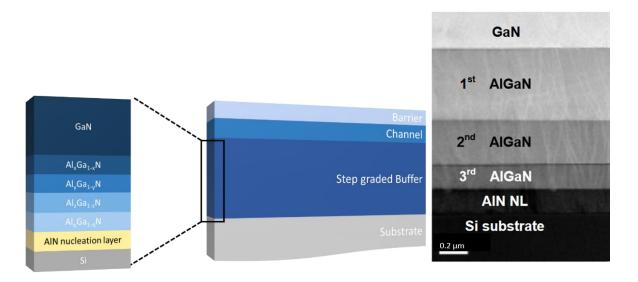

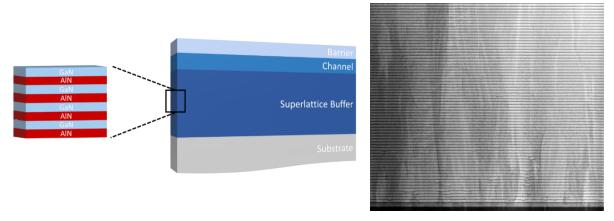

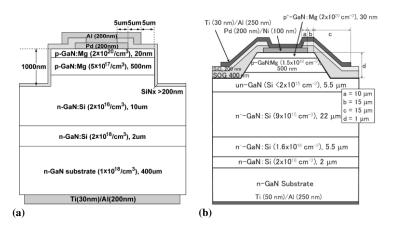

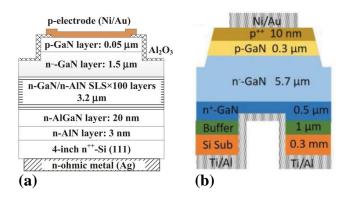

As will be described in detail in the paper, current GaN devices have typically a lateral layout. Several key aspects related to device design, fabrication and performance must be discussed in detail, to understand how the performance of the transistors can be optimized through careful device design: this will be done extensively in the following sections of this paper. For introductory purposes, we remind here that in a HEMT current flows between drain and source through a 2dimensional electron gas (2DEG), which is formed at the heterojunction between an AlGaN barrier and a GaN layer. Figure 1 (a) reports the schematic structure of a GaN-based HEMT, showing the main layers that constitute the structure. Power GaN devices are typically grown on a silicon substrate, to minimize cost and maximize yield. Growing GaN on a silicon substrate is particularly complicated, due to: a) the large mismatch of the in-plane thermal expansion coefficient (2.6x10<sup>-1</sup> <sup>6</sup> K<sup>-1</sup> for Si and 5.59x10<sup>-6</sup> K<sup>-1</sup> for GaN [27]), that may lead to cracking of the GaN layer during the cooling-phase after the epitaxial growth; b) the large lattice mismatch (around 16 % for Si(111)) [28], [29], that may result in the propagation of dislocations through the gallium nitride epitaxial layers, with consequent defect generation. A careful optimization of the buffer is needed in order to limit the propagation of such defects towards the 2DEG region; Figure 1 (b) reports a cross sectional SEM image of the epitaxial layers of a GaN-based transistor. As can be noticed, the use of a step-graded buffer in combination with an AlN nucleation layer is used to release the strain and prevent the formation/propagation of dislocations.

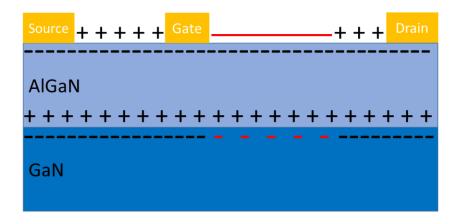

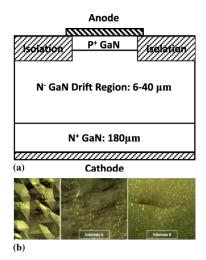

The lateral structure described in Figure 1 may have some limitations, when extremely high breakdown voltages and/or power densities are targeted. First, in a lateral transistor the breakdown voltage scales with the gate-drain spacing. Thus, devices with a high breakdown voltage can be fabricated, but will be more resistive and will use a wider semiconductor area, thus resulting in a higher device cost. Second, the density of electrons in the 2DEG can be strongly influenced by surface charges: for this reason, the performance of the final devices is strongly dependent on the process and backend. To solve the limitation of GaN lateral devices, vertical device structures are currently being explored and investigated, in line with what has been done with silicon and silicon carbide components. In a vertical device (see a schematic structure in Figure 1 (c)), current flows

through the bulk of the material, thus allowing high current and power densities. The density of electrons in the channel is modulated through a metal-oxide-semiconductor (MOS) stack, and a ptype body is usually employed to shift the threshold voltage towards more positive values. The breakdown voltage of a vertical GaN transistor depends on the thickness of the lightly-doped drift region, and not on the size and area of the device as in a lateral transistor. Vertical GaN devices represent the latest development in GaN technology, and the reader will find interest in the related concepts and applications, described in this paper.

As for every technology, there are some physical processes that may limit the performance and the reliability of GaN devices. The on-resistance of a GaN transistors (and thus the density of electrons in the 2DEG) strongly depends on the intrinsic (spontaneous and piezoelectric) polarization charges of GaN, as well as on the presence of charges trapped at surface states (e.g. in the passivation layer or at the interface between the passivation layer and the AlGaN barrier) or in buffer states. For this reason, it is of fundamental importance to know and manage the surface-and buffer-related trapping phenomena that may limit the dynamic performance of GaN transistors, leading to a recoverable increase in on-resistance (dynamic-Ron problem). Trapping in the epitaxial layers and/or at the gate-stack may result in positive- or negative-bias threshold instability (PBTI or NBTI), and the related processes must be investigated and understood to be able to fabricate fast and reliable devices.

Finally, GaN-based transistors are operated at field, temperature, and frequency levels which are unimaginable for conventional silicon devices. Electric fields can be in excess of 3 MV/cm, and channel temperatures can be above 300 °C during operation, if lightweight heat dissipators are used. Such conditions may favor sudden or time-dependent breakdown phenomena, leading to the failure of the devices. Furthermore, operation at high frequencies may exacerbate the degradation processes related to hard switching events. For this reason, it is of utmost importance to understand the degradation processes of GaN power devices, and to identify ways and strategies for improving the robustness of the components.

This tutorial paper presents a detailed overview on the physics, performance and reliability of GaN-based power devices. In the Section 3-5, the properties and physical parameters of gallium nitride are discussed, to help the reader understanding the unique advantages offered by GaN compared to other semiconductors. The main figures of merit (FOM) for high speed (Johnson

FOM) and high power (Baliga FOM) devices are also introduced. Finally, the properties of AlGaN/GaN heterostructures, and the related band diagrams are described in detail, and first-order formulas for the calculation of sheet electron charge and threshold voltage are introduced. In Section 6, the properties, structure and characteristics of lateral GaN devices are discussed. Specific details is given to the various approaches for normally-off operation, to the main device parameters, and to the optimization of the buffer. A perspective on AlN-based devices and on possible strategies to increase the breakdown voltage is given, also by discussing devices with local substrate removal. Section 7 deals with GaN vertical devices. First, the advantages of vertical GaN transistors are described. Attention is then given to the choice of the substrate (GaN-on-GaN vs GaN-on-Si) for vertical device manufacturing. Then, the various vertical device architectures are discussed and compared, in terms of performance and structural parameters. In Section 8, the stability of GaN devices is analyzed in detail. Specific focus is given to the role of surface traps, barrier traps and buffer traps in modifying the main device parameters, to present a clear overview of the topic. A complete overview of the dominant defects and deep levels in GaN is given in Section 8.1, to provide an exhaustive view of the problem. Finally, Section 9 describes the most relevant degradation processes that can limit the lifetime of GaN-based transistors. Specific attention will be towards the degradation mechanisms induced by exposure to off-state stress, semi-on state regime, and on-state degradation (with focus on gate reliability for p-GaN and insulated-gate devices).

Through a pedagogical approach, this paper helps the reader understanding the advantages of GaN technology, and getting familiar with the main performance, design, and reliability aspects.

Figure 1: (a) schematic representation of the structure of a lateral GaN high-electron mobility transistor (HEMT). The main layers constituting the structure are shown, as well as the three contacts of source (S), gate (G) and drain (D). (b) Cross-sectional SEM images of the epi-structure of GaN HEMT on silicon. Reprinted from "Strain Analysis of GaN HEMTs on (111) Silicon with Two Transitional Al<sub>x</sub>Ga<sub>1-x</sub>N Layers", Y. Cai et al., https://doi.org/10.3390/ma11101968, licensed under CC BY 4.0 (http://dx.doi.org/10.3390/ma11101968) [30]. (c) schematic representation of a vertical GaN trench-MOSFET

#### 3 Gallium nitride: properties and physical parameters

Gallium nitride, along with its InGaN and AlGaN alloys, represents an excellent material for both optoelectronics and electronics. In the early GaN era, the research efforts on gallium nitride have been driven by the need of fabricating high-efficiency short-wavelength (blue/violet) LEDs. GaN has a direct bandgap of 3.4 eV, thus being ideal for manufacturing ultraviolet optoelectronic devices. In addition, the energy gap of III-N alloys can be tuned between the 0.7 eV of InN and the 6.2 eV of AlN thus, in principle, allowing fabrication of LEDs with ultraviolet (UVA, UVB, UVC), visible and infrared emission.

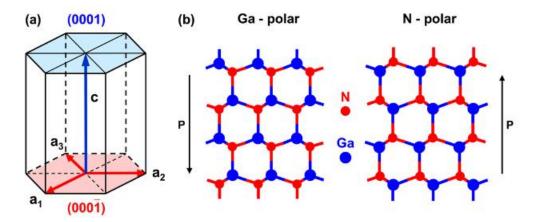

Contrary to other semiconductors, like InP or GaAs, III-N semiconductors typically have a wurtzite crystal, with its characteristic hexagonal shape (see Figure 2). It can be easily understood that this lattice arrangement does not have an inversion plane perpendicular to the c-axis (0001) and, for this reason, the surfaces have either atoms from group III (In, Ga, Al), or nitrogen atoms [31]. The nature of the surfaces has a fundamental importance, since it determines the polarity of the polarization charges, as will be discussed in the following.

Figure 2: (a) Hexagonal unit cell and (b) atomic structure of Ga- and N-polar GaN. The arrows represent the direction of the spontaneous polarization dipole, P, in the GaN crystal. From "Recent progress in metal-organic chemical vapor deposition of (0001) N-polar group-III nitrides", S. Keller et al., Semiconductor Science and Technology, Volume 29, Number 11, 113001, August 2014, DOI: 10.1088/0268-1242/29/11/113001, IOP Publishing. Reproduced with permission. All rights reserved. (<a href="https://iopscience.iop.org/article/10.1088/0268-1242/29/11/113001/pdf">https://iopscience.iop.org/article/10.1088/0268-1242/29/11/113001/pdf</a>) [32].

Table 1 reports the main parameters of gallium nitride, as compared with other semiconductor materials, including silicon, gallium arsenide, silicon carbide, aluminum nitride, diamond and gallium oxide. The materials are ordered with increasing energy gap E<sub>G</sub>, from left to right. Excluding the three semiconductors for which commercial devices are not available (gallium oxide, diamond, and aluminum nitride), GaN is the semiconductor with the largest energy gap, the largest critical field, and the highest saturation velocity. As a consequence, it is an ideal candidate for the fabrication of power semiconductor devices, capable of operating at high temperature and voltage levels.

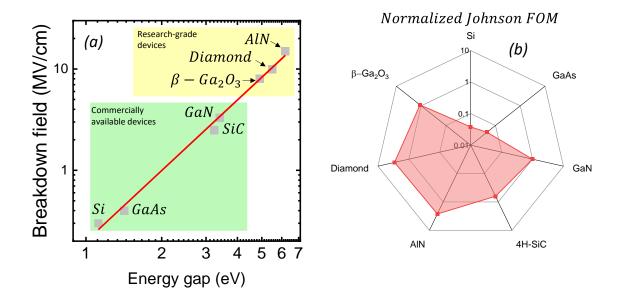

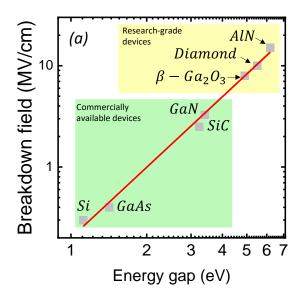

Figure 3 (a) reports the relation between breakdown field and energy gap for the semiconductor materials in Table 1. As can be noticed, breakdown field has a power-law dependence on the energy gap, in the form  $E_{crit} \propto E_G^{2.3}$ . This dependence is consistent with previous reports in the literature [33], and demonstrates the great advantage of using wide bandgap semiconductors for fabricating electron devices with high breakdown voltage.

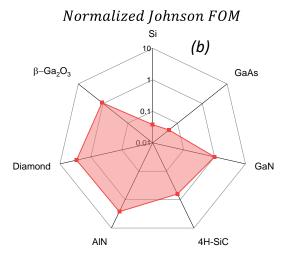

Since a single parameter does not fully describe the properties of a material, semiconductors are typically compared by using figures of merit: the most commonly used are the Johnson FOM, for high-speed devices, and the Baliga FOM, for high power devices. With regard to the first, it is defined as the product of the maximum voltage and the maximum transit frequency, for a given value of the drain-source spacing (see details in Ref. [34]), i.e. as:

$$Johnson FOM = f_T V_{DS,max} = \frac{E_{crit} v_s}{2\pi}$$

The Johnson figure of merit indicates that, in general, devices with high breakdown voltage are typically slower than devices with lower voltage rating.

Figure 3 (b) reports the values of the Johnson figure of merit for the semiconductors listed in Table 1; all values are normalized to that of GaN, to allow an easy comparison. As can be noticed, the Johnson FOM of GaN is slightly higher than that of SiC (0.556), comparable to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (0.978),

and is much larger than that of silicon (0.0379) and GaAs (0.0455). AlN and diamond are better than GaN, but their Johnson FOMs are between 2.5 and 3, thus having the same order of magnitude of GaN. While there is a substantial advantage by moving from Si/GaAs to GaN, the improvement obtained by changing to AlN and diamond is only incremental, in terms of the Johnson FOM [34].

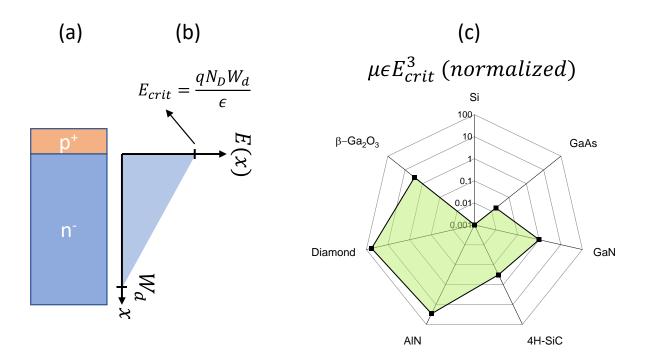

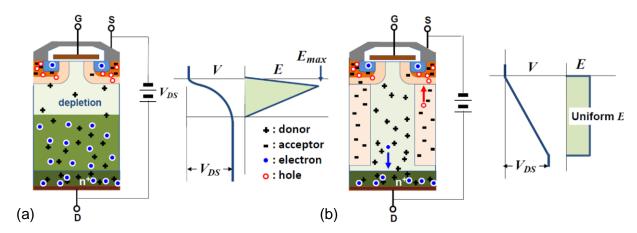

While the Johnson FOM allows to compare semiconductor materials for the fabrication of high-speed devices, the Baliga FOM has been introduced to compare semiconductors for application in power electronics. Considering a unilateral and abrupt (e.g.  $p^+/n^-$ ) junction, as depicted in Figure 4 (a), the electric field profile at the n-side has a triangular shape (Figure 4 (b)), and – at the critical electric field  $E_{crit}$  – the space charge region has a width equal to

$$W_d = \epsilon_{r,GaN} \epsilon_0 E_{crit} / q N_D$$

where  $N_D$  is the donor density at the n-side of the diode, and  $\epsilon_{r,GaN}\epsilon_0$  is the product between the relative permittivity of GaN and the permittivity of vacuum. The breakdown voltage is therefore

$$V_{br} = \frac{1}{2} E_{crit} W_d = \frac{\frac{1}{2} E_{crit}^2 \epsilon_{r,GaN} \epsilon_0}{q N_D}$$

The resistance  $R_{ON}$  of the n-type semiconductor region is proportional to  $W_d/\mu N_d$ , so we can calculate [35]

$$R_{ON} \propto \frac{W_d}{\mu N_D} \propto \frac{W_d^2}{\mu \epsilon_{r,GaN} \epsilon_0 E_{crit}} \propto \frac{4 V_{br}^2}{\mu \epsilon_{r,GaN} \epsilon_0 E_{crit}^3}$$

The denominator of the last term is linked to the Baliga FOM [36], [37] (that was initially defined as  $\mu \in E_G^3$ ), and identifies the material parameters that help minimizing the conduction losses in power transistors. This FOM is defined based on the assumption that power losses only originate from the on-resistance of the FET. For this reason, it applies at relatively moderate frequencies, where conduction losses are dominant [36]. For higher frequency devices, one would have to consider also the contribution of switching losses. Figure 4 (c) reports the Baliga figure of merit (calculated as  $\mu \in E_{crit}^3$ ) for the same set of semiconductors in Table 1. All values are normalized to GaN: the plot indicates that the Baliga FOM of GaN is substantially larger than those of silicon and GaAs, higher than SiC, similar to the one of gallium oxide. Diamond and AlN (ultra wide-

bandgap semiconductors) have a much higher Baliga FOM, and can be considered as interesting alternatives to further push the limits.

| Material                   | Si   | GaAs | 4H-SiC | GaN  | b-Ga <sub>2</sub> O <sub>3</sub> | Diamond | AlN  |

|----------------------------|------|------|--------|------|----------------------------------|---------|------|

| $E_G(eV)$                  | 1.12 | 1.42 | 3.23   | 3.4  | 4.9                              | 5.5     | 6.2  |

| $\epsilon_{ m r}$          | 11.7 | 12.9 | 9.66   | 8.9  | 10                               | 5.7     | 8.5  |

| μ (cm <sup>2</sup> /Vs)    | 1440 | 9400 | 950    | 1400 | 250                              | 4500    | 450  |

| E <sub>crit</sub> (MV/cm)  | 0.3  | 0.4  | 2.5    | 3.3  | 8*                               | 10*     | 15*  |

| $v_s (x10^7 \text{ cm/s})$ | 1    | 0.9  | 2      | 2.4  | 1.1                              | 2.3     | 1.4  |

| κ <sub>th</sub> (W/cmK)    | 1.3  | 0.55 | 3.7    | 2.5  | 0.1-0.3                          | 23      | 2.85 |

Table 1: main material parameters for GaN, as compared with other semiconductors. Reported parameters are energy gap ( $E_G$ ), relative dielectric permittivity ( $\epsilon_r$ ), electron mobility ( $\mu$ ), critical electric field ( $E_{crit}$ ), electron saturation velocity ( $v_s$ ), and thermal conductivity ( $\kappa_{th}$ ). Data are taken from: P. Fay et al.,High-Frequency GaN Electronic Devices, <a href="https://doi.org/10.1007/978-3-030-20208-8-2">https://doi.org/10.1007/978-3-030-20208-8-2</a> [34] (\*Estimated). The critical electric field of GaN is taken from Ref [12]. Note that for GaN mobility values up to 2000 cm²/Vs are reported, see for instance [12].

Figure 3: (a) dependence of breakdown field on energy gap for the semiconductor materials in Table 1. (b) Johnson figure of merit for the same set of semiconductors. All values are normalized to GaN, to allow an easy comparison. Data are taken from Table 1

Figure 4: (a) schematic representation of a unilateral abrupt  $p^+/n^-$  junction; (b) approximated electric field profile for the junction in (a); (c) Baliga figure of merit (calculated as  $\mu \epsilon E_{crit}^3$ ) for the same set of semiconductors in Table 1. All values are normalized to GaN, to allow an easy comparison. Data are taken from Table 1

The dependence of the bandgap of GaN on temperature follows the Varshni relation

$$E_G(T) = E_{G,0} - \frac{\alpha T^2}{T + \beta}$$

For GaN, AlN and InN the related parameters are summarized in Table 2. As can be noticed, by using alloys of GaN, AlN and InN it is possible to vary the bandgap of the alloy in a wide range,

from 0.7 eV to 6.2 eV. In most cases, GaN transistors are based on AlGaN/GaN heterostructures, and AlN and AlGaN layers are used as nucleation and buffer layers respectively. InAlN devices have also been investigated: lattice matched InAlN/GaN HEMTs allow an efficient down-scaling of the transistor dimensions, thus allowing to reach high cut-off frequencies [38].

For ternary alloys, such as AlGaN and InGaN, the bandgap deviates from the Vegard's rule, and follows the empirical expression

$$E_G(A_x B_{1-x} N) = x E_G(AN) + (1-x) E_G(BN) - x(1-x)b$$

where  $E_G(AN)$  and  $E_G(BN)$  are the bandgaps of the two materials (AN and BN), x is the molar fraction of A, and b is a bowing parameter. For AlGaN, the material of interest for Al<sub>x</sub>Ga<sub>(1-x)</sub>N/GaN HEMTs, the relation has been determined as [39], [40]

$$E_{G(AlGaN)}(x) = [6.0x + 3.42(1 - x) - 1.0x(1 - x)] eV$$

Other bandstructure parameters of interest for GaN are the effective density of states in the conduction and valence bands ( $N_C = 2.24 \cdot 10^{18} \ cm^{-3}$ ,  $N_V = 4.56 \cdot 10^{19} \ cm^{-3}$ ), and the effective masses of electrons and holes ( $m_e = 0.20$  and  $m_h = 1.49$ ) [34]

|     | $E_{G,0}(eV)$ | $\alpha \left(\frac{meV}{K}\right)$ | β (K) |

|-----|---------------|-------------------------------------|-------|

| GaN | 3.507         | 0.909                               | 830   |

| AlN | 6.23          | 1.799                               | 1462  |

| InN | 0.69          | 0.414                               | 454   |

Table 2: bandgap and Varshni parameters for GaN, AlN and InN. For GaN, results data are taken from [41], for AlN from [42], for InN from [43].

### 4 Polarization charges in GaN

Controlled doping of wide bandgap semiconductors is not always straightforward: typically, mobile carriers in FET are induced through impurity doping, i.e. by introducing foreign atoms in

a semiconductor lattice. The energy distance between the dopant level and the related band ( $E_C - E_D$  for a donor level at energy  $E_D$ , or  $E_A - E_V$  for an acceptor level at energy  $E_A$ ) represents the dopant binding (or ionization) energy. The best dopants are relatively shallow, with binding energies in the range 0.01 eV - 0.05 eV. For GaN, only shallow donors are available (silicon,  $E_C - E_D = 0.015$  eV), while the conventional acceptor is magnesium, that creates a level 0.16 eV above the valence band energy. As a consequence, it is relatively easy to achieve high electron concentrations, whereas for reaching high hole densities dopant levels in excess of  $10^{19}$  cm<sup>-3</sup> are required. It is worth noticing that even high quality GaN has a residual n-type (unintentional) conductivity, resulting in carrier densities in the range  $10^{15} - 10^{17}$  cm<sup>-3</sup>, depending on material properties. Such residual conductivity has been ascribed to native defects of the semiconductor (e.g. point defects, vacancies, antisites), and impurities (like carbon, oxygen, hydrogen) [40]. The suppression of such defect-induced free carriers is very important for the fabrication of highly-insulating GaN layer, to be used in devices with extremely high blocking voltages.

Contrary to conventional semiconductors, GaN has a unique advantage, that helps obtaining high carrier densities even in absence of intrinsic doping: gallium nitride, in fact, is a polar material, and exhibits strong polarization effects.

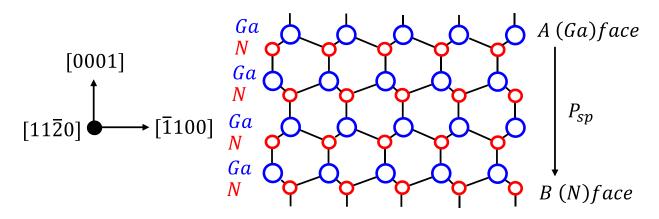

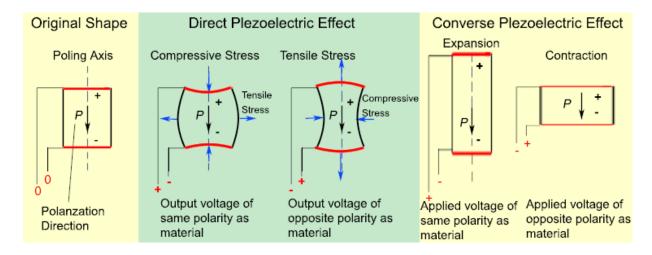

As already mentioned, the wurtzite crystal of III-N semiconductors, which are typically grown epitaxially along the (0001) orientation, leads to the existence of polarization fields, that are both spontaneous and piezoelectric. With zero external field, the total polarization P is equal to the sum of the spontaneous polarization  $P_{sp}$  and of the piezoelectric (or strain-induced) polarization  $P_{pz}$ . Bernardini et al. [44] investigated the polarization in GaN layers along the (0001) axis. Nitrogen has a higher electronegativity, compared to gallium. As a consequence, Ga and N atoms have anionic (+) and cationic (-) characteristics, generating a spontaneous polarization  $P_{sp}$  along the (0001) axis [35]. Wurtzite is the crystal arrangement with highest symmetry compatible with the presence of spontaneous polarization [44]–[46]. The arrangement of the cation and anion sublattices can lead to a relative movement from the ideal wurtzite position, favoring the spontaneous polarization [47]. The orientation of spontaneous polarization is defined assuming that the positive direction goes from the metal (Ga) to the nearest nitrogen atom, along the c-axis [48]. Figure 5 depicts the crystal structure of GaN, and the sign and direction of the spontaneous polarization.

The values of the spontaneous polarization in GaN, InN and AlN are reported in Table 3 for binary semiconductors. In the case of interfaces between binary and ternary semiconductors, the following expressions can be used (see also [49] and references therein):

$$P_{sp,Al_xGa_{1-x}N / GaN}(x) = (-0.052x - 0.029) [C \cdot m^{-2}]$$

$$P_{sp,In_xGa_{1-x}N / GaN}(x) = (-0.003x - 0.029) [C \cdot m^{-2}]$$

$$P_{sp,In_xAl_{1-x}N / GaN}(x) = (0.049x - 0.081) [C \cdot m^{-2}]$$

Figure 5: crystal structure of GaN, showing the sign and direction of the spontaneous polarization (adapted from Ref. [50])

| Material | GaN (C m <sup>-2</sup> ) | InN (C m <sup>-2</sup> ) | AlN (C m <sup>-2</sup> ) |

|----------|--------------------------|--------------------------|--------------------------|

| $P_{sp}$ | -0.029                   | -0.032                   | -0.081                   |

| $P_{sp}$ | -0.034                   | -0.042                   | -0.090                   |

Table 3: values of spontaneous polarization of III-N semiconductors (binary). Values in the first row are from [44], values in second row are from [51].

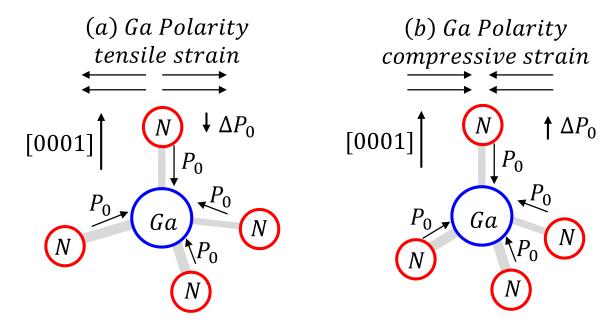

The strain in the crystal, and the displacement of the anion sublattice with respect to the cation sublattice, can lead to a piezoelectric polarization of the III-N semiconductors. A (simplified)

representation of the polarization is given in Figure 6, that reports a ball and stick diagram of the bond (theahedral) between gallium and nitrogen. In this figure, the Ga-polar configuration is represented. The electron cloud is closer to the nitrogen atoms, and this generates the polarization vectors. If the tetrahedron is ideal, the in-plane and vertical polarization components cancel each other [52]. When an in-plane tensile strain is applied (as shown in Figure 6, (a)) the polarization generated by the triple bonds decreases, and this generates a net polarization along the  $(000\overline{1})$  direction. On the contrary, when an in-plane compressive strain is applied (as shown in Figure 6, (b)) the polarization generated by the triple bonds increases, and this generates a net polarization along the (0001) direction.

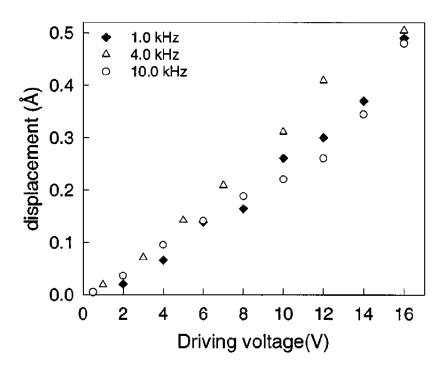

To calculate the piezoelectric polarization, one needs to refer to the piezoelectric constants of the materials under analysis. Details on the main parameters were given in [44], [48], [53], and a comprehensive summary was presented in [49]; here, in Table 4, we report the values of piezoelectric constants  $e_{ij}$  and lattice parameters  $a_0$  and  $c_0$  for GaN, InN and AlN.

As discussed in [48], the lattice structure of wurtzite semiconductors is defined by the length of the hexagonal edge  $a_0$ , the height of the prism  $c_0$ , and a parameter u that defines the length of the bond parallel to the c-axis ([0001]) in units of  $c_0$ . To calculate the piezoelectric polarization  $P_{pz}$  along the c-axis, the key relation is

$$P_{pz} = e_{33}\epsilon_z + e_{31}(\epsilon_x + \epsilon_y)$$

Here  $\epsilon_z = (c - c_0)/c_0$  represents the strain along the c-axis, while the in-plane strain  $\epsilon_x = \epsilon_y = (a - a_0)/a_0$  is assumed to be isotropic. a and c are the lattice constants of the strained layers, and differ from  $a_0$  and  $c_0$ .

By considering that the lattice constants in a hexagonal AlGaN system are related according to

$$\frac{c - c_0}{c_0} = -2\left(\frac{C_{13}}{C_{33}}\right)(a - a_0)/a_0$$

where  $C_{13}$  and  $C_{33}$  are elastic constants, the value of piezoelectric polarization along the c-axis can be calculated as

$$P_{pz} = 2(a - a_0)/a_0 \left(e_{31} - \frac{e_{33}C_{13}}{C_{33}}\right)$$

For an  $Al_xGa_{1-x}N/GaN$  stack, the material system of interest for GaN-based transistors, the values of the elastic constants can be calculated from the following formulas (see [49], [54] for details)

$$C_{13}(x) = (5x + 103) [GPa]$$

$C_{33}(x) = (-32x + 405) [GPa]$

and the variation of the lattice constant with the molar fraction is

$$a(x) = (-0.077x + 3.189) \cdot 10^{-10} m$$

Figure 6: schematic ball-and-stick configuration of a GaN tethrahedron with in-plane (a) tensile and (b) compressive strain, showing a net polarization. A full description including also the case of N-polar material can be found in [52].

| Material                           | GaN        | InN        | AlN                   |

|------------------------------------|------------|------------|-----------------------|

| $e_{31}\left(C\cdot m^{-2}\right)$ | -0.49 [44] | -0.57 [44] | -0.6 [44], -0.58 [54] |

| $e_{33} (C \cdot m^{-2})$ | 0.73 [44] | 0.97 [44] | 1.46 [44], 1.55 [54] |

|---------------------------|-----------|-----------|----------------------|

| a <sub>0</sub> (Å)        | 3.189     | 3.54      | 3.112                |

| c <sub>0</sub> (Å) [48]   | 5.185     | 5.705     | 4.982                |

Table 4: values of piezoelectric constants  $e_{ij}$  and lattice parameters  $a_0$  and  $c_0$  for GaN, InN and AlN

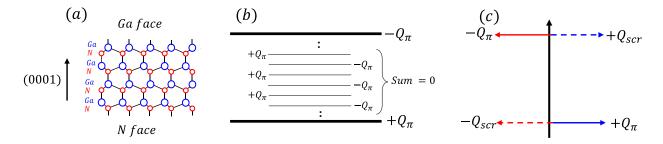

In a GaN layer, polarization charges are present on each unit cell. As schematically depicted in Figure 7, the internal polarization charges cancel each other. Only the  $Q_{\pi}$  and  $-Q_{\pi}$  at the N- and Ga-faces remain, and form a charge dipole (Figure 7 (c)). Based on the numbers given in Table 3, the spontaneous polarization charge in GaN has values in the range  $1.8 - 2.1 \cdot 10^{13} \, e^{-/cm^2}$ . In absence of other charges, the polarization charge would lead to the presence of a dipole, resulting in a fairly high electric field, in the range of MV/cm. Such dipole is screened through the formation of a screening dipole ( $Q_{scr}$ ). In absence of the screening dipole, a non-physical situation would form. As discussed in [47], a first hypothesis would be that the screening dipole originates from ions from the atmosphere ( $H^+$ ,  $OH^-$ ); however, the dipole is present also in material grown in atmosphere free of counter ions, like during molecular beam epitaxy (MBE) growth.

A different interpretation can be given by considering the presence of donor states at the surface of the GaN layer [55], [56], as schematically represented in Figure 8 (a). In absence of compensating charge, due to the presence of the polarization dipole  $\pm Q_{\pi}$ , an electric field is present in the GaN layer, and the band diagram shows a linear slope (Figure 8 (b)). If the GaN layer is sufficiently thick, the donor states pins the Fermi level at the surface (at the donor level  $E_{DD}$ ), and the screening charge  $N_{DD}^+$  at the surface is formed. The presence of a surface level  $E_{DD}$  has been proved also experimentally [47]. Realistic GaN layers typically have a n-type conductivity, as mentioned above. The ionized (bulk) donors also contribute to the overall charge balance. For a thick GaN layer (see Figure 8 (d)), the bands are nearly flat (corresponding to negligible field), apart from the surface region. The polarization charge  $-Q_{\pi}$  at the surface is compensated by the positive charge of the ionized surface defects  $N_{DD}^+$  and by the total density of charges in the depleted n-type GaN [47].

Figure 7: (a) schematic representation of a GaN lattice with ball and stick representation of the bonds, and indication of the Ga- and N-faces, along the (0001) direction. (b) model for polarization charge in a gallium nitride layer. (c) charge distribution at the Ga- and N-faces, showing the polarization and screening dipoles (see also [47])

Figure 8: (a) schematic representation of a n-type GaN layer grown on a substrate. The (defective) interface region is shown. (b) charge diagram showing the screening induced by surface donors. (c) band diagram showing the surface donor level approaching the Fermi level at the surface of GaN, thus leading to the generation of the screening charge  $qN_{DD}^+$ . (d) band diagram for a thick

GaN (n-type), considering the presence of surface states and of donor charges (figure adapted from [47])

# 5 Band diagrams and charge density in AlGaN/GaN heterostructures

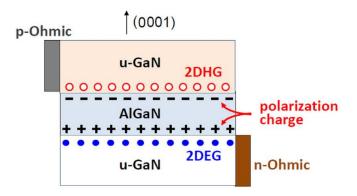

The core of a GaN-based HEMT is the AlGaN/GaN heterostructure. Both the GaN and the AlGaN layers are typically left undoped, to minimize electron scattering at impurities. Based on the considerations above, undoped GaN has a weak n-type conductivity, with electron densities that depend on the quality of the epitaxy, and that – even in the best case – are higher than  $10^{15}$  cm<sup>-3</sup> [47] (early GaN films were showing a high n-type conductivity, in the range of  $10^{17}$ - $10^{18}$  cm<sup>-3</sup> [57], [58]). Optimizing the background electron density in lateral and vertical HEMTs requires a tuning of the growth process, and the control of the residual impurities (such as carbon, see for instance [59]).

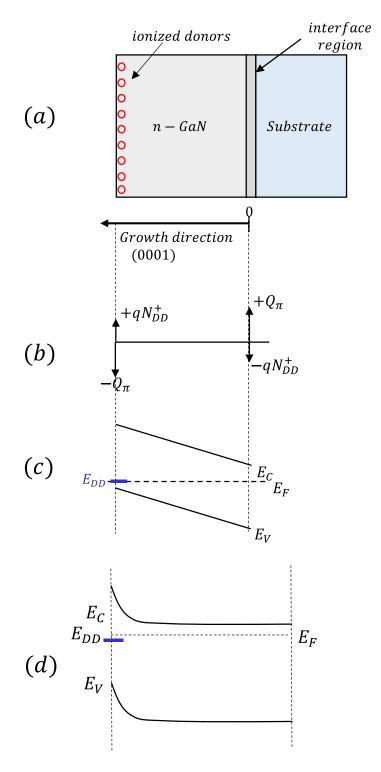

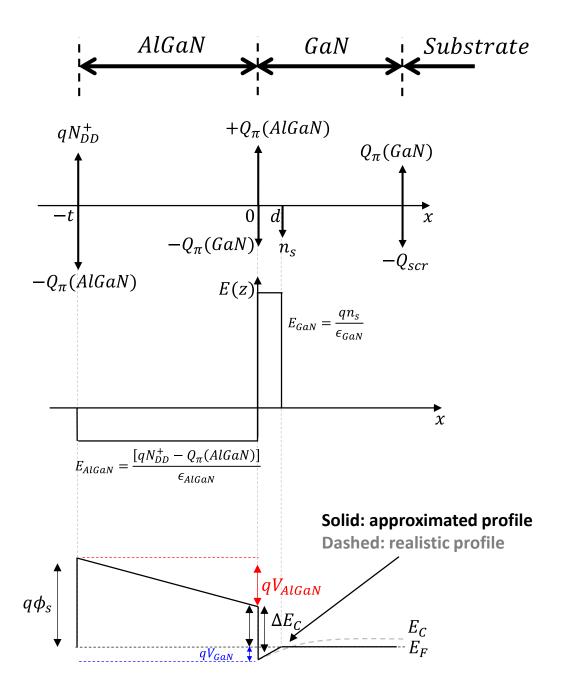

Figure 9 shows the charge distribution, the electric field profile, and a schematic band diagram for an AlGaN/GaN heterostructure used in HEMT technology. In the figure, t is the thickness of the AlGaN layer, while the 2DEG is supposed to be located at a position d, a few nanometers far from the heterojunction, on the GaN side.

At the surface of the AlGaN layer, the total charge is determined by the sum of the charge of the surface donors and of the polarization charge of the AlGaN layer,  $qN_{DD}^+ - Q_{\pi(AlGaN)}$ . At the AlGaN/GaN heterojunction, the total charge is given by the difference between the polarization charges of AlGaN and GaN, i.e.  $Q_{\pi(AlGaN)} - Q_{\pi(GaN)}$ . For gallium polar material, this is a positive number, since AlGaN has a higher polarization, compared to GaN. In the triangular potential well formed near the heterojunction, on the GaN side, a 2-dimensional electron gas is formed. For simplicity, we consider this sheet of charge to be located in x = d (position of the centroid of the electron distribution).

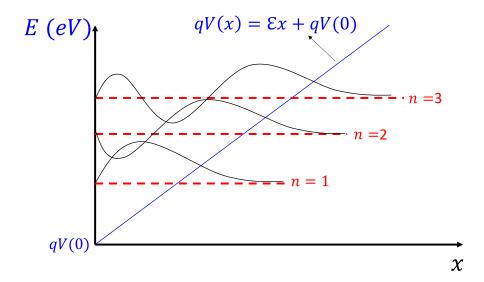

The value of d can be easily determined by solving the Schroedinger equation in the triangular potential well formed at the AlGaN/GaN interface, that is schematically represented in Figure 10.

The electric field  $\mathcal{E}_{GaN}$  is supposed to originate only from the charge in the 2DEG  $(n_s)$ , and is thus equal to  $qn_s/(\epsilon_0\epsilon_{GaN})$ . The solution of the Schroedinger equation is approximated by the formula [60]–[62]

$$E_{n} \approx \left(\frac{\hbar}{2m^{*}}\right)^{\frac{1}{3}} \left(\frac{3}{2}\pi q \mathcal{E}_{GaN}\right)^{\frac{2}{3}} \left(n + \frac{3}{4}\right)^{\frac{2}{3}} = \left(\frac{\hbar}{2m^{*}}\right)^{\frac{1}{3}} \left(\frac{3}{2}\pi q\right)^{\frac{2}{3}} \left(n + \frac{3}{4}\right)^{\frac{2}{3}} \left(\frac{q n_{s}}{\epsilon_{0} \epsilon_{GaN}}\right)^{\frac{2}{3}}$$

We now consider that the first sub-band  $E_0$  is dominant. The 2D density of states associated with a single quantized level is [62]

$$D_{DOS} = \frac{qm^*}{\pi\hbar^2}$$

The electron concentration in the 2DEG can then be calculated starting from the 2D density of states and from the position of the Fermi level, by using the Fermi-Dirac distribution as follows [62]:

$$n_{s} = D_{DOS} \cdot \frac{kT}{q} \cdot \ln \left[ 1 + \exp \frac{q(E_{F} - E_{0})}{kT} \right]$$

where k is the Boltzmann constant.

By simple calculations (see details in Ref. [47]), one can calculate the position d of the 2DEG, with respect to the heterointerface. Here the 2DEG is considered as an ideal 2D sheet of electrons located at a distance d from the interface, on the GaN side. For an AlGaN/GaN heterostructure, a typical value of d is 2 nm [47].

At the bottom of the GaN layer, at the interface with the substrate, a screening charge compensates the (positive) component  $Q_{\pi(GaN)}$ . The reader should note that in more realistic structures other layers (e.g. a C-doped layer, a step-graded or a superlattice-based buffer, an AlN nucleation layer) are placed between the GaN channel layer and the substrate; these layers are not shown here for simplicity.

At the surface of the AlGaN layer (if the layer is thick enough), the potential  $q\phi_s$  is pinned at the surface donor level  $E_{DD}$ . The AlGaN layer is not doped, so – in absence of external bias – its electric field depends only the sheet charge densities as follows:

$$\xi_{AlGaN} = \frac{[qN_{DD}^{+} - Q_{\pi}(AlGaN)]}{\epsilon_{0}\epsilon_{AlGaN}}$$

With regard to the electric field in the GaN, we suppose that it originates only from the charge in the 2DEG, and neglect (for this analysis) the effect of the n-type donor charge in the GaN. A more realistic solution can be obtained numerically, through technology computer-aided design (TCAD) tools. Under this assumption, the electric field in the GaN is

$$\mathcal{E}_{GaN} = \frac{qn_s}{\epsilon_0 \epsilon_{GaN}}$$

The total potential drop in the AlGaN is then

$$V_{AlGaN} = -\mathcal{E}_{AlGaN}t = -\frac{[qN_{DD}^{+} - Q_{\pi}(AlGaN)]}{\epsilon_{0}\epsilon_{AlGaN}}t = \frac{[Q_{\pi}(AlGaN) - Q_{\pi}(GaN) - qn_{s}]}{\epsilon_{0}\epsilon_{AlGaN}}t$$

and, for GaN

$$V_{GaN} = \mathcal{E}_{GaN}d = \frac{qn_s}{\epsilon_0 \epsilon_{GaN}}d$$

Considering the band diagram in Figure 9, one can calculate

$$\phi_s - V_{AlGaN} - \frac{\Delta E_c}{q} + V_{GaN} = 0$$

By combining the equations above, by considering  $\epsilon = \epsilon_0 \epsilon_{GaN} \sim \epsilon_0 \epsilon_{AlGaN}$ , the value of the sheet-charge density  $n_s$  can be calculated

$$n_s = \frac{[Q_{\pi}(AlGaN) - Q_{\pi}(GaN)]t - \epsilon \quad (\phi_s - \frac{\Delta E_C}{q})}{q(t+d)}$$

When a potential  $V_G$  is applied to the gate (through a suitable metal deposited on the AlGaN barrier), the charge in the 2DEG can be modulated: a more positive voltage will fill the channel, whereas moving to negative values of  $V_G$  will lead to the depletion of the 2DEG.

The dependence of  $n_s$  on  $V_G$  has the following form:

$$n_s(V_G) = \frac{\left[Q_{\pi}(AlGaN) - Q_{\pi}(GaN)\right]t + \epsilon \left[V_G - \left(\phi_b - \frac{\Delta E_C}{q}\right)\right]}{q(t+d)}$$

where  $\phi_b$  is the barrier at the metal/AlGaN interface.

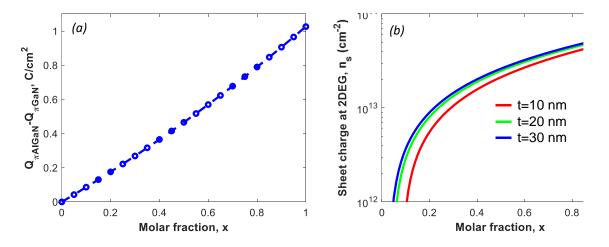

Figure 11 (a) reports the value of the polarization charge  $Q_{\pi}(AlGaN) - Q_{\pi}(GaN)$  at the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface as a function of the molar fraction x. The values have been calculated based on the parameters given in Ref, [54] as:

$$Q_{\pi}(AlGaN) - Q_{\pi}(GaN) = Q_{\pi,pz}(AlGaN) + Q_{\pi,sp}(AlGaN) - Q_{\pi,sp}(GaN)$$

$$= \left| \frac{2(a(0) - a(x))}{a(x)} \left[ e_{31}(x) - e_{33}(x) \cdot \frac{C_{13}(x)}{C_{33(x)}} \right] + Q_{\pi,sp}(x) - Q_{\pi,sp}(x) \right|$$

where the spontaneous polarization charge in an Al<sub>x</sub>Ga<sub>1-x</sub>N layer is defined as

$$Q_{\pi,sp}(x) = (-0.052x - 0.029) \left[ \frac{C}{m^2} \right]$$

A typical range of interest for the mole fraction is between 0.2 and 0.4; such values are sufficiently high to give a reasonable polarization charge (which is necessary for generating electrons in the 2DEG), and enough conduction band discontinuity at the AlGaN/GaN heterointerface (which is necessary to ensure a good confinement of the 2DEG electrons). At the same time, the use of molar fractions higher than 0.4 may be critical, since the thermal and lattice mismatch between AlGaN and GaN may lead to high defect density and rough interfaces, that may limit the overall device performance.

Figure 11 (b) reports the sheet charge density  $(n_s)$  of the 2DEG for three Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interfaces, as a function of the Al mole fraction and of the thickness of the AlGaN layer. For the calculation, a Schottky barrier equal to

$$q\phi_b = 1.3x + 0.84 \, eV$$

was used, and the conduction band discontinuity at the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface was calculated as

$$\Delta E_C = 0.7[E_G(x) - E_G(0)]$$

with

$$E_G(x) = x \cdot 6.13 \ eV + (1 - x) \cdot 3.42 \ eV - x(1 - x) \cdot 1 \ eV$$

in agreement with Ref. [54].

As can be noticed, when the mole fraction x is around 0.2-0.3, the sheet charge density is around  $10^{13}$  cm<sup>-3</sup>. With increasing thickness of the AlGaN layer, the density of electrons in the 2DEG increases, since the conduction band at the channel edge drops further below the Fermi level at the AlGaN/GaN interface (see also the band diagram in Figure 9). As can be understood, AlGaN/GaN HEMTs are intrinsically normally-on. At zero gate bias, the channel is formed, with a high electron density. A first possible approach to change the threshold voltage (by keeping the same Al content in the barrier) is to reduce the thickness of the AlGaN barrier. For sufficiently thin AlGaN barriers, the electron density falls to zero, and the 2DEG vanishes. This effect has also been observed experimentally, see for instance Ref. [55]. This is just one of the possible approaches to achieve normally-off operation in HEMTs; an excessive thinning of the barrier, along with the related etching process, may result in a significant increase in the leakage, and counter measures are required to guarantee a good device performance. In the next sections, the various approaches for normally-off operation are compared critically.

Figure 9: charge distribution, electric field profile, and schematic band diagram of an AlGaN/GaN heterostructure

Figure 10: triangular potential well, similar to the one formed at the GaN-side of an AlGaN/GaN interface. The energy varies linearly with field  $\mathcal{E}$ , starting from the value qV(0) at the GaN-side of an AlGaN/GaN interface. The energy levels and wavefunctions are schematically drawn (not to scale). Figure is adapted from Ref [63].

Figure 11: (a) polarization charge density at the AlGaN/GaN heterointerface  $(Q_{\pi}(AlGaN) - Q_{\pi}(GaN))$  calculated as described in [54]. (b) sheet charge density calculated for the 2DEG of an AlGaN/GaN heterojunction as a function of molar fraction x and thickness t of the AlGaN layer

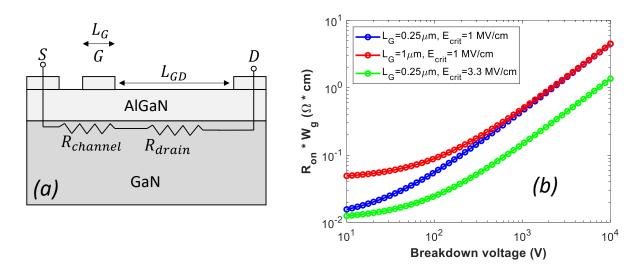

In a GaN-based transistor, a gate metal is placed on an AlGaN/GaN heterostructure; the resulting schematic structure is shown in Figure 12 (a). For a power semiconductor device, the most critical parameters are the on-resistance  $R_{on}$  (that needs to be as low as possible, to minimize the resistive losses in power converters) and the breakdown voltage ( $V_{br}$ , that must be sufficiently high to ensure good reliability). In AlGaN/GaN HEMTs, these two parameters are strongly correlated: carriers are generated by polarization, and the breakdown voltage scales with the distance between the gate and drain ( $L_{GD}$ ) [35]. In an first-order approximation, the on-resistance of the device is the sum of the channel resistance ( $R_{channel}$ , originated from 2DEG under the gate) and of the drain-side access region ( $R_{drain}$ ), according to the following equation [35]:

$$R_{on} = R_{channel} + R_{drain} = \frac{L_G}{W_G} \cdot \frac{1}{q\mu n_s} + \frac{L_{GD}}{W_G} \cdot \frac{1}{q\mu n_s}$$

It is worth noticing that in this calculation the contribution of the source and contact resistance is neglected, with no loss of generality. The off-state voltage is supported by the gate-drain access region; at the breakdown voltage, the relation between gate-drain spacing and the breakdown voltage is  $L_{GD} = V_{br}/E_{crit}$ , and we can write:

$$R_{on} = R_{channel} + R_{drain} = \frac{1}{W_G} \frac{1}{q \mu n_s} \left( L_G + \frac{V_{br}}{E_{crit}} \right)$$

In high-voltage devices, the gate-drain spacing is typically longer than the gate length. Figure 6 (b) reports the variation of the on-resistance (multiplied by the gate width  $W_g$ ) as a function of the target breakdown voltage for devices having different gate lengths (0.25  $\mu$ m and 1  $\mu$ m). For mobility and sheet charge density values of 1400 cm<sup>2</sup>/Vs and 10<sup>13</sup> cm<sup>-2</sup> were used. As can be understood, for low-breakdown voltage devices (corresponding to devices with a short gate-drain distance), the on-resistance is strongly determined by the gate length. Decreasing the gate length from 1  $\mu$ m to 0.25  $\mu$ m can lead to a substantial reduction in the resistive losses. On the contrary, for high breakdown voltage devices, the resistive contribution of the gate-drain access region becomes relevant, and  $R_{on}$  scales with the breakdown voltage. Figure 6 (b) also shows that the use of GaN devices with nearly-ideal breakdown field (3.3 MV/cm, see Table 1) can lead to a substantial improvement in on-resistance, compared to the more conservative case of 1 MV/cm

reported in previous publications [35]. Optimizing the breakdown field of the material is a key step for minimizing the resistive losses in power semiconductor devices.

Figure 12: (a) schematic representation of the structure of a GaN HEMT, showing the parasitic resistance of the channel ( $R_{channel}$ ) and of the gate-drain access region ( $R_{drain}$ ). (b) dependence of the product  $R_{on} \cdot W_g$  on breakdown voltage, for devices with different gate length, and under the hypothesis that the breakdown field is 1 MV/cm and 3.3 MV/cm

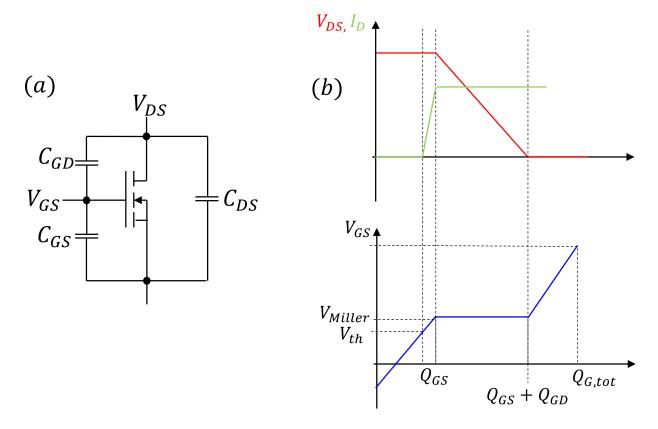

Besides resistive losses, also switching losses can play a relevant role in limiting the efficiency of a switching mode power converter. One of the parameters used to quantify the switching losses related to a specific transistor is the gate charge  $Q_G$ . For understanding the meaning of this parameter, we consider the simple circuit in Figure 12 (a). Here the FET is supposed to be ideal, and three capacitances  $C_{GS}$ ,  $C_{GD}$ , and  $C_{DS}$  are added to model the parasitic capacitive components. A fixed current is forced into the gate, and the measured gate voltage is plotted as a function of the charge flowing towards the gate. Figure 12 (b) shows the schematic gate-charging curve, during a turn-on event, i.e. when the device switches from the off-state (high drain voltage, zero current) to the on-state (low-drain voltage, high current). At device turn-on, the gate-source voltage  $V_{GS}$  increases; when  $V_{GS}$  reaches the threshold voltage  $V_{th}$ , current starts flowing through the device. At the same time, the gate-source capacitance  $C_{GS}$  is charged, until the  $V_{Miller}$  voltage (and

the corresponding plateau) is reached. At this point,  $C_{GS}$  is completely charged, and the drain current reaches the value fixed by the circuit. At the same time,  $V_{GS}$  becomes almost constant, and the drive current starts charging the Miller capacitance  $C_{GD}$ . This process goes on until the capacitance  $C_{GD}$  is fully charged. When both  $C_{GS}$  and  $C_{GD}$  are fully charged, the gate voltage starts increasing again. Through this experimental procedure the charges  $Q_{GS}$  and  $Q_{GD}$  can be calculated. The gate charge  $Q_{GS} + Q_{GD}$  is the minimum charge required to turn on the transistor [64], and is thus representative of the switching losses.

A low value of  $Q_{GS} + Q_{GD}$  results in the device's ability to achieve high commutation speed (dV/dt), and in a substantial reduction in switching losses [65]. A low gate charge also results in a reduced gate drive power for GaN devices, compared to silicon components [66]. Since, as stated above, the dc losses depend on the  $R_{on}W_{G}$  product, and the ac losses are proportional to  $Q_{G}/W_{G}$  [35], the  $R_{on} \cdot Q_{G}$  product is an important parameter describing the switching efficiency of a given device. In a recent paper [67], Chen et al. compared devices based on silicon, silicon carbide and gallium nitride in terms of figures of merit. They showed that, for devices with comparable onresistance, the  $R_{on} \cdot Q_{G}$  product can be around 3800  $m\Omega \cdot nC$  for a silicon superjunction MOSFET, in the range 1950 – 3480  $m\Omega \cdot nC$  for SiC-based FETs, and around 290 – 300  $m\Omega \cdot nC$  for a Emode GaN transistor. This result indicates that GaN E-mode HEMTs can contribute to a substantial reduction in switching losses, compared to conventional semiconductor transistors.

A further advantage of GaN-based transistors is the absence of reverse-recovery charge. Silicon-based power transistors have an intrinsic body diode, whose presence results in a large reverse recovery charge during commutation. For a silicon superjunction (SJ) MOSFET, the product of on-resistance ( $R_{DS,ON}$ ) and reverse-recovery charge ( $Q_{rr}$ ) can be in excess of 300 m $\Omega\mu$ C [67]. On the other hand, lateral GaN devices are based on the high-electron mobility transistor (HEMT) concept, and do not have any body diode. HEMTs are majority carrier devices, and the lack of minority carriers leads to a near-zero  $Q_{rr}$  ( $R_{DS,ON}$  x  $Q_{rr}$  down to 2.2 m $\Omega\mu$ C [67]), with beneficial impact on the switching losses.

Figure 13: (a) schematic circuit for understanding the dependence of gate charge on gate voltage during device turn-on; (b) voltage, current, and gate charge characteristics for a generic field-effect transistor during a gate-charge measurement

# 6 Lateral GaN transistors: technology and operation

The rapid evolution of wide bandgap semiconductors in the recent years has positioned lateral GaN transistors as key enablers in the power device market. The interest in power applications has undergone a remarkable shift due to the technological advantages of GaN HEMTs, which allow for simultaneous high voltage, high current and low on-state resistance, resulting in high power and high efficiency operation. In addition, the wide bandwidth provides a robust and reliable technology capable of operating at high frequency and high temperature. This is why GaN-based lateral power electronic devices are emerging as switching components for next generation highefficiency power converters. Furthermore, GaN-on-Silicon technology platform offers the best cost figures for commercialization of these products, although technologically very challenging. For instance, a complex GaN buffer for stress management and insulation purpose is required. This paves the way for a growing number of applications in various fields, including consumer electronics, transportation and energy, as well as several industrial, automotive and aerospace applications, such as rectifiers and high-voltage converters. As can be seen in Figure 14, each application uses a specific voltage range. In terms of device market, currently, the majority of GaN components are designed for 600/650V applications and below. However, there are few companies that offer devices for 900V applications.

Figure 14: Examples of applications using different voltage ranges

### 6.1 Lateral GaN device architectures

GaN-on-Si typical HEMT structures (Figure 15) consist of several epi-layers. These layers include materials with a wider bandgap and a lower bandgap, and an AlGaN/GaN heterostructure. At the interface between AlGaN and GaN, a two dimensional electron gas (2DEG) is created with an electron channel accumulation without extrinsic doping. The 2DEG formation results from both the spontaneous and piezoelectric effects [48], [54], [68]. The thickness and Al content of the AlGaN barrier layer defines the resulting polarization. It can be pointed out that a high electron mobility above 2000 cm²/Vs can be combined with a high carrier density within the 2DEG, thus resulting in excellent electrical performance.

Figure 15: Cross section of a typical AlGaN/GaN HEMT structure

One of the main issues for GaN-based heteroepitaxy is the lattice mismatch and difference in thermal expansion coefficients with the substrate. This generally leads to a high dislocation density, which may be a source of leakage current under high electric field and subsequent device degradation. Residual stress may be created, inducing eventually cracks. The most common materials used as substrates are silicon, sapphire, silicon carbide and more recently bulk GaN. In all cases, the epitaxial layers have rather high dislocation density ( $10^3 - 10^{10} \, \mathrm{cm}^{-2}$  [69], [70]). Some properties of the substrates typically used for GaN-based epitaxy are shown in Table 5. For power applications, the Si substrate is preferred because of its low cost and availability in large diameter (up to 12 inches), despite a 17% lattice mismatch and a strong difference in thermal expansion coefficient between GaN and Si, which makes the growth challenging. Although sapphire substrates combine a high resistivity and low cost, the low thermal conductivity leads to a significant self-heating, which is not suitable for power applications. Finally, the high cost of silicon carbide is prohibitive for large volume applications despite its outstanding properties.

Emerging GaN substrates, perfectly lattice-matched, are of interest for vertical GaN architectures, see also Section 7.

In order to grow crack-free and high quality GaN films by reducing the defect density, especially when using silicon substrates, the tensile stress during the growth and cooling process needs to be

limited. An AlN nucleation layer (NL) is typically used as an initiating layer for GaN growth. By using a AlN NL, the melt-back etching of Ga into Si can be avoided [71]. Besides, the AlN NL provides a GaN layer with a compressive strain due to the 2.5% lattice mismatch between AlN and GaN. This is necessary for compensating the tensile stress generated during the cooling process. Figure 16 shows a TEM image of the interface between the Si substrate and the AlN nucleation layer. Dislocations are reduced but still present across the buffer layers.

|          | Structure | Lattice     | Lattice     | Thermal      | Lattice  |

|----------|-----------|-------------|-------------|--------------|----------|

|          |           | constants a | constants c | conductivity | mismatch |

| Unit     |           | nm          | nm          | W/cm.K       | %        |

| Sapphire | Hexagonal | 0.476       | 1.2982      | 0.25         | 15       |

| 6H-SiC   | Hexagonal | 0.30806     | 1.51173     | 4.9          | 3.1      |

| Si       | Cubic     | 0.543102    |             | 1.56         | 17       |

Table 5: Properties of various substrates used for GaN epitaxy [72]

Figure 16: TEM image of a cross section of an AlN/Si interface. Reprinted from R. Liu et al., "Atomic arrangement at the AlN/Si (111) interface", Applied Physics Letters 83, 860-862 (2003) https://doi.org/10.1063/1.1597749, with the permission of AIP Publishing [73].

Whatever the choice of substrate, the buffer layers are critical. The high 2DEG sheet charge density in GaN-based HEMTs enables significant drain current densities. Inadequate carrier confinement within the channel leads to soft pinch-off characteristics and high sub-threshold leakage. The presence of a high defect or impurity density in the buffer produces high leakage currents and poor device reliability. Consequently, on top of a high quality AlN NL, a proper buffer configuration and material quality is mandatory.

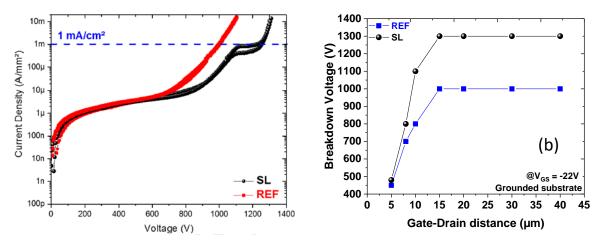

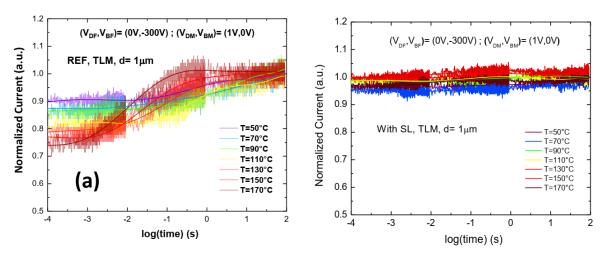

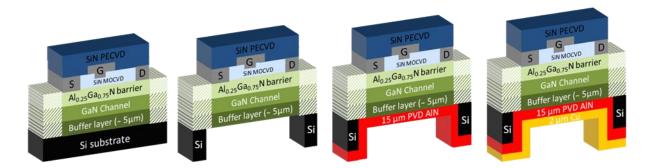

A well-known approach is the use of a step graded AlGaN buffer, as shown in Figure 17. Several micrometers thick Al<sub>x</sub>Ga<sub>1-x</sub>N buffer layers with various Al-content enable to further mitigate lattice and thermal-mismatch detrimental effects. The interest of this approach is also to improve the 2DEG electron confinement under high electric field, by limiting the carrier injection into the buffer layers, i.e. to the so-called punch-through effect. Another practical route to significantly increase the buffer layers' resistivity is the introduction of intentional compensating centers. Iron or carbon doping can be used to produce highly resistive buffers (carbon being the choice for GaN-on-Si GaN devices). Finally, super-lattice (SL) buffers consisting in many periods of thin AlN/GaN pairs have been proved to be one of the most effective techniques both to control the stress and enhance the blocking voltage [74]. With thick SL buffers, a high crystal quality and smooth surface of top-GaN layer can be obtained resulting in superior performance as described further in this paper.

Figure 17: Schematic cross section and TEM image of AlGaN layers with various Al content between the nucleation layer and the GaN layer. Reprinted from "AlGaN/GaN HFET grown on 6-inch diameter Si(111) substrates by MOCVD", S. M. Cho et al., https://doi.org/10.7567/SSDM.2011.AL-7-3, licensed under CC BY [75].

The epitaxial heterostructure is completed with a cap layer, which is generally composed of GaN or SiN to reduce the oxidation of the underlying AlGaN film. It is important to note that surface states [55] on top of the AlGaN constitute the origin of the 2DEG, as discussed in Section 5. However, surface defects may also be detrimental to the device performance. Under operating conditions, trapping at surface defects can create a virtual gate between gate and drain terminals, depleting unintentionally the 2DEG and thus severely degrading the device performances and/or reliability. Negatively charged surface states may compensate the donor atoms, thus depleting the channel between the gate and the drain. A surface passivation layer, typically SiN, allows to mitigate the 2DEG depletion as can be seen in Figure 18.

Figure 18: Schematic cross section showing surface state depletion effects within an AlGaN/GaN HEMT

Lateral heterostructure devices are inherently normally-on, i.e. they conduct current when no gate voltage is applied. This raises safety concerns because in case of a malfunctioning gate driver, the GaN transistor is not automatically switched off and an uncontrolled current flow can damage the entire system. Furthermore, normally-on transistors make circuit designs more complex because a negative-voltage supply is required. Thus, a substantial research effort was focused on creating normally-off devices in recent years.

### 6.2 Approaches for normally-off operation

In a conventional AlGaN/GaN HEMT, the threshold voltage  $V_{TH}$  depends on several parameters related to the gate metal and the heterojunction properties, as can be seen from the following equation [76]:

$$V_{TH}(x) = \phi_B(x) - \Delta E_C(x) - \frac{\sigma(x)}{\varepsilon_0 \varepsilon_{AlGaN}(x)} t - \frac{q N_D}{2 \varepsilon_0 \varepsilon_{AlGaN}(x)} (t)^2$$

x represents the Al content in the barrier layer;  $\phi_B(x)$  is the Schottky barrier height between the gate metal and the AlGaN barrier layer;  $\Delta E_C(x)$  is the conduction band discontinuity at the AlGaN/GaN interface;  $\sigma(x)$  is the polarization charge at the AlGaN/GaN interface;  $\varepsilon_0$  is the permittivity vacuum;  $\varepsilon_{AlGaN}(x)$  is the permittivity of the AlGaN layer; t is the AlGaN thickness; q is the electric charge;  $N_D$  is the doping.

Thicker AlGaN barriers and higher polarization differences between AlGaN and GaN lead to more negative  $V_{TH}$  as they increase  $n_s$  at zero bias. From this equation, it is clear that several degrees of freedom exist to tune the  $V_{TH}$ , such as changing the Schottky barrier height or the 2DEG carrier density related to the AlGaN barrier layer, which is dependent on the Al content and its thickness.

Different topologies have been proposed in order to achieve normally-off GaN HEMTs: a cascode configuration [77]–[79] combining a silicon normally-off MOSFET and a normally-on GaN HEMT, the use of a HEMT with fluorine implantation under the gate [80]–[82], a gate recessed MISHEMT (metal-insulator-semiconductor) with partial [83], [84] or complete [85] AlGaN barrier removal, and a p-GaN-gated [24], [86], [87] HEMT.

# **6.2.1** Cascode configuration

The cascode configuration uses a high voltage normally-on GaN HEMT connected in series with a low-voltage silicon MOSFET in the switching circuit, as can be seen in Figure 19. The silicon MOSFET controls the on and off-state switching of the GaN HEMT. When a positive gate voltage above the threshold voltage is applied to the MOSFET, the GaN HEMT gate voltage is close to zero and the device is turned on. As the two devices are connected in series, when a voltage is applied to the drain of the HEMT, the current will also flow through the MOSFET. On the other hand, when no gate voltage is applied to the MOSFET to turn it off, no current can flow through the channel of the HEMT. In addition, any increase of the drain voltage will be handled by the HEMT, thus resulting in a high reliability.

Figure 19: A cascode circuit showing the normally-on HEMT in series connection of a normally-off Si-MOSFET

Therefore, the cascode configuration enables to take advantage of the positive threshold voltage of the MOSFET as well as the low on-resistance of the 2DEG, together with the high breakdown field of the GaN HEMT in off-state conditions. However, it can be noticed that this approach limits the high temperature operation by the presence of the Si device. In addition, the packaging complexity and size are increased and parasitic inductances are introduced, and this may have an impact on the switching performance of the circuit.

# **6.2.2** Recessed gate MISHEMT

Another approach consists of etching the AlGaN barrier layer under the gate area followed by a deposition of a gate dielectric insulating layer. The AlGaN barrier layer is fully etched by plasma in the gate region (Figure 20). This allows for high threshold voltages, while the thick gate dielectric enables a large maximum forward gate bias (> +10 V).

Figure 20: Schematic cross section of a recessed gate GaN MISHEMT

The choice of the dielectric is extremely important, as it will directly impact the channel mobility within the 2DEG [88] and the stability of the threshold voltage [89]. Also, the dielectric quality and surface roughness of the etched area are critical parameters and the interface charge density needs to be well controlled. Several mechanisms, involving the surface states and related trapping

have been proposed to explain the possible origin of the device degradation phenomena (see Sections 8.2 and 8.3).

### 6.2.3 The "fluorine gate" HEMT

Fluorine ions implanted into the AlGaN layer self-aligned to the gate (see Figure 21) can also create a normally-off behaviour. The negative ions into the barrier change the surface potential, thus depleting the 2DEG. However, the V<sub>TH</sub> stability after annealing at high temperature and/or under high electric field is a source of concern for this approach [90], [91]. Moreover, previous studies have shown the relation between fluorine and current collapse [92], [93], which may be an issue for power switching applications [92], [94].

Figure 21: Schematic cross section of a F-doped GaN HEMT.

#### 6.2.4 P-GaN Gate

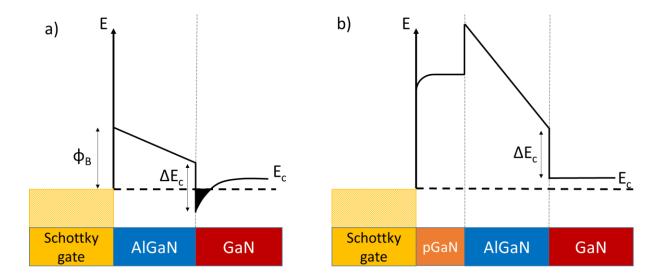

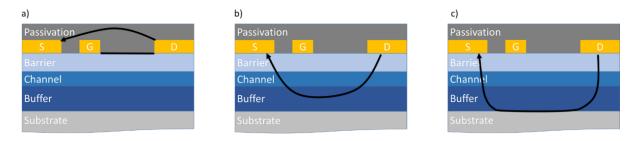

An attractive method to achieve normally-off GaN transistors is the use of a p-doped GaN layer [95] under the gate area (Figure 22). The presence of the p-GaN layer lifts the band diagram to higher energies (Figure 23), so that the 2DEG depletion occurs even in the absence of an applied external bias. In order to maximize the 2DEG depletion induced by the p-GaN cap layer, the Al mole fraction in the barrier and the thickness of the barrier must be carefully optimized. It has been demonstrated that to achieve a good depletion of the 2DEG, the Al content and thickness of the barrier should be kept relatively low [96]. Greco *et al* determined the energy band diagram by

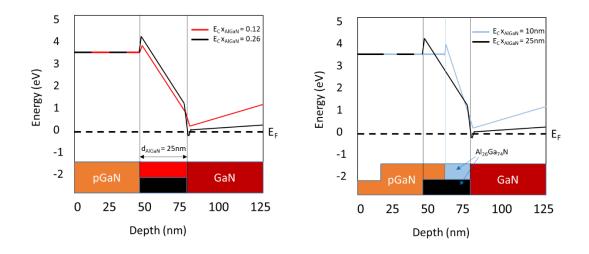

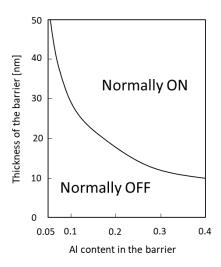

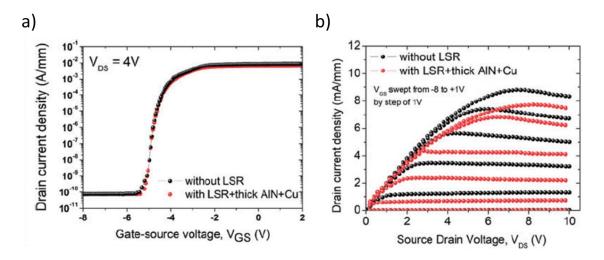

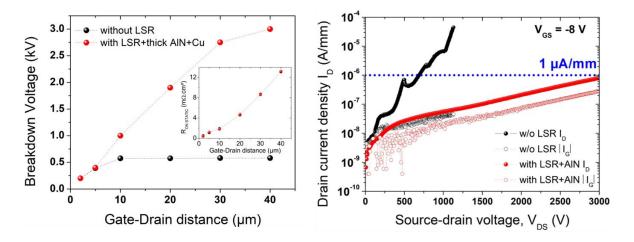

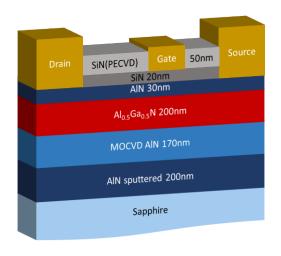

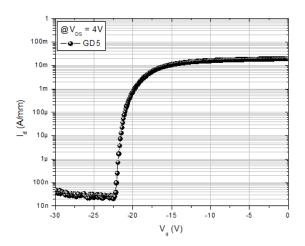

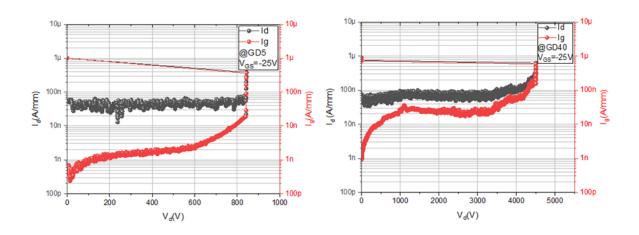

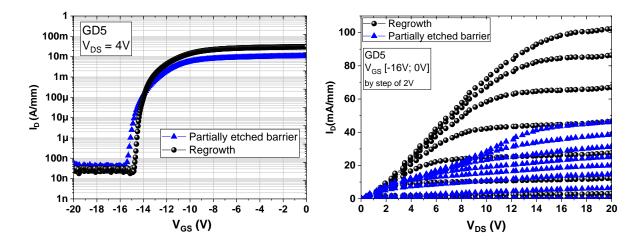

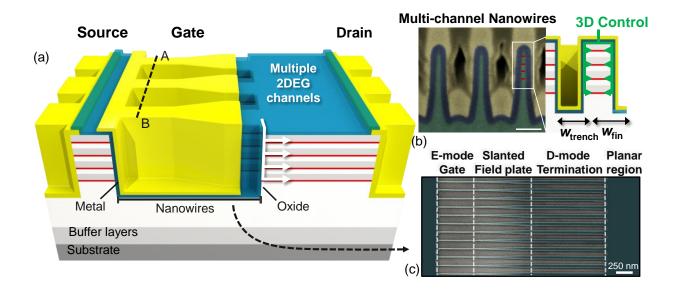

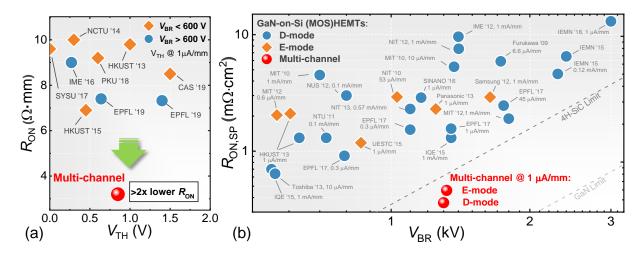

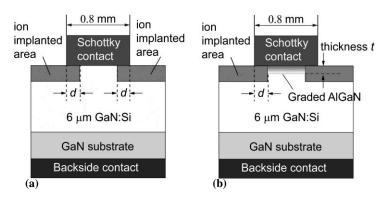

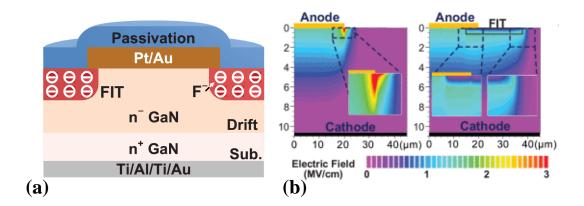

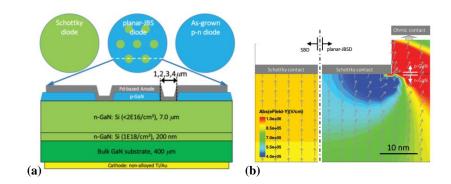

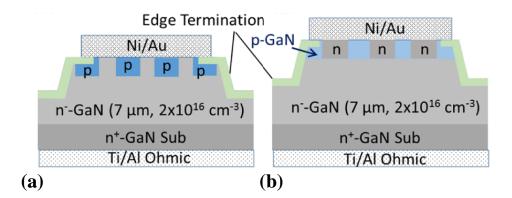

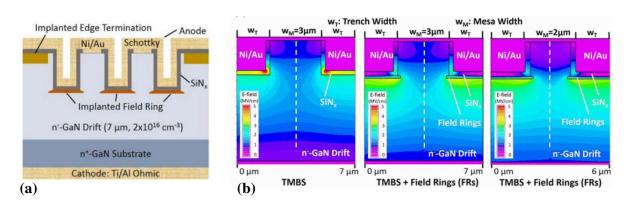

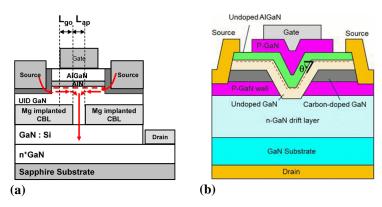

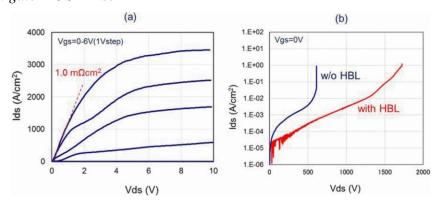

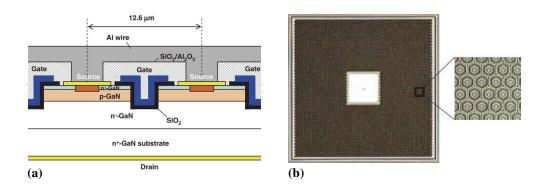

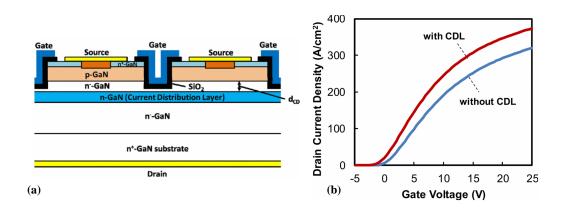

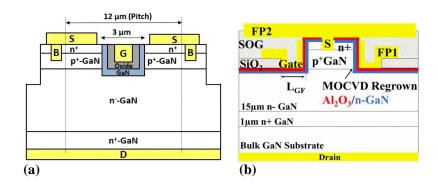

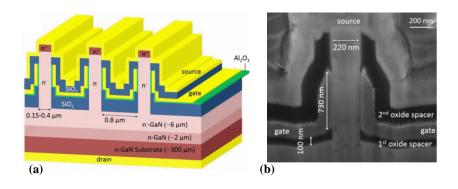

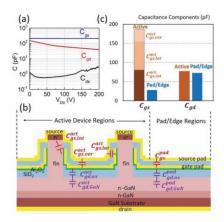

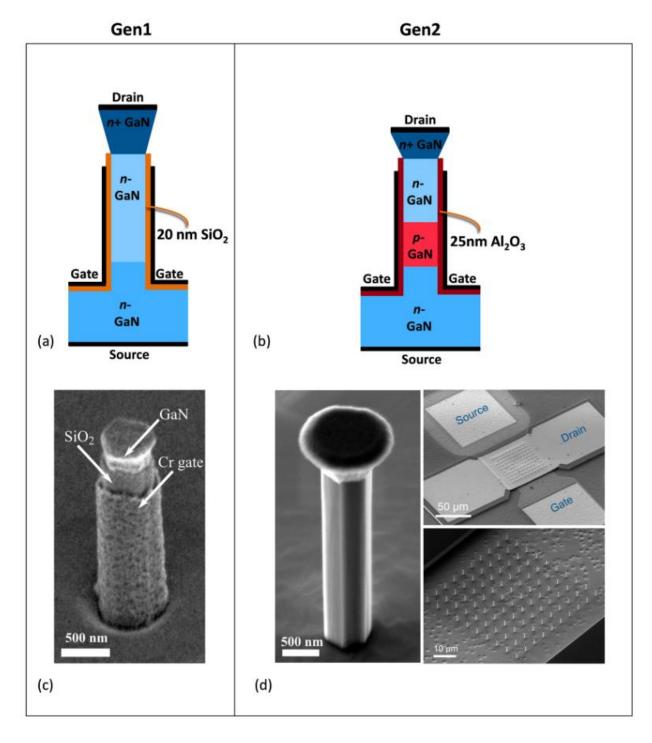

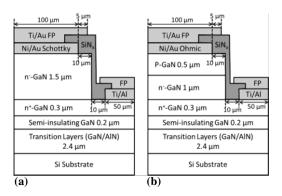

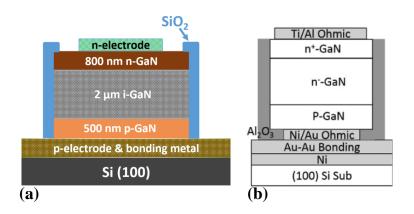

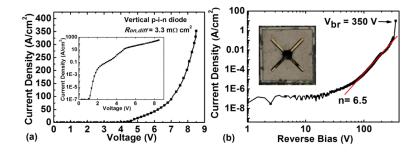

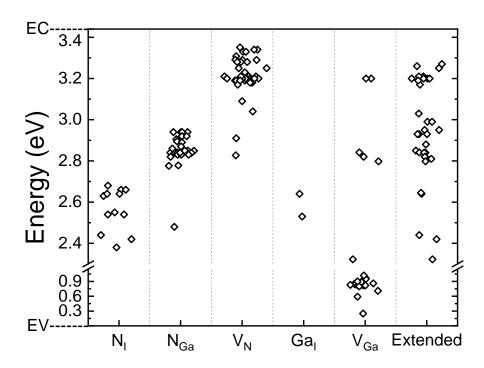

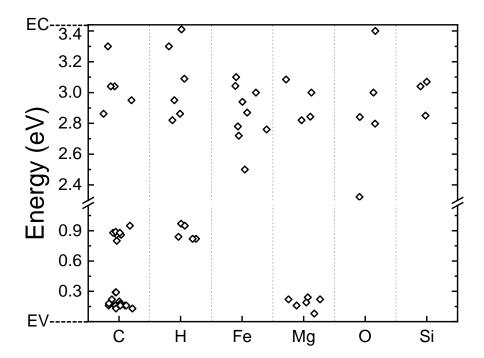

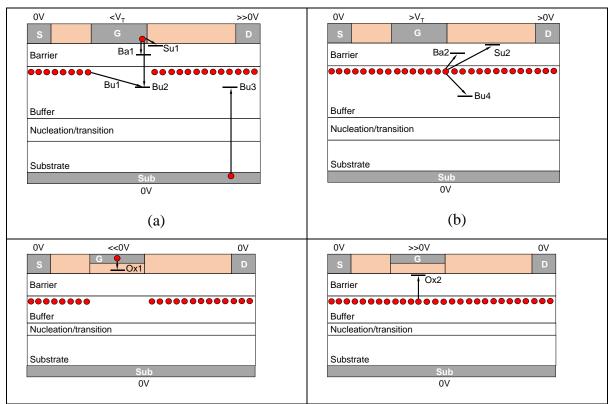

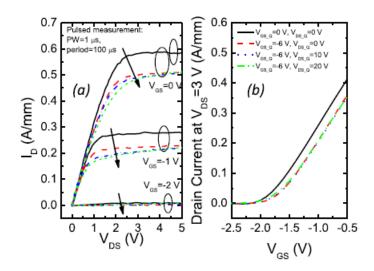

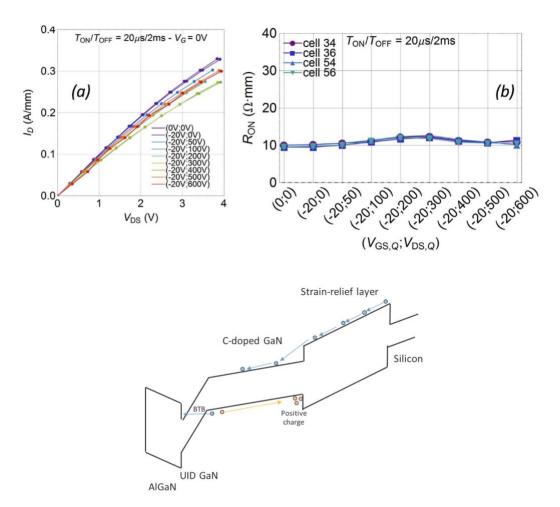

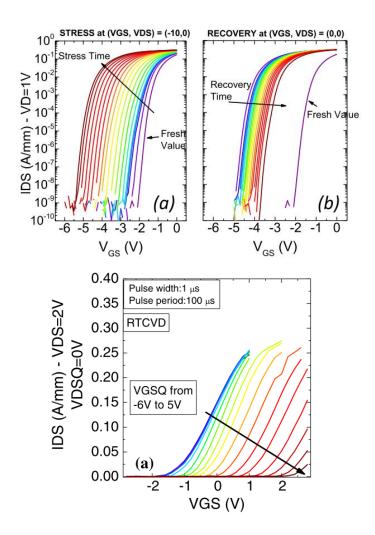

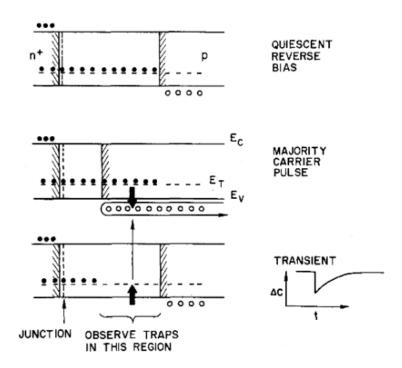

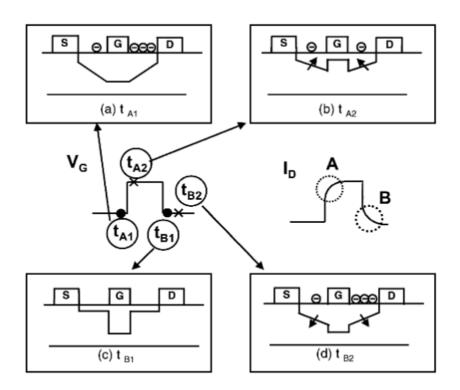

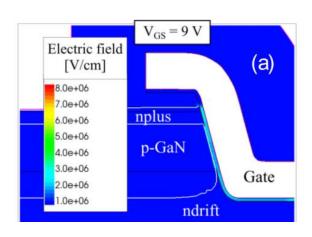

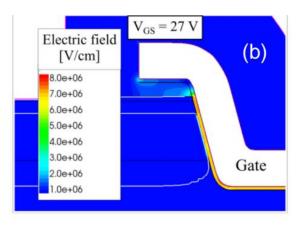

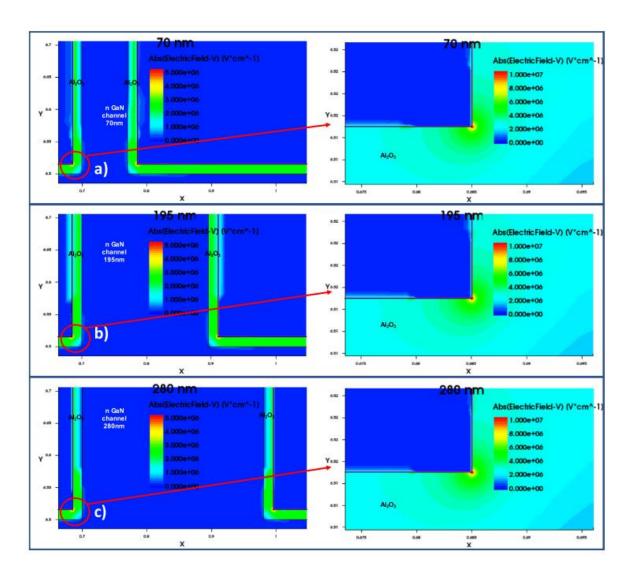

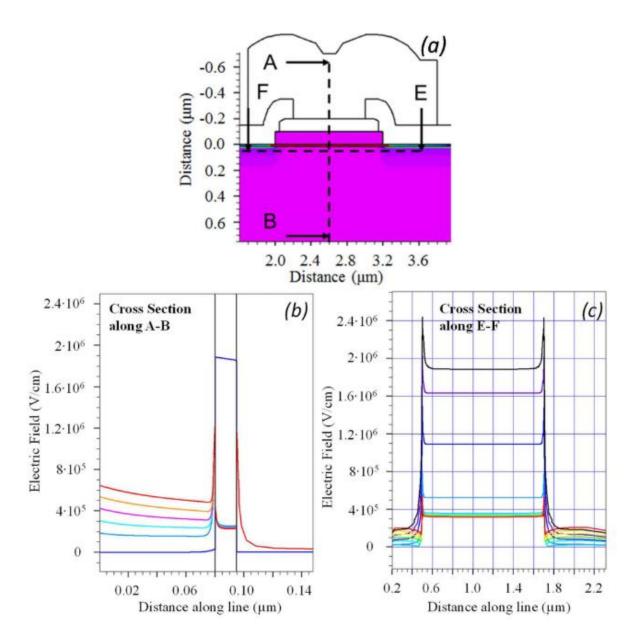

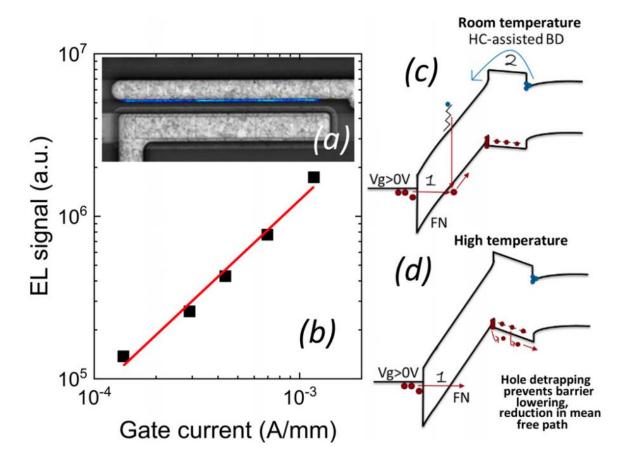

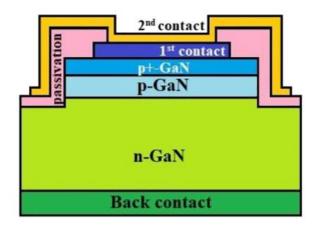

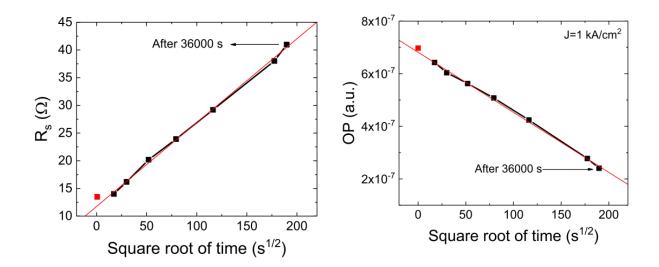

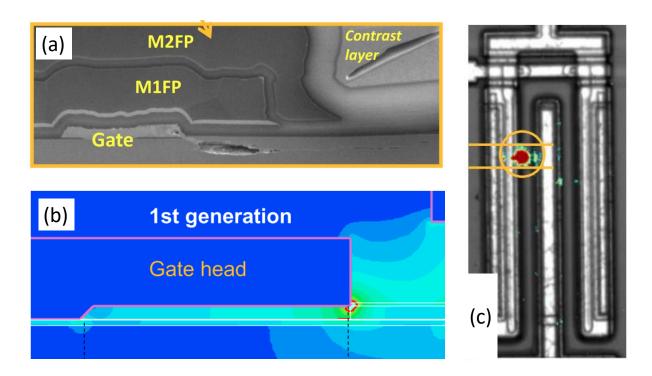

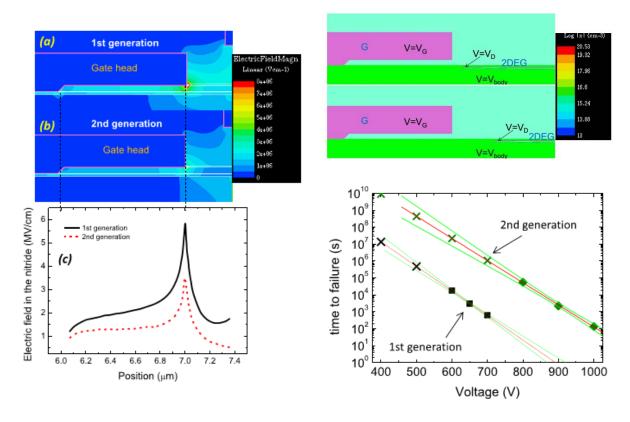

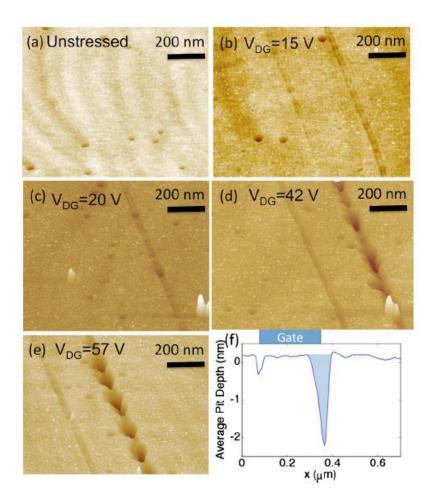

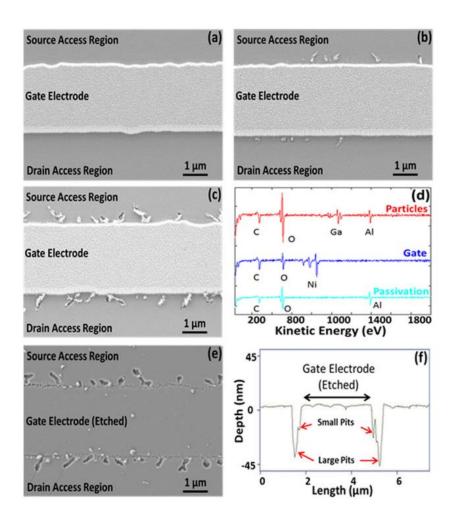

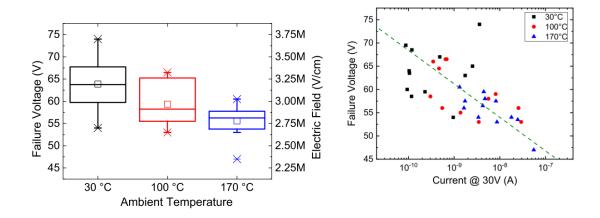

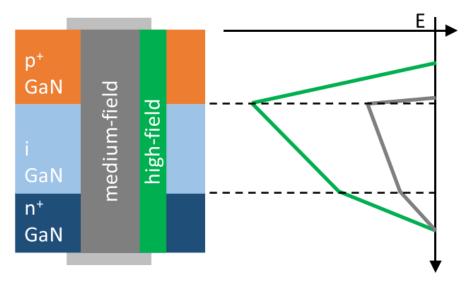

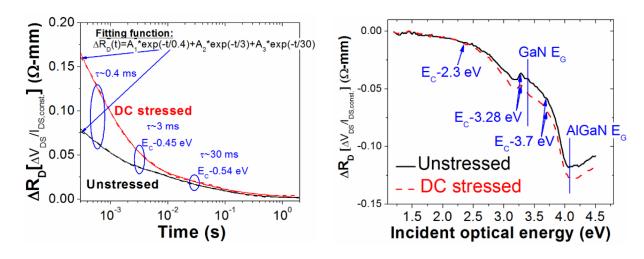

Schrödinger-Poisson (Figure 24) of two structures with an identical barrier thicknesses (25nm) but different Al content (12% and 26%), by using a p-GaN layer thickness of 50 nm with an acceptor concentration of 3×10<sup>19</sup>cm<sup>-3</sup>. Figure 24 clearly shows that despite the presence of the p-GaN layer, the high Al content structure still exhibits normally-on behaviour with the conduction band below the Fermi level at the AlGaN/GaN interface; on the contrary, the structure with reduced Al content can reach normally-off operation. Similarly, the conduction band diagram of p-GaN/AlGaN/GaN heterojunctions with two different barrier thicknesses (10 nm and 25 nm, with a fixed Al content of 26 %) has been simulated. As can be noticed, the structure with a thickness of 25 nm reveals a normally-on behavior, whereas the thinner barrier results in normally-off devices. Based on a series of tests, a summary graph can be produced showing the normally-on and normally-off area with respect to the thickness and Al content of the AlGaN barrier layer (Figure 25).