## Experimental observation and modeling of the impact of traps on static and analog/HF performance of graphene transistors

Anibal Pacheco-Sanchez, Nikolaos Mavredakis, Pedro C. Feijoo, Wei Wei, Emiliano Pallecchi, Henri Happy, David Jimenez

### ▶ To cite this version:

Anibal Pacheco-Sanchez, Nikolaos Mavredakis, Pedro C. Feijoo, Wei Wei, Emiliano Pallecchi, et al.. Experimental observation and modeling of the impact of traps on static and analog/HF performance of graphene transistors. IEEE Transactions on Electron Devices, 2020, 67 (12), pp.5790-5796. 10.1109/TED.2020.3029542 . hal-03321544

## HAL Id: hal-03321544 https://hal.science/hal-03321544

Submitted on 15 Jul2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Experimental observation and modeling of the impact of traps on static and analog/HF performance of graphene transistors

Anibal Pacheco-Sanchez, Nikolaos Mavredakis, Pedro C. Feijoo, Wei Wei, Emiliano Pallecchi, Henri Happy, David Jiménez

#### Abstract

The trap-induced hysteresis on the performance of a graphene field-effect transistor is experimentally diminished here by applying consecutive gate-to-source voltage pulses of opposing polarity. This measurement scheme is a practical and suitable approach to obtain reproducible device characteristics. Trap-affected and trap-reduced experimental data enable a discussion regarding the impact of traps on static and dynamic device performance. An analytical drain current model calibrated with the experimental data enables the study of the traps effects on the channel potential within the device. High-frequency figures of merit and the intrinsic gain of the device obtained from both experimental and synthetic data with and without hysteresis show the importance of considering the generally overlooked impact of traps for analog and high-frequency applications.

#### **Index Terms**

GFET, traps, hysteresis, opposing pulses, channel potential, analytical model, high-frequency performance.

#### I. INTRODUCTION

Reproducible graphene field-effect transistor (GFETs) characteristics are required in order to boost the use of circuits based on this emerging technology, specially on the low-power high-frequency (HF) applications scenario where its extraordinary intrinsic characteristics, e.g., high carrier mobility, can be exploited [1]. In GFETs, traps within the channel, substrate and high- $\kappa$  oxide materials, as well as at the interfaces between them, are one of the major issues affecting the device performance, i.e., in order to obtain hysteresis-free reproducible characteristics, the impact of traps should be diminished [2], [3]. Technological efforts towards reducing the presence of traps in graphene-based technologies have shown a discrete success on individual devices [3]-[5]. For wafer-scale integration however, defect-induced traps within the channel associated to the graphene transfer process, as well as oxide traps, still affect the device behavior [6], [7]. The characterization of traps in GFETs is therefore required at this stage of the technology in order to enhance device and circuit reproducibility by finding the adequate bias conditions to diminish their impact on the overall device performance.

Trap mechanisms within GFET architectures have been experimentally characterized by observing the electrical device characteristics obtained with time-dependent-voltage pulses [2]-[5], [8]-[12]. Different time constants related to trapping and detrapping processes have been identified for different graphene technologies ranging over a large span of time, depending on the location of the traps (bulk, oxide, channel, interfaces) [2], [8]-[11]. In most of the GFETs trap studies, the drain-to-source voltage  $V_{\rm DS}$  signal has been varied over time while keeping the gate-to-source  $V_{\rm GS}$  constant [3], [5], [8], [11], [12] i.e.,  $V_{\rm DS}$ -induced hysteresis has been the main focus of such investigations rather than the trap impact on the device performance due to vertical fields applied to the channel. The latter effect has been studied for a global-back-gate device with SiO<sub>2</sub> dielectric [10] and for top-gate devices with high- $\kappa$  gate oxides [2] in order to obtain the trapping time constants of such specific technologies.

The impact of traps on analog/HF performance of GFETs has been rarely discussed. Some trapping processes can be too slow in comparison to the targeted operation frequency ( $\sim$ GHz), i.e., their impact is generally neglected based on this assumption [9]. However, the DC bias point, required to activate the transistor for its dynamic operation, is still affected by traps, i.e., the drift of this point due to traps can induce reproducibility issues in GFET-based HF applications, as demonstrated for other emerging transistor technologies [13], [14]. HF figures of merit (FoM) have been reported for GFETs measured under pulsed bias conditions [3], [15], however, no trap-affected data have been shown in order to understand the difference in the dynamic performance with and without hysteresis. As an alternative to overcome the challenging measurement setup required for pulsed HF characterization [3], [13], the HF FoM of GFETs can be measured by considering a non-quiescent holding time large enough for the traps to be inactive [16]-[18]. The latter is a useful approach to understand the internal device mechanisms after removing the impact of traps. However, such holding time for trap-reduced characterization varies between technologies and depends on the measurement history [2], [8]-[11]. Furthermore, in a practical HF scenario, GFET-based circuits should

A. Pacheco-Sanchez, N. Mavredakis, P. C. Feijoo and D. Jiménez are with the Departament d'Enginyeria Electrònica, Escola d'Enginyeria, Universitat Autònoma de Barcelona, Bellaterra 08193, Spain (e-mails: AnibalUriel.Pacheco@uab.cat, Nikolaos.Mavredakis@uab.cat).

W. Wei, E. Pallecchi and H. Happy are with CNRS, UMR 8520-IEMN, University of Lille, 59000 Lille, France.

© 2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This work has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreements No GrapheneCore2 785219 and No GrapheneCore3 881603, from Ministerio de Ciencia, Innovación y Universidades under grant agreement RTI2018-097876-B-C21(MCIU/AEI/FEDER, UE). This article has been partially funded by the European Regional Development Funds (ERDF) allocated to the Programa Operatiu FEDER de Catalunya 2014-2020, with the support of the Secretaria d'Universitats i Recerca of the Departament d'Empresa i Coneixement of the Generalitat de Catalunya for emerging technology clusters to carry out valorization and transfer of research results. Reference of the GraphCAT project: 001-P-001702.

work under rapid pulsed biasing schemes rather than on a holding time-based scheme in order to compete with incumbent technologies, e.g., in applications involving high-data rate communications with different pulse-based modulation schemes [19], [20]. Hence, an alternative practical biasing method to achieve trap-reduced GFET performance for its use in HF applications is required.

The aims of this work are to show experimentally the impact of traps on the GFET static and dynamic performance and to provide a straightforward model of trap-related effects. For the first goal, the trap-affected and trap-reduced performance of a buried-gate GFET technology are characterized with a standard  $V_{GS}$ -staircase sweep and with an opposing-pulse sweep of  $V_{GS}$ , respectively. The opposing-pulse sweep allows to determine the impact of traps on transistor performance indicators and it is a practical measurement approach to obtain reproducible characteristics. In second place, this paper successfully describes the impact of traps on the net charge within the device via an analytical compact model. Typical models only consider traps activated by vertical electrical fields caused by the gate voltage stress, but our model also include traps activated by hot-carriers, which result in a  $V_{DS}$ -dependence of trapped charge. Our compact model thus allows calculation of traps densities and enables the study of GFET-based circuits considering devices affected by traps at different bias points. This work projects the dynamic performance via HF/analog FoM, including cutoff frequency, maximum oscillation frequency and intrinsic gain. Additionally, it provides an insight on the generally neglected fact that traps affect not only the static device performance but also the dynamic response at different bias.

#### II. DEVICE DESCRIPTION AND MEASUREMENT TECHNIQUES

A two-finger aluminium back-gated GFET fabricated on a SiO<sub>2</sub> (300 nm)/Si (high resistivity silicon substrate) has been characterized in this study. The device gate width  $w_g$  and gate length are  $12 \times 2 \mu m$  and 300 nm, respectively (the transistor is a dual gate of 12 microns each). The single graphene layer has been grown via chemical vapor deposition in a host substrate (a copper foil) and transferred on the top of previously patterned bottom Al gate fingers via a wet chemical transfer technique. The natural oxidation of the Al back-gate has been obtained prior the transfer of monolayer of graphene. A ~4 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layer (ellipsometry measurement) is then obtained which separates graphene and gate. The Ni/Au source and drain contacts are separated by a distance of 1  $\mu m$ . The gate is located at the same distance from source and drain contacts. More details on the graphene transfer process and on the device fabrication process as well as the device layout have been discussed elsewhere [21].

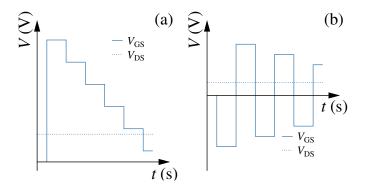

Two different measurement techniques have been used for the experimental device characterization: staircase voltage sweep and opposing voltage sweep. Fig. 1(a) shows a sketch of the  $V_{GS}$  and  $V_{DS}$  for the staircase sweep characterization. This standard characterization scheme usually acquires the current data at the end of the pulse where a steady-state current is expected. This steady-state in graphene devices however, depends on the technology and measurement history as elucidated by the wide span of trap-time constants reported in different studies (from ns to s) [2], [5], [8]-[12], [18].

Fig. 1. Sketch of the applied voltage signals over time for (a) staircase sweep and (b) opposing pulses sweep measurements.

The opposing sweep technique sketched in Fig. 1(b) diminishes the trap-effects since the measurement history is compensated by the consecutive opposite bias pulses, i.e., in time-symmetric trapping and detrapping processes, the effects related to remaining carriers trapped at the end of a positive or negative  $V_{\rm GS}$  pulse, if any, are counterbalanced by trapped carriers at the consecutive pulse of similar magnitude but opposite bias. This reversible trapping effects technique has been previously reported for devices with high- $\kappa$  oxides [13], [22]-[24] but not exploited before for GFETs. Furthermore, this bias scheme is less challenging to implement in contrast to a pulsed characterization technique and more practical in circuit applications than a holding-time bias approach, e.g., in modulators required for high-data rate communications [19], [20].

Measurements with both techniques described above have been performed with a K4200 semiconductor characterization system by applying consecutive forward and backward  $V_{GS}$ -sweeps at room temperature.  $V_{DS}$  has been kept constant. The duration of the applied  $V_{GS}$  signal is of ~0.9 s which is large enough to consider trapping processes to be active according to time constants in the same range obtained for GFETs [10], [11]. This is confirmed by the hysteresis observed in the experimental section. Self-heating effects are expected to be much faster [11], [12] than the trapping processes characterized with this pulse width. Notice that in contrast to other studies [3], [5], [8], [11], [12], the gate oxide traps are directly affected by transitions of the applied vertical fields here.

#### **III. EXPERIMENTAL INVESTIGATION**

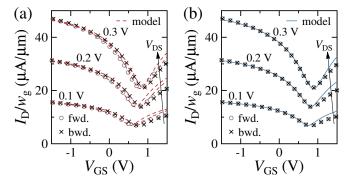

The channel potential of the device can be modified by interface or oxide traps capturing or releasing carriers since these processes reduce the gate control, i.e., traps shield the channel potential from the applied voltage [25]. These trap effects have a different impact on the device performance depending on the measurement technique. The transfer characteristics of the device obtained via consecutive forward-backward sweeps with the staircase and opposing measurement techniques are shown in Fig. 2. The typical ambipolar behavior of GFETs, separated by a charged neutrality voltage point identified as the Dirac voltage  $V_{\text{Dirac}} = V_{\text{GS}}|_{\min(I_{\text{D}})}$ , can be observed.

Fig. 2. Transfer characteristics of the 300 nm-long GFET with (a) stair-case sweep and (b) opposing pulse sweep characterization. Markers are experimental data and lines represent modeling results.

The hysteresis in the experimental characteristics measured with forward and backward sweeps using the staircase technique (Fig. 2(a)) is induced by trapping processes started during the forward sweep and continued during the change of sweep direction. This leads to lower  $I_D$  and higher  $V_{Dirac}$  in the backward sweep compared to the forward sweep at  $V_{GS} > V_{Dirac}$ . The release of trapped carriers at  $V_{GS} < V_{Dirac}$  during the backward sweep affects positively the channel potential [8], i.e., higher  $I_D$  is observed in contrast to the acquired during the former sweep. The reduced hysteresis observed at more negative  $V_{GS}$  can be associated to the device reaching a steady-like-state.

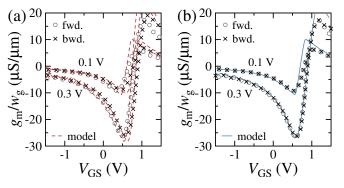

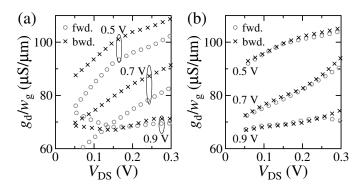

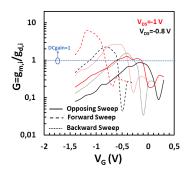

The almost negligible hysteresis observed in the transfer characteristic measured with the opposing pulse technique, as observed in Fig. 2(b), can be explained by trapping and detrapping processes with quasi-symmetrical time constants and by the compensating effect due to opposing polarity pulses as mentioned in Section II. The transconductance ( $g_m = \partial I_D / \partial V_{GS}$ ) and output conductance ( $g_d = \partial I_D / \partial V_{DS}$ ) plots in Figs. 3 and 4, make the hysteresis in the staircase sweeps more evident. The slight observed hysteresis in the opposing sweep data at high  $V_{DS}$  can be related to hot carriers-induced [2] asymmetric trapping processes which can not be counterbalanced with this technique.

Fig. 3. Transconductance versus  $V_{\rm GS}$  at different  $V_{\rm DS}$  of a 300 nm-long GFET with (a) stair-case sweep and (b) opposing pulse sweep characterization. Markers are experimental data and lines represent modeling results.

Transistor performance indicators oftenly used to project the device HF performance are the maximum point of the transconductance  $g_{m,max}$  and a low value of  $g_d$ . Due to traps, however, the bias-point and the magnitude of each of these parameters differ in each measurement run. E.g., by analyzing the sweeps with the staircase technique,  $|g_{m,max}|$  is found at different  $V_{GS}$  and its magnitude differ in comparison to the same metric obtained with both sweeps using the opposing pulse technique. Furthermore, a  $|g_{m,max}|$  equal to  $634 \,\mu\text{S}$  at the highest  $V_{DS}$  obtained with trap-affected data is ~21  $\mu\text{S}$  lower than the same metric observed at the same  $V_{DS}$  with trap-reduced data. A large difference between trap-affected and trap-reduced data is observed for the output conductance (Fig. 4). In addition to the distinct values obtained in each case, the bias dependence of trap-affected data is notoriously different between different sweeps. Variations in the operating bias point and magnitude of  $g_m$  and  $g_d$  can mislead the expected analog/HF performance projections based on this parameter such as the maximum oscillation frequency.

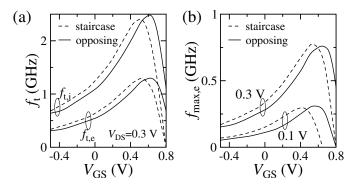

In order to explicitly show the impact of traps on analog/HF FoMs, the intrinsic/extrinsic cutoff frequency  $f_{t,i/e}$  and the extrinsic maximum oscillation frequency  $f_{max,e}$  have been estimated from the trap-affected and trap-reduced data of the

Fig. 4. Output conductance versus  $V_{\rm DS}$  at different  $V_{\rm GS}$  of a 300 nm-long GFET with (a) stair-case sweep and (b) opposing pulse sweep characterization.

device by an approximation based on a small-signal model of GFETs [1], [27], [28]. An average gate capacitance of  $42 \,\mathrm{fF}$  obtained elsewhere [21] for the device used here has been considered. An effective physical gate resistance [26] of  $4.9 \,\Omega$  has been calculated. A contact resistance value (see Table I), required for the intrinsic transconductance and intrinsic output conductance, has been extracted from the experimental data with a method presented elsewhere [27]. The obtained HF FoM have been shown in Fig. 5 for the forward sweep of each technique.

Fig. 5. Trap-affected (staircase sweep) and trap-reduced (opposing sweep) calculated (a) intrinsic and extrinsic cutoff frequency and (b) extrinsic maximum oscillation frequency versus  $V_{\rm GS}$  of the device under study.

The magnitude and bias-dependence of the HF FoMs differ due to traps affecting differently the channel potential. The trap-induced bias drift and the value of  $f_{t,e}$  and  $f_{max,e}$  can affect critically GFET-based HF circuits performance, e.g., by misleading the design for a specific bias point of matching or stability networks connecting the device with other stages of a monolithic circuit [29].

Other transistor performance indicators obtained with the different characterization techniques are shown in Table I at the highest  $V_{\rm DS}$  used here. For comparison purposes,  $V_{\rm Dirac}$  has been taken as a reference point, i.e.,  $I_{\rm D,p/n} = I_{\rm D}|_{V_{\rm GS}=V_{\rm Dirac}\mp 0.5 \text{ V}}$ , where the subindexes p and n indicate that the data is taken at the p-type ( $V_{\rm GS} < V_{\rm Dirac}$ ) or n-type ( $V_{\rm GS} > V_{\rm Dirac}$ ) part of the transfer curve. The contact resistance  $R_{\rm C}$  has been extracted [27] at the corresponding linear unipolar region of the transistor operation.

TABLE I TRANSISTOR PERFORMANCE INDICATORS AT  $V_{\rm DS}=0.3\,{\rm V}$  of the 300 nm GFET using different characterization techniques

|                                                                                    | staircase |          | opposing |          |

|------------------------------------------------------------------------------------|-----------|----------|----------|----------|

| param.                                                                             | forward   | backward | forward  | backward |

| param.                                                                             | sweep     | sweep    | sweep    | sweep    |

| $V_{\rm Dirac}$ (V)                                                                | 0.8       | 0.9      | 0.9      | 0.9      |

| $I_{\rm D,p}/w_{\rm g}~(\mu {\rm A}/\mu {\rm m})$                                  | 31.45     | 31.41    | 29.04    | 29.25    |

| $R_{\rm C,p} \cdot w_{\rm g} ~({\rm k}\Omega \cdot \mu{\rm m})$                    | 6.61      | 7.57     | 6.97     | 6.71     |

| $I_{\rm D,n}/w_{\rm g}~(\mu {\rm A}/\mu {\rm m})$                                  | 28.28     | 29       | 28.53    | 28.36    |

| $R_{\mathrm{C,n}} \cdot w_{\mathrm{g}} \; (\mathrm{k}\Omega \cdot \mathrm{\mu m})$ | 12.35     | 13.89    | 13.5     | 13.1     |

The shielding of the channel potential due to traps leads to an offset in  $V_{\text{GS}}$ , i.e., the same current level is obtained at different applied vertical fields in staircase sweeps. Trap-reduced data enables the reproducibility of these carrier current levels despite the measurement history. Larger differences in the contact resistivity from trap-affected data in comparison to the same parameter obtained with opposing pulses are due to the consideration of a bias range rather than a bias point related to the  $R_{\text{C}}$ -extraction method [27], i.e., hysteresis in this value is scaled up. A wrong estimation of this parameter could mislead the technology development.

#### IV. MODELING-ENABLED ANALOG PERFORMANCE ASSESSMENT

The need for an analytical current-voltage (IV) model that will accurately predict the behavior of both trap-reduced and trap-affected data is crucial for better comprehending these phenomena. Such a model is proposed in this section based on the one derived in [30] and on the experimental empirical observations presented above. The basic electrostatic equation of a one-gated graphene transistor without the impact of traps leads to an expression for the net charge in graphene given by [30], [31]

$$Q_{\rm net}(x) = C_{\rm ox} \left( V_{\rm GS} - V_{\rm GSO} - V_{\rm c}(x) - V_{\rm ch}(x) \right),\tag{1}$$

where  $V_{\rm c}$  and  $V_{\rm ch}$  are the chemical and the channel potential at channel position x, respectively. The chemical potential accounts for the voltage drop across the quantum capacitance along the channel.  $V_{\rm GS} - V_{\rm GSO}$  is the gate voltage overdrive with  $V_{\rm GSO}$ used as a model parameter and  $C_{\rm ox}$  is the oxide capacitance per unit area. By considering a straightforward approach [30] in which  $Q_{\rm net}$  approaches to 0 at the charge neutrality point and the channel potential is averaged over the channel such as  $V_{\rm ch} \sim V_{\rm DS}/2$ , the Dirac voltage is calculated here as  $V_{\rm Dirac} \approx V_{\rm GSO} + V_{\rm DS}/2$  [30].

At the presence of traps, Eq. (1) is modified as

$$Q_{\rm net,tr}(x) = C_{\rm ox} \left( V_{\rm GS} - V_{\rm GSO,tr} - V_{\rm c}(x) - V_{\rm ch}(x) \right), \tag{2}$$

with  $V_{\rm GSO,tr} = V_{\rm GSO} - DV_{\rm tr} + K_{\rm tr}V_{\rm DS}/2$ . The term  $DV_{\rm tr} - K_{\rm tr}V_{\rm DS}/2$  corresponds to the induced potential due to trap density<sup>1</sup>  $N_{\rm tr} = C_{\rm ox}(DV_{\rm tr} - K_{\rm tr}V_{\rm DS}/2)/q$  with q as the electron charge.  $DV_{\rm tr}$  and  $K_{\rm tr}$  are the new defined model parameters where the first corresponds to the shift of  $V_{\rm Dirac}$  due to trap impact while the latter embraces the  $V_{\rm DS}$  dependence of this shift. Trap-affected  $V_{\rm Dirac}$  is now calculated as  $V_{\rm Dirac,tr} = V_{\rm GSO} - DV_{\rm tr} + (K_{\rm tr} + 1)V_{\rm DS}/2$ . In order to incorporate the above effects in the  $I_{\rm D}$  model,  $V_{\rm GSO,tr}$  is used instead of  $V_{\rm GSO}$  in Eqs. (1) and (4) of [30] for the potential calculation. In contrast to other compact GFET model including the impact of traps [32], a straightforward implementation of the  $V_{\rm DS}$ -dependence of a trap-affected Dirac voltage related to hot carriers [2], [33] has been considered here. The latter is an attractive feature to describe the impact of traps in GFET-based circuits at different bias.

The model accurately captures experimental  $I_{\rm D}$  and  $g_{\rm m}$  data as illustrated in Figs. 2 and 3 for all available sweeps in the p-type region. The asymmetric experimental n-type behavior with respect to the p-type region is not described by the model due to an inherent symmetric condition as discussed elsewhere [17]. In the following, the discussion is for the transistor operating in the p-type region. The extracted model parameters are shown in Table II where  $\mu$  is the mobility,  $\rho_0$  the residual charge density and  $\hbar\Omega$  the phonon energy. The impact of the traps mostly contributes to the shift of the  $V_{\rm Dirac}$  through  $DV_{\rm tr}$  and  $K_{\rm tr}$  parameters which is more intense at the forward sweep while the rest of the model parameters are the same for both trap-reduced and trap-affected data. Having both data sets available, permits a reliable parameter extraction procedure. In more detail, from the opposing sweep all the model parameters apart from  $\hbar\Omega$  can be extracted from low  $V_{\rm DS}$  regime while the precise fitting of the data at high  $V_{\rm DS}$  by just adjusting  $\hbar\Omega$  is a good indicator that impact of the traps is negligible; in such case  $DV_{\rm tr}$  and  $K_{\rm tr}$  are deactivated. The latter are extracted afterwards in forward and backward sweeps.

TABLE II

MODEL PARAMETERS FOR DIFFERENT MEASUREMENT SWEEPS

| forward              | backward                                                                       | opposing                                                                                                                                      |

|----------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 135                  | 135                                                                            | 135                                                                                                                                           |

| 0.68                 | 0.68                                                                           | 0.68                                                                                                                                          |

| $1.55 	imes 10^{12}$ | $1.55 	imes 10^{12}$                                                           | $1.55 	imes 10^{12}$                                                                                                                          |

| 116                  | 116                                                                            | 116                                                                                                                                           |

| 10                   | 10                                                                             | 10                                                                                                                                            |

| 250                  | 70                                                                             | 0                                                                                                                                             |

| 1.05                 | 0.5                                                                            | 0                                                                                                                                             |

|                      | $\begin{array}{c} 135\\ 0.68\\ 1.55\times 10^{12}\\ 116\\ 10\\ 250\end{array}$ | $\begin{array}{c cccc} 135 & 135 \\ 0.68 & 0.68 \\ 1.55 \times 10^{12} & 1.55 \times 10^{12} \\ 116 & 116 \\ 10 & 10 \\ 250 & 70 \end{array}$ |

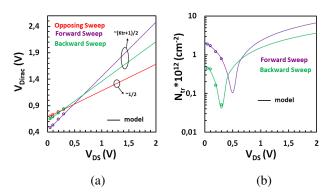

Fig. 6(a) depicts both experimental and simulated  $V_{\text{Dirac}}$  for trap-reduced and trap-affected cases versus  $V_{\text{DS}}$ . The model is extended to higher  $V_{\text{DS}}$  values where after a point,  $V_{\text{Dirac}}$  of forward and backward sweeps become larger than the one of opposing case. This can be justified in terms of the different  $V_{\text{DS}}$  dependence of trap-reduced and trap-affected channel potential. When traps are present, this dependence is  $(K_{\text{tr}} + 1)V_{\text{DS}}/2$  instead of  $V_{\text{DS}}/2$  in the case they are not there, as shown before. Experimental trap density is calculated as  $N_{\text{tr}} = \Delta V_{\text{Dirac}}C_{\text{ox}}/q$  where  $\Delta V_{\text{Dirac}}$  is the shift of the measured  $V_{\text{Dirac}}$  such as  $\Delta V_{\text{Dirac}} = V_{\text{Dirac-fwd/bwd}}$ , respectively while  $N_{\text{tr}}$  can be also calculated by the model as mentioned previously. Both are illustrated in Fig. 6(b) versus  $V_{\text{DS}}$  where the trapping and detrapping processes can be elucidated for voltages lower and higher than the minimum point of the curve, respectively. The minimum point of the  $N_{\text{tr}}(V_{\text{DS}})$  plot corresponds to a change of polarity of the term  $DV_{\text{tr}} - K_{\text{tr}}V_{\text{DS}}/2$ .

The model results in Fig. 6 confirm the increasing impact of traps with  $V_{\rm DS}$  on device performance ellucidated by experimental data, specially on  $g_{\rm d}$  (see Fig. 4). Trapping and detrapping processes can be simultaneously enabled at the same  $V_{\rm DS}$ , e.g., at 0.4 V, where traps are still being filled during a forward  $V_{\rm GS}$  sweep while in the backward sweep other traps can either start to release carriers or been enhanced by hot carriers [2], [33] as suggested by the increase of the modeled  $N_{\rm tr}$  at this bias point. An accurate calculation and projection over bias of  $N_{\rm tr}$  such as the one provided by this model (cf. Fig. 6(b)), is an important information towards improved insights in the device physics, e.g., on the low-frequency noise characterization of GFETs [17].

<sup>&</sup>lt;sup>1</sup>Absolute values are considered. See results and discussions of Fig. 6(b)

Fig. 6. Measured and simulated Dirac voltage (a) and absolute value of the trap density (b) versus  $V_{\rm DS}$  for all available sweeps. Markers: data, lines: model. The different slopes of the plots in (a) are pointed out.

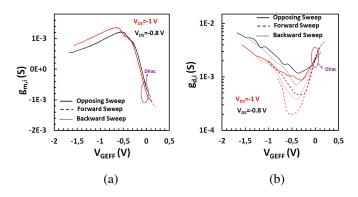

Synthetic intrinsic gain  $G = g_{m,i}/g_{d,i}$ , calculated with the simulated data<sup>2</sup>, is depicted in Fig. 7 for different  $V_{GS}$  at the p-type region for two high negative  $V_{DS}$  values in order to ensure both the p-type operation of the device and that G exceeds unity. It is evident that traps can affect tremendously this important analog FoM as well by affecting the DC bias point and consequently resulting in a *false-positive* result, i.e., an overestimated trap-affected G that can not be exploited in circuit applications since it depends on the measurement history of the device. A more reliable result is the one obtained with the diminished impact of traps which can be reproduced and used in circuits by using an appropriate biasing scheme.

Fig. 7. Simulated intrinsic gain at different bias for all available sweeps.

The higher impact of traps on  $g_d$  observed in the experiments (cf. Fig. 4) is also confirmed with the model since the larger the  $V_{\rm DS}$ , the more trapping/detrapping mechanisms can be enabled (higher  $N_{\rm tr}$ ). In contrast, the trap-affected  $I_{\rm D}$  changes slowly with the vertical applied fields, i.e.,  $g_{\rm m}$  is mainly shifted in  $V_{\rm GS}$  but not in magnitude ( $N_{\rm tr}$  shifted in  $V_{\rm GS}$ ). This is confirmed with the simulated  $g_{\rm m,i}$  and  $g_{\rm d,i}$  plots at different bias shown in Fig. 8.

Fig. 8. Simulated intrinsic (a) transconductance and (b) output conductance versus an effective gate voltage  $V_{

m GEFF}$ .

The effect of traps can be claimed to be diminished regardless the characterization technique if the difference of  $V_{\text{Dirac}}$  with  $V_{\text{GS}}$  is compensated, i.e., by a  $V_{\text{GEFF}} = V_{\text{GS}} - V_{\text{Dirac,tr}}$  for the staircase sweeps and  $V_{\text{GEFF}} = V_{\text{GS}} - V_{\text{Dirac}}$  for the opposing sweeps. At  $V_{\text{GEFF}} = 0$  V the values of the simulated  $g_{\text{m,i}}$  and  $g_{\text{d,i}}$  are the same for all sweeps at the same  $V_{\text{DS}}$  as shown in Fig. 8. This implies similar G at such bias. However, the condition of identical trap-affected characteristics required to exploit this feature is challenging to reproduce in practical scenarios since they are strongly affected by the measurement history. Hence, trap-reduced data should be always considered for feasible and reproducible device characteristics.

$^{2}V_{\text{GS},i} = V_{\text{GS}} - I_{\text{D}}R_{\text{C}}/2$  and  $V_{\text{DS},i} = V_{\text{DS}} - I_{\text{D}}R_{\text{C}}$  with  $R_{\text{C}}$  values of Table II.

#### V. CONCLUSION

Consecutive opposite bias pulses applied to a fabricated graphene transistor have been used here in order to diminish the impact of trapping processes on the device performance. This biasing scheme is more practical than the holding time approach generally used to obtain trap-reduced data. In contrast to other GFET studies focused on the device response to varying lateral field in the channel, the opposing pulses stressing the gate of the device here have enabled the observation of trapping effects due mainly to available states in the oxide, i.e., the channel potential is shielded from the applied vertical field due to traps. Trap-affected and trap-reduced static characteristics have been experimentally observed and qualitatively discussed. The oftenly overlooked impact of traps in analog/HF figures of merit has been shown here with calculations of the cutoff frequency and maximum oscillation frequency based on experimental data. The dynamic response can differ from the expected due to the DC bias-point drift induced by trapping processes. Trap-reduced data obtained with practical bias schemes, e.g., by the opposing pulse technique, can ease the design of matching networks for GFETs in high-frequency circuits by providing reproducible characteristics.

An analytical drain current model has been able to reproduce trap-reduced and trap-affected data by considering the impact of traps on the device electrostatics. Two empirical factors have been obtained to describe the  $V_{\text{Dirac}}$  shift and its  $V_{\text{DS}}$  dependence for the trap-affected data. The straightforward implementation of the latter effect in the compact model enables the study of GFET-based circuits including the trap-affected device performance. The trap density obtained from experimental data has been also reproduced by using the model parameters. The synthetic trap density over bias reveals also the effect of trapping and detrapping processes. An important analog figure of merit such as the intrinsic gain has been obtained here from the simulated data. Similarly to the HF FoMs ( $f_t$  and  $f_{max}$ ), an important difference is observed for this analog metric between trap-affected and trap-reduced results. Traps affect not only the biasing point but the magnitude of the intrinsic gain.

The impact of traps should be considered in both static and dynamic scenarios in order not to spoil the analog/HF performance of GFETs. A practical and straightforward biasing scheme as the one used here as well as the modeling approach presented in this work are convenient for both obtaining the trap-reduced device performance and exploiting the device dynamic characteristics in circuits.

#### REFERENCES

- [1] F. Schwierz, "Graphene Transistors: Status, Prospects, and Problems", *Proceedings of the IEEE*, vol. 101, no. 7, pp. 1567-1584, Jul. 2013. DOI: 10.1109/JPROC.2013.2257633

- [2] E. A. Carrion, A. Y. Serov, S. Islam, A. Behnam, A. Malik, F. Xiong, M. Bianchi, R. Sordan, E. Pop, "Hysteresis-Free Nanosecond Pulsed Electrical Characterization of Top-Gated Graphene Transistors", *IEEE Transactions on Electron Devices*, vol. 61, no. 5, pp. 1583-1589, May 2014. DOI: 10.1109/TED.2014.2309651

- [3] C. Mukherjee, S. Fregonese, T. Zimmer, C. Maneux, H. Happy, D. Mele, "Qualitative Assessment of Epitaxial Graphene FETs on SiC Substrates via Pulsed Measurements and Temperature Variation", in Proc. European Solid State Device Research Conference (ESSDERC), Venice, Italy, Sep. 2014. DOI: 10.1109/ESSDERC.2014.6948821

- [4] Y. J. Kim, Y. G. Lee, U. Jung, S. Lee, S. K. Lee, B. H. Lee, "A facile process to achieve hysteresis-free and fully stabilized graphene field-effect transistors", *Nanoscale*, vol. 7, 4013, Jan. 2015. DOI: 10.1039/c4nr06397j

- [5] J. Nathawat, M. Zhao, C.-P. Kwan, S. Yin, N. Arabchigavkani, M. Randle, H. Ramamoorthy, G. He, R. Somphonsane, N. Matsumoto, K. Sakanashi, M. Kida, N. Aoki, Z. Jin, Y. Kim, G.-H. Kim, K. Watanabe, T. Taniguchi, J. P. Bird "Transient Response of h-BN-Encapsulated Graphene Transistors: Signatures of Self-Heating and Hot-Carrier Trapping", ACS Omega, vol. 4, no. 2, pp. 4082-4090, Feb. 2019. DOI: 10.1021/acsomega.8b03259

- [6] A. D. Smith, S. Wagner, S. Kataria, B. G. Malm, M. C. Lemme, M. Östling,, "Wafer-Scale Statistical Analysis of Graphene Field-Effect Transistors—Part II: Analysis of Device Properties", *IEEE Transactions on Electron Devices*, vol. 64, no. 9, pp. 3927-3933, Sep. 2017. DOI: 10.1109/TED.2017.2727823

- [7] D. Neumaier, S. Pindl, M. C. Lemme, "Integrating graphene into semiconductor fabrication lines", *Nature Materials*, vol. 18, pp. 520-529, Jun. 2019. DOI: 10.1038/s41563-019-0359-7

- [8] Y. G. Lee, C. G. Kang, U. J. Jung, J. J. Kim, H. J. Hwang, H.-J. Chung, S. Seo, R. Choi, B. H. Lee, "Fast transient charging at the graphene/SiO2 interface causing hysteretic device characteristics", *Applied Physics Letters*, vol. 98, 183508, 2011. DOI: 10.1063/1.3588033

- [9] H. Madan, M. J. Hollander, J. A. Robinson, S. Datta, "Extraction of near interface trap density in top gated graphene transistor using high frequency current voltage characteristics", in Proc. Device Research Conference, 2012. DOI: 10.1109/DRC.2012.6257022

- [10] D.-C. Mao, S.-G. Wang, S.-A. Peng, D.-Y. Zhang, J.-Y. Shi, X.-N. Huang, M. Asif, Z. Jin, "The two timescales in the charge trapping mechanism for the hysteresis behavior in graphene field effect transistors", *Journal of Materials Science: Materials in Electronics*, vol. 27, pp. 9847-9852, Jun. 2016. DOI 10.1007/s10854-016-5052-x

- [11] H. Ramamoorthy, R. Somphonsane, J. Radice, G. He, J. Nathawat, C.-P. Kwan, M. Zhao, J. P. Bird, "Probing charge trapping and joule heating in graphene field-effect transistors by transient pulsing", *Semiconductor Science and Technology*, vol. 32, 084005, Jul. 2017. DOI: 10.1088/1361-6641/aa7ba3

[12] A. Mishra, A. Meersha, S. Raghavan, M. Shrivastava, "Observing non-equilibrium state of transport through graphene channel at the nano-second

- [12] A. Mishra, A. Meersha, S. Raghavan, M. Shrivastava, "Observing non-equilibrium state of transport through graphene channel at the nano-second time-scale", *Applied Physics Letters*, vol. 111, no. 26, 263101, Dec. 2017. DOI: 10.1063/1.5006258

- [13] M. Haferlach, A. Pacheco, P. Sakalas, M. Alexandru, S. Hermann, T. Nardmann, M. Schröter, M. Claus, "Electrical characterization of emerging transistor technologies: issues and challenges", *IEEE Transactions on Nanotechnology*, vol. 15, no. 4, pp. 619-626, 2016. DOI: 10.1109/TNANO.2016.2564925

- [14] M. Hellenbrand, E. Lind, O.-P. Kilpi, L.-E. Wernersson, "Effects of traps in the gate stack on the small-signal RF response of III-V nanowire MOSFETs", Solid-State Electronics, 2020. DOI: 10.1016/j.sse.2020.107840

- [15] L. Sang, Y. Xu, Y. Wu, R. Chen, "Device and Compact Circuit-Level Modeling of Graphene Field-Effect Transistors for RF and Microwave Applications", *IEEE Transactions on Circuits and Systems-I: Regular Papers*, vol. 65, no. 8, pp. 2559-2570, Aug. 2018. DOI: 10.1109/TCSI.2018.2793852

[16] N. Mavredakis, R. G. Cortadella, A. B. Calia, J. A. Garrido, David Jiménez, "Understanding the bias dependence of low frequency noise in single layer

- [16] N. Mavredakis, R. G. Cortadella, A. B. Calia, J. A. Garrido, David Jimenez, "Understanding the bias dependence of low frequency noise in single layer graphene FETs", *Nanoscale*, vol. 10, 14947, Jul. 2018. DOI: 10.1039/c8nr04939d

- [17] N. Mavredakis, W. Wei, E. Pallecchi, D. Vignaud, H. Happy, R. G. Cortadella, A. B. Calia, J. A. Garrido, D. Jiménez, "Velocity Saturation Effect on Low Frequency Noise in Short Channel Single Layer Graphene Field Effect Transistors", ACS Applied Electronic Materials, vol. 1, pp. 2626-2636, Nov. 2019. DOI: 10.1021/acsaelm.9b00604

- [18] M. Asad, M. Bonmann, X. Yang, A. Vorobiev, K. Jeppson, L. Banszerus, M. Otto, C. Stampfer, D. Neumaier, J. Stake, "The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties", *IEEE Journal of the Electron Devices Society*, vol. 8, pp. 457-464, Apr. 2020. DOI: 10.1109/JEDS.2020.2988630

- [19] S. Lee, K. Lee, C.-H. Liu, G. S. Kulkarni, Z. Zhong1, "Flexible and transparent all-graphene circuits for quaternary digital modulations", *Nature Communications*, vol. 3, no. 1018, Aug. 2012. DOI: 10.1038/ncomms2021

- [20] O. Habibpour, Z. S. He, W. Strupinski, N. Rorsman, H. Zirath, "Wafer scale millimeter-wave integrated circuits based on epitaxial graphene in high data rate communication", Scientific Reports, vol. 7, 41828, Feb. 2017. DOI: 10.1038/srep41828

- [21] W. Wei, X. Zhou, G. Deokar, H. Kim, M. M. Belhaj, E. Galopin, E. Pallecchi, D. Vignaud, H. Happy, "Graphene FETs With Aluminum Bottom-Gate Electrodes and Its Natural Oxide as Dielectrics", IEEE Transactions on Electron Devices, vol. 62, no. 9, pp. 2769-2773, Sep. 2015. DOI: 10.1109/TED.2015.2459657

- [22] S. Zafar, A. Kumar, E. Gusev, E. Cartier, "Threshold Voltage Instabilities in High-k Gate Dielectric Stacks", IEEE Transactions on Device and Materials Reliability, vol. 5, no. 1, pp. 45-64, Mar. 2005. DOI: 10.1109/TDMR.2005.845880

- [23] G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, G. Ghibaudo, "Review on high-k dielectrics reliability issues", IEEE Transactions on Device and Materials Reliability, vol. 5, no. 1, pp. 5-19, Mar. 2005. DOI: 10.1109/TDMR.2005.845236

- [24] A. Pacheco-Sanchez, I. Bejenari, M. Schröter, "Self-Heating Characterization and Thermal Resistance Modeling in Multitube CNTFETs", IEEE Transactions on Electron Devices, vol. 66, no. 11, pp. 4566-4571, Nov. 2019. DOI: 10.1109/TED.2019.2942783

- [25] M. Bonmann, A. Vorobiev, J. Stake, O. Engström, "Effect of oxide traps on channel transport characteristics in graphene field effect transistors", Journal of Vacuum Science and Technology B, vol. 35, 01A115, Jan. 2017. DOI: 10.1116/1.4973904

- [26] R. R. J. Vanoppen, J. A. M. Geelen, D. B. M. Klassen, "The high-frequency analogue performance of MOSFETs", in Proc. IEEE Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 1994. DOI: 10.1109/IEDM.1994.383437

- [27] A. Pacheco-Sanchez, P. C. Feijoo, D. Jiménez, "Contact resistance extraction of graphene FET technologies based on individual device characterization", Solid-State Electronics, vol. 172, 107882, Oct. 2020. DOI: 10.1016/j.sse.2020.107882

- [28] Z. Guo, R. Dong, P. S. Chakraborty, N. Lourenco, J. Palmer, Y. Hu, M. Ruan, J. Hankinson, J. Kunc, J. D. Cressler, C. Berger, W. A. de Heer, "Record Maximum Oscillation Frequency in C-Face Epitaxial Graphene Transistors", *Nano Letters*, vol. 13, pp. 942-947, Feb. 2013. DOI: 10.1021/nl303587r [29] C. Yu, Z. Z. He, Q. B. Liu, X. B. Song, P. Xu, T. T. Han, J. Li, Z. H. Feng, S. J. Cai, "Graphene Amplifier MMIC on SiC Substrate", *IEEE Electron*

- Device Letters, vol. 37, no. 5, pp. 684-687, May 2016. DOI: 10.1109/LED.2016.2544938

- [30] D. Jiménez, O. Moldovan, "Explicit Drain-Current Model of Graphene Field-Effect Transistors Targeting Analog and Radio-Frequency Applications", IEEE Transactions on Electron Devices, vol. 58, no. 11, pp. 4049-4052, Nov. 2011. DOI: 10.1109/TED.2011.2163517

- [31] S. A. Thiele, J. A. Schaefer, F. Schwierz, "Modeling of graphene metal-oxide semiconductor field-effect transistors with gapless large-area graphene channels", *Applied Physics Letters*, vol. 107, 094505, May 2010. DOI: 10.1063/1.3357398

- [32] S. Frégonèse, N. Meng, H.-N. Nguyen, C. Majek, C. Maneux, H. Happy, T. Zimmer, "Electrical compact modelling of graphene transistors", Solid-State Electronics, vol. 73, pp. 27-31, Apr. 2012. DOI: 10.1016/j.sse.2012.02.002

- [33] H.-Y. Chiu, V. Perebeinos, Y.-M. Lin, P. Avouris, "Controllable p-n Junction Formation in Monolayer Graphene Using Electrostatic Substrate Engineering", Nano Letters, vol. 10, no. 11, pp. 4634-4639, Oct. 2010. DOI: 10.1021/nl102756r