## Modeling of high-temperature superconducting pancake coils using the axisymmetric partial element equivalent circuit method

Rafael Medeiros, Loïc Quéval, Jean-Claude Vannier, Jing Dai, Philippe Egrot

### ► To cite this version:

Rafael Medeiros, Loïc Quéval, Jean-Claude Vannier, Jing Dai, Philippe Egrot. Modeling of high-temperature superconducting pancake coils using the axisymmetric partial element equivalent circuit method. 7th International Workshop on Numerical Modelling of High Temperature Superconductors (HTS 2020), Kévin Berger (Université de Lorraine - GREEN), Jun 2021, Nancy (Virtual), France. hal-03295740

## HAL Id: hal-03295740 https://hal.science/hal-03295740

Submitted on 22 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Modeling of high-temperature superconducting pancake coils using the axisymmetric partial element equivalent circuit method

Rafael Coelho-Medeiros<sup>1,2,3</sup>, Loic Queval<sup>1,2</sup>, Jean-Claude Vannier<sup>1,2</sup>, Jing Dai<sup>1,2</sup> and Philippe Egrot<sup>3</sup>

<sup>1</sup> Université Paris-Saclay, CentraleSupélec, CNRS, Laboratoire de Génie Electrique

et Electronique de Paris, 91192, Gif-sur-Yvette, France.

<sup>2</sup>Sorbonne Université, CNRS, Laboratoire de Génie Electrique et Electronique de Paris,

75252, Paris, France

<sup>3</sup>EDF R&D - Electrical Equipment Laboratory EDF Lab Les Renardières,

77250, Moret-sur-Loing, France

Abstract—The partial element equivalent circuit (PEEC) method has great potential to solve electromagnetic problems coupled with an electric circuit. Such capability is useful for modeling the integration of superconducting devices with power electronics converters. In this article we implement an axisymmetric PEEC model of pancake coils made of high-temperature superconducting (HTS) coated tapes fed by an arbitrary voltage source.

Keywords—partial element equivalent circuit (PEEC), superconducting pancake coils.

#### I. INTRODUCTION

Superconducting devices are expected to operate into complex environments. For example, superconducting fault current limiters (ScFCL) have already been successfully integrated into high-voltage grids with voltages ratings going from 10.5 kV to 220 kV [1], [2]. In such environments, the superconducting device may interact with power transformers, transmission lines, circuit breakers, power electronic converters, and electric machines. Other examples of possible future integration of superconducting devices in complex environments can be found in the literature. In [3], the author proposes the integration of a superconducting power filter for HVDC grids, [4] presents the integration of such filter into an aircraft electric DC Grid and in [5] possible applications of ScFCLs in transmission and distribution systems are studied. From a modeling perspective, the main challenge is to model the superconducting device coupled to an electrical circuit.

The partial element equivalent circuit (PEEC) method [6] is an electric circuit oriented approach to model electromagnetic problems based on the integral form of Maxwell's equations. It is well suited to model devices within electrical circuits and it has been widely used for problems having a small number of degrees of freedom due to its good performance in computation time compared to finite element (FE) methods.

However, the disadvantages of the PEEC method start to appears for medium and large numerical problems since the circuit matrices are dense due to inductive and capacitive coupling [6]. Thus, using the classical PEEC rectangular cells [6] to model pancake coils would generate a rather large system of equations. To overcome this problem, we use the PEEC method with axisymmetric cells with rectangular crosssections.

The article is organized as follows. In Section II, we derive the axisymmetric PEEC method and we explain its implementation for high-temperature superconducting pancake coils using an EJB constitutive law [7]. In Section III, we calculate current distribution and losses in AC and DC operation for an 8-turn HTS pancake coil and compare them with a FE model.

#### **II. AXISYMETRIC PEEC**

The full content of this section will be integrated in the final version of this article.

#### III. SIMULATION RESULTS FOR AN 8-TURN PANCAKE COIL

We consider an 8-turn pancake coil wound with 1G powderin-tube BSCCO tape of 4.5 mm width and 0.36 mm thickness. We model the BSCCO region and approximate it by a rectangular layer of 4.5 mm width and 45  $\mu$ m thickness divided into 50 current cells. The central layer of BSSCO is coated on both sides by a rectangular silver layer of 4.5 mm width and 90  $\mu$ m thickness followed by a rectangular copper layer of 4.5 mm width and 45  $\mu$ m thickness, each one of these layers is modeled by a single current cell. The geometric parameters of the application are listed in Table I and its electrical parameters are listed in Table II.

The PEEC model of this arrangement leads to a 372-th order system of ODEs solved using the built-in ode23s solver of MATLAB. Here we assume that the HTS pancake coil is fed by an arbitrary voltage source  $V_s(t)$ .

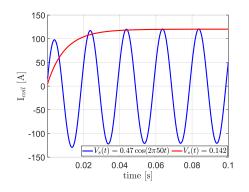

To study current distribution on the HTS pancake coil in AC and DC, let us consider the coil to be fed by a DC voltage source  $V_s(t) = 0.142$  and an AC voltage source

$V_s(t) = 0.47 \cos(2\pi 50t)$ . Both voltages sources will generate a peak current of 120 A (Fig. 1).

Fig. 1. Coil's current for voltage source excitation in AC and DC.

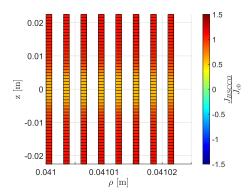

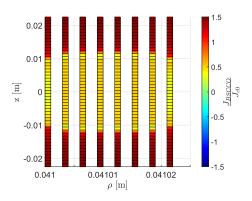

The resulting normalized current densities of the pancake coil in DC and AC are respectively plotted in Figs. 2 and 3. Notice that the space between layers is intentionally reduced for plotting.

Fig. 2. BSSCO layer normalized current density for DC with 120 A peak at  $t=0.0638\ s.$

Fig. 3. BSSCO layer normalized current density for AC with 120 A peak at t = 0.0638 s (peak current of the 4-th period).

The full content of this section will be integrated in the final version of this article.

TABLE I SIMULATION PARAMETERS

| Quantity               | Symbol            | Value        |

|------------------------|-------------------|--------------|

| Tape width             | $w_t$             | 4.5 mm       |

| BSCCO layer thickness  | $th_{BSCCO}$      | $45 \ \mu m$ |

| Silver layer thickness | $th_{Ag}$         | 90 µm        |

| Copper layer thickness | $th_{Cu}$         | $45 \ \mu m$ |

| Coil length            | L <sub>coil</sub> | 2 m          |

| Coil internal radius   | $R_{in}$          | 41 mm        |

| Insulation thickness   | $th_i$            | 0.18 mm      |

#### TABLE II SIMULATION PARAMETERS

| Quantity                   | Symbol      | Value                             |

|----------------------------|-------------|-----------------------------------|

| Critical electric field    | $E_c$       | $1 \times 10^{-4}$ V/m            |

| Power law exponent         | n           | 13                                |

| Critical current density @ | $J_{c0}$    | $2.148 \times 10^8 \text{ A/m}^2$ |

| 77.3 K and self field      |             |                                   |

| Constant for EJB law       | $B_0$       | 0.0682 T                          |

| Constant for EJB law       | k           | 0.0387                            |

| Constant for EJB law       | α           | 1                                 |

| Silver resistivity         | $\rho_{Ag}$ | $1.59 	imes 10^{-8} \ \Omega.m$   |

| Copper resistivity         | $\rho_{Cu}$ | $1.72 \times 10^{-8} \ \Omega.m$  |

| Connector resistance       | $R_c$       | $67.5 \ \mu\Omega$                |

#### **IV. CONCLUSION**

The full content of this section be integrated in the final version of this article.

#### REFERENCES

- [1] A. Hobl, S. Krämer, S. Elschner, C. Jänke, J. Bock and J. Schramm, "Superconducting fault current limiters — A new tool for the "Grid of the future"," CIRED 2012 Workshop: Integration of Renewables into the Distribution Grid, 2012, pp. 1-4, doi: 10.1049/cp.2012.0852.

- [2] M. Moyzykh et al., "First Russian 220 kV superconducting fault current limiter for application in city grid," in IEEE Transactions on Applied Superconductivity, doi: 10.1109/TASC.2021.3066324.

- [3] L. Queval, O. Despouys, F. Trillaud and B. Douine, "Feasibility Study of a Superconducting Power Filter for HVDC grids," 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), 2020, pp. P.1-P.7, doi: 10.23919/EPE20ECCEEurope43536.2020.9215939.

- [4] F. Trillaud, B. Douine and L. Queval, "Superconducting Power Filter for Aircraft Electric DC Grids," in IEEE Transactions on Applied Superconductivity, vol. 31, no. 5, pp. 1-5, Aug. 2021, Art no. 3700405, doi: 10.1109/TASC.2021.3060682.

- [5] H. Schmitt, "Fault current limiters report on the activities of CIGRE WG A3.16," 2006 IEEE Power Engineering Society General Meeting, 2006, pp. 5 pp.-, doi: 10.1109/PES.2006.1709205.

- [6] Albert Ruehli, Giulio Antonini and Lijun Jiang, "Circuit Oriented Electromagnetic Modeling Using the PEEC Techniques", IEEE, 2017, pp.9-46, doi: 10.1002/9781119078388.ch2.

- [7] Y. B. Kim, C. F. Hempstead and A. R. Strnad, "Critical persistent currents in hard superconductors," Phys. Rev. Lett., vol. 9, no. 7, p. 306, 1962.

- [8] S. Otten and F. Grilli, "Simple and Fast Method for Computing Induced Currents in Superconductors Using Freely Available Solvers for Ordinary Differential Equations," in IEEE Transactions on Applied Superconductivity, vol. 29, no. 8, pp. 1-8, Dec. 2019, Art no. 8202008, doi: 10.1109/TASC.2019.2949240.