## High voltage GaN-on-silicon with low-trapping up to 1200 V

A. Tajalli,<sup>1,\*</sup> I. Abid, <sup>2</sup> R. Kabouche, <sup>2</sup> M. Zegaoui, <sup>2</sup> M. Meneghini, <sup>1</sup> G. Meneghesso, <sup>1</sup> E. Zanoni, <sup>1</sup> A. Nishikawa<sup>3</sup> and F. Medjdoub<sup>2</sup>

<sup>1</sup>Department of Information Engineering, University of Padova, Italy <sup>2</sup>IEMN - CNRS, Institute of Electronics, Microelectronics and Nanotechnology, France <sup>3</sup>ALLOS Semiconductors GmbH, Dresden, Germany \*E-mail: tajalli@dei.unipd.it, farid.medjdoub@iemn.univ-lille1.fr

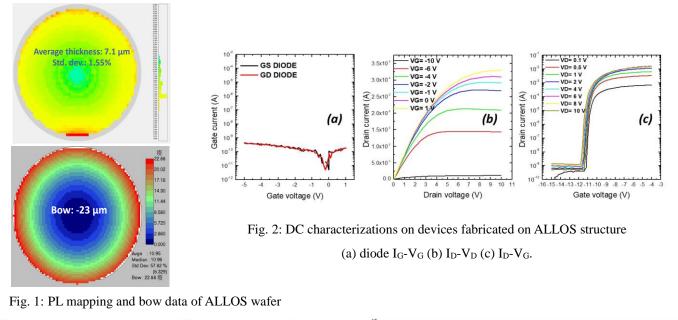

Carbon doped buffer within GaN heterostructures is widely used to increase the buffer resistivity and improve the electron confinement. However, it has been shown that carbon doping can also induce electron trapping under high electric field. This paper presents an assessment of a GaN-on-silicon buffer structure from the epi-wafer provider ALLOS Semiconductors GmbH targeting 1200 V power applications. This structure do not include intentional carbon doping showing a residual carbon below  $5 \times 10^{16}$  cm<sup>-3</sup> as measured by SIMS. The AlGaN/GaN heterostructure has been grown on 150 mm silicon (111) substrates by MOCVD. The total buffer thickness is as high as 7.1 µm with several interlayers for strain management. High crystal quality of GaN is observed, with XRD FWHM of (002) and (102) being 395 and 423 arcsec, respectively. The thickness uniformity is below 2% and the bow is less than 25 µm over the 6-inch wafer.

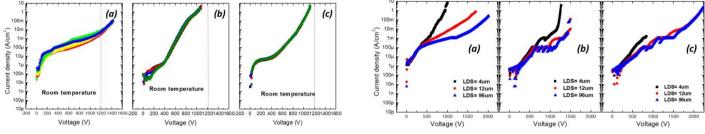

DC characteristics carried out on 2  $\mu$ m gate length transistors (using a 30 nm thick LPCVD SiN as gate dielectric) indicate low leakage and excellent pinch-off. These data confirm the absence of punch-through effects despite the fact that a carbon-free buffer has been used. Because of the thick and excellent crystal quality of the GaN buffer, low leakage current and state-of-the-art vertical breakdown voltage above 1400 V were achieved at room temperature. The vertical breakdown is above most of the commercially available GaN-based epi-structures (using typical thickness between 5 and 6  $\mu$ m) while delivering comparable floating lateral breakdown around 2 kV.

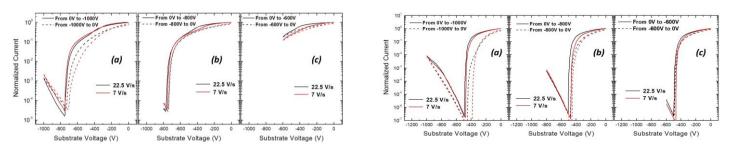

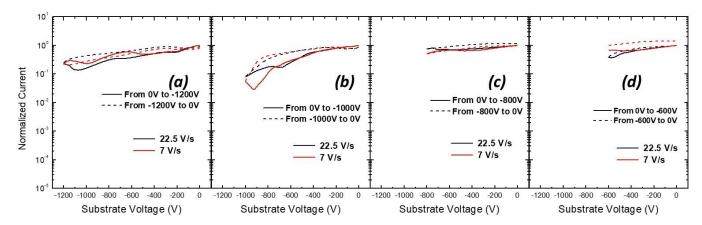

The effects of buffer traps have been studied by means of substrate bias ramp measurements. This approach is surface insensitive and applies a 1-D vertical field. Various sweep rates have been used because with slower sweep rates, the thermal generation rate of traps is expected to be enhanced. This is generally observed on 650V-rated commercial devices with trapping activation occurring below 1 kV with an enhancement of the charge storage when using slower sweep rates. In the case of the carbon-free thick buffer, low trapping effects are observed for the first time up to 1200 V. It can be pointed out that a low dependence of the substrate bias on the current density is also observed. This demonstrates the potential advantage of using carbon-free buffers, paving the way to GaN-on-silicon for 1200 V applications with a much lower on-resistance as compared to other existing technologies operating above 1 kV.

ACKNOWLEDGMENT: This work has received partial funding from the European Union's Horizon 2020 research and innovation program under grant agreement No 720527 project Innovative Reliable Nitride based Power Devices and (Inrel-NPower) and the French National grant ANR-16-CE05-0022-01 (DESTINEE).

Fig. 3: Vertical (left) and Lateral (right) breakdown voltage of (a) ALLOS structure (b), (c) commercial devices

Fig. 4: Substrate ramp down to (a) - 1kV (b) -800V (c) -600V on commercial device 1 (left) and commercial device 2 (right)

Fig. 5: Substrate ramp at two different rates on the ALLOS structure, down to (a) -1.2kV. (b) -1kV. (c) -800V. (d) -600V.