### Next generation of GaN-on-Silicon power devices

#### I. Abid, R. Kabouche, M. Zegaoui, and F. Medjdoub

# Outline

- o Introduction

- Towards 1200 V-rated GaN/Si buffers

(2 examples of successful achievements)

- High voltage epitaxy assessment

- Substrate ramp up to 1200 V

- Enhancement of GaN/Si BV using substrate removal technique

- High voltage DC characterizations

- Trapping assessment up to 3 kV

- Conclusion

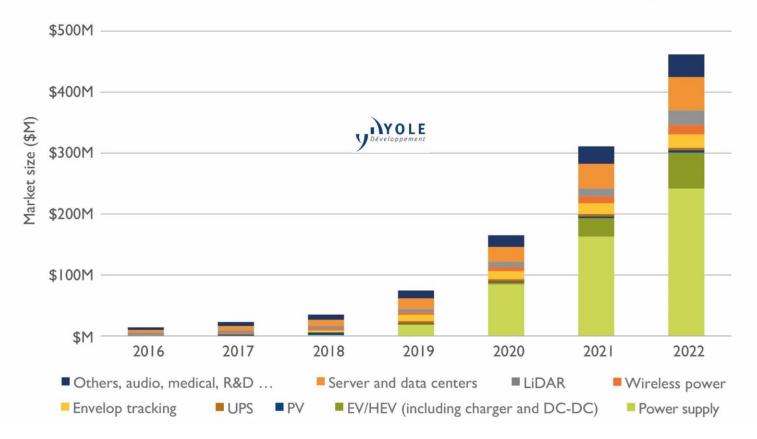

#### GaN power device market size split by application (\$M)

(Source: Power GaN 2017: Epitaxy, Devices, Applications, and Technology Trends 2017 report, Yole Développement, October 2017)

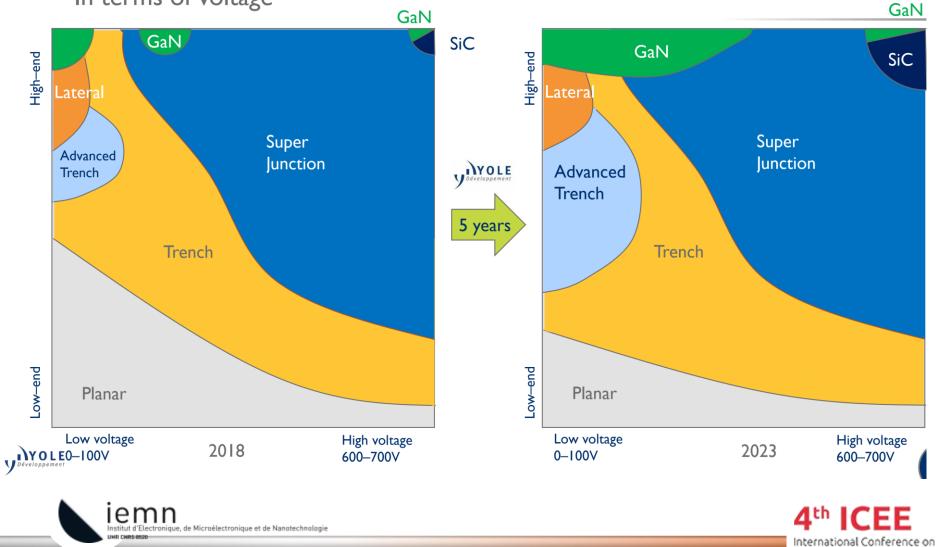

#### FUTURE MARKET DEVELOPMENT

In terms of voltage

**Emerging Electronics**

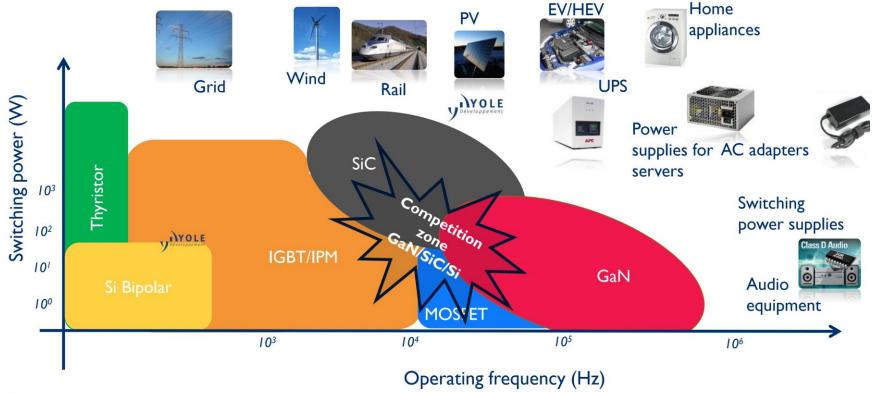

#### POWER VS FREQUENCY ON ELECTRONICS

Power device technology positioning (2018)

NYOLE

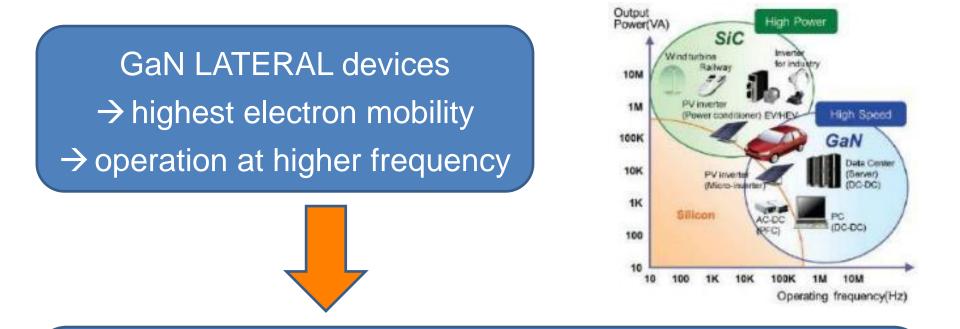

### GaN best choice for high speed power devices

For any voltage range that GaN / Si LATERAL devices can cover in a reliable way (e.g. low trapping effects) and with high enough blocking voltage margin, it should be the best choice for power applications based on the cost / performance ratio

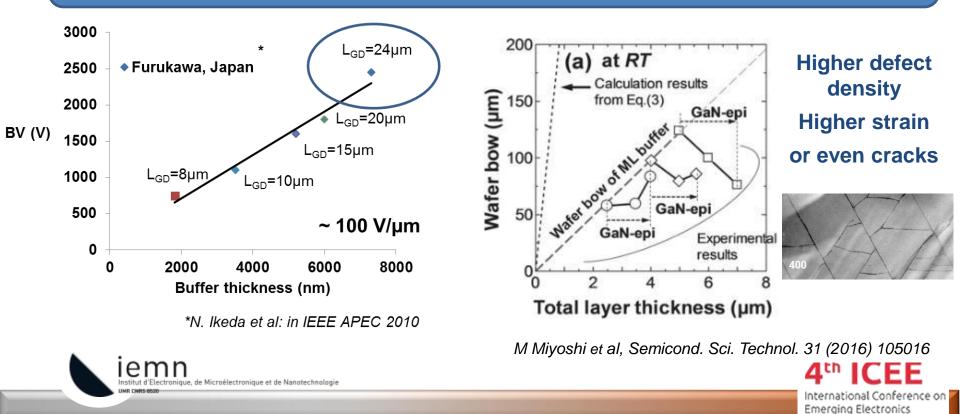

# **Breakdown limitation of GaN/Si**

However, 1.2 kV applications currently not reachable by GaN / Si due to :

- Limitation of breakdown voltage (buffer thickness with low bow < 6 μm)</li>

- Trapping assessment NEVER reported @ 1200 V yet

BV of GaN / Si scales with the buffer thickness but Thick buffers result in high wafer bow, high defect density and reliability issues

Targeting both higher vertical breakdown than available technologies WITH low trapping effects

A first example of a path for higher voltage GaN/Si operation with the development of thicker and carbon-free buffer layers

## Epiwafer structure and properties

> Carbon-free (which is known to induce trapping effects)

#### **Epiwafer structure**

| ~ 2 nm GaN cap                              |

|---------------------------------------------|

| ~ 20 nm Al <sub>23</sub> Ga <sub>77</sub> N |

| ~ 500 nm<br>GaN channel                     |

|                                             |

6.6 µm GaN buffer (proprietary design with several interlayers)

#### Silicon

que, de Microélectronique et de Nanotechnologie

| Parameters                                  | Values                                                                                                                            |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| XRD (002)                                   | 395 arcsec                                                                                                                        |

| XRD (102)                                   | 423 arcsec                                                                                                                        |

| Thickness                                   | 7.1 µm                                                                                                                            |

| Thickness STDEV                             | 1.55 %                                                                                                                            |

| Bow                                         | -23 µm (concave)                                                                                                                  |

| Residual impurities in GaN measured by SIMS | C: 4~5 x10 <sup>16</sup> cm <sup>-3</sup><br>H: 2 x10 <sup>17</sup> cm <sup>-3</sup><br>O: 1~2 x10 <sup>16</sup> cm <sup>-3</sup> |

| Mobility                                    | 2000 cm <sup>2</sup> /Vs                                                                                                          |

| Sheet resistance                            | 340 Ohm/sq.                                                                                                                       |

| Sheet resistance<br>STDEV                   | 1.5 %                                                                                                                             |

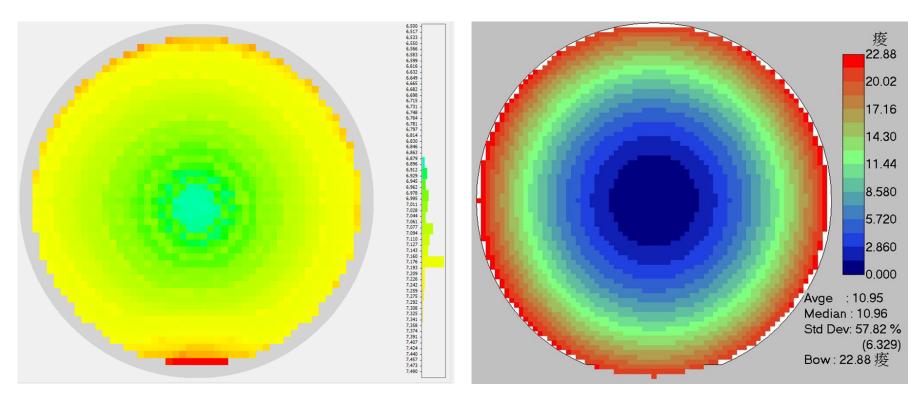

PL mapping and bow data for epiwafer

Despite the very thick buffer, high thickness uniformity and low bow are observed: efficient strain management

Average thickness: 7.1 µm STDEV: 1.55%

Bow: -23 μm

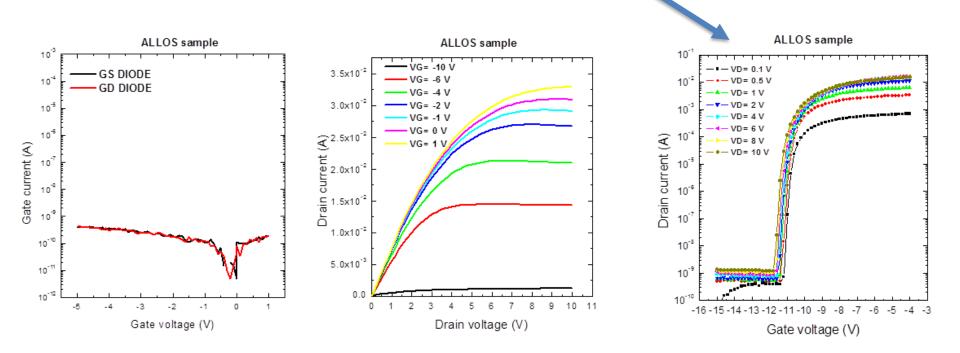

# **DC** characterization of transistors

- Low gate leakage current (MIS gate configuration)

- No evidence of punch-through effects despite the absence of carbon reflected by a high electron confinement

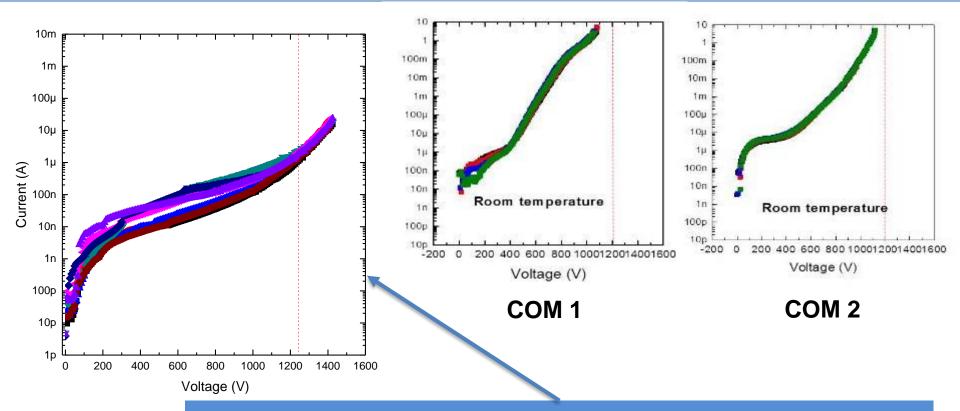

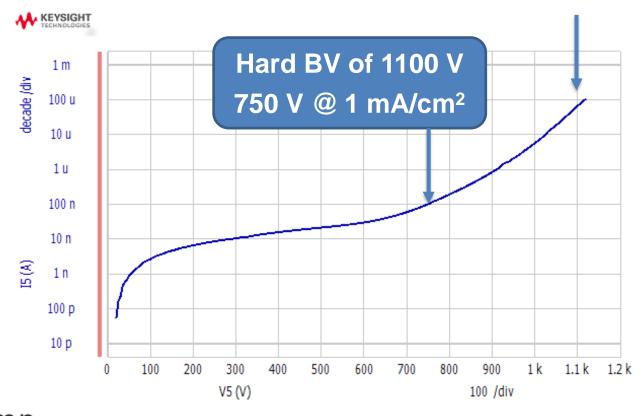

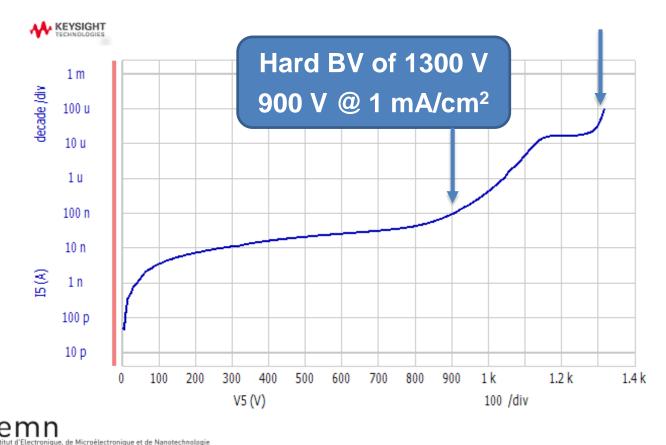

# **Vertical breakdown**

Vertical breakdown voltage above 1400 V, owing to the thicker buffer Still low leakage @ 1200 V favorably comparable to the state-of-the-art

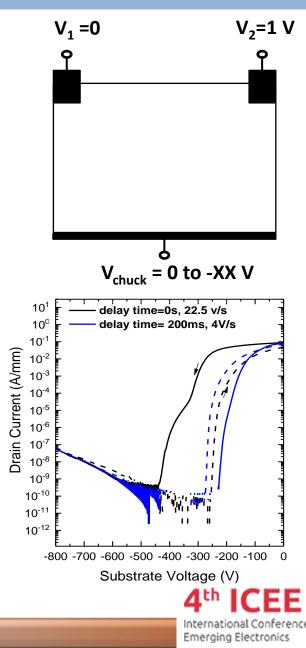

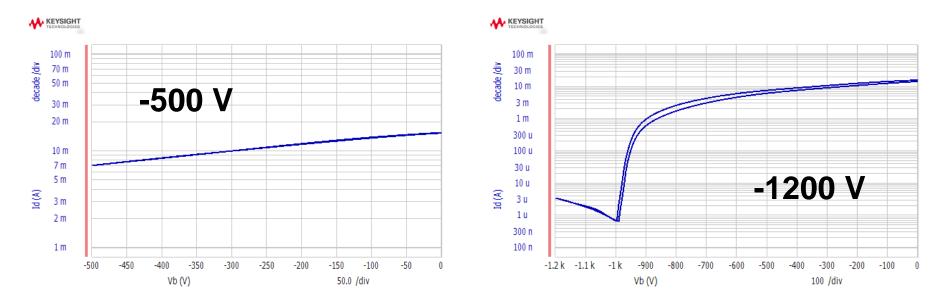

## Substrate ramp technique

- Simple and fast measurement giving information about the magnitude, the sign and the position relative to the 2DEG of stored charge

- By ramping the substrate to a high (negative) potential, mimicking the off-state operation under the drain contact in a transistor

- Any buffer charge trapping or storage will be visible in the substrate ramp characteristic

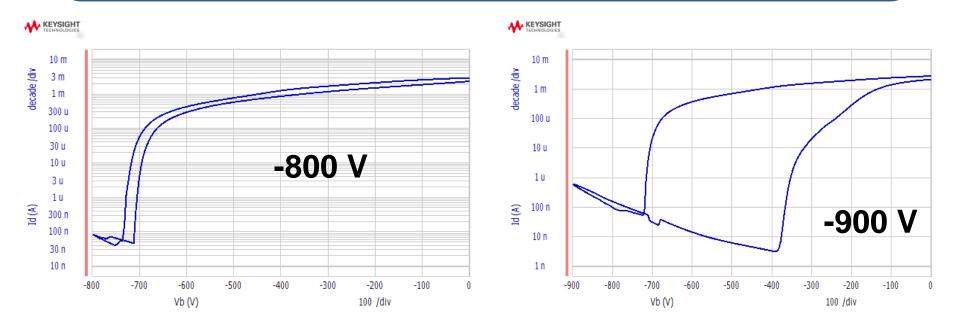

Example of sub. ramp measurements showing strong charge storage

# Substrate ramp for different rates

On commercial state-of-the-art 650V-rated epi-layers (≈ 6 µm)

- No trapping observed up to 800 V

- Trap activation @ 1 kV

- No measurements possible beyond 1 kV (breakdown voltage limited)

Emerging Electronics

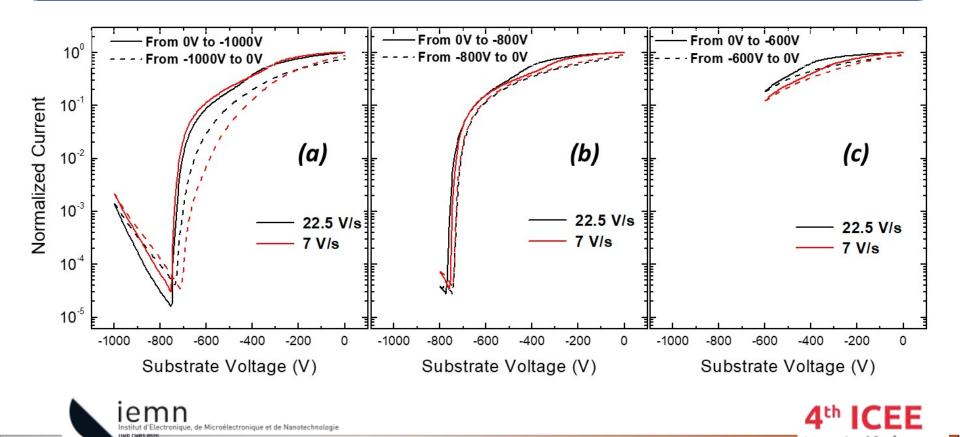

On ALLOS carbon-free epi-layers : wafer 1

$\,\circ\,$  Low trapping observed all the way to 1 kV

institut d'Electronique, de Microélectronique et de Nanotechnologi

ALLOS carbon-free epi-layers: wafer 2

Very low trapping observed up to 1200 V for various sweep rates

Paves the way to GaN-on-silicon for 1200 V applications

Emerging Electronics

Targeting both higher vertical breakdown than available technologies WITH low trapping effects

Another example of a path for higher voltage GaN/Si operation with the implementation of SL into the buffer layers

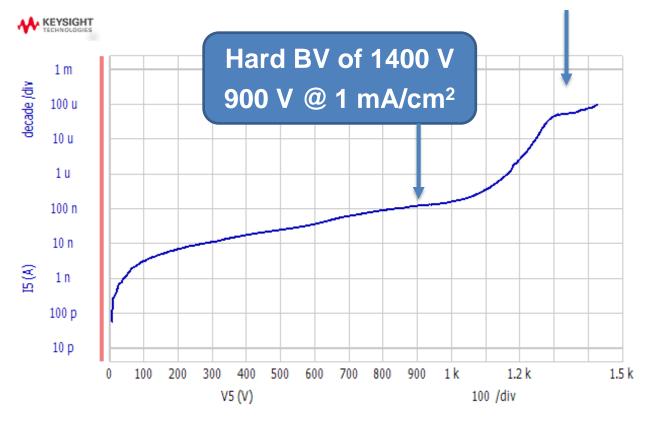

# **Vertical breakdown**

**Reference buffer optimized for 650 V applications :**

Specific double heterostructure Total thickness = 5.5 µm

onique, de Microélectronique et de Nanotechnologie

4<sup>th</sup> ICEE International Conference on Emerging Electronics

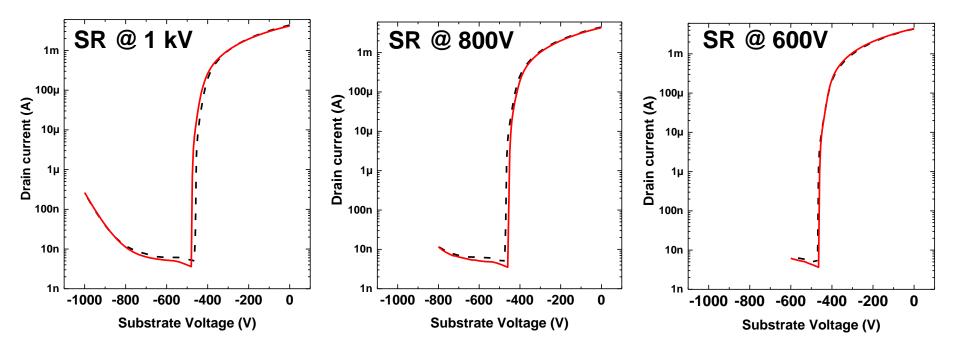

**Reference buffer optimized for 650 V applications :**

#### Specific double heterostructure Total thickness = 5.5 µm

Low trapping up to 800 V

Emerging Electronics

## **Vertical breakdown**

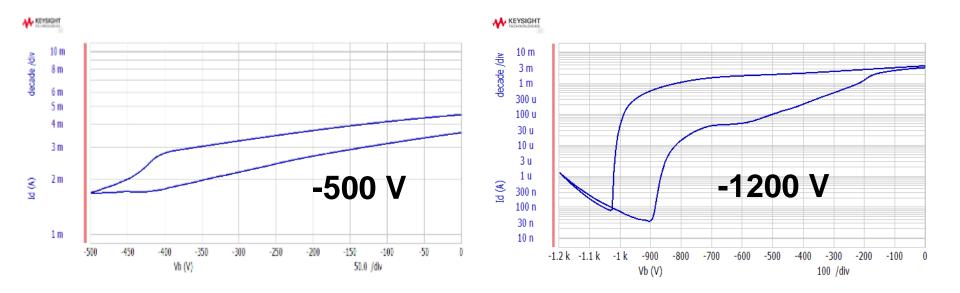

# Buffer including SL for higher voltage operation : Total thickness = $5.5 \ \mu m$

4<sup>th</sup> ICEE International Conference on Emerging Electronics

# Buffer including SL for higher voltage operation : Total thickness = $5.5 \ \mu m$

Severe trapping even @ 500 V

Emerging Electronics

# **Vertical breakdown**

Further optimized Buffer including SL for higher voltage operation :

#### Total thickness = 5.5 µm

4<sup>th</sup> ICEE International Conference on Emerging Electronics

Further optimized Buffer including SL for higher voltage operation :

#### Total thickness = 5.5 µm

Very low trapping observed all the way to 1200 V uniformly

Targeting both higher vertical breakdown than available technologies WITH low trapping effects

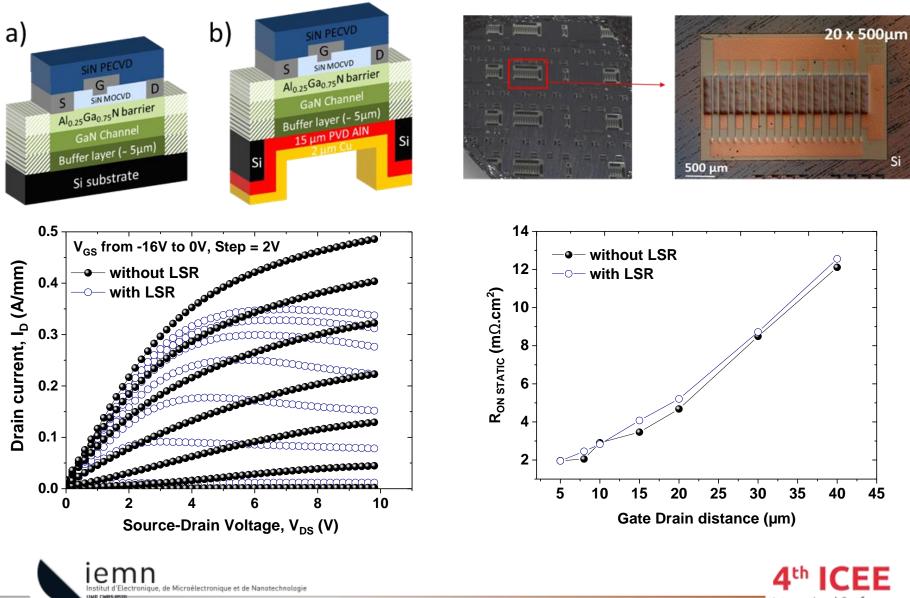

A last example of a path for higher voltage GaN/Si operation with the use of a local substrate removal technique and subsequent replacement with AIN ultra-wide bandgap

## Local substrate removal technique

International Conference on Emerging Electronics

## Local substrate removal technique

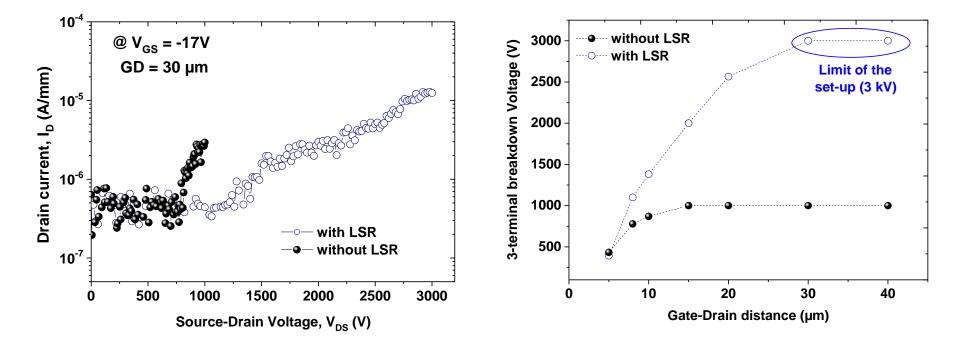

#### 2-terminal breakdown voltage

## Local substrate removal technique

#### **3-terminal breakdown voltage**

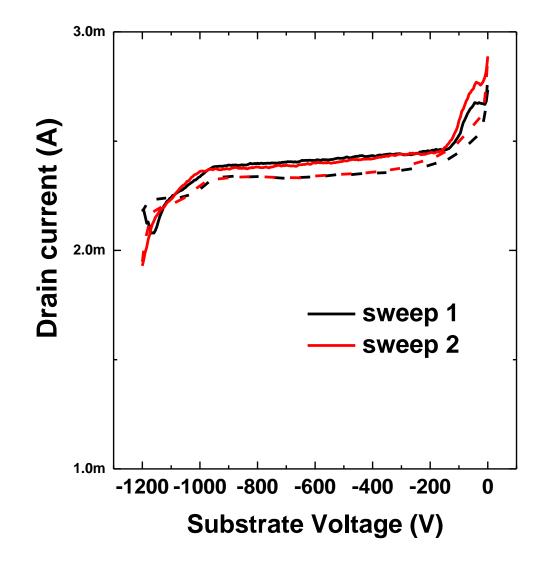

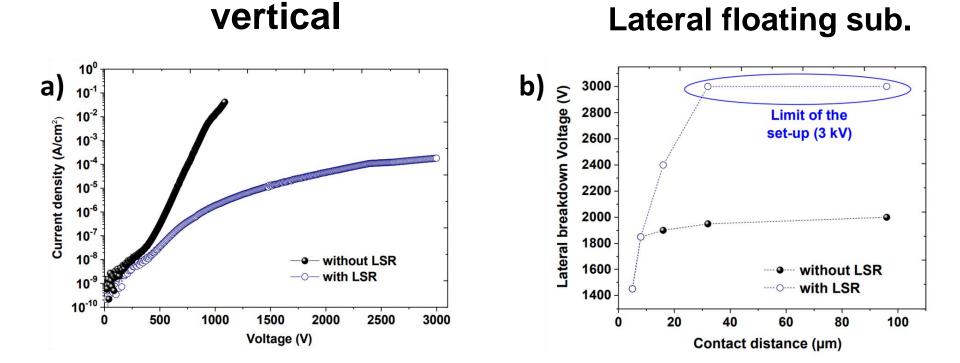

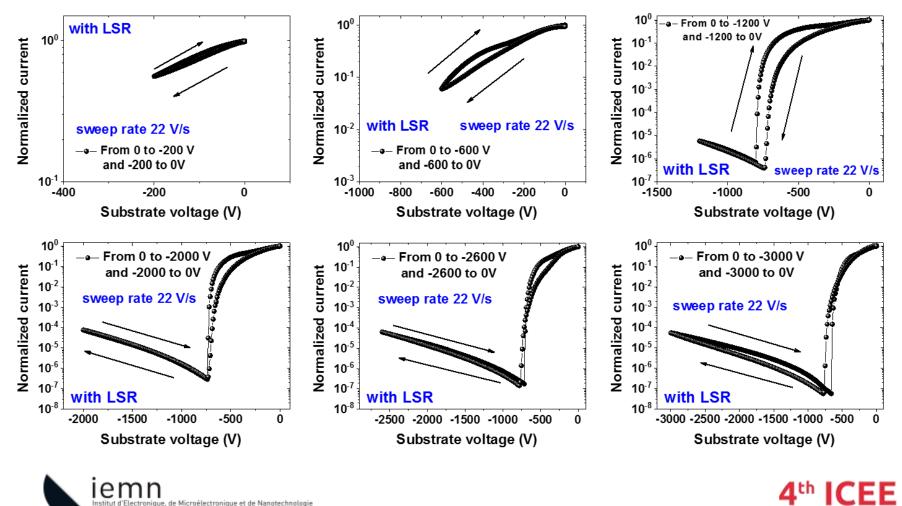

# Demonstration of low trapping using GaN/Si up to 3 kV for the first time

International Conference on Emerging Electronics

# Conclusion

- C-free and thicker (7 µm) GaN buffer on Si allows low leakage current and state-of-the-art vertical breakdown voltage above 1400 V

- Optimized SL implementation enables 1200 V + BV with low trapping effects

- LSR enabled not only to drastically enhance the BV of GaN/Si HEMTs but also does not induce any additional trapping effects

These results show that several ways for the improvement of lateral GaN devices are already available in order to satisfy 1200 V applications