# Novel Heterostructures for Millimeter-wave GaN devices

#### R. Pecheux, R. Kabouche, M. Zegaoui, and <u>F. Medjdoub</u>

Université de Lille

- Introduction

- Challenges and issues for mmW GaN devices

- Development of SiN/AIN/GaN DHFET

- Importance of the buffer configuration:

C-doped AIN/GaN HEMTs

- Potential advantages of ultrathin "buffer-free"

GaN HEMTs for mmW

- Conclusion

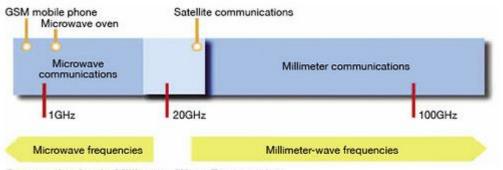

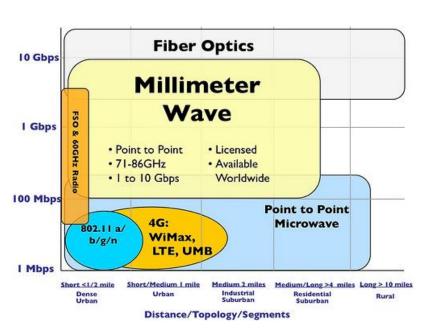

## Future communication in mmW frequency range

Towards significantly increased bandwidth

Communication in Millimeter-Wave Frequencies

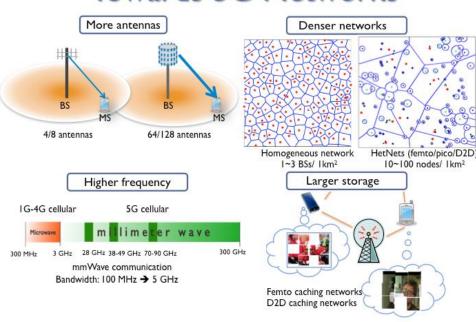

#### Towards 5G Networks

Millimeter Waves Will Expand The Wireless Future with larger bandwidth and smaller device size: more antennas, denser networks, faster communications, larger storage...

#### **IEMN-CNRS**

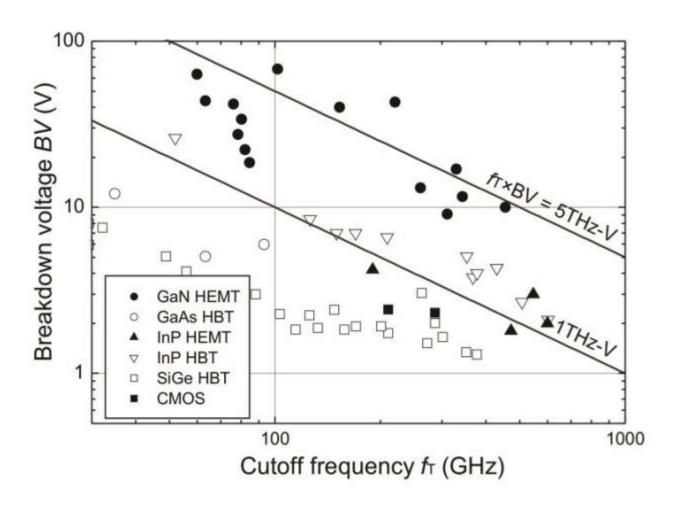

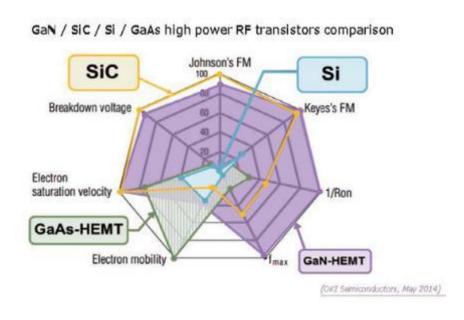

## Comparison of Johnson's figure-of-merit (JFoM) among various high-speed device technologies

$f_T \times V_{BK}$  five times better for GaN (theoretically this is true up to THz range)

## GaN devices delivered on their promises

- Significant advantages over GaAs technology or TWT

- Small size + high robustness (T°C, damp conditions) make GaN transistors the preferred choice for next generation SSPA

Triquint devices

6.5W Ku-band GaAs Power Amplifier

20W Ku-band GaN Power Amplifier

- In order to overcome the TWT, GaN will have to show extremely high power and efficiency also at higher frequency.

- High power density (e.g. high operating voltage) of a single GaN device has to be maintained while increasing frequency of operation.

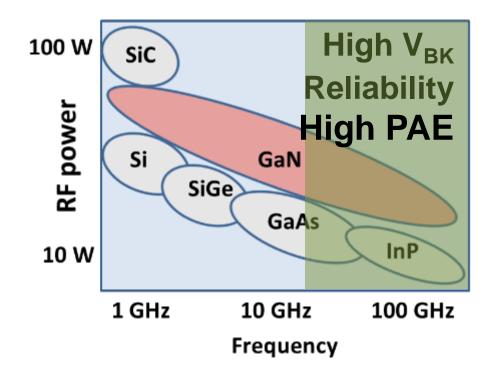

## GaN will cover the entire frequency range

Even though major challenges are still to be overcome beyond 30 GHz such as high  $V_{\rm BK}$ , reliability and especially high PAE

- o Introduction

- Challenges and issues for mmW GaN devices

- o Development of SiN/AlN/GaN DHFET

- Importance of the buffer configuration:

C-doped AIN/GaN HEMTs

- Potential advantages of ultrathin "buffer-free"

GaN HEMTs for mmW

- o Conclusion

## Issues and limitations for mmW applications

- Bias operation:

- √ V<sub>DS</sub> ≤ 15 V at 40 GHz and above

- Gate and drain leakage currents under high electric field

- Limited efficiency

- ✓ PAE ≤ 40% at 40 GHz +

- Reliability

- ✓ Not yet demonstrated on sub-150 nm GaN technology

#### Limiting factors of GaN device PAE

- High gain at frequency of operation (i.e. high frequency performances)

- Low R<sub>ON</sub> (minimizing the losses)

- Self-heating (i.e. T<sub>channel</sub>) affecting the effective electron mobility under high bias

- Trapping effects both from surface and buffer to avoid dc to RF dispersion

# Device robustness and reliability: crucial for any applications

➤ GaN RF industrial devices currently qualified up to K band (~30 GHz) using standard AlGaN/GaN structure with gate length down to 0.15 μm

## Improved epilayers quality:

bulk traps, interfaces, point defects...

#### <u>Technology</u>:

Ohmic contacts reproducibly  $< 0.4 \Omega$ .mm

Schottky contact: low gate leakage current

Passivation: low surface trapping

#### Epi & device design:

%Al into the barrier layer and use of field plates to reduce the electric field peak around the gate

Larger device topology in order to decrease the self-heating

Key factors to achieve highly reliable GaN RF devices

#### **IEMN-CNRS**

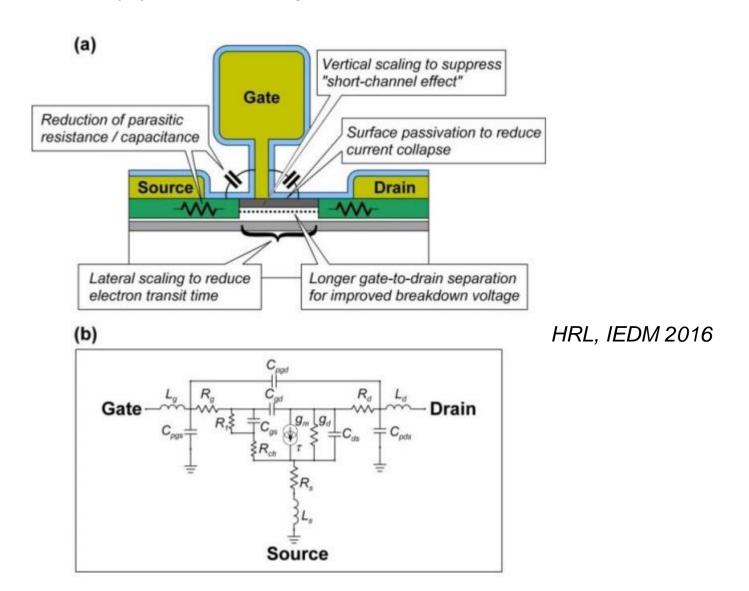

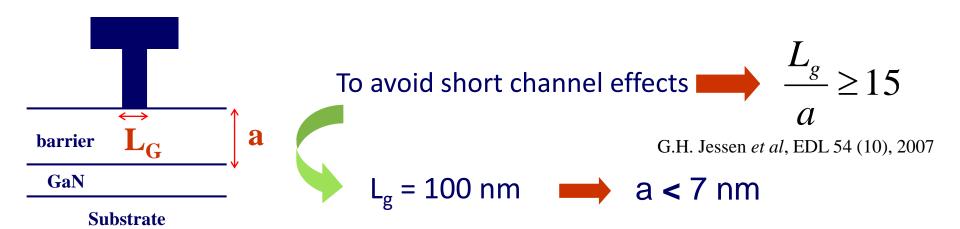

## Important device scaling features for high frequency operation (a) and an equivalent circuit model

○ For Ka band and above (35 GHz +), the power gain becomes an issue with standard AlGaN barrier by using  $L_G \le 0.15 \ \mu m$

### Gate recess for mmW GaN devices: not an option!

InAIN

Gate leakage issue not solved!

**InAlGaN**

AIN

**IEMN-CNRS**

# Device robustness and reliability: crucial for any applications

For mmW apps, reduction of %AI, use of FP or large device design are not possible

#### Improved epilayers quality:

bulk traps, interfaces, point defects...

#### <u>Technology</u>:

Ohmic contacts reproducibly  $< 0.4 \Omega$ .mm

Schottky contact: low gate leakage current

Passivation: low surface trapping

#### Epi & device design:

%Al into the barrier layer and use of field places to reduce the electric field peak around the gate

Larger device topology in order to decrease the self-heating

# Top RF performances achieved with ultrathin Al-rich HEMTs up to the W-band

AIN/GaN HEMTs with  $F_T > 450$  GHz Y. Tang et al, IEEE EDL, 2015 from HRL

AIN/GaN HEMTs with high PAE at V-band M. Micovic *et al*, IEEE EDL, 38 (12) 2017 from HRL

3.6 W/mm High Power Density W-band InAlGaN/GaN HEMT MMIC PA Y. Nida *et al*, IEDM 2016 from Fujitsu

Significant progress in N-polar GaN devices up to W band also recently achieved

However still limited in terms of leakage current, breakdown voltage, and reliability (to be proven)

- o Introduction

- o Challenges and issues for mmW GaN devices

- Development of SiN/AIN/GaN DHFET

- Importance of the buffer configuration:

C-doped AIN/GaN HEMTs

- Potential advantages of ultrathin "buffer-free"

GaN HEMTs for mmW

- o Conclusion

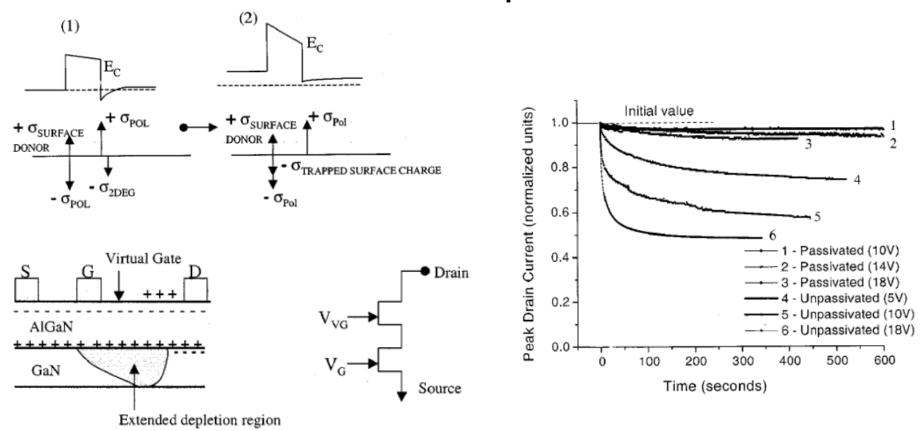

## DC-to-RF dispersion

GaN-based heterostructures: inherent surface charges dependent on the electric field, directly interacting with the 2DEG and creating a so-called virtual gate that extends the depletion region, especially when the surface is close to the 2DEG.

Surface charges needs to be properly passivated, otherwise the maximum current available during a microwave power measurement will be limited.

#### **HEMT Surface Passivation with SiN**

Cleaning procedures for GaN are based on nitridation (N2 plasmas, NH3 plasmas, (NH4)2S, Thermal treatments in N2 or NH3) + ex-situ SiN passivation

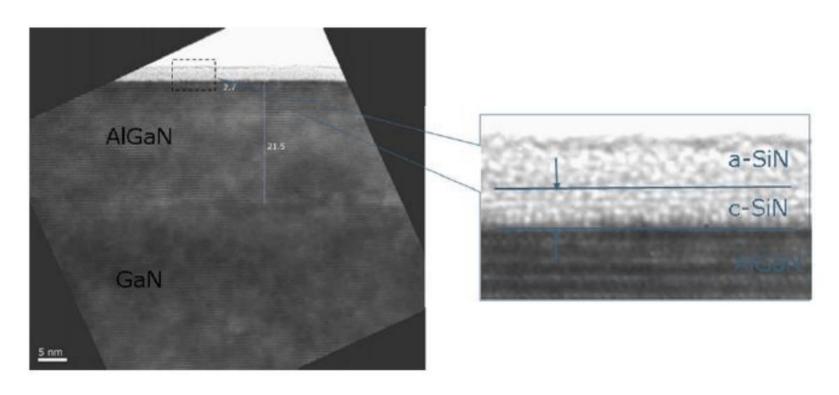

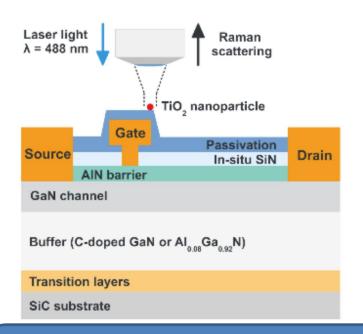

#### **HEMT Surface Passivation with in-situ SiN**

SiN deposited inside the MOCVD tool ending the heterostructure growth

- Clean interface

- Crystalline interface

- Relaxation prevention

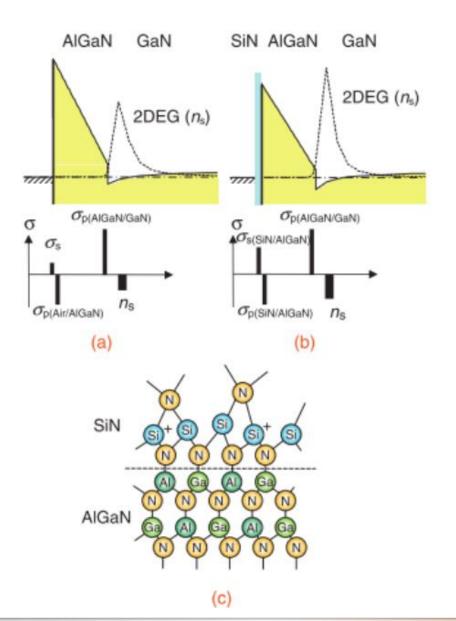

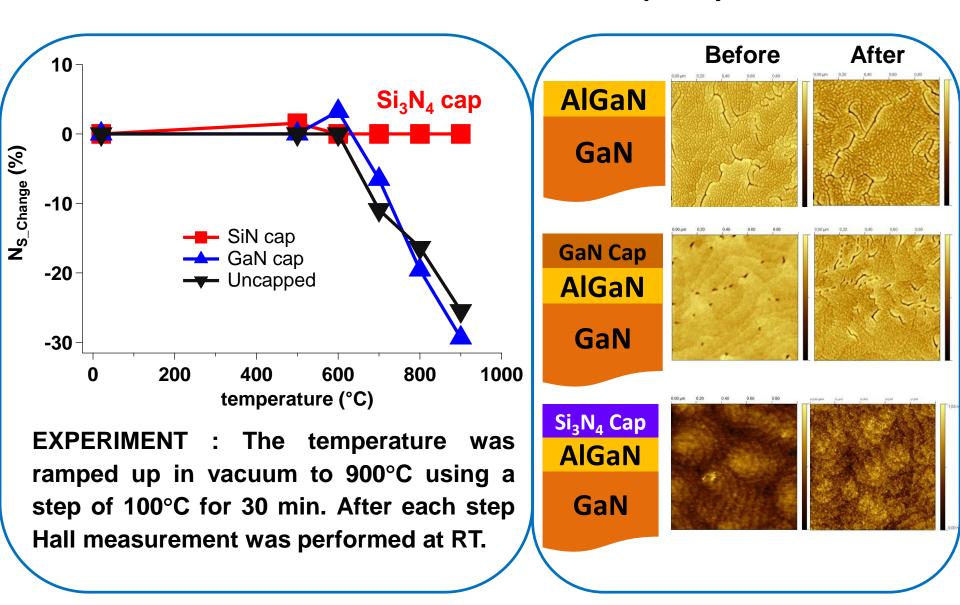

## Benefit of in-situ SiN cap layer

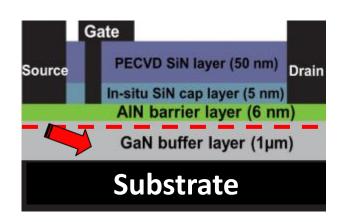

## AIN/GaN heterostructure

#### An old idea but difficult to achieve:

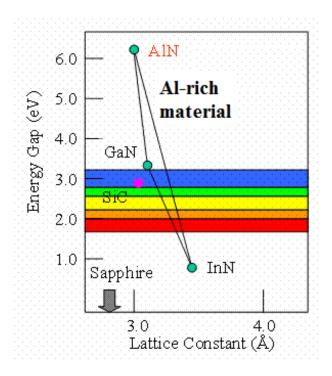

Use of the widest III-N bandgap (AIN), theoretically the most attractive material to maintain high polarization while using ultrathin barrier

### **Challenges:**

- Leakage through / on top of the ultrathin barrier

- Leakage following extra PECVD SiN passivation

- Leakage due to punch-through effects (electron injection into the buffer)

- Trapping effects: surface close to the 2DEG

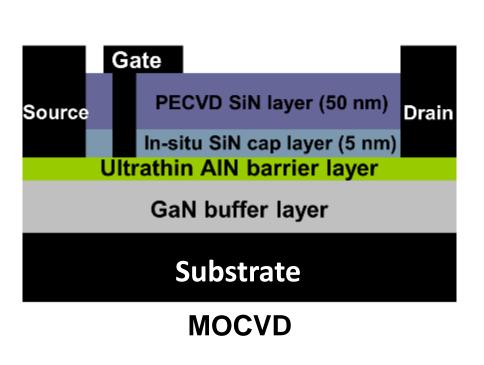

## Development of a novel GaN mmW devices

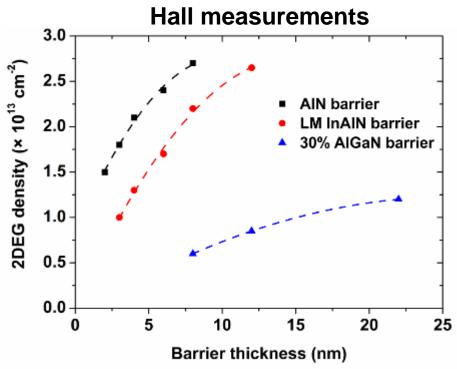

Much higher 2DEG density with ultrathin AIN barriers with  $\mu > 1000 \text{ cm}^2/\text{Vs}$

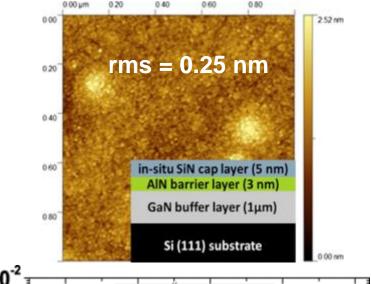

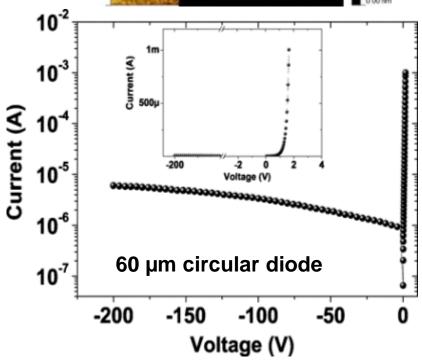

## Low gate leakage through only 3 nm AlN barrier

High surface quality owing to the in-situ SiN preventing strain relaxation

Low Schottky gate leakage deposited directly on the AIN barrier layer (see forward diode)

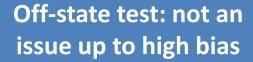

## Buffer confinement for high voltage operation

## What about high voltage operation when using ultrashort GaN devices?

Poor electron confinement can be expected even if the material and processing are of high quality

#### Back barrier needed

Punch-through effect: Poor electron confinement even if the material and processing are of high quality

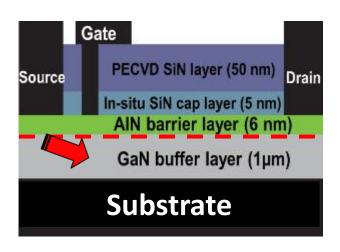

#### DHFET

Introduction of an AlGaN back barrier to prevent the electron injection under high bias (double heterostructure: DHFET)

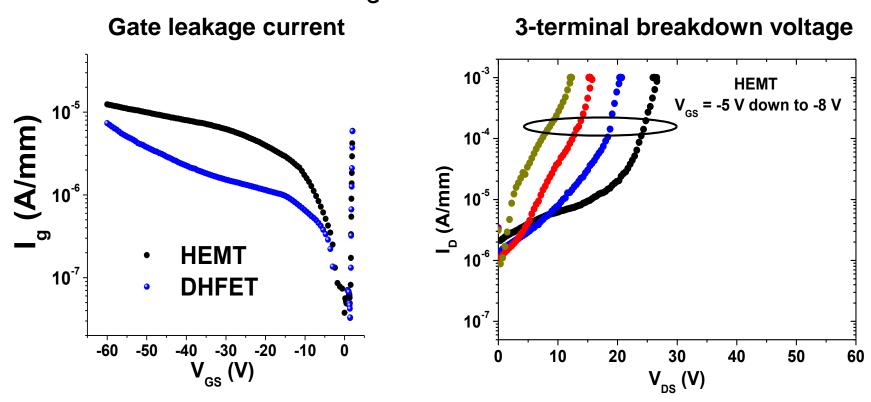

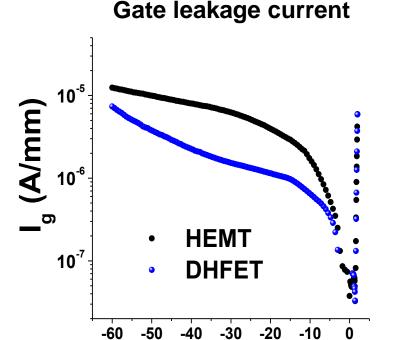

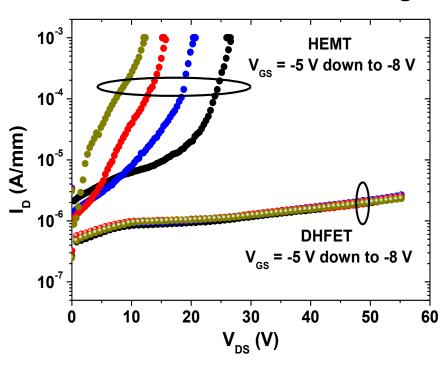

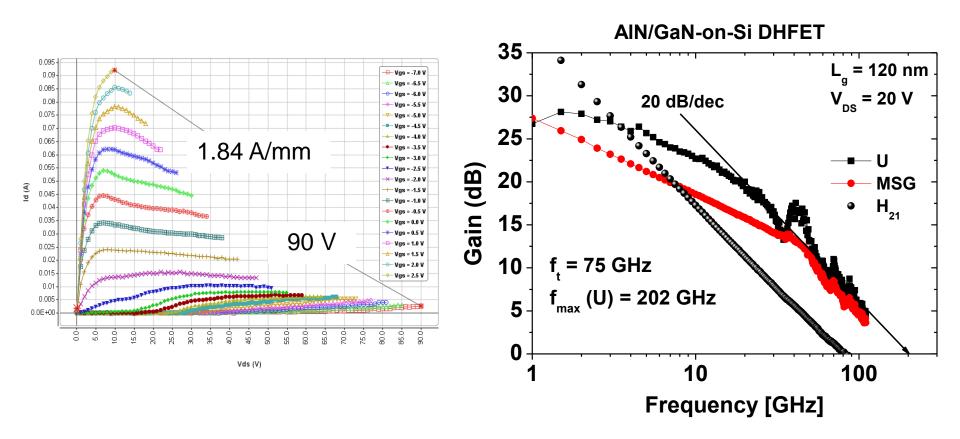

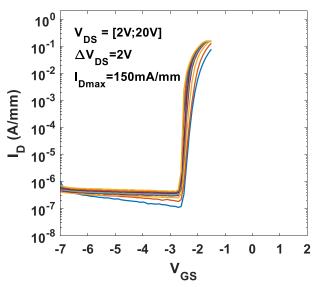

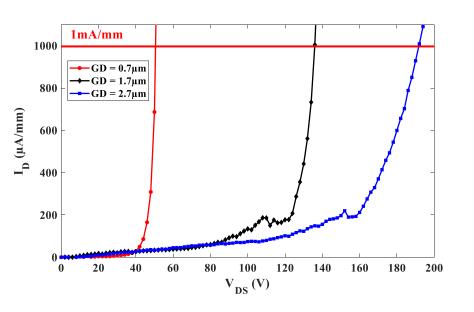

## AIN/GaN DHFET under high bias

$L_{G} = 200 \text{ nm}$

- Low Gate leakage current in both cases

- Huge drain leakage current: punch-through effect!

### AIN/GaN DHFET under high bias

$$L_{G} = 200 \text{ nm}$$

$V_{GS}(V)$

#### 3-terminal breakdown voltage

- Low Gate leakage current in both cases

- Low drain leakage: punch-through effect significantly reduced resulting in high  $V_{BK}$  (2  $\mu$ A/mm @  $V_{DS}$  = 50 V)

## Improvement of the electron confinement under high electric field to further push the GaN performance limits

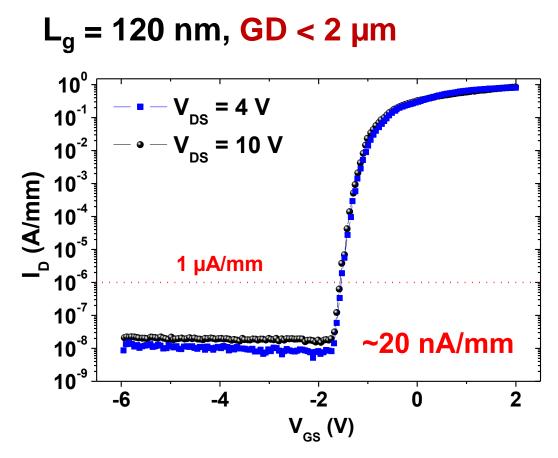

Outstanding subthreshold leakage current < 1  $\mu$ A/mm for sub-150 nm  $L_g$  while using a Schottky contact on < 5 nm AlN barrier thickness showing an excellent electron confinement owing to an optimized buffer configuration

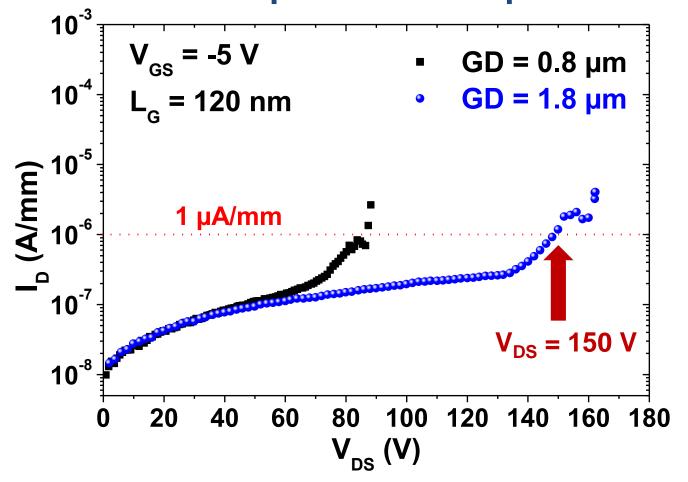

# Improvement of the electron confinement under high electric field to further push the GaN performance limits

BV about 100 V/ $\mu$ m for GD < 2  $\mu$ m while using L $_g$  sub-150 nm with extremely low leakage current < 1 $\mu$ A/mm up to 150 V which is quite untypical

## High combination: $f_{max} \times V_{BK}$

Fully reproducible devices delivering both high breakdown and high f<sub>max</sub>

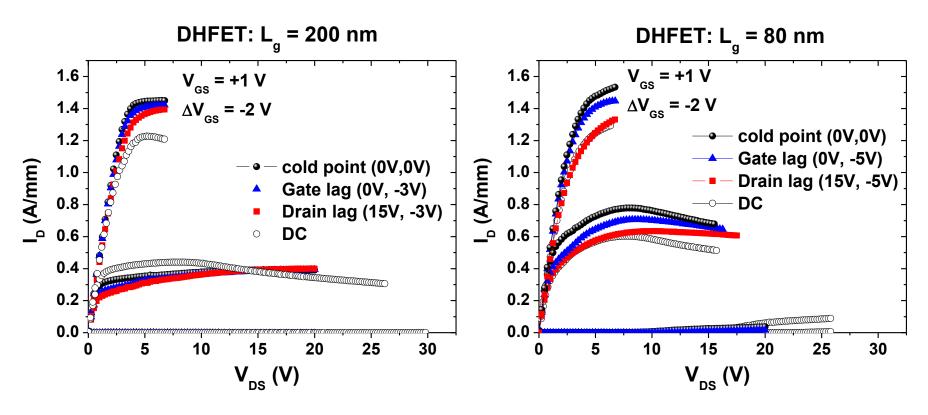

### Improved dynamic behavior in short GaN devices

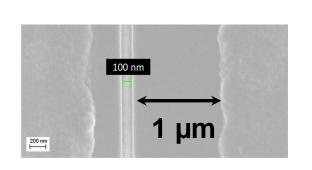

AIN/GaN devices using a critical SiN cap thickness (L<sub>G</sub> down to sub-100 nm)

Low trapping effects under 500 ns pulse width in highly scaled AIN/GaN devices

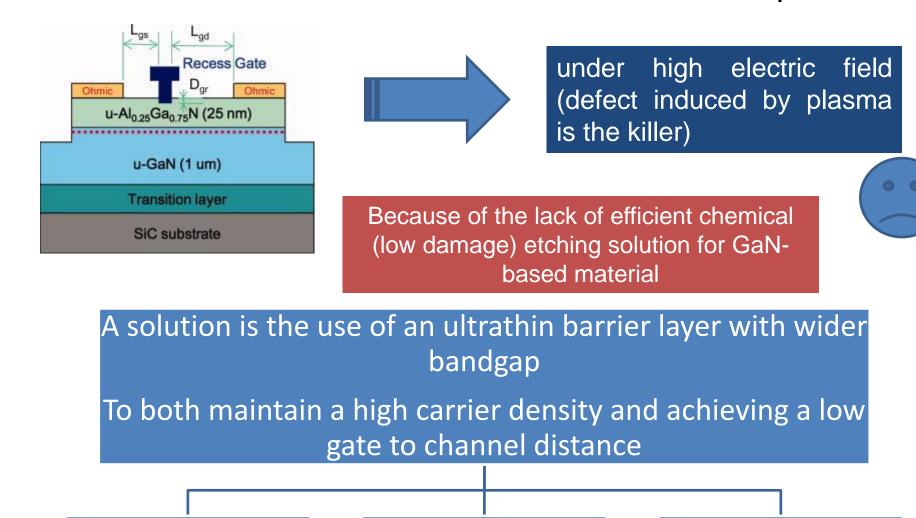

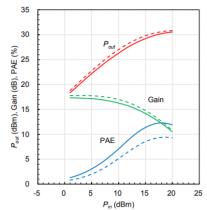

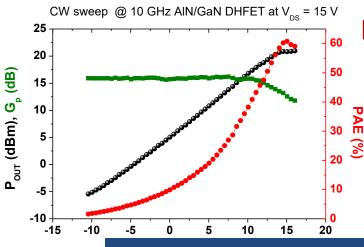

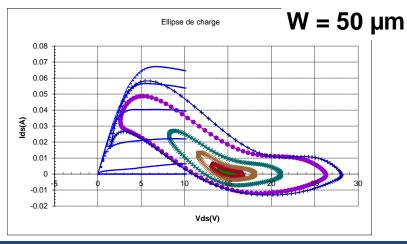

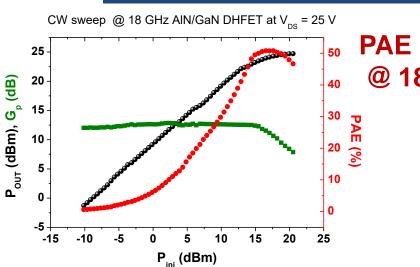

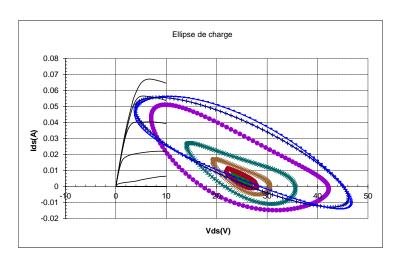

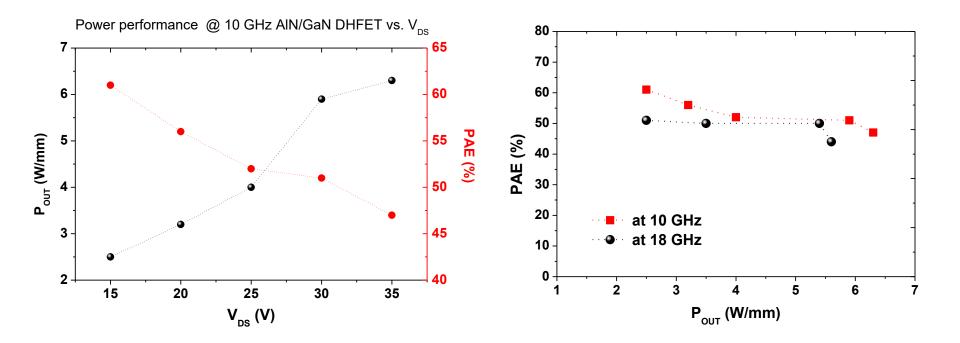

## 0.15 μm AlN/GaN-on-SiC power measurement @ 10 and 18 GHz

4 nm barrier thickness!

PAE > 60% @ 10 GHz

Load lines reflect the low RF dispersion The power gain confirms the high frequency performances

PAE > 50% @ 18 GHz

High PAE for the first time on sub-10 nm barrier GaN devices

#### 0.15 μm AlN/GaN-on-SiC power measurement @ 10 and 18 GHz

- High bias operation with ultrathin barrier GaN devices

- High PAE maintained up to high power densities

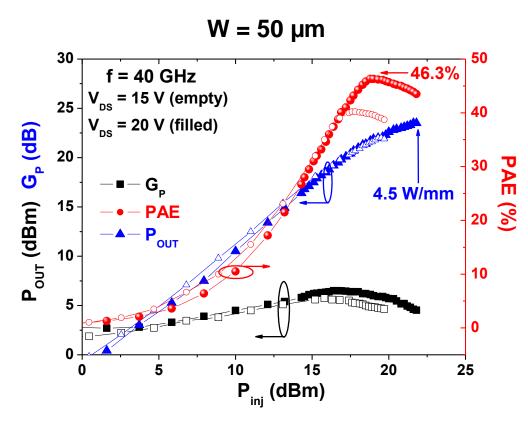

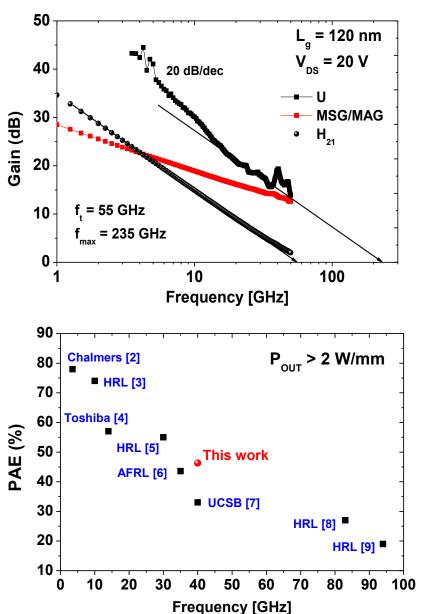

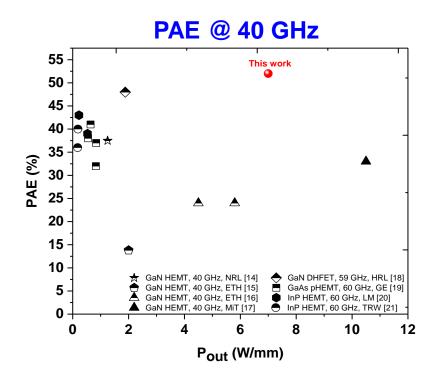

### 0.15 µm AlN/GaN-on-SiC power measurements @ 40 GHz

State-of-the-art PAE @ 40 GHz for GaN devices

$L_{G} = 150 \text{ nm}$

$GD = 2 \mu m$

f<sub>max</sub> ≥ 200 GHz

Thermally-limited in semi-on conditions for  $V_{DS} \approx 15$  to 20 V

surface robustness enhancement owing to the in-situ SiN cap layer

Optimum electron confinement owing to the back barrier

Poor thermal dissipation of the AlGaN back barrier

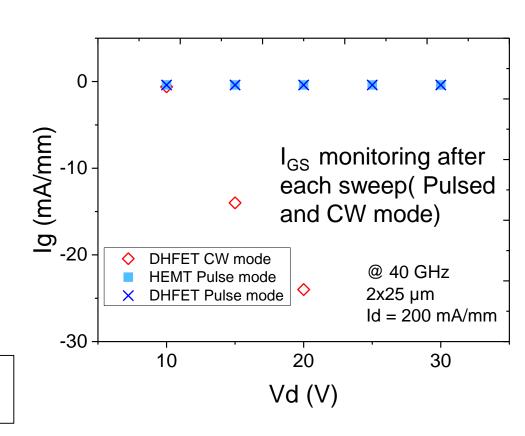

#### Device robustness

- DHFET in CW mode

- Strong degradation

- DHFET in Pulse mode

- No degradation

Pulse Mode reduces the selfheating effect in the transistor

Degradation due to self heating resulting from the poor thermal dissipation of the thick AlGaN back barrier

AIN/GaN DHFET is a very good solution up to about 15 V drain bias operation with excellent performance but other buffer configurations are needed to operate beyond 15 V

For short GaN devices, it seems that hot electron is one of the prime factor degrading the reliability.

- o Introduction

- o Challenges and issues for mmW GaN devices

- o Development of SiN/AlN/GaN DHFET

- Importance of the buffer configuration:

C-doped AIN/GaN HEMTs

- Potential advantages of ultrathin "buffer-free"

GaN HEMTs for mmW

- o Conclusion

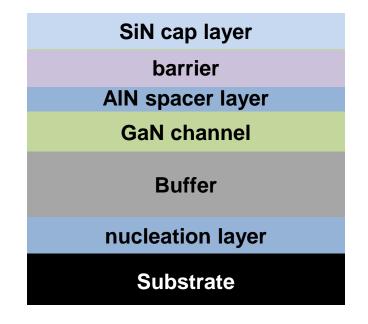

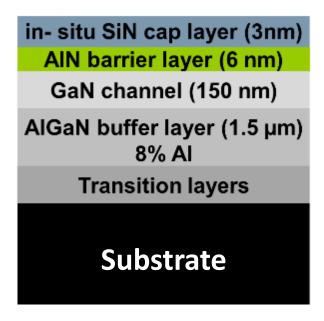

# Change in the buffer layers: From AlN/GaN DHFET to C-doped HEMT

#### **DHFET**

In-situ SiN cap layer (10 nm)

AIN barrier layer (4 nm)

GaN channel

AlGaN thick back barrier

**Transition layers**

4-inch SiC substrate

In-situ SiN cap layer (10 nm)

AIN barrier layer (4 nm)

GaN channel

**C-doped GaN buffer**

**Transition layers**

4-inch SiC substrate

Much better thermal dissipation expected in HEMT configuration but what about electron confinement and trapping effects

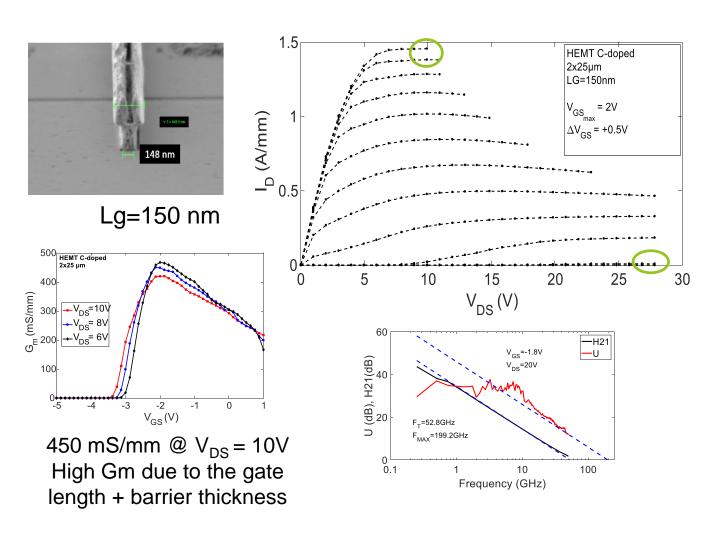

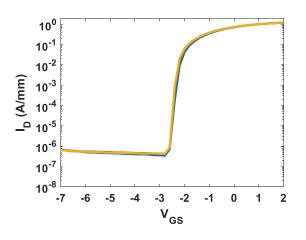

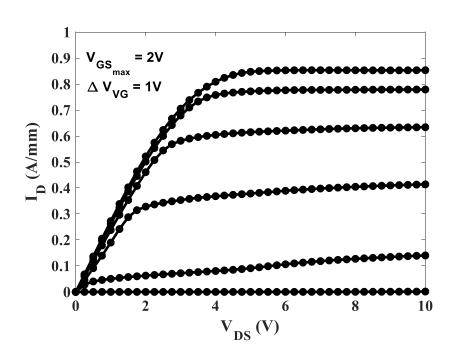

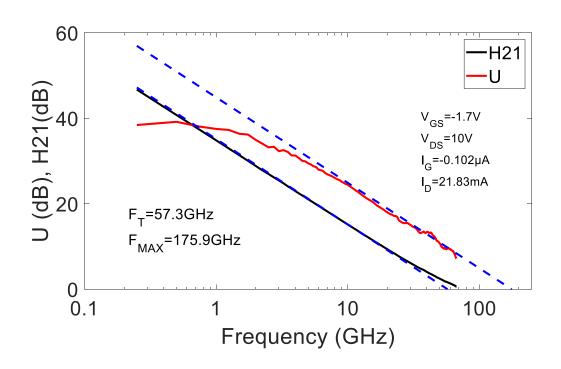

### DC Characteristics of AlN/GaN C-doped HEMT

- ➤ 1.4 A/mm @ V<sub>GS</sub> = 2V High current density owing to high Ns

- > Low leakage current (<1µA/mm)

- High electronic confinement

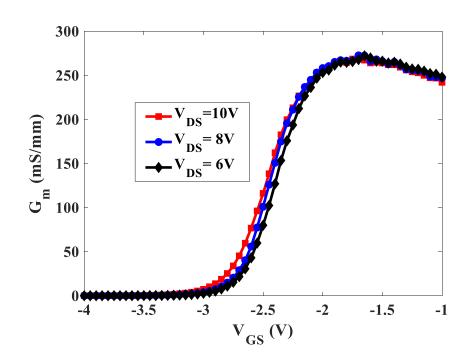

- ➤ High frequency performance F<sub>T</sub>=60GHz/F<sub>MAX</sub>=200GHz

- Operation bias up to 30V with high gain @ 40 GHz

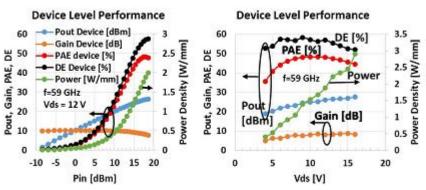

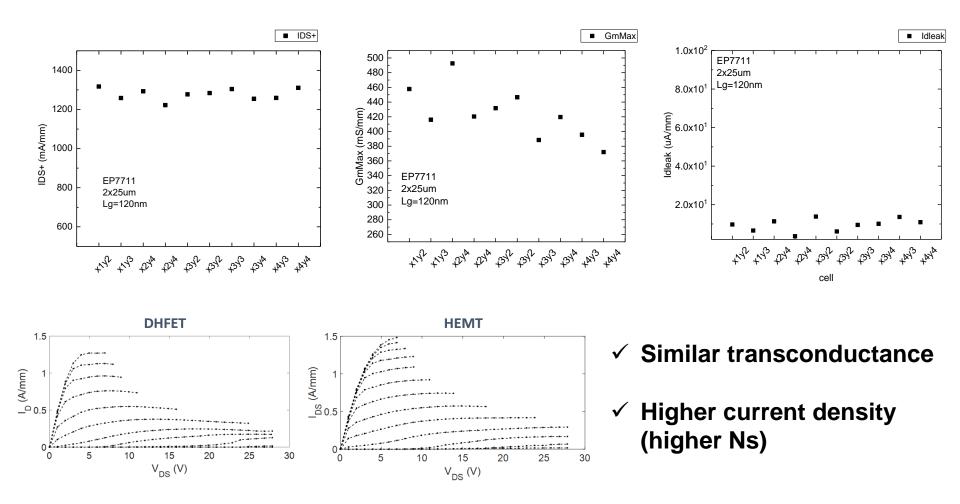

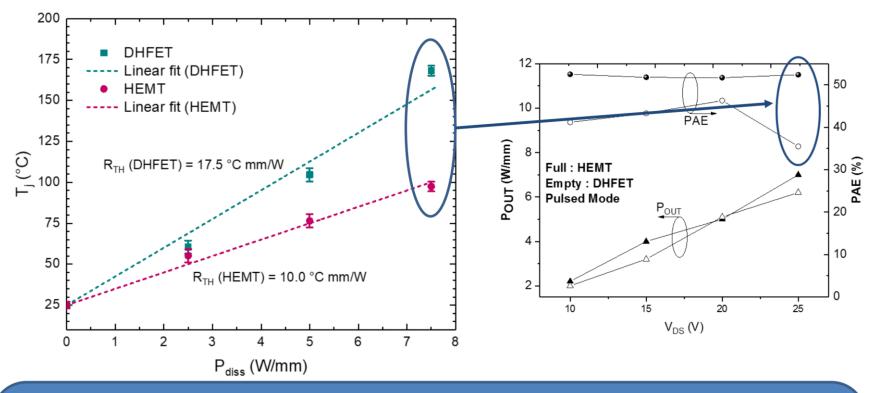

#### Comparison of the AlN/GaN DHFET and HEMT using $L_G = 120 \text{ nm}$

#### Comparison of the AIN/GaN DHFET and HEMT using $L_G = 120 \text{ nm}$

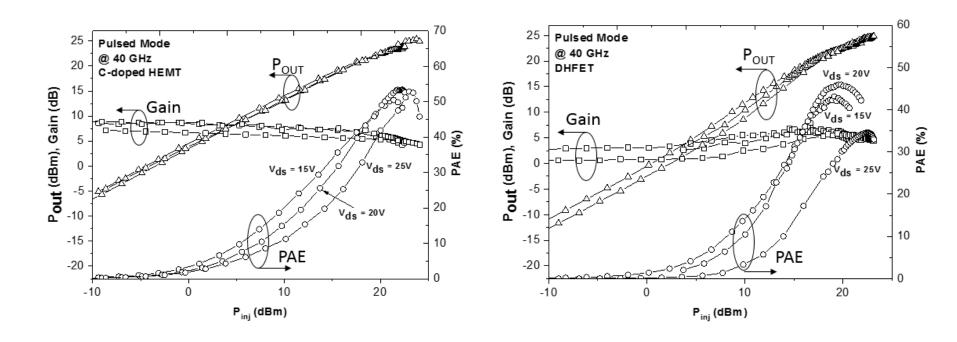

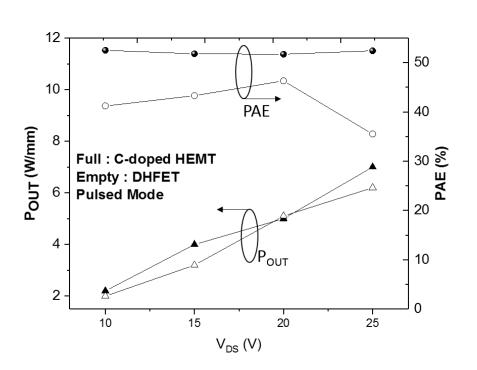

- √ High power density in both cases

- ✓ Strong degradation of the PAE at  $V_{DS} = 25V$  for the DHFET due to self-heating despite the pulsed mode.

#### Comparison of the AIN/GaN DHFET and HEMT using $L_G = 120 \text{ nm}$

- ✓ Better PAE for the HEMT attributed to a better thermal dissipation

- ✓ State-of-the-art PAE @ 40 GHz

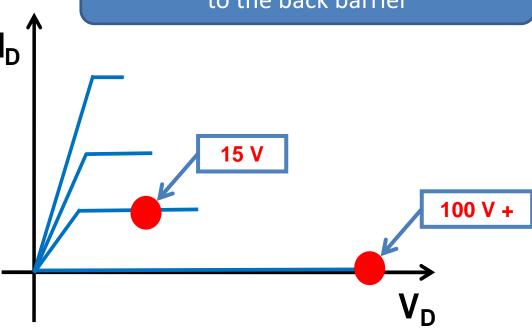

## AIN/GaN Device robustness

- DHFET in CW mode

- Strong degradation

- DHFET in Pulse mode

- No degradation

- HEMT in Pulse mode

- No degradation

Pulse Mode reduces the selfheating effect in the transistor

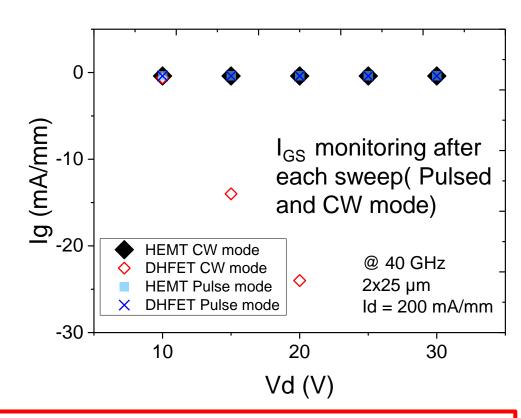

## AIN/GaN Device robustness

- DHFET in CW mode

- Strong degradation

- DHFET in Pulse mode

- No degradation

- HEMT in Pulse mode

- No degradation

- HEMT in CW mode

- No degradation

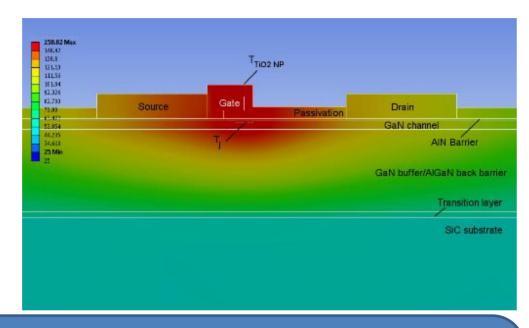

- The absence of degradation shows the superior thermal conductivity of the carbon-doped GaN buffer as compared to the AlGaN back barrier

- Owing to the better heat dissipation through the buffer, the C-doped HEMT can operate up to V<sub>DS</sub>=30V against V<sub>DS</sub>=15V for the DHFET

## AIN/GaN Device robustness

**Lg=120nm**

**Before**

After

#### **Raman Thermography measurement**

- Thermal shift of E<sub>g</sub> Raman peak of TiO<sub>2</sub> nanoparticles (NP) deposited on the device surface

- Measurement by confocal Renishaw InVia Raman microscope in backscattering configuration under 488 nm laser excitation

University of Bristol

#### **Raman Thermography measurement**

#### As expected:

- $T_{j\_DHFET}$  >>  $T_{j\_HEMT}$  approaching 60% for  $P_{diss}$  > 5W/mm

- → R<sub>TH\_DHFET</sub> < R<sub>TH\_HEMT</sub>

- → Degradation of the PAE observed in the case of DHFET for  $V_{DS} = 25V$  due to the self-heating

#### **IEMN-CNRS**

- o Introduction

- o Challenges and issues for mmW GaN devices

- o Development of SiN/AlN/GaN DHFET

- Importance of the buffer configuration:

C-doped AIN/GaN HEMTs

- Potential advantages of ultrathin "buffer-free"

GaN HEMTs for mmW

- o Conclusion

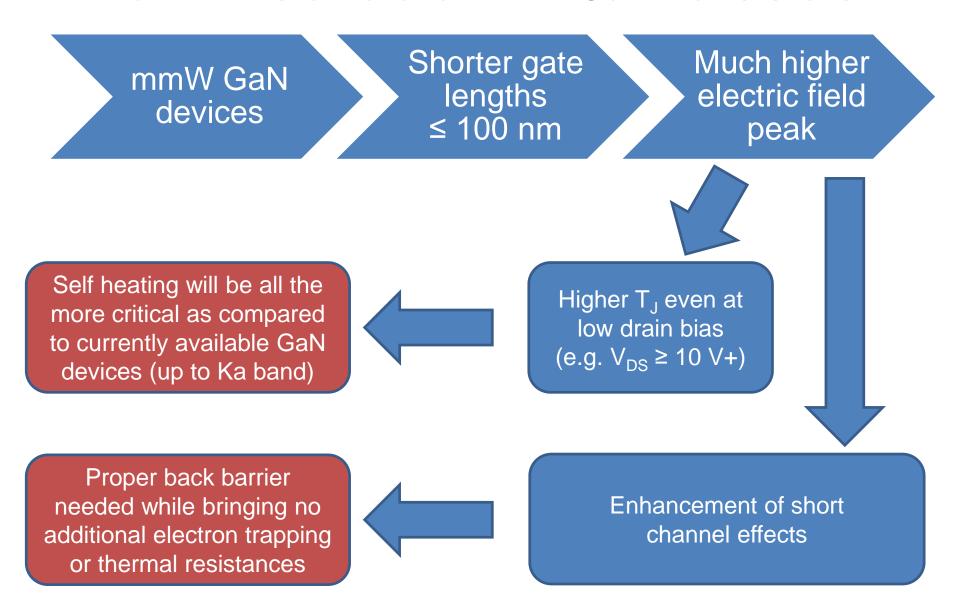

#### Main limits of future mmW GaN transistors

#### Main limits of future mmW GaN transistors

At the epi-level, special care should be given to:

- 1. Thermal dissipation

- Reducing thermal resistances through the transition and buffer layers

- 2. Short channel effects

- Gate-to-channel distance (i.e. ultrathin barriers)

- Proper back barrier

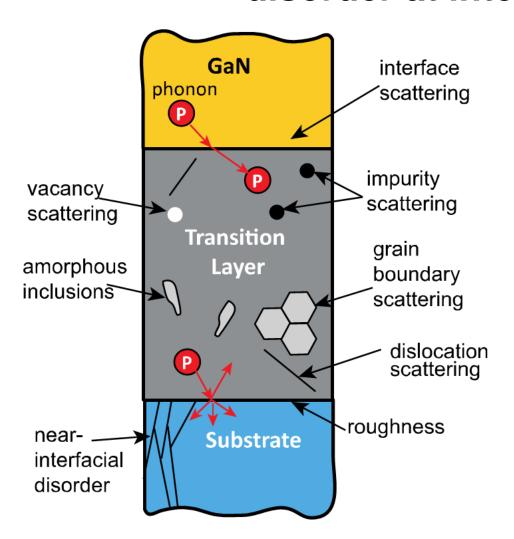

# Thermal resistances associated with material disorder at interfaces

Rather thick transition layers are needed to mitigate the lattice mismatch

Y. Won et al, IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), 2013

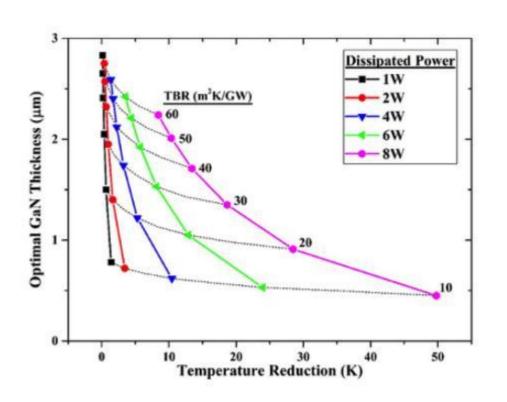

#### Thinner is cooler but...

By thinning the device layer, we can reduce the hotspot temperature of a high-power GaN transistor

Too thin buffers are compromised by performance degradation due to 2DEG properties deterioration and increase of trapping effects

K. Park et al, Appl. Phys. Lett. 109, 151904 (2016)

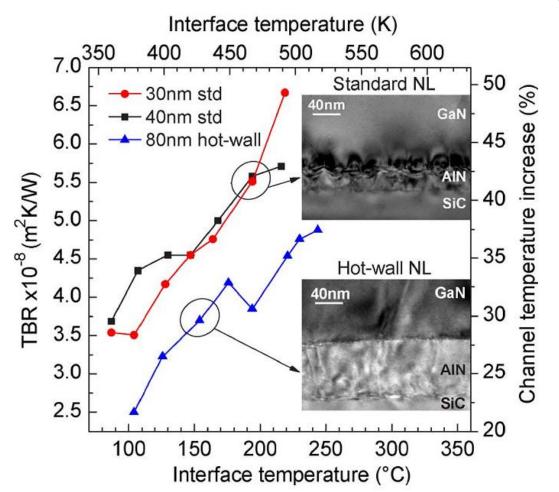

# Thermal-boundary resistance strongly improved with the AIN NL quality

A large part of the channel temperature is due to the NL

Hot-wall MOCVD at Linköping

RIEDEL et al.: Reducing thermal resistance of AlGaN/GaN electronic devices using NLs IEEE Electron Device Lett., Vol. 30, 2009, Bristol's group

### **Current situation with standard HEMTs**

Cap layer

barrier layer

**GaN Channel**

Thick buffer ≥ 1 µm

**Transition layers**

4-inch SiC substrate

- ➤ Manage the strain

- ➤ Keep the 2DEG away from defects / dislocations

But

Many interfaces through rather thick buffer layers => High R<sub>TH</sub>

Theoretically, a thin nucleation layer with an outstanding quality would be enough to accommodate the growth of high quality GaN HEMTs avoiding the use of a complex stack

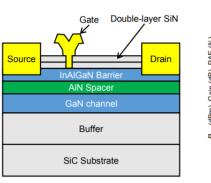

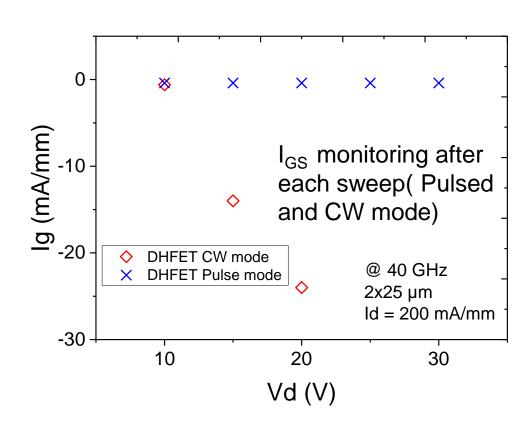

## Potential advantages of GaN ultrathin HEMTs

Total barrier layer barrier layer GaN Channel AIN thin NL

SiC substrate

Ultrathin HEMTs

- Enhancement of the thermal dissipation due to the reduced number of interfaces and high AIN NL quality

- AIN is the ultimate back barrier owing to its ultra-wide bandgap

### **Ultrathin HEMT structure**

Cap GaN (2 nm)

Al<sub>0,29</sub>GaN barrier layer (14 nm)

GaN channel (220 nm)

AIN (≤ 200 nm)

4-inch SiC substrate

State-of-the-art 2DEG properties without buffer layers!

Hall measurements: 1×10<sup>13</sup> cm<sup>-2</sup> 2100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>

**Hot-wall MOCVD**

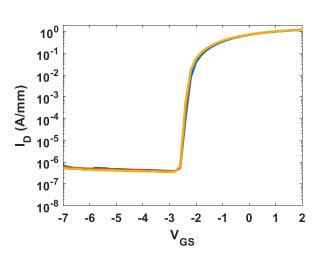

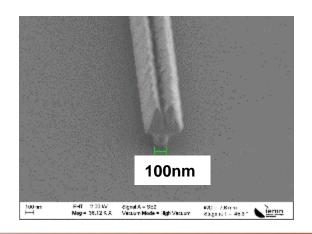

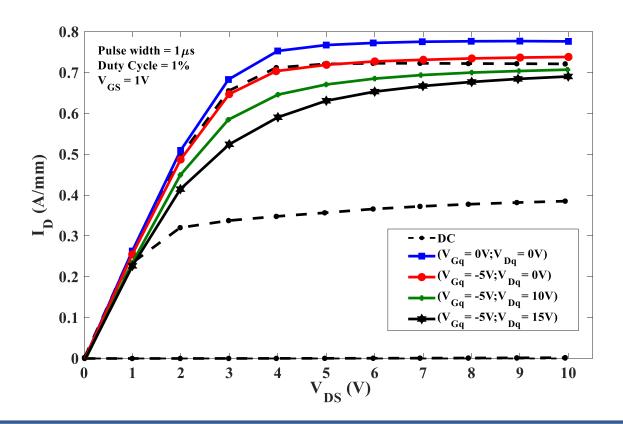

## **DC** characteristics

Gm lower than expected due to non-optimized contact resistances contact but fully functional devices with an off-state leakage current about 20 µA/mm

## **Small signal characterization**

Despite non-optimized ohmic contacts of 0.75 Ω.mm, and a limited extrinsic transconductance (Gm), rather good RF Performances are observed

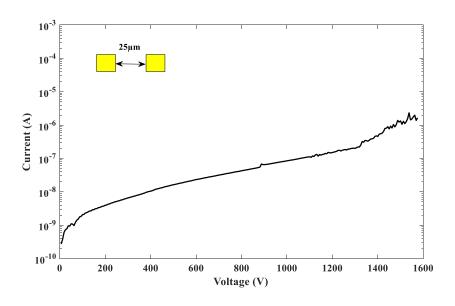

## Breakdown voltage

Claquage Latéral >1600V

Excellent breakdown voltage characteristics (about 70 V / µm), which is as good as standard thick buffer HEMTs

Lateral breakdown on large distance is > 1.5 kV, reflecting the high AIN ultrathin transition layer quality

What about trapping when having the 2DEG so close to the NL?

# **Trapping effects**

Initial pulsed measurements show a trapping level comparable to standard HEMTs (no penalty from the absence of buffer layers)

### **Conclusion**

- Possibility to achieve high breakdown (close to 100 V/μm) under high electric field, with low leakage, and high PAE while using highly scaled sub-10 nm barrier GaN devices

- A critical in-situ SiN cap layer thickness is helpful to enhance the surface robustness resulting in superior device performance and reliability

- Buffer configuration is a key to break the trade-off between electron confinement and self-heating

- Novel ultrathin may be a breakthrough solution for mmW applications

#### Bright future for GaN!

Overcoming all challenges in highly scaled nitrides for breakthrough RF performances up to 100 GHz and above will definitely be achieved!