## New monolithic multi-terminal Si-chips integrating a power converter phase-leg for specific applications

Amirouche Oumaziz, Abdelhakim Bourennane, Frédéric Richardeau

### ▶ To cite this version:

Amirouche Oumaziz, Abdelhakim Bourennane, Frédéric Richardeau. New monolithic multi-terminal Si-chips integrating a power converter phase-leg for specific applications. 28th International Conference Mixed Design of Integrated Circuits and Systems (on-line) June 24-26, 2021, Lodz, POLAND, Jun 2021, Lodz (online), Poland. 10.23919/MIXDES52406.2021.9497636. hal-03286416

## HAL Id: hal-03286416 https://hal.science/hal-03286416

Submitted on 14 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# New monolithic multi-terminal Si-chips integrating a power converter phase-leg for specific applications

Amirouche Oumaziz<sup>(1,2,3)</sup>, Abdelhakim Bourennane<sup>(1)</sup> (1) LAAS-CNRS, University of Toulouse, CNRS, UPS Toulouse, France

*Abstract*— The paper deals with the monolithic integration of a power converter phase leg. It focuses on the integration of a power phase leg consisting of a VDMOS and an IGBT. This association is suitable for monolithic power integration in silicon. Different monolithic chips integrating phase legs were proposed and discussed in this paper. Interesting advantages can be brought by the monolithic integration of the converter phase leg. These advantages include power chips realization simplification, control of gate transistors with respect to constant voltages (DC-link or ground-0V).

*Keywords*—P-IGBT; N-VDMOS; monolithic integration; power conversion; switching cells.

#### I. INTRODUCTION

Currently commercialized conventional power modules are generally realized using 2D hybrid packaging technology in which two-terminal power dies such as IGBT and PiN-diode are soldered on their backside and interconnected using wire bonds. A power module is made of a great number of twoterminal dies that are interconnected by wire bonds. Power modules are therefore bulky and their mass fabrication is limited in productivity. Wire bonds require an expensive wiring operation and are a source of reliability problems [1]-[3]. Moreover, they are a source of stray inductance [4] that limits the operation frequency of the power modules.

In order to overcome these shortcomings, a significant breakthrough can be achieved by an optimized mixed hybrid/monolithic integration of the multi-phase power converters. Different monolithic integration approaches were proposed in literature [5][6]. However, they are either limited in performance due to lateral integration with vertical insulation trenches through the die [5] or require a complex technological process for their realization due to molecular bonding of two silicon wafers [6]. Within the same context, the authors have proposed a vertical quasi-monolithic integration of a multiphase converter called dual-chip approach as well as an ultra-compact single chip approach [7]. From the technology process realization point of view, the proposed multi-terminal chips require the realization of through silicon deep trenches and therefore their realization is complex.

For power conversion applications, the use of P-type power devices is very rare as compared to N-type power devices. This

Frédéric Richardeau<sup>(2,3)</sup> (2) LAPLACE, University of Toulouse, CNRS, INPT, UPS, France 2 rue Charles Camichel, BP 7122, F-31071 Toulouse cedex

is mainly due to the poor on-state characteristics of P-type power devices as compared to their N-type counterparts. However, the association of P-type and N-type transistors, for specific applications, can make easier the monolithic integration in one chip of the phase leg.

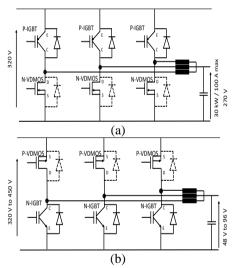

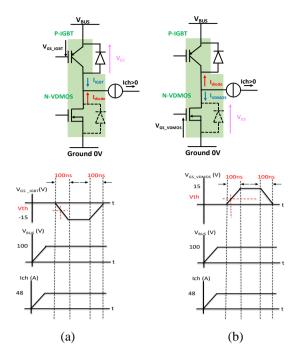

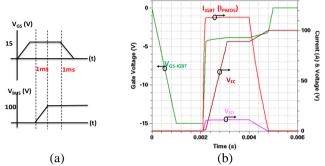

In this paper, new multi-terminal power chips were proposed for monolithic phase leg integration. The integrated phase legs are illustrated in Figure 1. The converter of Figure 1.a is a current reversible DC/DC buck converter while the converter of Figure 1.b is a current reversible DC/DC boost. In the case of Figure 1.a, the phase leg consists of a high side P-IGBT and a low side N-VDMOS. In the case of Figure 1.b, the phase leg consists of a high side N-VDMOS and a low side P-IGBT. In this paper, only on the buck configuration (Figure 1.a) was studied..

Figure 1 : Converter leg typical applications for the DC/DC buck converter (a) and the DC/DC boost converter (b)

The converters components are placed (high-side or lowside) according to their type (unipolar or bipolar), so that the power losses would be always minimum for a given duty cycle. More specifically, the configurations exploit the conductivity modulation principle of bipolar components to reduce the power losses. For instance, for a 0.8 duty cycle, in order to optimize the power losses in the buck configuration (Figure 1.a), the bipolar transistor will be conducting 80 % of the time and the N-VDMOS the complement (20 %). The same principle applies for the boost configuration (Figure 1.b). This time, in order to reduce the power losses, a 0.2 duty cycle will be affected to the high-side unipolar transistor (P-VDMOS), while the low-side N-IGBT will beconducting 80 % of the time.

The monolithic architectures and the operating modes of the multi-terminal chips were validated through mixed-mode Sentaurus<sup>TM</sup> 2D-numerical simulations.

#### II. PRINCIPLE OF THE APPROACH

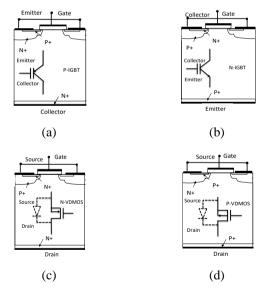

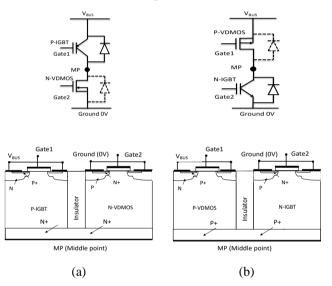

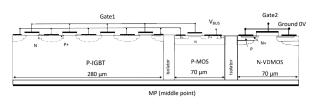

The 2D cross sectional views of a P-IGBT, N-IGBT, P-VDMOS and N-VDMOS are summarized in Figure 2. In the proposed buck converter topology (Figure 1.a), one can notice that the N<sup>+</sup> back-side region is the same in the high side P-IGBT and in the low-side N-VDMOS. By mutualizing this backside N<sup>+</sup> regions, the monolithic chip of Figure 3.a is proposed. It consists of a vertical N-VDMOS and a vertical P-IGBT separated by deep but not through silicon trenches [7]. This latter can be filled by an insulator [8]-[9].

The same principle applies for the proposed boost converter topology (Figure 1.b). Noticing the same P<sup>+</sup> backside regions for the high side P-VDMOS and the low side N-IGBT, these could be associated. By mutualizing this backside P<sup>+</sup> regions, the monolithic chip of Figure 3.b is proposed. It consists of a vertical P-VDMOS and a vertical N-IGBT separated by deep but not through silicon trenches that can be filled by an insulator.

Figure 2 : P-IGBT (a), N-IGBT (b), P-VDMOS (c) and N-VDMOS (d) topologies.

#### III. CHIPS DESIGN

For the sake of illustration, the monolithic chip integrating a phase leg of Figure 4 is designed to support a blocking voltage of 100 V and carry out a nominal current of 48A. The chosen rated voltage (100 V) is a design example. Designs at higher

voltages are possible by following the procedure described here after.

The design starts first by estimating the drift regions doping concentration and thickness of each device separately (P-IGBT and N-VDMOS) that allow to withstand the rated (100 V) voltage. The on-state static I(V) characteristics of each device is used to determine the on-sate current density  $J_{VDMOS}$  and  $J_{IGBT}$  and voltage drop that limits power losses to 50 W.cm<sup>-2</sup>.

Assuming a monolithic chip area of  $1 \text{ cm}^2$ , and knowing each transistor's current density, the total rated current  $I_{tot}$  is determined using equation (1).

$$I_{tot} = \frac{S_{tot}}{\frac{1-\alpha}{J_{VDMOS}} + \frac{\alpha}{J_{IGBT}}}$$

(1)

Where  $\alpha$  represents the duty cycle,  $S_{tot}$  the chip surface (1 cm<sup>2</sup>) and  $J_{VDMOS}$ ,  $J_{IGBT}$  the N-VDMOS and P-IGBT current densities. Once the rated current is determined, each transistor occupied surface is then calculated using (2) and (3).

Figure 3 : Cross-sectional view of the proposed monolithic chip integrating the phase leg P-IGBT (high side) and N-VDMOS (low side) (a), N-IGBT (low side) and P-VDMOS (high side) (b).

$$J_{VDMOS} \times S_{VDMOS} = I_{tot} (1-\alpha) (2)$$

$$J_{IGBT} \times S_{IGBT} = I_{tot} (\alpha) (3)$$

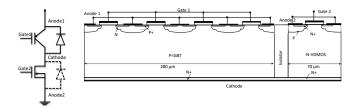

As a design application, Figure 4 shows a P-IGBT and N-VDMOS monolithic structure integration, where a 0.8 duty cycle ( $\alpha$ ) is used. The 2D mixed mode simulation of the monolithically integrated structure requires the use of the same components depth (area factor). Consequently, four IGBT cells and one VDMOS cell are used to reach the required devices areas at the designed rated current density, with respect to power losses constraint. This monolithic integration increases the onstate voltage of the N-VDMOS due to the required P-IGBT thickness to support the rapplied voltage (100 V),.

Figure 4 : Designed P-IGBT and N-VDMOS phase leg with duty cycle 0.8, 100 V bus voltage and 48A rated current

#### IV. SENTAURUS<sup>TM</sup> MIXED-MODE SIMULATIONS RESULTS

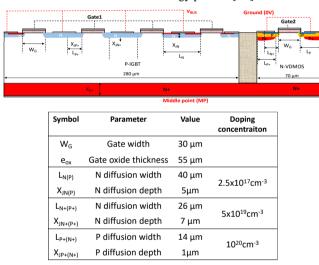

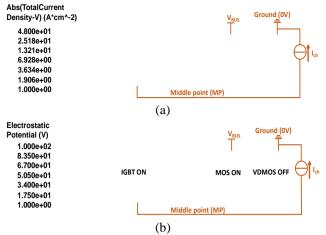

The main physical and geometrical parameters of the diffused regions used in the IGBT and VDMOS sections are those set by the IGBT process-flow of the micro and nanotechnology platform at LAAS-CNRS (Table 1). The drift regions thickness and concentration are chosen so the that the devices are able to withstand 100 V. The simulation conditions correspond to a static state, when one diagonal section of the half H-bridge is in on-state, the other is in off-state. A current source of 48 A simulates an inductive load. Both presented architectures (Figure 3) are simulated using the circuits configurations shown in Figure 5.

Table 1 :Main Physical and geometrical parameters of the LAAS-CNRS IGBT-Technology process [10].

Figure 5 : Simulated architectures and control signals used for simulations.

Mixed-mode 2D simulations using Sentaurus<sup>TM</sup> were carried out to validate the architecture in boost converter circuit. The results of the simulated structure under short switching time (100 ns) are presented below.

#### A. P-IGBT switching

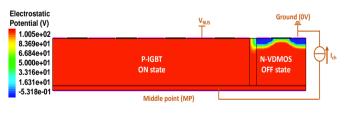

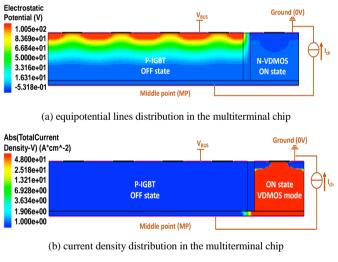

Figure 6 and Figure 7 show simulation results on the P-IGBT conduction and blocking capabilities. During P-IGBT conduction (Figure 6.a and Figure 6.b), N-VDMOS reverse biased junction P/N- supports the applied voltage. When the P-IGBT's threshold voltage is reached through  $V_{GS-IGBT}$  (green curve) increasing voltage, its current starts to increase (Figure 7.a), until the forward recovery phenomenon is completed. Subsequently, the voltage across the component ( $V_{EC}$ , purple curve) decreases to reach the on-state drop voltage (0.91 V). During this time, the voltage.

(a) equipotential lines distribution in the multiterminal chip

(d) current density distribution in the multiterminal chip

Figure 6: Equipotential lines distribution and current density distribution in the multi-terminal chip: P-IGBT on-state and NVDMOS in off-state (Leakage current:  $0.2 \mu A$ ) (a-b); and NVDMOS on-state and P-IGBT in off-state (Leakage current:  $94 \mu A$ ) (c-d).

The P-IGBT turn-off phase (Figure 7.b) begins with a voltage switching across the component ( $V_{EC}$ , purple curve), to reach to DC-bus voltage where the component withstands the rated voltage (100 V) thanks to the reverse biased N/P- junction (Figure 6.c). Then, the P-IGBT current decreases to zero. Simultaneously, the current through the N-VDMOS increases, meaning the component's body diode is in on-state (Figure 6.d).

#### B. N-VDMOS switching

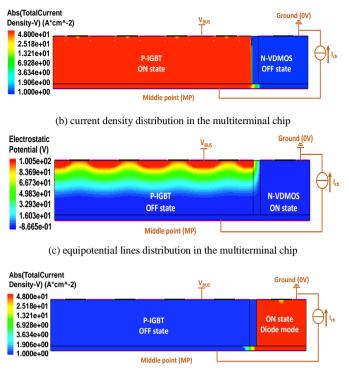

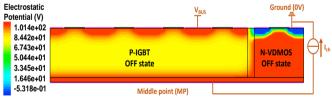

During N-VDMOS conduction (Figure 9.a), the P-IGBT reverse biased junction N/P- withstands the DC-bus (Figure 8.a) voltage. Once the threshold voltage is reached, the current starts to increase in the VDMOS structure, until the forward recovery phenomenon is complete (Figure 8.b). Then voltage across the drain source ( $V_{DS}$ ) decreases to reach an on-state voltage of 2.1 V. At the same time, the P-IGBT anti-parallel freewheeling diode voltage increases and supports the applied DC-bus voltage.

Once the N-VDMOS turn-off phase begins (Figure 9.b ), the voltage across drain source rises ( $V_{DS}$ ), until the reverse recovery phenomenon is complete. When the component turn-off is completed, the freewheeling diode is in on-state, where the VDMOS supports the DC-bus voltage (Figure 8.c).

Figure 7 :P-IGBT turn-on (a) and turn-off (b) switching waveforms.

(c) equipotential lines distribution in the multiterminal chip

Figure 8 :Equipotential lines distribution and current density distribution in the multi-terminal chip: NVDMOS on-state and P-IGBT in off-state (Leakage current: 0.3  $\mu$ A) (a-b): and P-IGBT freewheeling diode on-state and NVDMOS in off-state (Leakage current: 0.2  $\mu$ A) (c).

Figure 9:N-VDMOS turn-on (a) and turn-off (b) switching waveforms.

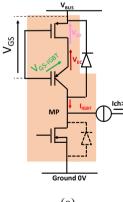

#### C. P-IGBT current limitation

To limit the P-IGBT current under short circuit occurrence, a low voltage depletion mode P-channel-MOS transistor is added in series with the vertical P-IGBT as shown in Figure 10. This transistor limits the current through the P-IGBT and provides P-IGBT's gate-depolarization, its desaturation current limitation and then prevents the component's latch-up under short-circuit conditions. Sentaurus<sup>TM</sup> simulation results illustrate the impact of the addition of the P-MOS transistor on the I(V) characteristics of the high-side part of the phase leg.

(b)

Figure 10 : Improved P-IGBT structure against latch-up phenomena during short-circuit using a depletion mode P-MOS transistor

Figure 11: A combined P-IGBT/P-MOS structure switching waveforms obtained using mixed mode simulation in a short-circuit case.

When the short-circuit is initiated (Figure 11, green zone), both current and voltages across the transistors rise until saturation of the P-MOS is reached, according to the designed saturation current of the P-MOS. During the short-circuit (Figure 11, orange zone), the components support the DC-bus voltage (V<sub>BUS</sub>=100 V). The IGBT withstands 90 V and the P-MOS supports the difference. The on-state voltage drop across the P-MOS increases, which leads to a decrease in the P-IGBT gateemitter voltage (V<sub>GS-IGBT</sub>, green curve). As a result, the current through the P-IGBT is maintained at the P-MOS saturation current (~115 A), which is lower than lath-up current and higher than rated current (48 A). When the transistors gates control signal ( $V_{GS}$ ) is decreased to zero (Figure 11, blue zone), the current through the components decreases. Once the transistors switch off, the P-IGBT supports the DC-bus voltage (100 V). Equipotential and current density lines distribution in the integrated monolithic structure comprising the three components (IGBT, VDMOS and P-MOS) during IGBT onstate are shown in Figure 12. During IGBT conduction (Figure 12.a), the VDMOS reverse biased junction P<sup>+</sup>/N- withstands (Figure 12.b) the DC bus voltage (100 V). The IGBT on-state voltage drop remains the same (0.91 V).

Figure 12 : Current density distribution (a) and equipotential lines distribution (b) in the multi-terminal chip: P-IGBT & P-MOS on-state and N-VDMOS in off-state.

#### V. CONCLUSION

In this paper, original monolithic chips integrating converter phase legs were proposed. From the technology process realization point of view, these multi-terminal chips do not require the realization of through silicon deep trenches [6] and therefore their realization is not complex. The operating modes of the chips were validated in a buck converter application using Sentaurus<sup>™</sup> mixed-mode simulations. 2D The design approaches were illustrated and validated in an a 100V, 48A application. An improved version of the multi-terminal chip was proposed. It uses a depletion mode P-MOS transistor in series with the P-IGBT in order to limit the current through this latter mainly in the case of a short-circuit condition and therefore prevents P-IGBT latch-up.

#### REFERENCES

- B. Weiss et al., "Operation of PCB-Embedded, High Voltage Multilevel-Converter GaN-IC," 2017 IEEE 5<sup>th</sup> Workshop on Wide Bandgap Devices and Applications (WiPDA), Albuquerque, NM,2017,pp. 398-403. doi: 10.1109/WiPDA.2017.8170580

- [2] S. QiN et al., "A High-Power-Density Power Factor Correction Front End Based On Seven-Level Flying Capacitor Multilevel Converter," *in IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 3, pp. 1883-1898, Sept. 2019. doi: 10.1109/JESTPE.2018.2865597

- [3] S. Li, L. M. Tolbert, F. Wang and F. Z. Peng, "Stray Inductance Reduction of Commutation Loop in the P-cell and N-cell-Based IGBT Phase Leg Module," in *IEEE Transactions on Power Electronics*, vol.29, no.7, pp.3616-3624, July2014. doi: 10.1109/TPEL.2013.2279258

- [4] A. K. Solomon, A. Castellazzi, N. Delmonte and P. Cova, "Highly integrated low-inductive power switches using double-etched substrates with through-hole viases," *International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, Hong Kong, 2015, pp. 329-332. doi: 10.1109/ISPSD.2015.7123456

- [5] D. W. Green and E. M. Sankara Narayanan, "Fully Isolated High Side and Low Side LIGBTs in Junction Isolation Technology,", *ISPSD*, Naples, 2006, pp. 1-4. doi: 10.1109/ISPSD.2006.1666111

- [6] L. Benaissa, N. Rouger, J. Widiez, JC. Crébier, J. Dafonseca, D. Lafond, V. Gaude, K. Vladimirova, "A vertical power device conductive assembly at wafer level using direct bonding technology,", *ISPSD*, Bruges, 2012, pp. 77-80.

- [7] A. El Khadiry, A. Bourennane and F. Richardeau, "Multiphase Power Converter Integration in Si: Dual-Chip and Ultimate Monolithic Integrations," in *IEEE Transactions on Electron Devices*, vol. 63, no. 5, pp. 1977-1983, May 2016. doi: 10.1109/TED.2016.2537212

- [8] L. Theolier, H. Mahfoz-Kotb, K. Isoird, F. Morancho, S. Assie-Souleille and N. Mauran, "A New Junction Termination Using a Deep Trench Filled With BenzoCycloButene," in *IEEE Electron Device Letters*, vol. 30, no. 6, pp. 687-689, June 2009. doi: 10.1109/LED.2009.2020348

- [9] Chanho Park, Jinmyung Kim, Taehoon Kim and D. J. Kim, "Deep trench terminations using ICP RIE for ideal breakdown voltages," *ISPSD*, 2003, pp. 199-202. doi: 10.1109/ISPSD.2003.1225263

- [10] E. Imbernon et al., "Flexible technological process for functional integration" Int. Semicond. Conf. (CAS'2001)