### Impact of channel length on the operation of junctionless transistors with substrate biasing

Dae-Young Jeon, Mireille Mouis, Sylvain Barraud, Gérard Ghibaudo

### ▶ To cite this version:

Dae-Young Jeon, Mireille Mouis, Sylvain Barraud, Gérard Ghibaudo. Impact of channel length on the operation of junctionless transistors with substrate biasing. IEEE Transactions on Electron Devices, 2021, 68 (6), pp.3070-3073. 10.1109/TED.2021.3069936. hal-03194757

HAL Id: hal-03194757

https://hal.science/hal-03194757

Submitted on 29 Aug 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Impact of channel length on the operation of junctionless transistors with substrate-biasing

Dae-Young Jeon, Mireille Mouis, *Senior Member, IEEE*, Sylvain Barraud and Gérard Ghibaudo, *Fellow, IEEE*

Abstract—Junctionless transistors (JLTs) have promising advantages such as structural simplicity without PN-junctions and bulk conduction-based operation for the realization of advanced CMOS technologies. Here, channel length dependence on the operation of JLTs with substrate-biasing  $(V_{gb})$  was investigated in detail. Parasitic series resistance  $(R_{sd})$  was noticeably decreased as increasing  $V_{gb}$ . In addition, transconductance  $(g_m)$ , its derivative  $(dg_m/dV_{gf})$  and on-drain current  $(I_{on})$  in a short-channel JLT were significantly affected by the  $V_{gb}$ -modulated  $R_{sd}$  with charge coupling effects. This work provides important information for better understanding and true estimation of intrinsic JLT performance, for practical applications based on polycrystalline Si, III-V semiconductors and TMDs nano-materials as well as advanced logic devices.

Index Terms—Junctionless transistors (JLTs), substrate-biasing effect, channel length dependence, series resistance ( $R_{sd}$ ), electrical parameters modulated by substrate bias.

#### I. INTRODUCTION

tructural simplicity without PN-junctions of junctionless transistors (JLTs) is the most promising advantage for the realization of sub-5 nm complementary metal-oxide-semiconductor (CMOS) technologies [1-5].

The junctionless architecture with uniformly doped source (S), channel and drain (D) enables no need of precise gate-alignment and abrupt S/D junction formation with a low-thermal-budget [3-5]. Bulk conduction-based operation in JLTs also results in better reliability, lower 1/f noise and less mobility degradation against transverse electric-field (E-field)

This work was supported by European Union 7th Framework Program project SQWIRE under grant agreements No. 257111 and the National Research Foundation of Korea (NRF-2017M3A7B4049167).

D.-Y. Jeon is with Institute of Advanced Composite Materials, Korea Institute of Science and Technology, Joellabuk-do 55324, South Korea (e-mail: dyjeon@kist.re.kr).

M. Mouis and G. Ghibaudo are with IMEP-LAHC, Grenoble INP, Minatec, BP 257, 38016 Grenoble, France.

S. Barraud is with CEA-LETI Minatec, 17 rue des Martyrs, 38054 Grenoble, France.

[6-9]. In addition, JLTs in a variety of materials, including polycrystalline silicon (Si), III-V semiconductors and 2-dimentional (2D) transition metal dichalcogenides (TMDs), have been reported for high performance thin-film transistors (TFTs), 3D vertical transistors, sensors and multi-functional devices with excellent short-channel characteristics [10-14].

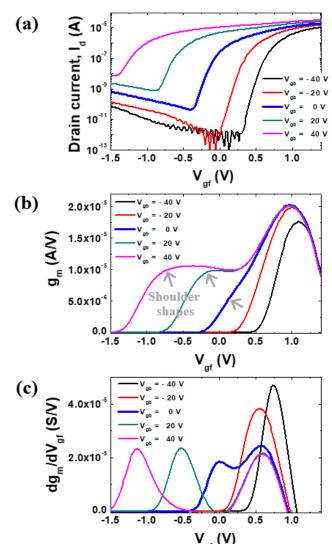

Fig. 1. (a) Transfer curves, (b) transconductance  $(g_m)$  and (c) derivative of  $g_m$   $(dg_m/dV_{gf})$  measured from a very long channel JLT of  $L_m=10~\mu m$  with varying  $V_{gb}.$  The device was biased in the linear operation-regime with drain voltage  $V_d=50~mV.$

## Author version – Original paper published in IEEE Transactions on Electron Devices, Vol. 68, Issue 6, pp. 3070-3073, doi: 10.1109/TED.2021.3069936 (June 2021). HAL reference: hal-03194757

Silicon-on-insulator (SOI) technology based JLTs can be operated by both front-gate and back-gate [15,16]. In-depth studies about substrate-biasing effects and charge coupling between front and back interfaces are very important for optimizing performance and better understanding operation mechanism of JLTs.

In this paper, channel length dependent substrate-biasing effects on the operation of JLTs were investigated in detail. Parasitic series resistance ( $R_{sd}$ ) of JLTs was noticeably modulated by the substrate bias. Transconductance ( $g_m$ ), its derivative ( $dg_m/dV_{gf}$ ) and effective mobility in a short-channel JLT were significantly affected by the substrate-bias-controlled  $R_{sd}$  with charge coupling effects between front and back interfaces.

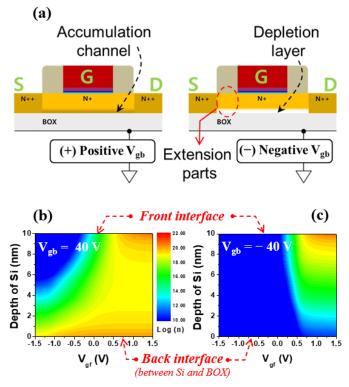

Fig. 2. (a) Schematic architecture of JLT describing the accumulated charge carriers at back interface for positive  $V_{gb}$ , and the depletion of charge carriers due to negative  $V_{gb}$ . Simulated distribution of electron carrier concentration per unit volume (n) along the depth of device Si varying  $V_{gf}$  with different  $V_{gb}$ , (b)  $V_{gb} = 40 \text{ V}$  and (c)  $V_{gb} = -40 \text{ V}$ .

#### II. EXPERIMENTS

JLTs with device Si  $\approx$  10 nm and high-k dielectric  $\approx$  1.2 nm were fabricated on (100) SOI wafers with thick buried oxide (BOX)  $\approx$  145 nm. Channel of JLTs was highly doped with

phosphorus, and effective doping concentration was estimated as  $\approx 5 \times 10^{18} / \text{cm}^3$ . An additional S/D implantation was also performed to reduce access resistance. Further detail information with respect to fabrication and material parameters was described in previous works [17]. Electrical characteristics were measured by using HP 4155A semiconductor parameter analyzer, and simulated results were obtained by FlexPDE software, which is a numerical solver based on scripted finite element models.

#### III. DISCUSSION

The bold blue plots as shown in Fig.1 show transfer curve, transconductance  $(g_m)$  and derivative of  $g_m$   $(dg_m/dV_{gf})$ , where V<sub>gf</sub> means front-gate voltage), obtained from a very long channel JLT ( $L_m = 10 \mu m$ ) with back-gate voltage (substrate bias)  $V_{gb} = 0V$ . Shoulder shape on the  $g_m$  and two clear peaks on the  $dg_{\text{m}}\!/dV_{\text{gf}}$  in JLTs represent unique electrical properties based on both bulk neutral and surface accumulation conductions, which is very different from the operation of conventional inversion-mode (IM) transistors [8,17]. The first (left-hand side) and second peak (right-hand side) on dg<sub>m</sub>/dV<sub>gf</sub> denote conduction threshold voltage (V<sub>th</sub>) and flat-band voltage (V<sub>fb</sub>), i.e. threshold of accumulation conduction channel, respectively. The shoulder shape on  $g_m$  is also strongly associated with the amount of charge carriers on the operation at  $V_{gf} = V_{fb}$  condition. As  $V_{gb}$  decreased, the shoulder shrunk in Fig. 1(b) and the two peaks merged as a single peak in Fig. 1(c), due to the effectively reduced bulk channel thickness resulted from the negative V<sub>gb</sub>-induced depletion of free charge carriers at back interface between device Si and BOX [18]. On the other hand, bulk neutral channel of JLTs can be early turned on, and additional accumulation channel is newly created at the back interface with a positive V<sub>gb</sub>. Those gave rise to the pronounced shoulder shape in Fig. 1(b) and left-shift of the first peak in Fig. 1(c), as  $V_{gb}$  increased.

Figure 2 shows the simulated substrate-biasing characteristics of JLTs. The distribution of electron carrier concentration per unit volume (n) along the depth of device Si was visualized by varying  $V_{gf}$  with different  $V_{gb}$ . One can clearly identified the shrunk bulk channel with negative  $V_{gb}$ , and the early turned-on

## Author version – Original paper published in IEEE Transactions on Electron Devices, Vol. 68, Issue 6, pp. 3070-3073, doi: 10.1109/TED.2021.3069936 (June 2021). HAL reference: hal-03194757

bulk channel with the newly accumulated carriers for positive  $V_{gb}$ . Indeed, a depletion layer in blue color was observed at back interface for  $V_{gb} = -40 \text{ V}$  in Fig. 2(c), while an additional accumulation layer in red or orange color was created at the back interface for  $V_{gb} = 40 \text{ V}$  in Fig. 2(b).

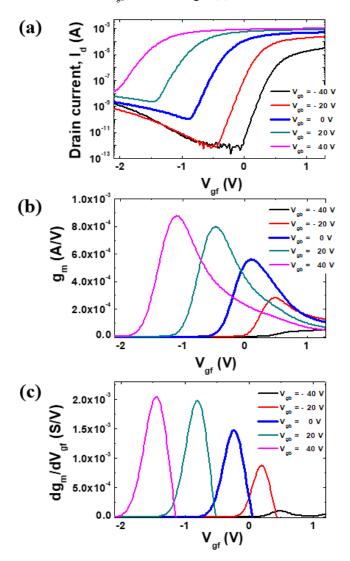

Fig. 3. (a) Transfer curves, (b) transconductance  $(g_m)$  and (c) derivative of  $g_m$   $(dg_m/dV_{gf})$  measured from a very short channel JLT of  $L_m$  = 40 nm with varying  $V_{gb}$ . The device was biased in the linear operation-regime with drain voltage  $V_d$  = 50 mV.

Completely different substrate-biasing behaviors were investigated in JLTs with a very short channel length ( $L_m = 40$  nm), as shown in Fig. 3. A shoulder shape was not observed any more in Fig. 3(b), and only a single peak was shown in Fig. 3(c), since the parasitic series resistance ( $R_{sd}$ ) considerably affects the short-channel JLTs characteristics [19,20]. In addition, the on-drain current ( $I_{on}$ ,  $V_{gf} > 1.0$  V) in Fig. 3(a) was

dramatically changed by varying  $V_{gb}$ , as compared to that of the long channel JLT in Fig. 1(a). The  $g_m$  in Fig. 3(b) was also getting noticeably degraded as decreasing  $V_{gb}$ . The variation of  $V_{gb}$  could have an effect on the value of  $R_{sd}$ , and the  $R_{sd}$  modulated by  $V_{gb}$  could affect overall results related to substrate-biasing in the short channel JLTs.

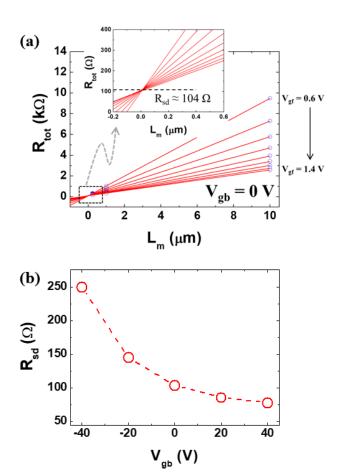

$V_{gb}$  controlled  $R_{sd}$  of JLTs was estimated by using transfer length method (TLM) in Fig. 4. Total resistance ( $R_{tot}$ ) including JLT channel resistance ( $R_{ch}$ ) and  $R_{sd}$  can be calculated as [21]:

$$R_{tot} = R_{ch} + R_{sd} = \rho_{ch} \times \frac{L_m - \Delta L}{W_m} + R_{sd}$$

(1)

where  $\rho_{ch},~\Delta L$  and  $W_m$  are channel sheet resistance, channel length reduction and on-mask channel width, respectively. The clear common intersection point of the linear fitted lines on the accumulation operation regime  $(V_{gf} > V_{fb})$  successfully determined  $R_{sd} \approx 104~\Omega$  for  $V_{gb} = 0V,$  as shown in Fig. 4(a).

Fig. 4. (a) Total resistance ( $R_{tot}$ ) versus channel lengths ( $L_m = 250$  nm, 1  $\mu m$  and 10  $\mu m$ ) with varying  $V_{gf}$ , for determination of series resistance ( $R_{sd}$ ). The inset shows a clear common intersection of the linear fitted lines. (b) Extracted  $R_{sd}$  modulated by  $V_{gb}$ .

Finally,  $V_{gb}$  dependent  $R_{sd}$  was plotted in Fig. 4(b) after the same procedure for  $R_{sd}$  extraction with different  $V_{gb}$  from -40 V to 40 V. Indeed,  $R_{sd}$  was decreasing for positive  $V_{gb}$ , while it was increasing when applying negative  $V_{gb}$ . Accumulated charge carriers at back interface for positive  $V_{gb}$  reduces resistance of the extension parts ( $R_{ext}$ ), as illustrated in Fig. 2(a).  $R_{ext}$  can be also enhanced by the depletion of charge carriers due to negative  $V_{gb}$ . Similar trend of the substrate-bias affected  $R_{sd}$  have been also reported in SOI based transistors with lightly doped drain (LDD) [22].

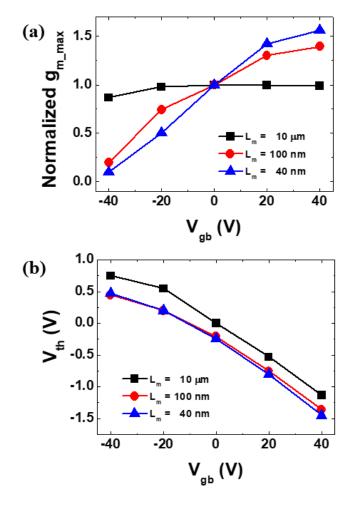

Fig. 5. (a) Normalized  $g_{m\_max}$  [i.e. maximum- $g_m(V_{gb})$ /maximum- $gm(V_{gb}=0\ V)$ ] versus  $V_{gb}$ , with different JLT lengths. (b) Threshold voltage  $(V_{th})$  as a function of  $V_{gb}$  with different JLT lengths, the  $V_{th}$  was extracted from the first peak in the  $dg_m/dV_{gf}$  plots.

Figure 5(a) shows the normalized  $g_{m\_max}$  [i.e. maximum- $g_m(V_{gb})$ /maximum- $g_m(V_{gb} = 0 \text{ V})$ ] versus  $V_{gb}$ , with different JLT lengths. It should be noted that the trend of  $g_m$  is closely related to characteristics of field-effect mobility

behaviors [23]. There was a slight decrease in the normalized  $g_{m\_max}$  of long length JLT (L  $_m$  = 10  $\mu m)$  as decreasing  $V_{gb}.$  This feature is attributed to the lower mobility at the top interface, since the high-k dielectric (HfSiON) for top-gate insulator has poorer interface-properties than that in pure thermal oxide (SiO<sub>2</sub>) of BOX at the back interface [15-17]. However, the variation of  $V_{gb}$  significantly changed the normalized  $g_{m\_max}$  in JLTs with  $L_m = 40$  nm. The increased value of  $R_{sd}$  at a negative  $V_{\mbox{\scriptsize gb}}$  caused the dramatically enhanced degradation of  $g_{\mbox{\scriptsize m}}$  and field-effect mobility in the short channel JLTs. Moreover, the threshold voltage (V<sub>th</sub>) extracted from the first peak in the  $dg_m/dV_{gf}$  plots was plotted as a function of  $V_{gb}$  as shown in Fig. 5(b). As decreasing length of JLTs with a same  $V_{\text{gb}}$ ,  $V_{\text{th}}$  was reduced due to short-channel effects [17]. Whereas the variation rate of  $V_{th}$  against  $V_{gb}$  changes was very similar regardless of JLT lengths. Interestingly, this means that substrate-biasing impact on the operation near V<sub>th</sub> regime is independent of channel-length variation in JLTs.

#### IV. CONCLUSIONS

The operation of junctionless transistors (JLTs) with substrate-biasing (V<sub>gb</sub>) has been investigated, and its channel length dependence was also discussed in detail. A shoulder shape on transconductance (g<sub>m</sub>) and clear two peaks on derivative of  $g_m$  ( $dg_m/dV_{gf}$ ) were observed in a long-channel  $(L_{\text{m}}$  = 10  $\mu\text{m})$  JLT with  $V_{\text{gb}}$  = 0V, since JLTs have both bulk neutral and surface accumulation conduction channels. The shoulder shape shrunk and the two peaks merged as a single peak when applying negative  $V_{\rm gb}$ . For positive  $V_{\rm gb}$ , the shoulder shape was pronounced and the first peak on the  $dg_m/dV_{\rm gf}$  moved to the left-hand side. Completely different features (no shoulder shape on g<sub>m</sub> and only a single peak on  $dg_m/dV_{gf}$ ) were investigated in a very short-length ( $L_m = 40 \text{ nm}$ ) JLT due to parasitic series resistance (R<sub>sd</sub>) effect. The R<sub>sd</sub> was noticeably decreased as increasing V<sub>gb</sub>, and this gave rise to the dramatical changes on-drain current (Ion) and field-effect mobility of the short-channel JLTs against the variation of V<sub>gb</sub>. However, substrate-biasing impact on the operation near V<sub>th</sub> regime was similar regardless of JLT lengths. Further calibration with the experimental data and stronger coupling

## Author version – Original paper published in IEEE Transactions on Electron Devices, Vol. 68, Issue 6, pp. 3070-3073, doi: 10.1109/TED.2021.3069936 (June 2021). HAL reference: hal-03194757

effects in ultra-thin body and buried oxide (UTBB) structures will be our future works [24,25].

#### REFERENCES

- [1] J.-P. Colinge, et al., "Nanowire transistors without junctions," Nature nanotechnology, vol. 5, pp. 225-229, 2010, doi: 10.1038/nnano.2010.15.

- [2] A. M. Ionescu, "Nanowire transistors made easy," Nature nanotechnology, vol. 5, pp. 178-179, 2010, doi: 10.1038/nnano.2010.38.

- [3] A. Veloso, et al., "Gate-all-around NWFETs vs. triple-gate FinFETs: Junctionless vs. extensionless and conventional junction devices with controlled EWF modulation for multi-VT CMOS," in 2015 Symposium on VLSI Technology (VLSI Technology), 2015, pp. T138-T139, doi: 10.1109/VLSIT.2015.7223652.

- [4] A. Veloso, et al., "Junctionless versus inversion-mode lateral semiconductor nanowire transistors," Journal of Physics: Condensed Matter, vol. 30, p. 384002, 2018, doi: 10.1088/1361-648X/aad7c7.

- [5] S. Deleonibus, Emerging Devices for Low-power and High-performance Nanosystems: Physics, Novel Functions, and Data Processing: CRC Press, 2018.

- [6] J.-P. Colinge, et al., "Reduced electric field in junctionless transistors," Applied Physics Letters, vol. 96, p. 073510, 2010, doi: 10.1063/1.3299014.

- [7] S. J. Park, et al., "Less mobility degradation induced by transverse electric-field in junctionless transistors," Applied Physics Letters, vol. 105, p. 213504, 2014, doi: 10.1063/1.4902549.

- [8] D.-Y. Jeon, et al., "Low-temperature operation of junctionless nanowire transistors: Less surface roughness scattering effects and dominant scattering mechanisms," Applied Physics Letters, vol. 105, p. 263505, 2014, doi: 10.1063/1.4905366.

- [9] D.-Y. Jeon, et al., "Low-frequency noise behavior of junctionless transistors compared to inversion-mode transistors," Solid-State Electronics, vol. 81, pp. 101-104, 2013, doi: 10.1016/j.sse.2012.12.003.

- [10] D.-R. Hsieh, et al., "Comprehensive analysis on electrical characteristics of Pi-Gate poly-Si Junctionless FETs," IEEE Transactions on Electron Devices, vol. 64, pp. 2992-2998, 2017, doi: 10.1109/TED.2017.2704933.

- [11] P. Razavi and G. Fagas, "Electrical performance of III-V gate-all-around nanowire transistors," Applied Physics Letters, vol. 103, p. 063506, 2013, doi: 10.1063/1.4817997.

- [12] W. Cao, et al., "Junction-Less Monolayer MoS2 FETs," arXiv preprint arXiv:1509.00561, 2015.

- [13] S. M. Kim, et al., "Device characterization and design guideline of amorphous InGaZnO junctionless thin-film transistor," IEEE Transactions on Electron Devices, vol. 64, pp. 2526-2532, 2017, doi: 10.1109/TED.2017.2696048.

- [14] Y. M. Georgiev, et al., "Fully CMOS-compatible top-down fabrication of sub-50 nm silicon nanowire sensing devices," Microelectronic engineering, vol. 118, pp. 47-53, 2014, doi: 10.1016/j.mee.2013.12.031.

- [15] S. J. Park, et al., "Back biasing effects in tri-gate junctionless transistors," Solid-State Electronics, vol. 87, pp. 74-79, 2013, doi: 10.1016/j.sse.2013.06.004.

- [16] T. Rudenko, et al., "Experimental study of transconductance and mobility behaviors in ultra-thin SOI MOSFETs with standard and thin buried oxides," Solid-State Electronics, vol. 54, pp. 164-170, 2010, doi: 10.1016/j.sse.2009.12.014.

- [17] D.-Y. Jeon, et al., "Revisited parameter extraction methodology for electrical characterization of junctionless transistors," Solid-State Electronics, vol. 90, pp. 86-93, 2013, doi: 10.1016/j.sse.2013.02.047.

- [18] D.-Y. Jeon, et al., "Controlling the Effective Channel Thickness of Junctionless Transistors by Substrate Bias," IEEE Transactions on Electron Devices, vol. 67, pp. 4736-4740, 2020, doi: 10.1109/TED.2020.3020284.

- [19] D.-Y. Jeon, et al., "Impact of series resistance on the operation of junctionless transistors," Solid-State Electronics, vol. 129, pp. 103-107, 2017, doi: 10.1016/j.sse.2016.12.004.

- [20] D.-Y. Jeon, et al., "Series Resistance Effects on the Back-gate Biased Operation of Junctionless Transistors," in 2019 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), 2019, pp. 1-4, doi: 10.1109/EUROSOI-ULIS45800.2019.9041921.

- [21] D. K. Schroder, Semiconductor material and device characterization: John Wiley & Sons, 2015.

- [22] T. Rudenko, et al., "Substrate bias effect linked to parasitic series resistance in multiple-gate SOI MOSFETs," IEEE Electron Device Letters, vol. 28, pp. 834-836, 2007, doi: 10.1109/LED.2007.903955.

- [23] B. Szelag and F. Balestra, "Transconductance enhancement at low temperatures in deep submicrometre MOSFETs," Electronics Letters, vol. 34, pp. 1793-1794, 1998, doi: 10.1049/el\_19981227.

- [24] W. Schwarzenbach et al., "Advanced FD-SOI and beyond low temperature SmartCut™ enables high density 3-D SoC applications," IEEE Journal of the Electron Devices Society, vol. 7, pp. 863-868, 2019, doi: 10.1109/JEDS.2019.2916460.

- [25] S. Cristoloveanu, M. Bawedin, and I. Ionica, "A review of electrical characterization techniques for ultrathin FDSOI materials and devices," Solid-State Electronics, vol. 117, pp. 10-36, 2016, doi: 10.1016/j.sse.2015.11.007.