# Axiomatization and Imperative Characterization of Multi-BSP Algorithms: A Q&A on a Partial Solution

Frédéric Gava, Yoann Marquer

## ▶ To cite this version:

Frédéric Gava, Yoann Marquer. Axiomatization and Imperative Characterization of Multi-BSP Algorithms: A Q&A on a Partial Solution. International Journal of Parallel Programming, 2020, 48 (4), pp.626-651. 10.1007/s10766-020-00669-9 . hal-03189898

## HAL Id: hal-03189898 https://hal.science/hal-03189898

Submitted on 5 Apr 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Axiomatization and Imperative Characterization of Multi-BSP Algorithms

A Q&A about a partial solution and some inherent problems

Frédéric Gava LACL, University of Paris-East Créteil, France frederic.gava@univ-paris-est.fr and Yoann Marquer Inria, Univ Rennes, CNRS, IRISA Rennes, France yoann.marquer@inria.fr

August 13, 2020

#### Abstract

MULTI-BSP is a new bridging model which takes into account hierarchical architectures. We discuss two questions about MULTI-BSP algorithms and their programming: (1) How do we get a formal characterization of the class of MULTI-BSP algorithms? (2) How can a programming language be proven algorithmically complete for such a class? Our solution is based on an extension of a BSP version of sequential Abstract State Machines (ASMS).

## 1 Introduction

#### 1.1 Context of the work and background

Modern HPC architectures are made of hundreds of interconnected nodes each, with thousands of cores. Programming and reasoning on such *hierarchical* architectures is a daunting task without the use of some *high-level abstractions*.

#### 1.1.1 Multi-processors algorithms and hierarchical architectures

As it has been shown in [2], the BSP model [4, 23] is not truly adapted for hierarchical architectures (design of portable and scalable algorithms, performance prediction, *etc.*). BSP then partially loses the fact of being an efficient *bridging model*. An update of this model is needed and must be defined with the same level of abstraction, and bridges most of the architectures as the original BSP model did. So a proposition has been made in [26] and it has been called MULTI-BSP. The intention is: "with the comparison with the previous literature, our goal here is that of finding a bridging model that isolates the most fundamental issues of multi-core computing and allows them to be usefully studied in some detail." [26].

An important issue [1, 26] is the ability of designing *immortal algorithms*, which are algorithms that *scale* for *any machine* in the present and in the future as long as the bridging model can be adapted to it. In particular, these algorithms must work for any number of computing units (up to some constraints such as a number of processors equal to a power of two). This raises two questions: (1) can we *characterize* the *class* of the MULTI-BSP algorithms so that it is a natural extension of the class of the BSP algorithms [20]? And (2), can we prove that all the MULTI-BSP algorithms can be *programmed* using a programming language? If we can *intuitively* answer yes to these two questions or at least as soon as you see a MULTI-BSP algorithm or a programming language, *formally*, this requires more attention. Firstly, what is an algorithm [27] and secondly what is being algorithmically complete. And thus, what class do MULTI-BSP algorithms belong to?

#### **1.1.2** Axiomatization and imperative characterization of sequential algorithms

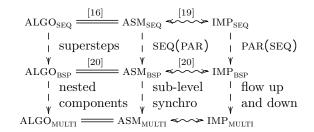

The most known definition of *sequential* (small steps and discrete time) algorithms is the *axiomatic* presentation of [15, 16]. The main idea is that there is not any standard language that truly represents all algorithms. Three widely consensual *postulates* are used to define the infinite set of sequential algorithms: (1) *sequential time*, algorithms work step-by-step; (2) *abstract states*, algorithms are oracular and the steps only depend on primitives (elementary operations); (3) *bounded exploration*, each of these steps is finite. This axiomatic definition has been mapped to the notion of Abstract state Machine (ASM, also called *evolving algebras*, *a kind of Turing machine with the appropriate level of abstraction* [15, 16]). Every sequential algorithm can be captured by an ASM and every ASM is a sequential algorithm. That is  $ALGO_{SEO}=ASM_{SEO}$ .

Furthermore, the study of class models [14, 19, 20] allows us to classify what can or cannot be effectively programmed. Indeed, if it is known that mainstream languages such as C or JAVA are Turing-complete, which means that they can simulate the computation of any computable function (so the inputoutput of any Turing machine, up to an unbounded memory), what is called algorithmic completeness rather focuses on the step-by-step behavior that is, a model could compute all the desired functions, but some algorithms (ways to compute these functions) could be missing [14]. By using the aforementioned axiomatization of the algorithms and an operational semantics of an imperative core-language (IMP), it has been formally proved in [19] that  $ASM_{SEQ} \simeq IMP$  that is mainstream languages are also algorithmically complete, which was only informally assumed so far.

In [20], we extended these results to BSP and proved that  $ALGO_{BSP} = ASM_{BSP} \simeq IMP_{BSP}$ . To do so, we add another postulate that arranges the steps into BSP's *supersteps* and in a way that the BSP algorithms no longer work on a single memory (a first-order structure) but on *p*-tuples of arbitrary sizes, on per computing unit. We also extend the ASMs so that they work on these *p*-tuples in a SEQ(PAR) manner [7]. ASM<sub>BSP</sub> use internally a global *function of communication* (which is also working step-by-step) *ab-stracting* how communications are performed by any BSP library. Finally, we extend IMP in an SPMD (Single Program Multiple Data) fashion so that programs also work on *p*-tuples but in a PAR(SEQ) manner. IMP<sub>BSP</sub> programs use an explicit call of a function of communication (*i.e.* a specific command). In this way, we define the class of BSP algorithms and prove that BSP languages (mostly C/JAVA+BSPLIB ones) are algorithmically complete to this class.

#### 1.2 Content of the work

We are now interested in answering the question of whether such results can be extended to the MULTI-BSP model, that is

(Intended theorem)  $ALGO_{MULTI} = ASM_{MULTI} \simeq IMP_{MULTI}$

That is proving an equivalence between an axiomatic definition of the MULTI-BSP algorithms and their operational points of view  $(ASM_{MULTI})$  and, proving an algorithmic simulation between  $IMP_{MULTI}$  and  $ASM_{MULTI}$  (up to elementary operations, *e.g.* how to perform integer additions or how to manage the communications). Because the MULTI-BSP model is ("just") a hierarchical extension of BSP, it seems appropriate to ask the question of how to extend the previous results about BSP [20] in a "*minimal*" way rather than doing all the proofs from scratch. We will show that this is mostly feasible but that there are some points that require more important modifications due to the use of *nested supersteps*. It is to notice that some definitions will be slightly unsatisfying because there is a lack of description of how computations are performed on "nodes" in the MULTI-BSP model [26].

#### 1.3 Outline

We mimic the works of [14, 15, 23] to organize the rest of the paper as a *dialog* between the *author* and a curious but equally *scrupulous colleague*. We made this uncommon choice of writing because this article is the *continuation* of [20] (which also contains a lot of FAQs) and it seems natural to ask ourselves the question of how to do such a work.

In Section 2 p.5, we first discuss MULTI-BSP algorithms (SubSection 2.1 p.5) and their axiomatization (SubSection 2.2 p.7). In Section 3 p.13, we then discuss their operational points of view as an extension of ASMs (SubSection 3.1 p.13) and the algorithmic simulation with a core programming language (Sub-Section 3.2 p.16). We finish this section by proving the intended theorem and that the *cost model is*

preserved. Some related work is presented in Section 4 p.22. Section 5 p.25 concludes and finishes with a brief outlook on future work.

## Contents

|                                                                               | 1                       |

|-------------------------------------------------------------------------------|-------------------------|

| .1 Context of the work and background                                         | 1                       |

| 1.1.1 Multi-processors algorithms and hierarchical architectures              | 1                       |

| 1.1.2 Axiomatization and imperative characterization of sequential algorithms | 2                       |

| .2 Content of the work                                                        | 2                       |

|                                                                               | 2                       |

| An axiomatization of MULTI-BSP algorithms                                     | <b>5</b>                |

| 2.1 The MULTI-BSP model                                                       | 5                       |

| Axiomatization of MULTI-BSP algorithms                                        | 7                       |

| 2.2.1 MULTI-BSP algorithms as state transition systems                        | $\overline{7}$          |

|                                                                               | 8                       |

|                                                                               | 10                      |

| 2.2.4 MULTI-BSP algorithm nested computations                                 | 10                      |

| mperative characterization of MULTI-BSP algorithms                            | 13                      |

| ASM <sub>MULTI</sub> and the MULTI-BSP algorithms                             | 13                      |

| 3.1.1 Definition and operational semantics of ASM <sub>MULTI</sub>            | 14                      |

| 3.1.2 ASM <sub>MULTI</sub> captures MULTI-BSP algorithms                      | 14                      |

| 2.2 Programming MULTI-BSP algorithms and algorithmical completeness           | 16                      |

|                                                                               | 10                      |

| 3.2.1 Semantics of a core imperative MULTI-BSP language                       | 16                      |

| 1 0 0                                                                         |                         |

| 3.2.2 Algorithmic completeness of a core-imperative MULTI-BSP language        | 16                      |

| 3.2.2 Algorithmic completeness of a core-imperative MULTI-BSP language        | 16<br>19                |

| 3.2.2 Algorithmic completeness of a core-imperative MULTI-BSP language        | 16<br>19<br><b>22</b>   |

|                                                                               | 1.2 Content of the work |

## 2 An axiomatization of MULTI-BSP algorithms

**Question 1:** Hello. Before we start, we probably need a common vocabulary. What should I read so that we can understand each other?

We recommend the original papers about ASMS [15, 16]. The author presents the ideas behind ASMS (the wanted Church-Turing thesis for algorithms). The paper [14] is also a good introduction to the ideas of classes and algorithmic completeness whereas [23] is a perfect introduction to the BSP bridging model. And of course [26] is the reference for MULTI-BSP.

This work is the continuation of [20], so, to get a common *vocabulary*, it is strongly recommended to read it. All the notions used in this work are presented there (except what is dedicated to the MULTI-BSP model): first-order structures X (page. 6), signature, terms  $\theta$  and universe (p. 7), interpretation of terms  $\overline{\theta}^{X}$  (p. 7), isomorphism of structures (p. 8) and consistent updates  $\Delta$  (p. 8), *etc.*

#### 2.1 The MULTI-BSP model

#### Q2: Could you remind me of the MULTI-BSP model which is less known than BSP?

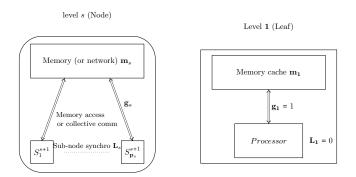

MULTI-BSP extends the BSP bridging model to take into account modern hierarchical architectures. There exist other extensions such as the one of [9] but MULTI-BSP describes hierarchical architectures in a simpler way. This model brings a *tree*-based view of nested *components* (sub-machines) where the lowest *levels*<sup>1</sup> are computing units (processors, the *leaves*) with a small block of memory (*e.g.* caches) and every other level (the *nodes*) contains a memory *only* (or a network). Inside a node-component, each memory can access other memories only with the use of an explicit global communication. The tree is of depth **d** and is assumed *balanced and homogeneous*. Fig. 1 illustrates the different components. A MULTI-BSP architecture has four parameters at each level  $s \in \{1 \cdots d\}$ :

- 1.  $\mathbf{p}_{\mathbf{s}}$  is the number of sub-components inside level s;

- 2.  $\mathbf{g}_{s}$  is the *bandwidth* between levels s and s-1; the ratio of the number of operations to the number of words that can be transmitted in a second;

- 3.  $L_s$  is the synchronization cost of all sub-components at s-1 level;

- 4.  $\mathbf{m}_{s}$  is the amount of memory available for each component at level s.

Finally, there is the homogeneous local processing speed  $\mathbf{r}$  of each of the processors (components of level 1) where a step on a word is considered as the unit of time ( $\mathbf{g}_1 = 1$ ). A leaf does not have sub-components making  $\mathbf{p}_1$  and  $\mathbf{L}_1$  both equal to 0. For example, the BSP model with parameters ( $\mathbf{p}, \mathbf{g}, \mathbf{L}$ ) where each basic unit has memory  $\mathbf{m}$  would be modeled with [26]  $\mathbf{d} = 2$  and ( $\mathbf{p}_1 = 0, \mathbf{g}_1 = 1, \mathbf{L}_1 = 0, \mathbf{m}_1 = \mathbf{m}$ ), ( $\mathbf{p}_2 = \mathbf{p}, \mathbf{g}_2 = \mathbf{g}, \mathbf{L}_2 = \mathbf{L}, \mathbf{m}_2$ ) where  $\mathbf{m}_2$  is, for example, the size of a slower but bigger memory. Another value for  $\mathbf{m}_2$  could be n, the size of the problem (implemented as a virtual memory with a distributed file system). Assuming a specific architecture with data streams as input,  $\mathbf{m}_2$  could also be  $\infty$  and  $\mathbf{g}_2$  could rely on the acquisition stream data rate.

#### Q3: And what about the execution model of MULTI-BSP algorithms?

A MULTI-BSP computer works in a sequence of nested supersteps where at a node level s, each superstep is made of the supersteps of levels s - 1 and terminates by a synchronization (barrier) of all the sub-machines of level s - 1 in favor of a data exchange between the  $m_{s-1}$  memories and  $m_s$  whereas on leaves (level 1), a superstep is made of computations only<sup>2</sup> (using the data accessible the local memories of leaves). Then, a new superstep can start at level s. Note that the definition requires synchronization of the directly below sub-components of a component, but no synchronization across branches that are separated in the component hierarchy. The cost of a MULTI-BSP algorithm is the sum of the costs of the supersteps of the root node, where the cost of each of these supersteps is (recursively) the maximal cost of the supersteps of the sub-components plus the needed communication plus the synchronization; And for each leaf, the cost is the computation time. And so on.

<sup>&</sup>lt;sup>1</sup>The term of "stage" was used in place of "level" in [1, 2] because "level" (as layer or floor) is largely used in other domains in computer science notably in type systems that were used in [2].

$<sup>^{2}</sup>$ Regarding a level that is only composed by a memory capacity, that is to say a node, one processor of the branch is

Figure 1: The MULTI-BSP components.

#### **Q4:** Hum, the architecture is not exactly identical to the original work of [26]. Why?

Indeed and these modifications do not change the way to write or analyze the MULTI-BSP algorithms. Firstly, we slightly change the indexes for convenience only. For example, the bandwidth parameter of the memory concerns the current level instead of the upper level as originally described in [26]. Secondly, in our purpose, each level has its own memory whereas in [26], the leaves are computing units only, an additional abstract level. This also simplifies the presentation. Thirdly, we natively allow *horizontal* communications to make the set of the BSP algorithms a *subset* of the MULTI-BSP ones and, in particular, with the idea of working in an *incremental* manner (as in [1]), that is using BSP programs inside MULTI-BSP ones.

### Q5: So your model do not have shared memories and concurrent accesses to them?

Definitively not. Concurrent writing induces unnecessarily complicated semantics (non-deterministic behaviour) and even if we assume only concurrent reading, we will see later that this leads to an axiomatization too far away from that of [16]. From a certain point of view, our MULTI-BSP model is a kind of homogeneous tree organized D-BSP [25] model without dynamic subgroup synchronizations and where sub-components shared a memory.

**Q6:** So, in your model, processors cannot read/write values from any level. And the communication phase at a given level *i* (the h-relation+synchronization  $L_i$ ) is performed by the sub-components only and not by all the processors that belong to level *i*. What about the  $G_i = g_i + g_{i1} + \cdots + g_1$  parameter (the cost of communication from level 1 to outside level *i*) of [26]? Can you elaborate on that? Because your model deviates from the original model of [26] where each memory, at a level *i*, is shared be all processors belong it.

Absolutely. We are in a distributed memory model. There are some pro and cons. First, hierarchicalnetwork clusters can be taken into account (assuming that some machines share their own memomies with other ones and where the accesses are, of course, only using communication). Second, a superstep that is using communication from level 1 to outside level i (the  $G_i$  parameters<sup>3</sup>) can be simulated by using only communication on the deeper levels  $(i - 1, \dots, 1)$ ; that is closer to the recursive data decomposition of algorithms. And if processors share a given memory (say the L3 cache), then we can cut it into several parts. Using distributed memories is also closer to the original BSP model. Third, if there are too much cores, there may be a bootleneck making the  $G_i$  parameter inoperative when accessing certain memories (e.g. the RAM). On the contrary, the number of "simultaneous" accesses is reduced by considering those by sub-nodes only (during a communication phase). And for performing the communications (scattering/gathering data) where would be the intermediary needed values, on the lowest levels? And finally, how could processors access a memory (e.g. the RAM) without having caches copies (kind of miss-caches) made by the OS/architecture? Using only communications between levels makes this more explicit (assuming always enough memory when doing the local computations that is when processors are using the memories at level 1).

responsible for all the memory manipulations that are done to it: this processor (which is chosen depends on the implementation) performs the data exchanges such as gathering data, *etc.* We will show later the inherent problem of such a design.

$<sup>{}^{3}</sup>$ It is to notice that such parameters are defined but never explicitly used in [26] and only communication between consecutive levels are used in the algorithms.

But this model suffers for two main defects. First, if there are only communication between different levels, how does the system handle them? Scattering and gathering data needs a little of computation. The solution of [29] is using a "master" that is selecting a core to handle a given level. We will analyse this later. Second, there is no possible communication between processors of different sub-trees without going through all their top levels and thus using there synchronization mechanisms (unlike the model of [26]). This overcost must be taken into account when designing MULTI-BSP algorithms in this model.

Q7: You actually define a MULTI-BSP computer and so what are algorithms?

**Definition 1** (MULTI-BSP algorithms, informal) A MULTI-BSP algorithm is a computation, organized in a nested sequence of supersteps, that can stand on any MULTI-BSP machine<sup>4</sup>.

Now let us present a more formal definition.

#### 2.2 Axiomatization of MULTI-BSP algorithms

**Q8:** It does not seem to be moving too far. What is necessary to be modified in your previous formal axiomatization [20] of the BSP algorithms?

Obviously the tree of nested components (memories) and the organization of the nested supersteps. **Q9:** That sounds too easy. I guess you must redefine all the previous postulates and the ASMs? And the imperative language too?

You are right. But let us start with a word of caution and with the postulates. The first one is identical to the one of both sequential [16] and BSP algorithms [20]. It stipulates that there is no concurrency.

#### 2.2.1 MULTI-BSP algorithms as state transition systems

Postulate 1 (Sequential Time) A MULTI-BSP algorithm A is given by:

- 1. A (potentially infinite) set of states S(A);

- 2. A (potentially infinite) set of initial states  $I(A) \subseteq S(A)$ ;

- 3. A transition function  $\tau_A : S(A) \to S(A)$ .

Sets are potentially infinite because an algorithm A, such as an integer sorting, can have an infinite number of inputs, *e.g.* all possible integer arrays, or the possible distributions whatever the number of processors for a parallel sorting algorithm. These inputs are encoded in the initial states. We recall [16, 20] that an *execution* of an algorithm A is an infinite sequence of states  $\vec{S} = S_0, S_1, S_2, \ldots$  such that  $S_0$  is an initial state and for every  $t \in \mathbb{N}$ ,  $S_{t+1} = \tau_A(S_t)$  (accessible states). And we will say that a state  $S_t$  of an execution  $\vec{S}$  is final if  $\tau_A(S_t) = S_t$  (terminal execution). The duration is

$$\operatorname{time}(A, S_0) \stackrel{\text{def}}{=} \begin{cases} \min\left\{t \in \mathbb{N} \mid \tau_A^t(S_0) = \tau_A^{t+1}(S_0)\right\} & \text{if the execution is terminal} \\ \infty & \text{otherwise} \end{cases}$$

Every algorithm can access *elementary operations* (a.k.a. *primitives*) which only depend of the architecture.

#### **Q10:** Is it what is called "intrinsically oracular"?

Right. This is an essential feature. For example, a MULTI-BSP algorithm could be different whether a broadcasting primitive is available or is simulated by point-to-point sending of data. We are not interested in a specific library nor a particular machine but to all possible MULTI-BSP algorithms.

Q11: And so what happens to MULTI-BSP architectures. Are they also oracular?

Basically yes. MULTI-BSP algorithms will manipulate *states* as *d*-nested-tuples (called *trees* in the rest of the paper) of structures. Each structure represents the *available memory* of a component which could only be accessible using communicating primitives (nodes), except the ones of computing units (leaves) where computations could also occur. The related definitions about structures of [16, 20] will subsequently be used for each component. Let us define the trees.

<sup>&</sup>lt;sup>4</sup>Assuming, if necessary, some properties on the performance parameters such as  $\mathbf{p_2}$  is even or, on most modern and realistic machines, that  $\forall s \in \{1 \dots d\}, \mathbf{m}_s \gg \mathbf{m}_{s-1}, etc.$

#### 2.2.2 States as MULTI-BSP Trees

Definition 2 (MULTI-BSP Trees) Trees are made of nodes and leaves. Trees are defined by induction

$$T \stackrel{\text{def}}{=} \langle X \rangle \mid \langle X | T_1, \dots, T_p \rangle$$

where p > 0 (the number of subcomponents at the level) and X is the **memory** (structure) of the component.  $T_1, \ldots, T_p$  (noted  $\vec{T}$  in the following) are the p **branches** (subtrees) of the node.

We assume that for each leaf  $\langle Y \rangle$ , a processor exists and can only access without communication to the Y memory (local computations), whereas nodes  $\langle X | T_1, \ldots, T_p \rangle$  can only communicate between two consecutive levels. We also assume that each memory is unique, for instance that there exists a symbol **id** interpreted differently on every memory. To remain consistent with Subsection 2.1 p.5, the leaves and their associated processors are homogeneous. Moreover, in the following (and for simplicity and when it is unambiguous), by assuming  $p \ge 0$ ,  $\langle X | T_1, \ldots, T_p \rangle$  or  $\langle X | \vec{T} \rangle$  may denote both leaves and nodes.

**Q12:** You provided a classical yet general definition for trees, but in Subsection 2.1 p.5 you assumed the trees to be balanced.

Indeed this is an important assumption for the MULTI-BSP algorithms (cost analysis, *optimality* [26] and algorithm design such as for the distribution and *load-balancing* of data), but our proofs do not require this hypothesis and thus we wanted to prove a more general result. If we wanted the MULTI-BSP *d*-trees to be balanced, we could have defined them inductively as  $T \stackrel{\text{def}}{=} \langle X \rangle^1 | \langle X | T_1^n, \ldots, T_p^n \rangle^{n+1}$ , where *n* is the level.

Now we can define some simple relations on trees such as subtree, structural equality and position of a subtree in a tree.

**Definition 3 (Subtree relation)** For every S and T (trees), we define inductively  $S \leq T$ , S is a subtree of T, as

$$S \leq S$$

$$S \leq T_i \implies T \leq \langle X | T_1, \dots, T_i, \dots, T_p \rangle$$

Notice that because each memory is unique, if  $S \leq \langle X | T_1, \ldots, T_p \rangle$  then there exists a unique *i* such that  $S \leq T_i$ . Finally, for the second postulate, we need to define the notion of "*preserving* the structure of a tree" and tree-isomorphism.

Definition 4 (Tree-similarity (structurally))

$$\begin{array}{l} \langle X \rangle \stackrel{\circ}{=} \langle Y \rangle \\ \langle X | T_1, \dots, T_p \rangle \stackrel{\circ}{=} \langle Y | U_1, \dots, U_q \rangle \\ if \ p = q \ and \ for \ every \ 1 \le i \le p, T_i \stackrel{\circ}{=} U_i \end{array}$$

To put it simply, the trees are the same but with potentially different memory content on their components. This notation is not restricted to trees of structures, and will be used also in Definition 6 for trees of functions. For example,  $\langle X^1 | \langle X^2 \rangle, \langle X^3 \rangle \rangle$  is not similar to  $\langle Y^1 | \langle Y^2 \rangle, \langle Y^3 \rangle, \langle Y^4 \rangle \rangle$ .

**Definition 5 (Position in a tree)** For every similar pair of trees  $T \stackrel{\circ}{=} U$  and every subtree  $S \leq T$ , we define inductively pos(S,T;U) as the subtree of U that is in the same position as S is in T:

$$\mathbf{pos}(S, S; U) \stackrel{\text{def}}{=} U$$

$$\mathbf{pos}(S, \langle X | \vec{T} \rangle; \langle Y | \vec{U} \rangle) \stackrel{\text{def}}{=} \mathbf{pos}(S, T_i; U_i)$$

where  $T_i$  is the unique (see Definition 3)  $T_j$  amongst  $T_1, \ldots, T_p$  such that  $S \leq T_j$

In [20] we defined multi-isomorphisms for tuples of structures, that should have been named "tupleisomorphisms". For this paper, we define tree-isomorphisms.

**Definition 6 (Tree-isomorphism)** A tree-function  $\Phi$  is defined inductively as a tree of functions:

$$\Phi \stackrel{\text{der}}{=} \langle \varphi \rangle \mid \langle \varphi | \Phi_1, \dots, \Phi_p \rangle$$

where p > 0 and  $\varphi$  is a standard function, such that for every tree  $T \stackrel{\circ}{=} \Phi$ :

$$\begin{array}{l} \text{if } \Phi = \langle \varphi \rangle & \text{then } \Phi \langle X \rangle &= \langle \varphi(X) \rangle \\ \text{if } \Phi = \langle \varphi | \Phi_1, \dots, \Phi_p \rangle & \text{then } \Phi \langle X | T_1, \dots, T_p \rangle &= \langle \varphi(X) | \Phi_1(T_1), \dots, \Phi_p(T_p) \rangle \end{array}$$

For every T and U (trees), the tree-function  $\Phi$  is a tree-isomorphism between T and U if 1)  $T \stackrel{\circ}{=} \Phi \stackrel{\circ}{=} U$ , and 2) for every subtree  $\langle X | \vec{T} \rangle \leq T$  and  $\langle Y | \vec{U} \rangle = \mathbf{pos} (\langle X | \vec{T} \rangle, T; U)$  there exists  $\langle \varphi | \vec{\Phi} \rangle \stackrel{\circ}{=} \langle X | \vec{T} \rangle$  such that  $\varphi$ is an isomorphism between X and Y.

To put it simply, we apply an isomorphism to each memory (structure) of the tree. For example,  $\langle X^1 | \langle X^2 \rangle, \langle X^3 \rangle \rangle$  is isomorph to  $\langle Y^1 | \langle Y^2 \rangle, \langle Y^3 \rangle \rangle$  if each  $X^i$  is isomorph to each  $Y^i$ . Notice that if  $\Phi$  is a tree-isomorphism then  $\Phi^{-1}$ , defined as  $\Phi$  where all the  $\varphi$  have been replaced by their reciprocal  $\varphi^{-1}$ , is also a tree-isomorphism which is the reciprocal of  $\Phi$ .

**Q13:** What does isomorphism in this context mean?

We are interested in the actual properties of all the models of computation, not the naming conventions used for them, as in [16]. Thus, in the following, we always reason up to isomorphism.

**Postulate 2 (Abstract States)** For every MULTI-BSP algorithm A:

- 1. The states of A are trees of structures with the same finite signature  $\mathcal{L}(A)$  (containing at least the booleans, the equality and a uniquely interpreted id (identifier) symbol);

- 2. S(A) and I(A) are closed by tree-isomorphisms and subtrees;

- 3. The transition function  $\tau_A$  preserves tree structures and the universes, and commutes with treeisomorphisms.

#### **Q14:** Are you defining a fixed size for the trees?

No. For each state, d (the maximal depth of a tree) and each  $p_i$  are fixed for each execution only, abstracting the run of the algorithm on different MULTI-BSP machines and thus making the approach general when modeling algorithms (the notion of *immortal* algorithm). In the same way, the structures of different initial states contain potentially different values, abstracting the run of different input (initial) data.

Q15: Ok and what does "preserves tree structures" mean?

By "preserves tree structures" we mean that if T is a state (thus is a tree) then  $\tau_A(T)$  is a tree such that  $\tau_A(T) \stackrel{\circ}{=} T$ . For every subtree  $S \leq T$  we define  $\tau_A(T)_S$ , the (unique) subtree of  $\tau_A(T)$  which is in the same position in  $\tau_A(T)$  as S is in T.

#### Definition 7 (Next subtree)

$$\tau_A(T)_S \stackrel{\text{def}}{=} \mathbf{pos}(S,T;\tau_A(T))$$

Q16: Also, what does "closed and commute" by/with "tree-isomorphisms" or "subtrees" mean?

Let Z be a set of trees. Z is closed by tree-isomorphims means that if  $\Phi$  is a tree-isomorphism and  $T \in Z$  then  $\Phi(T) \in Z$ . Z is closed by subtrees means that if  $S \leq T$  and  $T \in Z$  then  $S \in Z$ .  $\tau_A$  commutes with tree-isomorphisms means that if  $\Phi$  is a tree-isomorphism and T is a state then  $\tau_A(\Phi(T)) = \Phi(\tau_A(T))$ .

Q17: Could you also briefly remind me of the concept of universe?

We recall [16, 20] that if a structure X has signature  $\mathcal{L}(A)$  and universe  $\mathcal{U}(X)$ , the update  $(f, \vec{a}, b)$ where  $f \in \mathcal{L}(A)$  and  $\vec{a}, b \in \mathcal{U}(X)$  is defined as in [20, 16], and so is the structure  $X \oplus (f, \vec{a}, b)$  with the same signature and universe as X, and where all the symbols are interpreted as in X except f that now has value b in  $f(\vec{a})$ . The update is said trivial if nothing has changed. As in [20, 16], the notation  $X \oplus \Delta$  is extended to tuples of updates  $\Delta$  that clash if inconsistent. Moreover, if the structures X and Y have the same signature and universe, then  $\Delta = Y \oplus X$  denotes the unique set of non-trivial updates such that  $Y = X \oplus \Delta$ .

**Definition 8 (Updates of a leaf)** As in [16, 20], the set of updates done to the memory of the leaf  $\langle X \rangle$  is  $\Delta(A, X) \stackrel{\text{def}}{=} \tau_A(X) \ominus X$ .

In [20] the states were tuples  $\vec{X}$  of structures and we defined  $\Delta^i(A, \vec{X})$  as the *i*-th component of the tuple  $\tau_A(\vec{X}) \ominus \vec{X}$ . But in the MULTI-BSP context, where the states are trees, we define updates of subtrees.

**Definition 9 (Updates of a subtree)** For every state T, the set of updates done for a subtree  $\langle X | \vec{T} \rangle \leq T$ is  $\Delta(A,T)_{\langle X | \vec{T} \rangle} \stackrel{\text{def}}{=} Y \ominus X$ , where  $\langle Y | \vec{U} \rangle = \tau_A(T)_{\langle X | \vec{T} \rangle}$ .

#### 2.2.3 MULTI-BSP algorithms work step-by-step

**Q18:** And now, do processors compute locally (and nodes communicate) on every isomorphic datastructure without limitation?

Sorry to say no again. We want the algorithms to work *step-by-step*. Indeed, step-by-step means that at every step, only a *bounded* number of terms are manipulated, not a growing number of terms, making any machine/algorithm *unrealistic* [16] (and thus opposed to the bridging model approach).

**Q19:** Are you speaking of the exploration witnesses à la Gurevich [16]?

Yes. We need such a postulate to forbid algorithms to work unrealistically<sup>5</sup>. It is as those of sequential and BSP algorithms. For the rest of the paper, we also need to define the notion of *coincidence*.

**Definition 10 (Coincidence over terms)** Let A be a MULTI-BSP algorithm and  $\Theta$  be a set of terms of  $\mathcal{L}(A)$ . We say that two states U and V of A coincide over  $\Theta$  if  $U \stackrel{\circ}{=} V$  and for every  $\langle X | \vec{U} \rangle \leq U$  and  $\langle Y | \vec{V} \rangle = \mathbf{pos}(\langle X | \vec{U} \rangle, U; V)$  we have for every  $\theta \in \Theta$  that  $\overline{\theta}^X = \overline{\theta}^Y$ .

where  $\overline{\theta}^{X}$  denotes the interpretation [20] (p. 7) of the term  $\theta$  in the structure (memory) X.

**Postulate 3 (Bounded exploration)** For every MULTI-BSP algorithm A there exists a finite set  $\Theta(A)$  of terms (closed by subterms) such that for every state U and V, if they coincide over  $\Theta(A)$  then for every pair of subtrees S and W such that  $S \leq U$  and  $W = \mathbf{pos}(S, U; V)$  we have  $\Delta(A, U)_S = \Delta(A, V)_W$ .  $\Theta(A)$  is called the *exploration witness* of A and contains at least the boolean symbol **true**. The interpretations of the terms in  $\Theta(A)$  are called the *critical elements*.

**Q20:** What can we do with these elements?

We can prove that every value in an update is a critical element.

**Lemma 1 (Critical Elements)** Let A be a MULTI-BSP algorithm and U be a state. For every subtree  $S \leq U$ , if  $(f, \vec{a}, b) \in \Delta(A, U)_S$  then  $\vec{a}, b$  are critical elements.

**Proof** (sketch). The proof (by contradiction and by using a fresh variable in the witness) is similar to the ones of [16, 20].  $\Box$

That implies that for every step of the computation, for a given memory (structure), only a bounded (finite) number of terms are read or written, thus that a bounded *amount of work* is done at every step.

**Lemma 2 (Bounded Set of Updates)** Let A be a MULTI-BSP algorithm and U be a state. For every subtree  $S \leq U$ , card( $\Delta(A, U)_S$ ) (cardinality) is bound.

**Proof** (sketch). The proof is similar to the one in [16, 20].

#### 2.2.4 MULTI-BSP algorithm nested computations

**Q21:** That is thus close to the original work of [16]. But, I currently do not see anything about the nested superstep organization of MULTI-BSP algorithms.

This is our last postulate. The communication between local memories occurs only during a communication phase. To do so, a MULTI-BSP algorithm A will use two functions  $\mathbf{compu}_A$  and  $\mathbf{comm}_A$ whether, during the execution of A, a branch runs computations or communications (it is *working*). The function  $\mathbf{comm}_A$  allows the communication between the memories of a component. So we need first to define the set of leaves (*resp.* nodes) for the  $\mathbf{compu}_A$  (*resp.*  $\mathbf{comm}_A$ ) function.

**Definition 11 (All leaves and nodes)** The (potentially infinite) sets of the single memories (from leaves) and tuples of memories (from nodes) of a MULTI-BSP algorithm A are defined as:

$$\begin{aligned} Leaves(A) &\stackrel{\text{def}}{=} \bigcup_{T \in S(A)} \{X \mid \langle X \rangle \leq T\} \\ Nodes(A) &\stackrel{\text{def}}{=} \bigcup_{T \in S(A)} \{(X_0, X_1, \dots, X_p) \mid p > 0 \land \langle X_0 \mid \langle X_1 \mid \overrightarrow{T_1} \rangle, \dots, \langle X_p \mid \overrightarrow{T_p} \rangle \rangle \leq T \end{aligned} \end{aligned}$$

where p + 1 is called the arity of the tuple.

$<sup>{}^{5}</sup>$ We insist that such witnesses are not used to prove that the executions are finite; It is not a kind of measurement as in the Hoare logic.

To put it simply, we recursively add all the memory components (from nodes and leaves) of all the subtrees of all the states (trees) of a MULTI-BSP algorithm A. We can now give the last postulate.

**Postulate 4 (Nested superstep phases)** For every MULTI-BSP algorithm A there exists a pair of functions  $compu_A$ : Leaves (A)  $\rightarrow$  Leaves (A) and  $comm_A$ : Nodes (A)  $\rightarrow$  Nodes (A) preserving the arity, such that by induction on every state  $\langle X | \vec{T} \rangle$ :

$$\tau_{A}\langle X_{0} | \langle X_{1} | \vec{T_{1}} \rangle, \dots, \langle X_{p} | \vec{T_{p}} \rangle \rangle = \begin{cases} \langle compu_{A}(X) \rangle \\ \langle X_{0} | \tau_{A} \langle X_{1} | \vec{T_{1}} \rangle, \dots, \tau_{A} \langle X_{p} | \vec{T_{p}} \rangle \rangle \\ if \exists 1 \leq i \leq p, \tau_{A} \langle X_{i} | \vec{T_{i}} \rangle \neq \langle X_{i} | \vec{T_{i}} \rangle \\ \langle X_{0}^{\prime} | \langle X_{1}^{\prime} | \vec{T_{1}} \rangle, \dots, \langle X_{p}^{\prime} | \vec{T_{p}} \rangle \rangle \end{cases}$$

where p > 0 and  $comm_A(X_0, X_1, ..., X_p) = (X'_0, X'_1, ..., X'_p)$ , which performs the communications of the memories of a component.

From a certain point of view,  $\mathbf{compu}_A$  is the call of a single processor's operation whereas  $\mathbf{comm}_A$  is a single collective data transfer.

Q22: Some explanations are needed.

Of course. The function  $\tau_A$  is close to the BSP one of [20] except that it is now defined recursively (on each level) and thus for each component.  $\tau_A$  performs computations on leaves only and communications within the upward memory components otherwise. Notice that  $\tau_A$  induces that the function of communication modifies the structures if a shifting (upward or downward the work in the tree) of level is needed. As intended for the MULTI-BSP model of execution, for a given level, such an evaluation is feasible only if there is no work in the lower levels (they finish their supersteps). Otherwise, nothing is done; That forbids concurrent memory manipulations from different levels.

**Q23:** I do not see the BSP's sequences of computations and communications as in your previous postulates about BSP [20]. Is this normal?

For a node controlling only p > 0 leaves, we have:

$$\tau_A \langle X_0 | \langle X_1 \rangle, \dots, \langle X_p \rangle \rangle = \begin{cases} \langle X_0 | \langle \mathbf{compu}_A(X_1) \rangle, \dots, \langle \mathbf{compu}_A(X_p) \rangle \rangle \\ \text{if } \exists 1 \le i \le p, \mathbf{compu}_A(X_i) \neq X_i \\ \langle X'_0 | \langle X'_1 \rangle, \dots, \langle X'_p \rangle \rangle \\ \text{otherwise, where } p > 0 \text{ and} \\ \mathbf{comm}_A(X_0, X_1, \dots, X_p) = (X'_0, X'_1, \dots, X'_p) \end{cases}$$

which corresponds closely to the fourth postulate [20] for BSP algorithms (the sequence of supersteps), especially when considering a BSP machine as a MULTI-BSP machine with a single node of p processors. Q24: It is strange that there is no computation on nodes because most communication patterns need a little computation. How do you do that?

It is the responsibility of the communication function to (implicitly) perform such computations because it is *oracular*. In "practice" [1, 30], the needed computations that are done in the upper memories focus on data management and one selected (by the implementation/architecture) processor of a branch can do such a work. We will discuss this issue later.

**Q25:** A bit of cheating but let us move on. What is thus a MULTI-BSP algorithm?

A MULTI-BSP *algorithm* is an object verifying these four postulates, and we denote by  $ALGO_{MULTI}$  the (infinite) set of MULTI-BSP algorithms.

Q26: And now, what can we deduce from all this?

Now, we can prove that the set of MULTI-BSP algorithms satisfies a strict separation of the phases. To do so, we first prove some lemmas about the computation and communication *phases*. So for convenience, we will define such phases for branches.

**Definition 12 (Computation and Communication phases)** A leaf  $\langle X \rangle$  is said to be in a computation phase if  $compu_A(X) \neq X$ . A node  $\langle X_0 | \langle X_1 | \vec{T_1} \rangle, \ldots, \langle X_p | \vec{T_p} \rangle \rangle$  is said to be in a computation phase if there exists  $1 \leq i \leq p$  such that  $\tau_A \langle X_i | \vec{T_i} \rangle \neq \langle X_i | \vec{T_i} \rangle$ . Otherwise, the node is said to be in a communication phase.

This requires some remarks. Firstly, we did not specify the function  $\mathbf{comm}_A$  in order to be generic (oracular spirit). Secondly, during a computation phase, if a processor has finished its computations, the processor "waits" for the communication phase, that corresponds to a possible load-balancing overhead of the algorithm. That can also happen between different nodes during the communication phases: one branch (sub-component) needs more computations/communications than other branches. Thirdly we do not distinguish a communication step from a synchronization step, because both are globally done, at a given level, by the function  $\mathbf{comm}_A$ . A superstep is a manipulation of the memories of each component until the sub-components finish their own supersteps.

**Lemma 3 (Computation phases are closed by subtree)** Let A be a MULTI-BSP algorithm, and T be a state. If a subtree  $S \leq T$  is in a computation phase, then T is also in a computation phase.

**Proof.** The proof is done by induction on the subtree relation. If S = T then T is in a computation phase by hypothesis. If  $S \leq T_i$  with  $T = \langle X | T_1, \ldots, T_i, \ldots, T_p \rangle$  and p > 0, then by induction hypothesis  $T_i = \langle X_i | U_1, \ldots, U_q \rangle$  is in a computation phase. So, either q = 0 (it is a leaf) and  $\operatorname{compu}_A(X_i) \neq X_i$ , or  $\tau_A \langle X_i | U_1, \ldots, U_q \rangle = \langle X_i | \tau_A(U_1), \ldots, \tau_A(U_q) \rangle$  and there exists  $1 \leq j \leq q$  such that  $\tau_A(U_j) \neq U_j$ . In any case,  $\tau_A(T_i) \neq T_i$ , so T is also in a computation phase.

Notice that in general we do not have  $\tau_A(T)_S = \tau_A(S)$ . For instance, two leaves  $\langle X_1 \rangle$  and  $\langle X_2 \rangle$  may have finished their computations so we have  $\tau_A \langle X_1 \rangle = \langle X_1 \rangle$ , but they may be updated by the communication function so  $\tau_A \langle X | \langle X_1 \rangle, \langle X_2 \rangle \rangle_{X_1} \neq X_1$ . But this is the case for subtrees in a computation phase.

**Lemma 4 (Computing states)** Let A be a MULTI-BSP algorithm, and T be a state. For every leaf  $S \leq T$  in a computation phase:  $\tau_A(T)_S = \tau_A(S)$ .

**Proof.** The proof is done by induction on T. If  $T = \langle X \rangle$  is a leaf, then the only subtree is T itself. Let us assume now that  $T = \langle X | T_1, \ldots, T_p \rangle$  is a node. If S = T then by definition of **pos** we have  $\tau_A(T)_S = \tau_A(T) = \tau_A(S)$ . If there exists  $1 \le i \le p$  such that  $S \le T_i$  then by induction hypothesis  $\tau_A(T_i)_S = \tau_A(S)$ . Because the subtree  $S \le T$  is in a computation phase, by Lemma 3, so do T. So  $\tau_A(T) = \langle X | \tau_A(T_1), \ldots, \tau_A(T_p) \rangle$  and thus, by definition of **pos**,  $\tau_A(T)_S = \tau_A(T_i)_S$ . Hence  $\tau_A(T)_S = \tau_A(S)$ .

**Corollary 1 (Computing leaves)** Let A be a MULTI-BSP algorithm, and T be a state. For every leaf  $\langle X \rangle \leq T$  in a computation phase:  $\Delta(A,T)_X = \Delta(A,X)$ .

**Proof.** By definition,  $\Delta(A, T)_X = \tau_A(T)_X \ominus X$ . Because  $\langle X \rangle$  is in a computation phase, by Lemma 4,  $\tau_A(T)_X = \tau_A(X)$ . So  $\Delta(A, T)_X = \Delta(A, X)$ .

Thus, a leaf in a computation phase ignores all the processors above.

**Technical Lemma 1 (Properties of the computation)** For every MULTI-BSP algorithm A,  $compu_A$  preserves the universes and commutes with isomorphisms.

**Proof** (sketch). The proof is similar to the one of [20].

**Lemma 5 (Computing states are closed by tree-isomorphisms)** Let A be a MULTI-BSP algorithm,  $\Phi$  be a tree-isomorphism and  $T \stackrel{\circ}{=} \Phi$  be a state. If T is in a computation phase, then  $\Phi(T)$  is in a computation phase too.

**Proof.** If  $T = \langle X \rangle$  is a leaf, we assume by contradiction that  $\Phi \langle X \rangle$  is not in a computation phase, so  $\tau_A(\Phi \langle X \rangle) = \Phi \langle X \rangle$ . By the second postulate,  $\tau_A(\Phi \langle X \rangle) = \Phi(\tau_A \langle X \rangle)$ . So  $\Phi(\tau_A \langle X \rangle) = \Phi \langle X \rangle$ , and by applying  $\Phi^{-1}$  on both sides we have  $\tau_A \langle X \rangle = \langle X \rangle$  that contradicts that  $\langle X \rangle$  is in a computation phase. If  $T = \langle X | T_1, \ldots, T_p \rangle$  is a node, we assume by contradiction that  $\Phi(T) = \langle \varphi(X) | \Phi_1(T_1), \ldots, \Phi_p(T_p) \rangle$  is not in a computation phase, so for every  $1 \leq i \leq p$ ,  $\tau_A(\Phi_i(T_i)) = \Phi_i(T_i)$ . By the second postulate,  $\tau_A(\Phi_i(T_i)) = \Phi_i(\tau_A(T_i))$ , so by applying  $\Phi_i^{-1}$  we obtain that for every  $1 \leq i \leq p$ ,  $\tau_A(T_i) = T_i$ , which contradicts that T is in a computation phase.

**Technical Lemma 2 (Shifting of level)** Let A be a MULTI-BSP algorithm, and T be a state. If a subtree  $S \leq T$  has finished its communication phase, then: (1) if  $S = \langle X | T_1, \ldots, T_p \rangle$  then the next phase (communication or computation) will be on the  $T_i$ ; exclusise or (2) if exist  $U = \langle X | T_1, \ldots, S, \ldots, T_p \rangle$  then the next phase (communication or computation) will be on U.

**Proof (sketch).** The proof is done by induction on T and by case using the fourth postulat: if S is a leaf (end of the computation phase) then U is a node (the level is "up"); otherwise, S is a node, and depending of  $\mathbf{comm}_A$ , either one of the  $T_i$  has been modified such that a new phase helds on  $T_i$  (the level is "down") or U has been modified such the next communication phase helds on U.

By abuse of language, we will say that the shifting of level (where the next phases take place in the tree, that is the flow of execution is changing of level) can only be directly downward (resp. upward) and we say "down" (resp. "up"). We will say that the level is  $\pm 1$  depending if it is "down" or "up". Notice that we did not assume in the fourth postulate that the communication function commutes with tree-isomorphisms, because this is a corollary (proved as in [20]) of the second postulate and Lemma 5.

Corollary 2 (Properties of communication) For every MULTI-BSP algorithm A and for every state in a communication phase,  $comm_A$  preserves the universes and commutes with tree-isomorphisms.

**Proof.** Let  $T = \langle X_0 | \langle X_1 | \overrightarrow{T_1} \rangle, \dots, \langle X_p | \overrightarrow{T_p} \rangle \rangle$  be a node not in a computation phase, so  $\tau_A(T) = \langle X'_0 | \langle X'_1 | \overrightarrow{T_1} \rangle, \dots, \langle X'_p | \overrightarrow{T_p} \rangle \rangle,$ where  $\operatorname{comm}_A(X_0, \dots, X_p) = (X'_0, \dots, X'_p)$ . By the second postulate,  $\tau_A$  preserves the universes, so does

where  $\operatorname{comm}_A(X_0, \ldots, X_p) = (X'_0, \ldots, X'_p)$ . By the second postulate,  $\tau_A$  preserves the universes, so does  $\operatorname{comm}_A$ . Let  $\Phi$  be a tree-isomorphism. Because T is not in a computation phase, by Lemma 5 (with  $\Phi^{-1}$ ),  $\Phi(T)$  is not in a computation phase either, so

$$\tau_A(\Phi(T)) = \left\langle \varphi_0(X_0)' \middle| \langle \varphi_1(X_1)' | \overrightarrow{\Phi_1}(\overrightarrow{T_1}) \rangle, \dots, \langle \varphi_p(X_p)' | \overrightarrow{\Phi_p}(\overrightarrow{T_p}) \rangle \right\rangle,$$

where  $\operatorname{comm}_A(\varphi_0(X_0), \dots, \varphi_p(X_p)) = (\varphi_0(X_0)', \dots, \varphi_p(X_p)')$ . Moreover, by the second postulate,  $\tau_A(\Phi(T)) = \Phi(\tau_A(T)) = \Phi(X_0' | \langle X_1' | \overrightarrow{T_1} \rangle, \dots, \langle X_p' | \overrightarrow{T_p} \rangle)$ , so for every  $0 \le i \le p$ ,  $\varphi_i(X_i)' = \varphi_i(X_i')$ , and thus  $\operatorname{comm}_A \operatorname{commutes}$  with tree-isomorphisms.

**Q27:** Could you justify that your work extends the one about BSP?

Our postulates are a "natural" extension of those in [16, 20].

**Proposition 1 (Hierarchy of models)** A BSP algorithm with a unique processor (p = 1) is a sequential algorithm. A MULTI-BSP algorithm with a single node controlling only leaves is a BSP algorithm. Thus:

$$ALGO_{SEQ} \subseteq ALGO_{BSP} \subseteq ALGO_{MULTI}$$

**Proof (sketch).** ALGO<sub>SEQ</sub>  $\subseteq$  ALGO<sub>BSP</sub> is proven in [20]. Regarding the second inclusion, by ignoring the node and considering the leaves as a tuple, we obtain the same postulates (see Question 23 p.11) as in [20]. The hypothesis on **id** in the second postulate and on the subtrees in the third postulate correspond to the location in the tuples of [20].

**Q28:** That is not a surprise and I am glad that this is the case. And what about the realization of a function of communication ( $comm_A$ ) as in [20]?

This function "simulates" the BSPLIB'S DRMA routines within the ASM framework and we exhibited its exploration witness. That allows a constructive result for BSP because any algorithm using such routines can be truly analysis. This construction matters since BSPLIB is a standard and common library. Sadly, such a library currently does not exist for MULTI-BSP and so we cannot do this work yet right now.

Q29: So for now, you have just an abstract axiomatization. What is the link with actual programming?

We will now follow [16, 20] to provide an operational point of view with the notion of Abstract State Machines (ASMs). And then, we will provide an imperative MULTI-BSP programming core-language and exhibit formally their links.

## **3** Imperative characterization of MULTI-BSP algorithms

#### 3.1 ASM<sub>MULTI</sub> and the MULTI-BSP algorithms

As for the sequential case [16] and the BSP case [20], we first define the  $ASM_{MULTI}$  machines and then we prove that they "capture" [15] the MULTI-BSP algorithms, or in other words, that MULTI-BSP algorithms and  $ASM_{MULTI}$  are the same mathematical objects.

#### 3.1.1 Definition and operational semantics of ASM<sub>MULTI</sub>

#### Q30: For the computing phases, are you using standard sequential ASMs?

Indeed. Sequential ASMs have been defined in [15] to give an operational model to the sequential (small-steps and discrete time) algorithms. We also used them in [20] for the BSP algorithms. In fact, an ASM program contains the full algorithm by giving, at each step of the computation, what needs to be modified in the structures (memories). We refer to [20] (p. 14) for a formal definition of ASM programs II and the sequential operational semantics  $\Delta(\Pi, X)$  (p. 14). We also used such multisets of updates ([20] p. 15) and the transition function  $\tau_{\Pi}$  induced by II on leaves. We assume that  $ASM_{MULTI}$  programs work in a SPMD-like way, which means that at each step of the computation, the  $ASM_{MULTI}$  program II is executed individually on each computing unit.

**Definition 13** An ASM<sub>MULTI</sub> machine M is a triplet  $(S(M), I(M), \tau_M)$  such that:

- 1. S(M) is a set of trees of structures with the same finite signature  $\mathcal{L}(M)$  (containing at least the booleans, the equality and a uniquely interpreted id symbol); S(M) and  $I(M) \subseteq S(M)$  are closed by tree-isomorphisms and subtrees;

- 2. There exists an ASM program  $\Pi$  and a communication function  $comm_M$ : Nodes  $(M) \rightarrow Nodes (M)$ such that  $\tau_M : S(M) \mapsto S(M)$  is defined by induction as:

$$\tau_{M}\langle X \rangle = \langle \tau_{\Pi}(X) \rangle (call \ to \ the \ \Pi \ program)$$

$$\tau_{M}\langle X_{0} | \langle X_{1} | \vec{T_{1}} \rangle, \dots, \langle X_{p} | \vec{T_{p}} \rangle \rangle = \begin{cases} \langle X_{0} | \tau_{M} \langle X_{1} | \vec{T_{1}} \rangle, \dots, \tau_{M} \langle X_{p} | \vec{T_{p}} \rangle \rangle \\ if \ \exists 1 \le i \le p, \tau_{M} \langle X_{i} | \vec{T_{i}} \rangle \neq \langle X_{i} | \vec{T_{i}} \rangle \\ \langle X_{0}^{\prime} | \langle X_{1}^{\prime} | \vec{T_{1}} \rangle, \dots, \langle X_{p}^{\prime} | \vec{T_{p}} \rangle \rangle \end{cases}$$

$$so \ and \ comm_{M}(X_{0}, X_{1}, \dots, X_{p}) = (X_{0}^{\prime}, X_{1}^{\prime}, \dots, X_{p}^{\prime}).$$

where p > 0 and  $comm_M(X_0, X_1, ..., X_p) = (X'_0, X'_1, ..., X'_p)$

- 3.  $comm_M$  verifies that:

- (1) For every state  $\langle X_0 | \langle X_1 | \vec{T_1} \rangle, \dots, \langle X_p | \vec{T_p} \rangle \rangle$  in communication phase, i.e. such that  $\forall 1 \leq i \leq p, \tau_M \langle X_i | \vec{T_i} \rangle = \langle X_i | \vec{T_i} \rangle$ , comm<sub>M</sub> preserves the universes and the arity, and commutes with tree-isomorphisms;

- (2) There exists a finite set of terms  $\Theta(\operatorname{comm}_M)$  such that for every state U and V in communication phase, if they coincide over  $\Theta(\operatorname{comm}_M)$  then for every subtrees  $S \leq U$  and  $W = \operatorname{pos}(S, U; V)$  we have  $\Delta(M, U)_S = \Delta(M, V)_W$ .

We denote by  $ASM_{MULTI}$  the set of such machines. As for the MULTI-BSP algorithms, a state T (a tree) is said final if  $\tau_M(T) = T$ . If U is a state of an  $ASM_{MULTI}$  machine M with an ASM program  $\Pi$ , and  $X \leq U$ is a leaf, then  $\Delta(\Pi, U)_X$  will denote  $\Delta(M, U)_X$  without ambiguity. The last two conditions about the communication function may seem arbitrary, but they are required to ensure that it is not a kind of magic device, and that it performs data-exchanges step-by-step.

**Q31:** If I understand well, some components may wait for lower or upper level components to finish their own supersteps. How do you manage that?

It is the role of the machine to do that. A solution, with the help of a fresh boolean, is to let the machine force the computing units to do empty steps (**par endpar** *i.e.* no update). That corresponds to a busy-looping (spinning). Another solution is considering that it is an implementation issue of the machine: a variety of system calls can block processes (locks, mutex, *etc.*). Notice that the machine is also responsive to shifting of level if necessary.

### $3.1.2 \quad {\rm ASM}_{\rm MULTI} \ captures \ {\rm MULTI-BSP} \ algorithms$

**Q32:** The semantics of your ASMs is close to the superstep postulate and that is not a surprise since the ASM thesis stipulates that ASMs and algorithms are the same objects. In the MULTI-BSP case, how are you going to redo that?

In the same way as for the BSP algorithms [20]. We first used the fact that the transitions of a

processor in a computation step can be captured by an ASM program (Lemma 6). Then, we prove in Corollary 3 that this potentially infinite number of ASM programs can be reduced to a finite number. Finally, we merge these programs into one (in normal form) in order to prove in Proposition 2 that  $ASM_{MULTI}$  captures the computation steps of MULTI-BSP algorithms. Finally, we prove that  $ALGO_{BSP} = ASM_{BSP}$ .

**Lemma 6 (Each Local Transition is Captured by an** ASM) Let A be a MULTI-BSP algorithm. For every state U and leaf  $X \leq U$  in a computation phase, there exists an ASM program  $\Pi_X$  such that  $Read(\Pi_X) \subseteq \Theta(A)$  and  $\Delta(\Pi_X, X) = \Delta(A, X)$ .

**Proof (sketch).** The proof is similar as in the sequential case [16, 19], and uses Lemma 1 for critical elements, and Lemma 2 to obtain a finite program  $\Pi_X$ .

As in [15, 20], to narrow the number of relevant states we use the *finiteness* of the exploration witness  $\Theta(A)$ . For every memory X, we denote by  $E_X$  the equivalence relation on pairs  $(\theta_1, \theta_2)$  of terms in  $\Theta(A)$  defined by:

$$E_X(\theta_1, \theta_2) \stackrel{\text{def}}{=} \begin{cases} \mathbf{true} & \text{if } \overline{\theta_1}^X = \overline{\theta_2}^X \\ \mathbf{false} & \text{otherwise} \end{cases}$$

**Corollary 3 (Syntactically equivalent memories)** Let A be a MULTI-BSP algorithm, U and V be two states, and  $X \leq U$  and  $Y \leq V$  be two leaves. If X and Y are in a computation phase and  $E_X = E_Y$  then:

$$\Delta(\Pi_X, V)_Y = \Delta(A, V)_Y$$

**Proof (sketch).** By definition of the operational semantics of  $ASM_{MULTI}$ ,  $\Delta(\Pi_X, U)_X = \Delta(\Pi_X, X)$ and  $\Delta(\Pi_X, V)_Y = \Delta(\Pi_X, Y)$ . Because X and Y are in a computation phase, by Corollary 1 p.12,  $\Delta(A, U)_X = \Delta(A, X)$  and  $\Delta(A, V)_Y = \Delta(A, Y)$ . Then the proof is identical to the sequential case [16].

**Proposition 2** (ASM<sub>MULTI</sub> capture Computations) For every MULTI-BSP algorithm A, there exists an ASM program  $\Pi_A$  such that for every state U and leaf  $X \leq U$  in a computation phase:

$$\Delta(\Pi_A, U)_X = \Delta(A, U)_X$$

**Proof** (sketch). The proof is similar to [16, 20] by using Corollary 3 to obtain subprograms and the finite exploration witness in the third Postulate to obtain a finite global program.  $\Box$

#### Theorem 1 $ALGO_{MULTI} = ASM_{MULTI}$

**Proof (sketch).** The proof is similar to [16, 20] and is made by mutual inclusion. 1) A MULTI-BSP algorithm A is an  $ASM_{MULTI}$  machine with the same (initial and standard) states and communication function, and using the program  $\Pi_A$  from Proposition 2 during the computation phases (and using technical Lemma 1, such computations preserve the universes and commute with tree-isomorphisms). Moreover, according to Corollary 2 the communication function preserves the universes and commutes with tree-isomorphisms. Finally, the other properties from Definition 13 are verified according to the postulates. 2) An  $ASM_{MULTI}$  machine M with an ASM program  $\Pi$  verifies the fourth postulate, in particular its exploration witness is the closure by subterms of  $\Theta(\Pi) \cup \Theta(\mathbf{comm}_M)$ , and thus is a MULTI-BSP algorithm.

#### Q33: It is a little long. Is this really useful?

Yes. But to our purpose, ASMs are *intermediary* objects only. Algorithmic completeness of programming languages is the main goal. How communications are organized (in a nested manner) is defined in both postulates and  $ASM_{MULTI}$  in a similar way so that does not modify how computations are performed. It is the communication function that decides how to shift levels and how terms are sent (depending on the content of the memories/structures which, of course, have been modified by the leaves during the execution of the program  $\Pi$  itself).

#### **3.2** Programming MULTI-BSP algorithms and algorithmical completeness

**Q34:** That is a curious computation model to let an abstract function manage the level and how to send data. Any programmer's code would rather contain explicit shifting of level and letting the function of communication order the data. Can you elaborate on that?

Indeed. The ASM program must modify the structures in order to initiate a shift of levels. Furthermore, the ASM execution flow is close to "low level" assembly codes and thus lacks control flow structures for programming algorithms in as usual. So most programmers naturally want a finer control and prefer using a programming language to get their algorithms implemented. We now present an SPMD extension of the standard IMP core-language. The IMP programs are common sequences of commands, which are standard control flow statements (conditionals and unbounded loop) or assignments (sequential updates), so this programming language can be seen as minimal.

#### 3.2.1 Semantics of a core imperative MULTI-BSP language

#### **Q35:** Why not directly choose a mainstream language such as C or JAVA?

There are too many *constructions* on such languages and thus when doing proofs on them, some cases may be missed. A theorem prover such as COQ can help you to do that but that is not the goal of this work. A core language is sufficient because we can apply the following results to every mainstream language with at minimal such control flows. Let us introduce you to  $IMP_{MULTI}$ , our core imperative language [19] (inspired by the library of [30]).

#### Definition 14 (Syntax)

commands:

$$c \stackrel{\text{def}}{=} f(\theta_1, \dots, \theta_\alpha) := \theta_0$$

$| \text{ if } F \{P_1\} \text{ else } \{P_2\}$

$| \text{ while } F \{P\}$

$| \text{ comm } | \text{ up } | \text{ down}$

$programs : P \stackrel{\text{def}}{=} \text{ end } | c; P$

where F is a formula ([20] p. 7), f has arity  $\alpha$  and  $\theta_0, \theta_1, \ldots, \theta_{\alpha}$  are terms. **comm** is used to perform one step of communication whereas **up** and **down** are used to shift of level. To improve readability we do not write the **end** when there is no ambiguity.

Q36: I imagine better primitives such as the use of synchronizing primitives (like BSP's bsp\_sync()) to control the shifts of levels (flow up and down) on the MULTI-BSP trees and communications between levels such as upward(value v) and downward(value v, int id) [30]. What about such primitives?

These primitives are for programs that are executed at each level of the *d*-trees, even on nodes. Assuming that only "scattering and gathering" of values are allowed as "computations" on nodes, the function of communication  $\mathbf{comm}_M$  can simulate them easily. Again, we use such an abstract function in order not to be restricted by a particular library. Take for example the upward routine. It allows us to upward values from the memories of a level *i* to the memory of *i*-1. In IMP<sub>BSP</sub>, we should have a code such as: up; while notEmpty(buffer) { if manage(id) { $comm_M;$  }

where the *buffer* contains the values to upward and *manage* is a function that determines if the leaf handles or not the node at the given level (being the "master" [30]). In our simulation, on each leaf, the  $ASM_{MULTI}$  program will run the above code where the values from the buffers are communicated step-by-step by the **comm**<sub>M</sub>.

#### Q37: And what about recursive calls on the d-trees of [2] or [30]?

Both are interesting programming languages that both allow to clearly distinguish what is executed on the nodes or leaves and how to send data between levels. They can be simulated by the use of the **down/up** primitives. A stack can also be used to keep track of the recursive calls of [2].

**Q38:** So, what is the formal operational semantics of such a core language?

The operational semantics of the local computations is formalized by a state transition system [19], where a state of the system is a pair  $P \star X$  of a program P and a memory (structure) X, and a transition  $\succ$ is determined only by the head command and the current structure. Here two examples of rule [20] (p. 31) (where  $\oplus$  stands for an update of structure and  $\overline{\theta_{\alpha}}^{X}$  for an interpretation of a term  $\theta$  in the structure X):

$$f(\theta_1, \dots, \theta_\alpha) := \theta_0; P \star X \implies P \star X \oplus (f, \overline{\theta_1}^X, \dots, \overline{\theta_\alpha}^X, \overline{\theta_0}^X)$$

while  $F\{P_1\}; P_2 \star X \implies P_1$ ; while  $F\{P_1\}; P_2 \star X$  if  $\overline{F}^X$  = true

Other rules are described in [20] (p. 31) and are without surprise. It is easy to show that this transition system is deterministic. The local states without successors are **sync**;  $P \star X$  (where **sync** is **comm** or **up** or **down**) and **end**  $\star X$ . We use the same notation as in [20] about  $\succ_t$  (the succession of t steps) and  $\Delta(P, X)$  (the succession of updates made by P on X).

Q39: Standard. But for true MULTI-BSP programs?

Firstly, for a tree T, we note  $\widetilde{P}_T$  (resp.  $\widetilde{I}_T$  and  $\widetilde{T}$ ) the tuple of programs  $(P_1, \ldots, P_\beta)$  (resp. level identifiers, structures) where each  $P_i$  (resp.  $I_i, X_i$ ) is a program (resp. identifier, structure) of a leaf of the tree T in a standard breadth-first traversal (in order of the id). The operational semantics of  $\text{IMP}_{\text{MULTI}}$ is also formalized by a state transition system, where a state of the system is a triple  $\widetilde{I}_T \star \widetilde{P}_T \star T$  where T is a tree of structures. The level identifiers (that take values from 1 to d) will be used to handle in which level the program manipulates a node and so, in different branches of T, these identifiers could be different. In practice, a component can choose a single representative leaf to handle the computations needed by the communications (contrary to this semantics where all processors on the same branch have a code that runs and manages the communication of the node at a given nested-superstep). It is to notice that the **comm**, **down** and **up** are synchronous and global to all the computing units of the same branch (accordling to the level identifiers); So if one diverges the overall computing diverges and if one performs a routine different than those of others then the overall machine fails.

If for a leaf  $\langle X \rangle$ ,  $\vec{I}_{\langle X \rangle} = (1)$ , then  $\vec{P}_{\langle X \rangle}$  is said to be in a **computation phase**. For a node  $\langle X | \vec{T} \rangle = T$ , if  $\vec{P}_T = (P_1, \ldots, P_\beta)$ , we say that  $\vec{P}_T$  is also in a computation phase if  $P_i \neq \text{sync}; P \star X$ , where sync = comm, up or down. Otherwise the tree is in a communication phase. We define next(sync; P) = P and next(end) = end. We also note  $\overrightarrow{\text{next}}(\ldots, P^i, \ldots) = (\ldots, \text{next}(P^i), \ldots)$ . We denote by  $\overrightarrow{\succ}_s$  the reduction at node level s which is defined as  $\overrightarrow{\succ}$  in [20] (p. 32) but where we are using  $\succ^s$  instead of  $\succ$  and  $\succ^s$  is defined as follow:

$P \star X \succ^{s} \tau_{X}(P) \star \tau_{P}(X)$  if  $P \star X$  has a successor (without being an update) and  $s \neq 1$  $P \star X = \tau_{X}(P) \star \tau_{P}(X)$  otherwise

**Definition 15 (A semantics machine for the** MULTI-BSP **core-language)** An IMP<sub>MULTI</sub> machine M is a quintuplet  $(S(M), I(M), P_{init}, comm_M, \widetilde{I}_{I(M)})$ :

- 1. S(M) is a set of trees of structures with the same finite signature  $\mathcal{L}(M)$  (with at least the booleans, the equality and a uniquely interpreted **id** symbol);

- 2. The initial states of the transition system have the form  $\widetilde{I}_T \star \widetilde{P}_T \star T$ , where  $T \in I(M) \subseteq S(M)$  and  $\widetilde{P}_T = (P_{init}, \dots, P_{init}) \ (P_{init} \ on \ each \ leaf);$

- 3.  $P_{init}$  is a program with terms from  $\mathcal{L}(M)$ ;

- 4.  $comm_M$ : Nodes (M)  $\rightarrow$  Nodes (M) verifies (as in Definition 13) that:

- (1) For every state  $\widetilde{I}_T \star \widetilde{P}_T \star T$  such that  $\widetilde{P}$  is in a communication phase,  $comm_M$  preserves the universes and the arity (size of tuples), and commutes with tree-isomorphisms;

- (2) There exists a finite set of terms  $\Theta(\operatorname{comm}_M)$  such that for every state  $\widetilde{I}_T \star \widetilde{P}_T \star T$  and  $\widetilde{J}_U \star \widetilde{Q}_U \star U$ , if  $\widetilde{P}_U$  and  $\widetilde{Q}_U$  are in a communication phase,  $T \stackrel{\circ}{=} U$  and T and U coincide over  $\Theta(\operatorname{comm}_M)$  then for each  $S = \langle X_0 | \langle X_1 | \overrightarrow{T}_1 \rangle, \cdots, \langle X_p | \overrightarrow{T}_p \rangle \rangle \leq T$  and  $V = \operatorname{pos}(S, T; U) = \langle Y_0 | \langle Y_1 | \overrightarrow{U}_1 \rangle, \cdots, \langle Y_p | \overrightarrow{U}_p \rangle \rangle$ we have  $\operatorname{comm}_M(X_0, X_1, \cdots, X_p) \Theta(X_0, X_1, \cdots, X_p) = \operatorname{comm}_M(Y_0, Y_1, \cdots, Y_p) \Theta(Y_0, Y_1, \cdots, Y_p)$ , where  $\Theta$  is defined in [20] (p. 25).

- **Q40:** Are they limitations on the  $\widetilde{I}_T$ ? They look like any identifier and so processors can do whatever. Indeed, but the operational semantics will forget to do whatever. If there is not computation from

an initial state, it is just an unless algorithm.

**Q41:** And why such a definition of  $comm_M$ ?

As explained in [20], such limitations are used to forbid this function to do whatever, especially an unbounded reduction on the structures.

We denote by level(S,T) at which level S is in T if  $S \leq T$ . For every  $T \stackrel{*}{=} U$  and  $s \in 1 \dots d$  (a level identifier, where d is the depth), the operational semantics  $\stackrel{\sim}{\succ}$  of  $IMP_{MULTI}$  denoted  $\widetilde{I}_T \star \widetilde{P}_T \star T \stackrel{\sim}{\Rightarrow} \widetilde{J}_U \star \widetilde{Q}_U \star U$  is defined with three cases:

**Communication case:**  $S = \langle X_0 | \langle X_1 | \vec{T_1} \rangle, \dots, \langle X_p | \vec{T_p} \rangle \rangle \leq T$  where  $\vec{I}_S = (s, \dots, s)$  and level(S, T) = s and  $\vec{P}_S = (P_1, \dots, P_\beta)$  (where for all  $i P_i = \text{comm}; P$ ), then  $\vec{I}_S = \vec{J}_S$  and  $\vec{Q}_V = \overrightarrow{\text{next}}(\vec{P}_S)$  and if  $V = \langle Y_0 | \langle Y_1 | \vec{U_1} \rangle, \dots, \langle Y_p | \vec{U_p} \rangle \rangle = \mathbf{pos}(T, S; U)$  then  $U_1 = T_1 \cdots U_p = T_p$  and  $(Y_0, Y_1, \dots, Y_p) = \mathbf{comm}_M(X_0, X_1, \dots, X_p);$

**Shifting case:**  $S = \langle X_0 | \vec{T} \rangle \leq T$  where  $\vec{I}_S = (s, \dots, s)$  and level(S, T) = s and  $\vec{P}_S = (P_1, \dots, P_\beta)$  (where for all  $i P_i = \mathbf{up}; P$  or  $P_i = \mathbf{down}; P$ ), then  $\vec{Q}_V = \overrightarrow{\mathbf{next}}(\vec{P}_S)$  and if  $\langle V | \vec{U} \rangle = \mathbf{pos}(T, S; U)$  then  $\vec{U} = \vec{T}$  and  $\vec{J}_S = \vec{I}_S \pm 1$  (for each  $s_i$  of  $\vec{I}_S$ ) according that **down** (resp.  $\mathbf{up}$ ) is the next command and if  $s \neq 1$  (resp.  $s \neq d$ );

**Computation case:** If  $S = \langle X \rangle$  then  $\widetilde{I}_S = \widetilde{J}_S = (1)$  and if  $\langle Y \rangle = \mathbf{pos}(T, B; U)$  and if  $\widetilde{P}_S = P$  then  $Y = \tau_P(X)$ and  $\widetilde{Q}_{\langle Y \rangle} = \tau_X(P)$ . If  $S = \langle X_0 | \vec{T} \rangle \leq T$  where  $\widetilde{I}_S = (s, \dots, s)$  and level(S, T) = s and  $\widetilde{P}_S = (P_1, \dots, P_\beta)$  (where for all  $i P_i \neq \mathbf{sync}; P$ ) then  $\widetilde{P}_S \star \widetilde{S} \Rightarrow_s \widetilde{Q}_V \star \widetilde{V}$  if  $V = \mathbf{pos}(T, S; U)$ .

A state  $\tilde{I}_T \star \tilde{P}_T \star T$  is said *final* if all components are in a communication phase (performing nothing). We say that, on local memories (tree) T and initial level identifier  $\tilde{I}_T$ , the (initial) program  $P_{init}$  terminates globally if there exists  $t, \vec{P'}$  and U such that  $\tilde{I}_T \star P_{init} \star X \approx_t \tilde{I'}_U \star \vec{P'} \star U$ , where  $U \cong T$ and  $\vec{P'} = \vec{P'}_U$  and it is a final state. We denote by time( $P_{init}, I, X$ ) the smallest of those t, by assuming (as in the Definition 2.2.1) potential infinite duration if  $P_{init}$  does not terminate globally (there is an infinite number of nested supersteps or during one of them, at least, the computations of one processor diverges). Moreover, because the reached state is a fixpoint, U is unique, and will be denoted by  $\vec{P}_{init}(I, X)$ .

**Q42:** Why select all the leaves of a branch to perform the node communications rather than use a single leaf (a master) as in [2] or [30]?

To be sure that they are all at the right level during communication. That is thus only for semantics convenience. Which leaf is the "master" and truly manipulated the memory is implementation dependent. Moreover, that allows us to formally specify when the "waiting" is not implemented with system calls but with a busy-looping.

Q43: So, are there computations on the nodes in your model?

As explained before, in our version of the MULTI-BSP model, nodes are memories only and so yes, only communications can occur. But how these communications are managed (and what are they doing) is thus the responsibility of the **comm**<sub>M</sub> function. For our core imperative language, to allow executing an unbound number of calls of this function and choosing how to shift levels, "while" and "if" statements are possible on nodes but no assignment (local modification of the structure/memory which can be considered as a "distant writing").

**Q44:** You forbid local assignments (on a leaf) when it is indicated that it is a node reduction (communication).

Indeed. Without that, during any nested superstep, a leaf can modify its own memory and thus not respecting the MULTI-BSP model of execution.

**Q45:** But then it is impossible for the  $comm_M$  function to be well executed. For example, if  $comm_M$  is inside a loop in order to send a complex data in several steps (e.g partitioned a list), then there is no way to write the current memory of the leaf to manage this number of steps. And it is unrealistic to use only the node memory to perform such a work. Could you elaborate on that?

You are right. By leaving a control to the programmer over the communications, it is necessary to "execute" some codes. Because leaf updates are not allowed, we need to allow the function of communications to perform some modifications on the memories of the leaves. But these updates must not allow the processors to enter again a local computing phase because that would break the MULTI-BSP execution model. These modifications must be used for the communications only. To do that we first note  $descendants(T) = (X_1, \dots, X_\beta)$  all the leaf structures (in a breadth-first order of the **id**) of a tree Twhich is not a parent of leaves. If  $\forall X_i \in descendants(T) \tau_{\Pi}(X_i) = X_i$  then every computing unit has finished its computation steps. Then, we modified **comm**<sub>M</sub> so that now  $(Y_0, Y_1, \dots, Y_p, descendants(U)) =$ **comm**<sub>M</sub> $(X_0, X_1, \dots, X_p, descendants(T))$  so that  $\forall X \in (descendants(T)), \tau_P(X) = \emptyset$  (a new local computing phase is still impossible). Finally, to keep an equivalence with your previous models, we need the same slight change of the definition of **comm**<sub>A</sub> in the postulates as well as in the ASM<sub>MULTI</sub> machine. Notice that the previous results are still valid, such a modification does not affect how the computations are organized, only what the communication can change. But we agree that this is an *unsatisfactory trick* but it is necessary if you want to be able to do several communication steps or user-programmed shifts of level.

Q46: Would not that hide some communications between the nodes and the leaves?

Admitting this new communication functions, yes. But that could be part of the  $\mathbf{g}_i$  parameters. Notice that the semantics forbids assignments during the node superstep, only  $\mathbf{comm}_A$  can modifying the structures. For example, such modifications could be used when *serializing* values (mainly an internally graph traversing) when using functional or object programming languages [2]. One can also imagine some restrictions on  $\mathbf{comm}_A$ . We currently prefer to stay as general as possible. We will discuss this issue in future work. Now let us present our final result.

#### 3.2.2 Algorithmic completeness of a core-imperative MULTI-BSP language

Now that we have defined our core MULTI-BSP programming language as a common imperative model of computation, we prove in the following that  $ASM_{MULTI}$  algorithmically simulates  $IMP_{MULTI}$  and *vice-versa*. Q47: "Algorithmically simulates", what is it?

We say that a computation model  $M_1$  can algorithmically simulate another computation model  $M_2$ if for every program  $P_2$  of  $M_2$  there exists a program  $P_1$  of  $M_1$  producing "similar" executions from the initial states.