## Packaged Ga2O3 Schottky Rectifiers with Over 60 A Surge Current Capability

Ming Xiao, Boyan Wang, Jingcun Liu, Ruizhe Zhang, Zichen Zhang, Chao Ding, Shengchang Lu, Kohei Sasaki, Guo-Quan Lu, Cyril Buttay, et al.

### ► To cite this version:

Ming Xiao, Boyan Wang, Jingcun Liu, Ruizhe Zhang, Zichen Zhang, et al.<br/>. Packaged Ga2O3 Schottky Rectifiers with Over 60 A Surge Current Capability. IEEE Transactions on Power Electronics, in<br/>Press, 10.1109/TPEL.2021.3049966 . hal-03186511

## HAL Id: hal-03186511 https://hal.science/hal-03186511

Submitted on 8 Apr 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Packaged Ga<sub>2</sub>O<sub>3</sub> Schottky Rectifiers with Over 60 A Surge Current Capability

Ming Xiao, Boyan Wang, Jingcun Liu, Student Member, IEEE, Ruizhe Zhang, Student Member, IEEE, Zichen Zhang, Chao Ding, Shengchang Lu, Kohei Sasaki, Guo-Quan Lu, Fellow, IEEE, Cyril Buttay, Senior Member, IEEE, and Yuhao Zhang, Member, IEEE

Abstract - Ultra-wide-bandgap gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) devices have recently emerged as promising candidates for power electronics; however, the low thermal conductivity  $(k_{\rm T})$  of Ga<sub>2</sub>O<sub>3</sub> causes serious concerns about their electrothermal ruggedness. This work presents the first experimental demonstrations of largearea Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes (SBDs) packaged in the bottom-side-cooling and double-side-cooling configurations, and for the first time, characterizes the surge current capabilities of these packaged Ga<sub>2</sub>O<sub>3</sub> SBDs. Contrary to popular belief, Ga<sub>2</sub>O<sub>3</sub> SBDs with proper packaging show high surge current capabilities. The double-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBDs with a 3×3 mm<sup>2</sup> Schottky contact area can sustain a peak surge current over 60 A, with a ratio between the peak surge current and the rated current superior to that of similarly-rated commercial SiC SBDs. The key enabling mechanisms for this high surge current are the small temperature dependence of on-resistance, which strongly reduces the thermal runaway, and the double-side-cooled packaging, in which the heat is extracted directly from the Schottky junction and does need to go through the low-k<sub>T</sub> bulk Ga<sub>2</sub>O<sub>3</sub> chip. These results remove some crucial concerns regarding the electrothermal ruggedness of Ga<sub>2</sub>O<sub>3</sub> power devices and manifest the significance of their die-level thermal management.<sup>1</sup>

*Index Term* – ultra-wide bandgap, gallium oxide, surge current, ruggedness, package, thermal management, simulation

#### I. INTRODUCTION

Ultra-wide-bandgap (UWBG) semiconductor gallium oxide  $(Ga_2O_3)$  is a promising material for next-generation power electronics due to its high critical electrical field  $(E_C)$ , controllable doping, excellent thermal stability, and the availability of large-diameter wafers by the melt growth [1], [2]. Recently, kilovolt-class Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes (SBDs) [3], [4] and power FinFETs [5], [6] were demonstrated with a peak electric field (E-field) in Ga<sub>2</sub>O<sub>3</sub>, exceeding the  $E_C$  of GaN and SiC. However, most of the reported Ga<sub>2</sub>O<sub>3</sub> devices have a small current, and only a few large-area Ga<sub>2</sub>O<sub>3</sub> devices have been demonstrated with a current over 1 Amp [7], [8].

A fundamental challenge for the current scaling in  $Ga_2O_3$ devices is the low thermal conductivity ( $k_T$ ) of  $Ga_2O_3$  (0.1-0.3 Wcm<sup>-1</sup>K<sup>-1</sup> [1]), which is about 1/6 of the  $k_{\rm T}$  of Si, 1/10 of GaN, and 1/20 of SiC. The high thermal resistance of the Ga<sub>2</sub>O<sub>3</sub> die makes its thermal management very challenging. While some modeling and simulation works have investigated the thermal management of Ga<sub>2</sub>O<sub>3</sub> devices [9]–[12], no experimental demonstrations of the packaging and thermal management of large-area Ga<sub>2</sub>O<sub>3</sub> devices have been reported to date.

Due to the low  $k_{\rm T}$  of Ga<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> devices are often perceived to have very limited electrothermal ruggedness. Surge current ruggedness is essential for power applications, when the device needs to temporarily sustain a current higher than the rated one. The surge current value is listed in a diode's datasheet and is usually measured in a half-sinusoidal currentpulse according to JEDEC standards [13]. While the surge current ruggedness has been extensively studied for SiC diodes [14], [15], no such tests have been reported for Ga<sub>2</sub>O<sub>3</sub> devices.

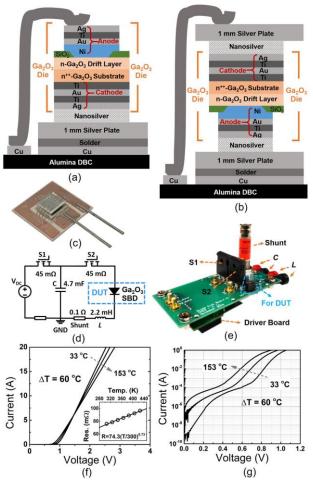

This work presents the first experimental study on the surge current capability of large-area, packaged  $Ga_2O_3$  devices. Vertical  $Ga_2O_3$  SBDs were fabricated with a current over 10 A. Two packaging structures were designed and prototyped, one based on the bottom-side-cooling scheme where the heat must diffuse through the entire  $Ga_2O_3$  chip before reaching the baseplate (Fig. 1(a)), and the other based on the double-side-cooling scheme (Fig. 1(b)), which allows the heat dissipation through the  $Ga_2O_3$  chip and directly from the Schottky junction simultaneously. Despite the low  $k_T$  of  $Ga_2O_3$ , the double-side-cooled  $Ga_2O_3$  chip showed a high surge current capability over 60 A. The electrothermal dynamics in the packaged  $Ga_2O_3$  SBDs were also studied using mixed-mode simulations.

#### II. DEVICE FABRICATION, PACKAGING, AND TEST SETUP

The Ga<sub>2</sub>O<sub>3</sub> wafer consists of a 10- $\mu$ m Si-doped n-Ga<sub>2</sub>O<sub>3</sub> layer (net donor concentration ~2×10<sup>16</sup> cm<sup>-3</sup>) grown on a 2-inch n<sup>+</sup>-Ga<sub>2</sub>O<sub>3</sub> (001) substrate (Sn: 1.3×10<sup>19</sup> cm<sup>-3</sup>). The substrate was thinned down to a thickness of 500  $\mu$ m. The device fabrication is similar to those reported in [3], [16]. A Ti/Au (30/150 nm) Ohmic contact was formed as the cathode. 1- $\mu$ m-thick SiO<sub>2</sub> was

Ming Xiao, Boyan Wang, and Jingcun Liu contributed equally to this work. (*Corresponding authors: Yuhao Zhang, Cyril Buttay, Guo-Quan Lu*).

Ming Xiao, Boyan Wang, Jingcun Liu, Ruizhe Zhang, Zichen Zhang, Chao Ding, Shengchang Lu, Guo-Quan Lu, and Yuhao Zhang are with the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA (e-mail: mxiao@vt.edu; wangboyan@vt.edu; jcliu@vt.edu; rzzhang@vt.edu; zichen2013@vt.edu; dingchao@vt.edu; lsheng1@vt.edu; gqlu@vt.edu; yhzhang@vt.edu).

Jingcun Liu is also with the School of Electrical Engineering, Xi'an Jiaotong University, Xi'an 710049, China.

Kohei Sasaki is with Novel Crystal Technology, Inc., Sayama 350-1328, Japan (email: sasaki@novelcrystal.co.jp).

Cyril Buttay is with Univ Lyon, INSA-Lyon, CNRS, Laboratoire Ampere, 69622 Villeurbanne, France (email: cyril.buttay@insa-lyon.fr).

Fig. 1. Schematic of the Ga<sub>2</sub>O<sub>3</sub> SBDs with (a) bottom-side-cooling package and (b) double-side-cooling package. (c) Photo of a double-side-packaged SBD. (d) Circuit diagram and (e) photo of the surge current test board. Forward I-V characteristics of the packaged Ga<sub>2</sub>O<sub>3</sub> SBDs at 33-153 °C in the (f) linear region and (g) subthreshold region. [inset of (f)] temperaturedependence of the differential  $R_{on}$  and the power law fitting.

deposited as the field-plate (FP) dielectrics, followed by a wet etch to produce a ~15° FP bevel angle. An Ni/Au stack was deposited as the Schottky and FP metals. 100-nm Ti and 200nm Ag were deposited on both sides as the contact layer for the device packaging that followed. The Schottky contact area is  $3\times3$  mm<sup>2</sup>, and the total sample size is about  $4.5\times4.5$  mm<sup>2</sup>.

A nanosilver paste from NBE Technologies was used for the die attach by a pressureless sintering process in air [17], [18]. The sintered-silver joint has a high melting temperature of 960 °C and a high thermal conductivity over 1 Wcm<sup>-1</sup>K<sup>-1</sup>. A laser-cut mask was used to stencil-print a 50-µm thick nanosilver paste on bonding pads with minimal lateral seepage. The sintering profile was: from room temperature to 250 °C at a ramp rate of 6 °C/min and held at 250 °C for 30 minutes, followed by air cool to room temperature. For the single-side-cooled package, the cathode of the Ga<sub>2</sub>O<sub>3</sub> chip was sintered on a 1-mm thick Ag plate, and wire-bonds were attached on the top anode. For the double-side-cooled package, each terminal of the Ga<sub>2</sub>O<sub>3</sub> chip was sintered on a 1-mm thick Ag plate. The packaged chips were then soldered on an alumina direct-bond-copper (DBC) substrate and electrically connected through two

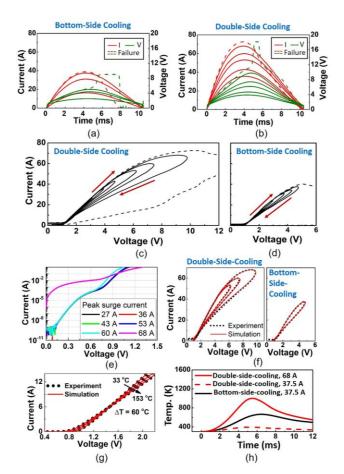

Fig. 2. Current/voltage waveforms of the (a) bottom-side-cooled and (b) double-side-cooled  $Ga_2O_3$  SBDs in the surge current tests. I-V loops of the (c) double-side-cooled and (d) bottom-side-cooled devices. (e) Transfer characteristics in the subthreshold region after each surge current test. Simulation model calibration for the (f) surge I-V loops and (g) static I-V characteristics. (h) Simulated junction temperature in the surge current tests for bottom-side-cooled and double-side-cooled  $Ga_2O_3$  SBDs.

leads to a curve tracer and a surge current test board. Fig. 1(c) shows a double-side-cooled Ga<sub>2</sub>O<sub>3</sub> package ready for test.

It should be noted that the cooling structure in this work is discussed in the context of a 10-ms transient instead of the steady state. The thickness of Ag plate (1 mm) is designed to ensure that the heat diffusion is confined in the plate during the 10-ms transient (validated in the simulation in Section III, see Fig. 3). The bottom solder and DBC in both packages as well as the top wire bond in the double-side package do not contribute to the heat dissipation during the 10-ms transient.

Fig. 1(d) and (e) show the surge-current test circuit and the prototype, respectively. The test circuit is similar to the one reported in [15]. A 10-ms-wide half-sinusoidal current waveform was produced by a resonance circuit (a 2.2-mH inductor and a 4.7-mF capacitor). SiC MOSFETs were used as the control switches. The peak surge current ( $I_{peak}$ ) was stepped up by increasing the power supply voltage. The device voltage was monitored by a differential probe, and the current was sensed by a 0.1- $\Omega$  coaxial current test, the device was measured on the curve tracer to identify any possible degradation.

#### III. EXPERIMENTAL RESULTS AND PHYSICAL ANALYSIS

Fig. 1(f) and (g) show the temperature-dependent I-V curves of the packaged large-area Ga<sub>2</sub>O<sub>3</sub> SBDs in the linear region and the subthreshold region, respectively. The I-V characteristics of the SBDs in both packages are almost identical. The current on/off ratio is ~10<sup>9</sup> at 33 °C and maintains ~10<sup>7</sup> at 153 °C, suggesting the good thermal stability of the Schottky contact. The turn-on voltage is ~0.85 V at 33 °C and decreases to ~0.65 V at 153 °C. The current reaches 13 A (144 A/cm<sup>2</sup>) at a forward voltage of 2 V. The temperature dependence of on-resistance ( $R_{on}$ ) can be fitted by a power law with a temperature coefficient ( $\alpha$ ) of 0.73. This  $\alpha$  is much smaller than the one reported for SiC SBDs (2.95 [19]), suggesting the superior thermal stability of Ga<sub>2</sub>O<sub>3</sub> SBDs. This could be attributed to the small temperature dependence of mobility in Ga<sub>2</sub>O<sub>3</sub> [12] and the increased donor ionization at high temperatures [16].

The breakdown voltage (BV) of the fabricated  $Ga_2O_3$  SBDs was measured to be ~700 V, similar to the one reported in [16] using a similar edge termination, regardless of the packaging structures. Note that this BV is limited by the edge termination and has not reached the material limit. If suitable termination were used, e.g., the one reported in [3] that produces an average junction field of 3.4 MV/cm, the BV of the chip used in this work could reach 1600 V.

Fig. 2(a) and (b) show the current/voltage waveforms in a set of surge current tests with increased  $I_{\text{peak}}$  for the Ga<sub>2</sub>O<sub>3</sub> SBDs with both package structures. The Ga2O3 SBD with the bottomside-cooling package was found to fail in the surge test with an  $I_{\text{peak}}$  of 39 A. The failure  $I_{\text{peak}}$  is much higher (70 A) in the double-side-cooled SBD. Fig. 2(c) and (d) show the surge I-V loops of the SBDs with both types of packages. Both I-V loops are clockwise, due to the increased  $R_{on}$  at higher  $T_j$ , and the loop area is correlated to the  $R_{on}$  (and  $T_j$ ) increase in the surge test. With a similar  $I_{\text{peak}}$  (e.g., 30 A), the loop area of the double-sidecooled SBD is smaller than that of the bottom-side-cooled SBD, suggesting a smaller  $T_i$  increase. In addition, the last safewithstand I-V loop of the double-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBD (I<sub>peak</sub>  $\sim$  68 A) shows a larger area than that of the bottom-side-cooled SBD ( $I_{\text{peak}} \sim 37.5 \text{ A}$ ), implying that the double-side-cooled SBD can sustain a higher  $T_j$ . Fig. 2(e) shows the transfer characteristics of the double-side-cooled SBD after each surge test with increased Ipeak. Almost no device degradation is shown

TABLE I. KEY MODELS IN THE ELECTROTHERMAL SIMULATION

| Parameter                                                                                            | Models and key parameters                                                                      |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| $\begin{array}{c} Ga_2O_3 \text{ electron mobility} \\ (cm^2V^{\text{-1}}s^{\text{-1}}) \end{array}$ | Klaassen's Unified Low-Field Mobility Model<br>mumaxn.kla = 120 (drift region) /30 (substrate) |  |  |

| $Ga_2O_3 k_T (Wcm^{-1}K^{-1})$                                                                       | $k(T_{\rm L}) = 0.1 \times (T_{\rm L}/300)^{-0.95} (T_{\rm L}: \text{ lattice temp.})$         |  |  |

| Ga <sub>2</sub> O <sub>3</sub> heat capacity<br>(JK <sup>-1</sup> )                                  | $C(T_{\rm L}) = 0.2038 + 0.00174 \times T_{\rm L} - 1.459 \times 10^{-6} \times T_{\rm L}^2$   |  |  |

| Nano-Ag $k_{\rm T}$ (Wcm <sup>-1</sup> K <sup>-1</sup> )                                             | $k(T_{\rm L}) = 1 \times (T_{\rm L}/300)^{-0.14}$                                              |  |  |

| Nano-Ag thermal contact resistance                                                                   | 0.087 K·cm <sup>2</sup> /W                                                                     |  |  |

| Thermal boundary condition                                                                           | 0.2 W/(cm <sup>2</sup> ·K) heat transfer coefficients at the exterior top/bottom surfaces      |  |  |

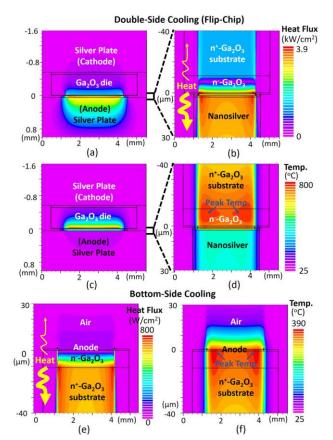

Fig. 3. Simulated heat flux contour in the (a) entire packaged device and (b) device junction region, and simulated temperature distributions in the (c) entire device and (d) junction region, in a double-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBD at the peak  $T_j$  transient in the surge current test with 68 A  $T_{peak}$ . Simulated (e) heat flux contour and (f) temperature contour in the junction region of the bottom-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBD at the peak  $T_j$  transient in the surge current test with 37.5 A  $T_{peak}$ .

with  $I_{\text{peak}}$  up to 60 A. At 68 A  $I_{\text{peak}}$ , higher leakage current is present, suggesting the degradation in the Schottky contact.

To understand the electrothermal dynamics within the device structure, mixed-mode electrothermal TCAD simulations were performed in Silvaco Atlas, which solves the self-consistent electrothermal device models [20] in a circuit arrangement consistent with that shown in Fig. 1(d). Temperature-dependent  $k_{\rm T}$ , heat capacity, and electron mobility models were employed for Ga<sub>2</sub>O<sub>3</sub> and nanosilver (Table I). A good agreement between the simulation and experiment was achieved in static I-V curves and the surge I-V loops (Fig. 2(f)-(g)).

Fig. 2(h) shows the simulated  $T_j$  evolution at the Schottky contact region of the two types of SBDs in the surge current tests. In the test with a similar  $I_{\text{peak}}$ , the simulation validates a lower peak  $T_j$  in the double-side-cooled SBD. The simulated  $T_j$  reaches the peak value at the transient  $t \approx 6$  ms, agreeing with the failure transients shown in Fig. 2(a) and (b). The simulation also verifies a smaller  $T_j$  in the bottom-side-cooled SBD at its critical  $I_{\text{peak}}$  (~ 37.5 A) as compared to the one in the double-side-cooled SBD (critical  $I_{\text{peak}} \sim 68$  A).

Figs. 3(a)-(d) show the simulated distributions of heat flux and temperatures in the double-side-cooled SBD at the peak  $T_j$ transient in the surge current test with  $I_{peak} \sim 68$  A. Fig. 3(e)-(f)

TABLE II COMPARISON OF THE SURGE CURRENT CAPABILITY OF SIC AND GA2O3 SCHOTTKY BARRIER DIODES

| Device                                                   | Rated<br>Current (A) | Max Surge<br>Current (A) | Max surge current over rated current |

|----------------------------------------------------------|----------------------|--------------------------|--------------------------------------|

| SiC SBD (CSD01060A)                                      | 4                    | 20.3                     | 5.1                                  |

| SiC SBD (CSD02060A)                                      | 8                    | 26.9                     | 3.36                                 |

| SiC SBD (CSD03060A)                                      | 11                   | 31.8                     | 2.89                                 |

| Bottom-side-cooled<br>Ga <sub>2</sub> O <sub>3</sub> SBD | 6.2                  | 37.5                     | 6.05                                 |

| Double-side-cooled<br>Ga <sub>2</sub> O <sub>3</sub> SBD | 9.2                  | 68                       | 7.4                                  |

show the simulated heat flux and temperature contours in the bottom-side-cooled SBD at the peak  $T_j$  transient in the surge current test with  $I_{peak} \sim 37.5$  A. The heat flux distribution in the double-side-cooled SBD reveals that most heat is dissipated directly from the Schottky junction instead of through the Ga<sub>2</sub>O<sub>3</sub> die. This explains the lower  $T_j$  in the double-side-cooled SBD as compared to that in the bottom-side-cooled SBD at a similar  $I_{peak}$ . As shown in Figs. 3(c) and (d), the simulated peak temperature is located within the Ga<sub>2</sub>O<sub>3</sub> drift layer in the double-side-cooled SBD. In contrast, as shown in Fig. 3(f), the peak temperature is located at the Schottky junction in the bottom-side-cooled SBD. The double-side-cooling package moves the peak temperature from the Schottky contact region into the robust bulk Ga<sub>2</sub>O<sub>3</sub>, which allows the device to sustain a higher  $T_j$  before degradation of the Schottky contact.

Additionally, as shown in Figs. 3(d) and (f), the temperature distribution at the Schottky junction region is much less uniform in the bottom-side-cooled SBD compared to that in the double-side-cooled SBD. This temperature non-uniformity could be exacerbated by the wire bonding on the top of the anode in the bottom-side-cooled SBD, which often induces local current crowding and thermal runaway. This explains the lower  $T_j$  that bottom-side-cooled SBDs can sustain as compared to the one that double-side-cooled SBDs can. This mechanism is supported by the observation of burning traces near the wire bonds in the failed bottom-side-cooled SBDs.

#### IV. BENCHMARK, DISCUSSION AND CONCLUSION

An important device ruggedness metric for practical power applications is the ratio between the maximum  $I_{\text{peak}}$  in 10-ms surge current tests and the rated current. The rated currents of the bottom-side-cooled and double-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBDs were determined by the calibrated static electrothermal simulations when the  $T_j$  reaches 150 °C, being 6.2 A for the bottom-side-cooled device and 9.2 A for the double-side-colled device. For comparison, several commercial SiC SBDs with similar ratings (600-V voltage rating and 4~11 A current ratings) were tested in the same surge current test setup to identify their maximum surge currents. As shown in Table II, despite the low  $k_T$  of Ga<sub>2</sub>O<sub>3</sub> (1/20 of SiC), the fabricated Ga<sub>2</sub>O<sub>3</sub> SBDs, particularly the ones with double-side-cooling package, show comparable, or even superior surge current capabilities as compared to the similarly-rated commercial SiC SBDs.

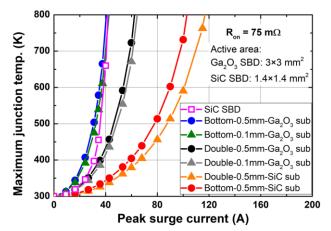

Fig. 4. Simulated max junction temperature as a function of peak surge current in 10-ms surge tests for the double-side-cooled and bottom-side-cooled Ga<sub>2</sub>O<sub>3</sub> SBDs on the 0.5-mm-thick Ga<sub>2</sub>O<sub>3</sub> substrate, 0.1-mm-thick Ga<sub>2</sub>O<sub>3</sub> substrate, and 0.5-mm-thick SiC substrate. A thermal boundary resistance of 0.01 K/(W·cm<sup>2</sup>) was set at the Ga<sub>2</sub>O<sub>3</sub>/SiC bonding interface. Identical electrical conductivity was set for Ga<sub>2</sub>O<sub>3</sub> and SiC substrates. The simulated SiC SBD has a 0.5-mm-thick substrate and a bottom-side-cooled package. Caughey-Thomas model was used for the SiC electron mobility.

Commercial SiC SBDs usually have bipolar p-n junctions that enhance the device ruggedness. Without p-type doping in  $Ga_2O_3$ , the superior surge current capabilities of  $Ga_2O_3$  SBDs can be attributed to two mechanisms: first, the inherently smaller  $\alpha$  in  $Ga_2O_3$  devices allows for a small conduction loss increase with increased  $T_j$  and less risks for thermal runaway; second, the double-side-cooling package obviates the heat extraction via the low- $k_T$   $Ga_2O_3$  chip and moves the peak temperature from the Schottky contact into the bulk  $Ga_2O_3$ .

To further understand the design space of the surge current capabilities of Ga<sub>2</sub>O<sub>3</sub> devices, two additional die-level thermal management approaches were considered: thinning of the Ga<sub>2</sub>O<sub>3</sub> substrate, and bonding Ga<sub>2</sub>O<sub>3</sub> device layers to a SiC wafer [21]. Using the calibrated simulation models, Fig. 4 shows the simulated peak  $T_i$  as a function of surge  $I_{peak}$  for the different Ga<sub>2</sub>O<sub>3</sub> device structures. A similarly-rated SiC SBD with identical substrate thickness was also simulated as a reference. In Ga<sub>2</sub>O<sub>3</sub> devices, the substrate thinning provides little improvement in the surge current capabilities when compared to the use of junction cooling, since most of the heat is directly extracted from the junction. Whereas, if low- $k_T$  SiC substrate is used in Ga<sub>2</sub>O<sub>3</sub> devices, the heat extraction through the bulk chip can be improved significantly. Hence, the surge current capabilities can be further improved in the double-sidecooled device as compared to the bottom-side-cooled one.

In summary, this work presents the first experimental demonstration of large-area vertical Ga<sub>2</sub>O<sub>3</sub> SBDs with different die-level cooling packages, and for the first time, reports the surge current capabilities of these packaged Ga<sub>2</sub>O<sub>3</sub> devices. Despite the low  $k_{\rm T}$  of Ga<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> SBDs packaged in a double-side-cooling scheme show comparable or even superior surge current capabilities when compared to SiC SBDs. These results remove the key concerns regarding the electrothermal ruggedness of Ga<sub>2</sub>O<sub>3</sub> devices and demonstrate the significance of die-level thermal management for Ga<sub>2</sub>O<sub>3</sub> electronics.

#### REFERENCES

- S. J. Pearton, J. Yang, P. H. Cary, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, "A review of Ga2O3 materials, processing, and devices," *Appl. Phys. Rev.*, vol. 5, no. 1, p. 011301, Jan. 2018.

- [2] M. Higashiwaki and G. H. Jessen, "Guest Editorial: The dawn of gallium oxide microelectronics," *Appl. Phys. Lett.*, vol. 112, no. 6, Feb. 2018.

- [3] N. Allen *et al.*, "Vertical Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes With Small-Angle Beveled Field Plates: A Baliga's Figure-of-Merit of 0.6 GW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 40, no. 9, pp. 1399–1402, Sep. 2019.

- [4] W. Li, K. Nomoto, Z. Hu, D. Jena, and H. G. Xing, "Field-Plated Ga<sub>2</sub>O<sub>3</sub> Trench Schottky Barrier Diodes With a BV<sup>2</sup>/R<sub>on</sub> of up to 0.95 GW/cm<sub>2</sub>," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 107–110, Jan. 2020.

- [5] Y. Zhang, T. Palacios, "(Ultra)Wide-Bandgap Vertical Power FinFETs," IEEE Trans. Electron Devices, vol. 67, no. 10, pp. 3960–3971, Oct. 2020.

- [6] W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. G. Xing, "Single and multi-fin normally-off Ga2O3 vertical transistors with a breakdown voltage over 2.6 kV," in 2019 IEEE International Electron Devices Meeting (IEDM), Dec. 2019, p. 12.4.1-12.4.4.

- [7] M. Ji *et al.*, "Demonstration of Large-Size Vertical Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 41–44, Jan. 2021.

- [8] J. Yang *et al.*, "Vertical geometry 33.2 A, 4.8 MW cm<sup>2</sup> Ga<sub>2</sub>O<sub>3</sub> field-plated Schottky rectifier arrays," *Appl. Phys. Lett.*, vol. 114, no. 23, p. 232106, Jun. 2019.

- [9] P. Paret et al., "Thermal and Thermomechanical Modeling to Design a Gallium Oxide Power Electronics Package," in 2018 IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2018, pp. 287–294.

- [10] B. K. Mahajan, Y.-P. Chen, J. Noh, P. D. Ye, and M. A. Alam, "Electrothermal performance limit of β-Ga<sub>2</sub>O<sub>3</sub> field-effect transistors," *Appl. Phys. Lett.*, vol. 115, no. 17, p. 173508, Oct. 2019.

- [11] C. Yuan, et al., "Modeling and analysis for thermal management in gallium oxide field-effect transistors," J. Appl. Phys., vol. 127, no. 15, p. 154502, Apr. 2020.

- [12] C. Buttay, H.-Y. Wong, B. Wang, M. Xiao, C. DiMarino and Y. Zhang, "Surge Current Capability of Ultra-Wide-Bandgap Ga<sub>2</sub>O<sub>3</sub> Schottky Diodes," *Microelectron. Reliab.*, in press.

- [13] "SILICON RECTIFIER DIODES: | JEDEC." [online available] https://www.jedec.org/standards-documents/docs/jesd-282b01 (accessed Jun. 05, 2020).

- [14] B. Heinze, J. Lutz, M. Neumeister, R. Rupp, and M. Holz, "Surge Current Ruggedness of Silicon Carbide Schottky- and Merged-PiN-Schottky Diodes," in 2008 20th International Symposium on Power Semiconductor Devices and IC's, May 2008, pp. 245–248.

- [15] J. Wu, N. Ren, H. Wang, and K. Sheng, "1.2-kV 4H-SiC Merged PiN Schottky Diode With Improved Surge Current Capability," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 3, pp. 1496–1504, Sep. 2019.

- [16] B. Wang *et al.*, "High-voltage vertical Ga2O3 power rectifiers operational at high temperatures up to 600 K," *Appl. Phys. Lett.*, vol. 115, no. 26, p. 263503, Dec. 2019.

- [17] T. Wang, X. Chen, G.-Q. Lu, and G.-Y. Lei, "Low-Temperature Sintering with Nano-Silver Paste in Die-Attached Interconnection," J. Electron. Mater., vol. 36, no. 10, pp. 1333–1340, Oct. 2007.

- [18] J. N. Calata, T. G. Lei, and G.-Q. Lu, "Sintered nanosilver paste for hightemperature power semiconductor device attachment," *Int. J. Mater. Prod. Technol.*, vol. 34, no. 1–2, pp. 95–110, Jan. 2009.

- [19] C. Buttay, C. Raynaud, H. Morel, G. Civrac, M.-L. Locatelli, and F. Morel, "Thermal Stability of Silicon Carbide Power Diodes," *IEEE Trans. Electron Devices*, vol. 59, no. 3, pp. 761–769, Mar. 2012.

- [20] Y. Zhang *et al.*, "Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2224–2230, Jul. 2013.

- [21] W. Xu *et al.*, "First Demonstration of Waferscale Heterogeneous Integration of Ga<sub>2</sub>O<sub>3</sub> MOSFETs on SiC and Si Substrates by Ion-Cutting Process," in 2019 IEEE International Electron Devices Meeting (IEDM), Dec. 2019, p. 12.5.1-12.5.4.