# Voltage controlled sub-THz detection with gated planar asymmetric nanochannels

H. Sanchez-Martin, J. Mateos, J. A. Novoa, J. A. Delgado-Notario, Y. M. Meziani, S. Perez, H. Theveneau, Guillaume Ducournau, Christophe Gaquière, T. Gonzalez, et al.

### ▶ To cite this version:

H. Sanchez-Martin, J. Mateos, J. A. Novoa, J. A. Delgado-Notario, Y. M. Meziani, et al.. Voltage controlled sub-THz detection with gated planar asymmetric nanochannels. Applied Physics Letters, 2018, 113 (4), 10.1063/1.5041507. hal-03183499

HAL Id: hal-03183499

https://hal.science/hal-03183499

Submitted on 27 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Voltage controlled sub-THz detection with gated planar asymmetric nanochannels

Cite as: Appl. Phys. Lett. 113, 043504 (2018); https://doi.org/10.1063/1.5041507 Submitted: 25 May 2018 • Accepted: 11 July 2018 • Published Online: 25 July 2018

H. Sánchez-Martín, 🔟 J. Mateos, J. A. Novoa, et al.

#### ARTICLES YOU MAY BE INTERESTED IN

Asymmetric dual-grating gates graphene FET for detection of terahertz radiations APL Photonics 5, 066102 (2020); https://doi.org/10.1063/5.0007249

Ultrahigh sensitive sub-terahertz detection by InP-based asymmetric dual-grating-gate highelectron-mobility transistors and their broadband characteristics

Applied Physics Letters 104, 251114 (2014); https://doi.org/10.1063/1.4885499

A flexible graphene terahertz detector

Applied Physics Letters 111, 021102 (2017); https://doi.org/10.1063/1.4993434

Lock-in Amplifiers up to 600 MHz

Zurich

## Voltage controlled sub-THz detection with gated planar asymmetric nanochannels

H. Sánchez-Martín, <sup>1</sup> J. Mateos, <sup>1,a)</sup> J. A. Novoa, <sup>1</sup> J. A. Delgado-Notario, <sup>1</sup> Y. M. Meziani, <sup>1</sup> S. Pérez, <sup>1</sup> H. Theveneau, <sup>2</sup> G. Ducournau, <sup>2</sup> C. Gaquière, <sup>2</sup> T. González, <sup>1</sup> and I. Íñiquez-de-la-Torre <sup>1</sup>

<sup>1</sup>Dpto. Física Aplicada, Universidad de Salamanca, 37008 Salamanca, Spain <sup>2</sup>Institut d'Electronique, de Microélectronique et de Nanotechnologie, Univ. Lille, CNRS, Centrale Lille, ISEN, Univ. Valenciennes, UMR 8520-IEMN, F-59652 Villeneuve d'Ascq, France

(Received 25 May 2018; accepted 11 July 2018; published online 25 July 2018)

This letter reports on room temperature sub-THz detection using self-switching diodes based on an AlGaN/GaN heterostructure on a Si substrate. By means of free-space measurements at 300 GHz, we demonstrate that the responsivity and noise equivalent power (NEP) of sub-THz detectors based on planar asymmetric nanochannels can be improved and voltage controlled by means of a top gate electrode. A simple quasi-static model based on the DC measurements of the current-voltage curves is able to predict the role of the gate bias in its performance. The best values of voltage responsivity and NEP are achieved when the gate bias approaches the threshold voltage, around 600 V/W and 50 pW/Hz<sup>1/2</sup>, respectively. A good agreement is found between modeled results and those obtained from RF measurements under probes at low frequency (900 MHz) and in free-space at 300 GHz. *Published by AIP Publishing*, https://doi.org/10.1063/1.5041507

In the last few years, different THz detectors have been investigated, looking for larger bandwidth and lower noise, with increasing practical interest in security, medical imaging, and high speed short range communications, among other fields. A non-classic architecture based on a single nanolithography step allowing to define an asymmetric planar diode so-called Self-Switching diode (SSD) was proposed by Song in 2003.<sup>2</sup> This particular geometry propagates the applied bias into a lateral field effect, which depending on the polarity is able to open or close the channel because of electrostatic and surface effects. The use of high mobility materials like InGaAs, InAs, or graphene for fabricating SSDs has allowed envisaging its use in relevant THz applications such as zero-bias detectors for passive imaging. In addition, GaN despite its lower mobility is also suitable for sub-THz detection. In all the cases, reducing the channel width is the first strategy to enhance the performance of SSDs as detectors. However, this has a drawback: the variability on their performance. It is difficult to precisely control such a stringent fabrication process and reproducibly fabricate SSDs with channel widths below 100 nm. Moreover, the detection performance depends on the nonlinearity of the I-V curve of the SSDs, which critically depends on the presence of surface charges at the sidewalls of the channels, so that many unknown trap mechanisms, especially in the GaN technology, arise.9

In order to control the conductance of planar nanochannels, different solutions based on the field effect have been proposed: (i) in-plane gates, where the confining electric field is parallel to the two-dimensional electron gas (2DEG), <sup>10–13</sup> which provide the transistor effect and voltage-tunability of their I-V curves or (ii) top Schottky contact (SC) gates, <sup>14</sup> used not only in FETs but also in

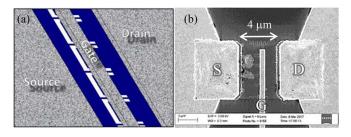

countless semiconductor devices including ballistic devices <sup>15</sup> and Gunn diodes. <sup>16</sup> In this work, we explore the benefits on the main figures of merit of RF detectors, i.e., responsivity ( $\beta$ ) and noise equivalent power (NEP), of adding a SC gate on the top of SSDs fabricated on GaN, as sketched in Fig. 1(a). The conventional vertical field effect mechanism for gating the carrier density in these devices, which we will call gated-SSDs (G-SSDs), will be studied. The advantage of G-SSDs over standard FETs, also showing a nonlinearity in the drain current vs. drain-to-source voltage curves ( $I_D$ – $V_{DS}$ ) originated from the gate electrode, is that the responsivity of G-SSDs has an additional contribution coming from the lateral field effect (associated with the SSD shape), superimposed to the effect of the top gate.

The characterized G-SSDs are based in an AlGaN/GaN heterojunction on a Si substrate grown by EpiGaN consisting of a 25 nm thick AlGaN barrier (with 35% Al content) on top of a 1.5  $\mu$ m thick GaN buffer. The fabrication process is similar to that of the recess technology presented in Ref. 8, in which, after the dry etching of the trenches, a final step associated with the top gate fabrication is added. This step is done as following: e beam writing of the PMMA and Argon

FIG. 1. (a) Sketch of a G-SSD and (b) SEM view of an array of 4 GaN SSDs with a top gate. The position of the source (S, at the left), drain (D, at the right), and gate (G, on the center of the channels) electrodes is also indicated.

a) Author to whom correspondence should be addressed: javierm@usal.es

etching, followed by a Ni/Au evaporation (40 nm/300 nm, respectively). The device under test has 4 channels in parallel, approximately  $70{\text -}100 \text{ nm}$  wide and  $1.0 \,\mu\text{m}$  long. The 500 nm gate electrode is located at the center of the channel, as shown in Fig. 1(b).

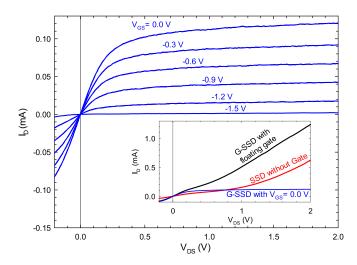

First, using a semiconductor analyzer (Keithley 4200-SCS), G-SSDs have been characterized in the DC regime at room temperature. Figure 2 shows the output curves of the devices, demonstrating good transistor operation, in spite of the appearance of a non-negligible gate leakage current, most probably associated with electrons injected from the gate through the lateral walls of the trenches. On the transfer characteristics ( $I_D$  vs. gate-to-source voltage,  $V_{GS}$ ), not shown here, it is observed that the threshold voltage,  $V_{\rm TH}$ , is more negative as  $V_{\rm DS}$  increases, a well-known short channel effect (drain induced barrier lowering). Since G-SSDs will be used not as transistors but as zero-bias detectors, their usual operation point is not in saturation, but no  $V_{DS}$  is applied. Therefore, as a reference for calculating the gate voltage overdrive, we will use the threshold voltage determined for the lowest values of  $V_{\rm DS}$ ,  $V_{\rm TH} = -1.6 \, \rm V$ . In the inset, the current measured in a G-SSD with a floating gate (gate in the open circuit) and that of a usual SSD without a gate electrode, with a similar channel geometry (width of 74 nm), are compared to that of the G-SSD with  $V_{\rm GS} = 0.0$  V. According to this result, it is clear that the inclusion of a SC gate has a significant impact reducing the depletion region imposed by the surface charges at the lateral trench walls, thus opening the channel and increasing the current. Figure 2 also shows that, as expected, the gate electrode of the G-SSD screens the drain voltage and imposes the saturation of the drain current, not found in the SSD without gate (neither on the G-SSD with an open circuit gate).

From these DC measurements, it is possible to predict the responsivity and NEP based on the first and second derivatives of the  $I_{\rm D}$ – $V_{\rm DS}$  curves, following the method described in Ref. 20. This quasi-static model has been satisfactorily used to analyze the performance of RF detectors based on SSDs made on InAs<sup>5</sup> and GaN.<sup>21</sup> By means of a polynomial

FIG. 2. Output characteristics of the G-SSD under test. The inset shows the I-V curve of the G-SSD with the gate contact in the open circuit (floating gate) and the SSD without gate with a similar geometry (74 nm width and  $1.0 \, \mu \text{m}$  length).

fitting of order three (using 20 points within the [-0.1 V, +0.1 V] range), the values of (i) the resistance, R, and (ii) the bowing coefficient, defined as  $\gamma = \left(\frac{d^2 I}{dV^2}\right)/\left(\frac{dI}{dV}\right) = \left(\frac{d^2 I}{dV^2}\right)R$ , can be calculated. The figure of merit called matched or optimum responsivity is given by  $\beta_{\text{opt}} = R\gamma/2$ .  $\gamma$  is a normalized parameter (given in units of  $V^{-1}$ ) allowing to compare different types of device architectures and whose value does not depend on the device size, i.e., the area of Schottky barrier diodes (SBDs), the gate width of FETs, or the number of parallel channels of SSDs or G-SSDs.

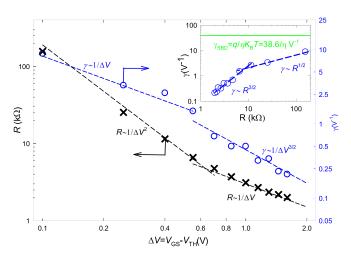

As expected, R and  $\gamma$ , shown in Fig. 3 as a function of  $\Delta V = V_{GS} - V_{TH}$ , increase monotonically when decreasing  $V_{GS}$ , taking values in the range of  $2.0-200 \,\mathrm{k}\Omega$  and  $0.2-10 \,\mathrm{V}^{-1}$ , respectively. However, we can identify two regions depending on the gate bias. For  $\Delta V$  above 0.5–0.6 V, the G-SSD behaves as a standard field effect transistor (FET), and R increases when decreasing  $V_{\rm GS}$ , following the ideal  $R \sim \Delta V^{-1}$  dependence. But when the G-SSDs approach pinch-off conditions ( $\Delta V < 0.5 \text{ V}$ ), R increases faster than expected, as  $\Delta V^{-2}$ . This indicates that the current control mechanism in the G-SSDs is modified from the pure field effect gating appearing at higher  $V_{GS}$  to a more complex behavior when  $V_{GS}$  comes close to  $V_{TH}$ . Under those conditions, the depletion imposed by the surface charges at the drain side of the channel may become more important due to a stronger electron heating (due to the strong electric field caused by the large gate-drain voltage difference,  $V_{\rm DG})$  and thus further increasing R.

Those two regions of gate bias can also be observed in the values of  $\gamma$ . In open channel conditions,  $\Delta V > 0.5 \, \mathrm{V}$ , when R is below  $10 \, \mathrm{k}\Omega$ ,  $\gamma$  goes as  $R^{3/2}$ , as shown in the inset of Fig. 3, so that  $\gamma \sim \Delta V^{-3/2}$ . However, this dependence cannot be extracted from the ideal FET theory, since it predicts a null value (as expected from a linear dependence of  $I_{\mathrm{D}}$  on  $V_{\mathrm{DS}}$ ), and it is the asymmetry of the channel (the SSD geometry) which produces this nonlinearity. In the low  $V_{\mathrm{GS}}$  region, in spite of the steeper increase in R,  $\gamma$  increases more slowly with decreasing gate bias as a result of a weaker dependence on R ( $\gamma \sim R^{1/2}$ , inset of Fig. 3) so that  $\gamma$  goes as

FIG. 3. Resistance, R, and bowing coefficient,  $\gamma$ , extracted from the DC measurements of the  $I_{\rm D}$ - $V_{\rm DS}$  curves (shown in Fig. 2) as a function of  $\Delta V = V_{\rm GS}$ - $V_{\rm TH}$  at  $V_{\rm DS} = 0.0$  V. Dashed lines show different dependencies on  $\Delta V$  for eye guiding. The inset shows the values of  $\gamma$  vs. R, with the eye guiding lines showing the  $\gamma \sim R^{3/2}$  and  $\gamma \sim R^{1/2}$  dependencies, appearing at high and low  $V_{\rm GS}$ , respectively.

$\Delta {

m V}^{-1}$ . As it can be extrapolated from these  $\gamma$  vs. R dependencies, the value of  $\left(\frac{d^2 I}{dV^2}\right)$  increases with R for low R (when  $\gamma \sim R^{3/2}$ ) and then decreases (when  $\gamma \sim R^{1/2}$ ), peaking at about ( $\Delta V \approx 0.5 {

m V}$ ).

Even if the change of the slope in the  $V_{\rm GS}$  dependencies of R and  $\gamma$  is not extremely obvious (for this sake, eyeguiding dashed lines have been included in Fig. 3), the separation between the open-channel and near-pinch-off regions is quite evident in the  $\gamma$  vs. R representation in the inset of Fig. 3: a clear switch from a rapid increase in  $\gamma$  as  $R^{3/2}$  for low  $V_{\rm GS}$  to a slower increase as  $R^{1/2}$  for the higher  $V_{\rm GS}$  values appears at  $R \sim 10 \,\mathrm{k}\Omega$  (i.e.,  $\Delta V = 0.5 - 0.6 \,\mathrm{V}$ ). The inset also shows the value of  $\gamma$  for devices with the exponential I-V curve (like SBDs, typically used as RF detectors),  $\gamma = q/\eta k_B T$ , with  $\eta$  being the non-ideality factor, which for  $T = 300 \,\mathrm{K}$  and  $\eta = 1$  leads to  $\gamma = 38.6 \,\mathrm{V}^{-1}$  (an invariant value regardless of the resistance of the SBD). This value of  $\gamma$ , which could be considered as the target for our G-SSDs (their non-linearity would be comparable to that of an exponential I-V), is approached when lowering  $V_{GS}$ , providing values not far from  $10 \,\mathrm{V}^{-1}$ .

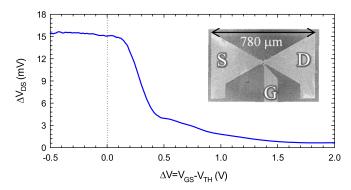

In order to demonstrate their potentiality as sub-THz detectors, the devices were integrated with broadband bowtie antennas, as shown in the inset of Fig. 4. A solid-state harmonic generator with an output power of ~6 mW at 300 GHz was used to excite the G-SSD. The induced  $V_{\rm DS}$ was measured at room temperature using a lock-in technique with a mechanical chopper. More details about the set-up can be found in Ref. 17. In this kind of configuration, optical losses (focusing, wave propagation, normalization due to beam spot and device size) are very difficult to estimate, so that in Fig. 4, we just present the output voltage,  $V_0$ , measured at the drain. This figure shows that the photoresponse increases sharply when  $V_{GS}$  approaches the threshold voltage and then saturates within the subthreshold region. This behavior is similar to that obtained in other FETs as shown in Ref. 18.

With the aim of having a better quantitative estimation of the responsivity of the devices, we have also characterized the G-SSD as a power detector under probes, also at room temperature. In this case, the average  $V_{\rm DS}$  output voltage,  $V_{\rm o}$ , was measured while simultaneously biasing the device with  $I_{\rm D}=0$  (through a bias tee) and the corresponding  $V_{\rm GS}$ . The input signal is provided by means of a vector network

FIG. 4. Output voltage when illuminating the sample with a 300 GHz beam as a function of  $\Delta V = V_{\rm GS} - V_{\rm TH}$  at  $I_{\rm D} = 0$ . The inset shows the geometry of the bow-tie integrated antenna.

analyzer (Keysight PNA X N5244) with a power range of  $P_{\text{VNA}} = [-20 \, \text{dBm}, +10 \, \text{dBm}]$ . Since coplanar waveguide accesses were not available for the G-SSD, the RF measurements were performed using DC needles at relatively low frequency, 900 MHz. In order to calibrate the electrical losses associated with this setup, a power compensation is required. For that purpose, a previous measurement with both RF probes and DC needles was done on SSDs without gate (with integrated RF accesses), providing a value of 10 dB losses. Thus, the voltage responsivity of the G-SSD is calculated as  $\beta = V_0/(P_{VNA}-10 \text{ dB})$ , which is constant in the whole range of input power used in these RF measurements, meaning that the device behaves as a square-law detector. On the other hand, the noise equivalent power, NEP, is obtained as NEP =  $(4k_BTR)^{1/2}/\beta$ , using the ideal value of the noise power of the G-SSD given by the Nyquist theorem. In the case of the free space measurements,  $\beta$  and NEP are calculated in the same way but the coupling and mismatch losses have been estimated by fitting the free-space results to the RF measurements at  $\Delta V = 0.1$  V, thus giving a value of 27 dB losses, approximately.

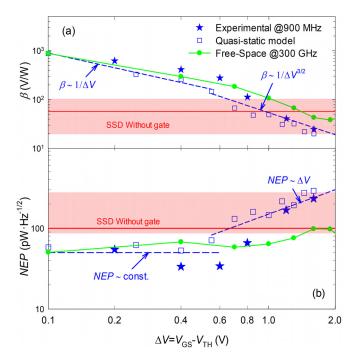

Figure 5 compares the values of  $\beta$  and NEP as a function of  $\Delta$ V measured in free-space (@300 GHz) and under probes (@900 MHz), with the calculations using the previously presented quasi-static model. In fact,  $\beta$  can also be extracted from the DC measurements of  $\gamma$  and R by taking into account the impedance mismatch factor  $M_0 = 4Z_0R/(R+Z_0)^2$ , so that  $\beta = \beta_{\rm opt} \times M_0 = R\gamma/2 \times M_0$ , where the characteristic impedance is  $Z_0 = 50 \Omega$ . DC, RF, and free space results show a reasonable agreement, the slight disagreement probably due not only to the power losses but also to the difficult

FIG. 5. Comparison of the values of (a)  $\beta$  and (b) NEP vs.  $\Delta V$  (at  $V_{\rm DS}=0.0$  V) calculated from the DC measurements (quasi-static model) with those obtained in the experimental free-space setup at 300 GHz and the RF measurements at 900 MHz. The values for the SSD without gate and the same geometry are shown by the horizontal solid line,  $^{20}$  while the results of GaN based SSDs with other geometries (fabricated in the same run and published in the literature  $^{7.8}$ ) are covered by the shaded regions.

extraction of the values of  $\gamma$  from very small values of current in the case of the quasi-static model and the frequency dependence of the impedance of the devices that could affect the value of the mismatch factor for the different frequency ranges.

The increase in  $\beta$  when lowering the gate bias shows the same trends as those of  $\gamma$  [Figs. 3 and 5(a)],  $\beta \sim \Delta V^{-3/2}$ , and  $\beta \sim \Delta V^{-1/2}$  in the  $\Delta V$  regions above and below 0.5–0.6 V, respectively. This happens because when R is very high, as occurs in our G-SSD, the value of the responsivity approaches  $\beta \approx 2\gamma Z_0 = 100\gamma$ . Therefore,  $\beta$  is just proportional to  $\gamma$ , i.e., depends only on the non-linearity of the  $I_{\rm D}$ - $V_{\rm DS}$  curves. Figure 5(a) also shows the values of  $\beta$ obtained in ungated SSDs. 7,8,20,21 Interestingly, the value of the responsivity of the G-SSD overcomes that of ungated SSDs when entering the near pinch-off gate bias region  $(\Delta V < 0.5 \text{ V})$ . This is also an evidence that under those conditions, an additional current control mechanism is in action. Remarkably, this leads to values of responsivity as high as 600 V/W never obtained previously in ungated SSDs, even with the optimum geometry (the highest responsivity, 100 V/W, was obtained with an extremely narrow channel defined by ion implantation<sup>7</sup>). Regarding the NEP, in open channel conditions, it decreases when lowering  $V_{\rm GS}$  as  $\Delta {

m V}^{-1}$  (as follows from the  $\Delta V^{-3/2}$  and  $\Delta V^{-1}$  dependencies of  $\beta$  and R, respectively), reaching a nearly constant value for  $\Delta V < 0.5 \text{ V}$ (where the  $\Delta V^{-1}$  and  $\Delta V^{-2}$  trends of  $\beta$  and R cancel each other). As a consequence, the value of NEP decreases below  $50 \text{ pW} \cdot \text{Hz}^{-1/2}$ .

These results show that the performance of the G-SSD architecture can approach the state-of-the-art of mm-and sub-mm-wave detectors, since the impedance-tunability provided by the voltage control of the characteristics of the device can be combined with additional design efforts aiming to mitigate the strong mismatch presented by these devices, such as the increase in the number of parallel channels and the use of high impedance access lines.

This work was partially supported by the Spanish MINECO through project TEC2017-83910-R, by the Consejería de Educación de la JCyL, project SA022U16, and by SATT Nord, project SSD COM MO226. H. Sánchez-

Martín acknowledges the Ph.D. contract from the University of Salamanca. We thank Victor Raposo for his support in the realization of the measurements.

- <sup>1</sup>S. S. Dhillon, M. S. Vitiello, E. H. Linfield, A. G. Davies, M. C. Hoffmann, J. Booske, C. Paoloni, M. Gensch, P. Weightman, and G. P. Williams, J. Phys. D: Appl. Phys. **50**, 043001 (2017).

- <sup>2</sup>A. M. Song, M. Missous, P. Omling, A. R. Peaker, L. Samuelson, and W. Seifert, Appl. Phys. Lett. **83**, 1881 (2003).

- <sup>3</sup>J. Mateos, B. G. Vasallo, D. Pardo, and T. González, Appl. Phys. Lett. 86, 212103 (2005).

- <sup>4</sup>C. Balocco, M. Halsall, N. Q. Vinh, and A. M. Song, J. Phys. Condens. Matter 20, 384203 (2008).

- Mestlund, P. Sangaré, G. Ducournau, P.-A. Nilsson, C. Gaquière, L. Desplanque, X. Wallart, and J. Grahn, Appl. Phys. Lett. 103, 133504 (2013).

Mestlund, M. Winters, I. G. Ivanov, J. Hassan, P. A. Nilsson, E. Janzén, N. Rorsman, and J. Grahn, App. Phys. Lett. 106, 093116 (2015).

- <sup>7</sup>C. Daher, J. Torres, I. Iñiguez-de-la-Torre, P. Nouvel, L. Varani, P. Sangaré, G. Ducournau, C. Gaquière, J. Mateos, and T. González, IEEE Trans. Electron Devices **63**, 353–359 (2016).

- <sup>8</sup>P. Sangaré, G. Ducournau, B. Grimbert, V. Brandli, M. Faucher, C. Gaquière, A. Íñiguez-de-la-Torre, I. Íñiguez-de-la-Torre, J. F. Millithaler, J. Mateos, and T. González, J. Appl. Phys. **113**, 034305 (2013).

- <sup>9</sup>G. Meneghesso, M. Meneghini, D. Bisi, I. Rossetto, A. Cester, U. K. Mishra, and E. Zanoni, Semicond. Sci. Technol. 28, 074021 (2013).

- <sup>10</sup>A. D. Wieck and K. Ploog, Appl. Phys. Lett. **56**, 928 (1990).

- <sup>11</sup>J. Mateos, A. M. Song, B. G. Vasallo, D. Pardo, and T. González, "Nanotechnology II," Proc. SPIE 5838, 145 (2005).

- <sup>12</sup>A. Ganczarczyk, S. Voßen, M. Geller, A. Lorke, D. Reuter, and A. D. Wieck, Physica E 42, 1216–1219 (2010).

- <sup>13</sup>K. Y. Xu, J. W. Xiong, A. M. Song, and G. Wang, Semicond. Sci. Technol. 26, 095026 (2011).

- <sup>14</sup>W. Shockley, Proc. IRE **40**, 1365–1376 (1952).

- <sup>15</sup>M. Szelong, A. Ludwig, A. D. Wieck, and U. Kunze, Semicond. Sci. Technol. 32, 105005 (2017).

- <sup>16</sup>A. H. Khalid, G. M. Dunn, N. Pilgrim, C. R. Stanley, I. G. Thayne, M. Holland, and D. R. S. Cumming, Electron Lett. 43, 837–838 (2007).

- <sup>17</sup>J. A. Delgado Notario, E. Javadi, J. Calvo-Gallego, E. Diez, J. E. Velázquez, and Y. M. Meziani, Int. J. High Speed Electron. Syst. 25(3 & 4), 1640020 (2016).

- <sup>18</sup>H. W. Hou, Z. Liu, J. H. Teng, T. Palacios, and S. J. Chua, Sci. Rep. 7, 46664 (2017).

- <sup>19</sup>A. M. Cowley and H. O. Sorensen, IEEE Trans. Microwave Theory Tech. 14, 588–602 (1966).

- <sup>20</sup>H. Sánchez-Martín, S. Sánchez-Martín, I. Íniguez-de-la-Torre, S. Pérez, J. A. Novoa, G. Ducournau, B. Grimbert, C. Gaquière, T. González, and J. Mateos, "GaN nanodiode arrays with improved design for zero-bias sub-THz detection," Semicond. Sci. Technol. (submitted).

- <sup>21</sup>H. Sánchez-Martin, S. Sánchez-Martín, O. García-Pérez, S. Pérez, J. Mateos, T. González, I. Íñiguez-de-la-Torre, and C. Gaquière, in 2017 Conference on Electron Devices, Barcelona, Spain, 2017.