# Monitoring of gate leakage current on SiC power MOSFETs: an estimation method for smart gate drivers

Julien Weckbrodt, Nicolas Ginot, Christophe Batard, Stephane Azzopardi

# ▶ To cite this version:

Julien Weckbrodt, Nicolas Ginot, Christophe Batard, Stephane Azzopardi. Monitoring of gate leakage current on SiC power MOSFETs: an estimation method for smart gate drivers. IEEE Transactions on Power Electronics, 2021, 36 (8), pp.8752 - 8760. 10.1109/TPEL.2021.3056648. hal-03154976

HAL Id: hal-03154976

https://hal.science/hal-03154976

Submitted on 4 Apr 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Monitoring of Gate Leakage Current on SiC Power MOSFETs: An Estimation Method for Smart Gate Drivers

Julien Weckbrodt, Nicolas Ginot, Christophe Batard, and Stephane Azzopardi

Abstract-Silicon Carbide (SiC) power transistors are more and more used in electric energy conversion systems. SiC power semiconductors devices, such as SiC metal-oxide-semiconductor field-effect transistor (MOSFET) can operate at higher frequency and higher temperature compared to Silicon power MOSFET or insulated-gate bipolar transistor. However, the maturity of the SiC technology is moderate compared to the well-known Silicon-based power semiconductor devices. Recent research works on reliability of SiC power MOSFET identified gate leakage currents as an ageing indicator. The monitoring of ageing indicators during normal operation may definitely help to predict damages and simplify the maintenance on the energy conversion systems. Due to the low amplitude of gate leakage currents, its direct measurement is difficult even under laboratory conditions and requires an offline characterization. This article presents a new method for estimating the gate leakage current using the gate drive circuit. The proposed method takes advantage of the internal structure of the typical gate drivers used to command SiC power MOSFETs.

Index Terms—Driver circuits, leakage currents, power system monitoring, semiconductor device reliability, silicon carbide (SiC) power metal-oxide-semiconductor field-effect transistor (MOSFET), smart gate drivers.

$I_{L, DRIVER}$  Average leakage current due to the drive system.

$I_{L,

m DUT}$  Estimated gate leakage current.  $I_{L,

m MES}$  Average leakage current measured.  $I_{L,

m TH}$  Theoretical gate leakage current. m Modulation coefficient (PWM signal).

$R_{

m DS(on)}$  ON-state resistance. Res Targeted resolution (%).  $R_{

m GS}$  Gate-source resistance.

T Switching period of the command signals.  $T_L$  Time required to reach  $\Delta VS$  ( = acquisition time).  $T_{L, CAL}$  Time required to reach  $\Delta VS$  during calibration.

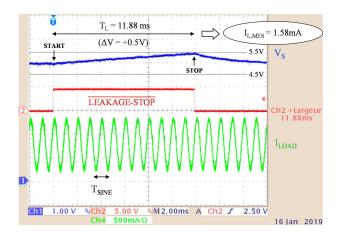

$T_{\rm SINE}$  Period of the modulating signal.

$V_{\rm DC}$  Power voltage source.

$V_{DD}$  Supply voltage of the gate driver.

$V_{\rm GS}$  Gate-source voltage.  $V_S$  Source potential.  $V_{\rm TH}$  Threshold voltage.

$\alpha$  Duty cycle of the command signal.  $\Delta V_S$  Authorized source potential variation.

#### NOMENCLATURE

| $C_1, C_2$  | Decoupling capacitors.   |

|-------------|--------------------------|

| $C_{ m GD}$ | Miller capacitance.      |

| $C_{ m GS}$ | Gate-source capacitance. |

cpt Size of the counter (algorithm implementation).dt Temporal step for acquisition (in seconds).

f Frequency of the modulating signal.

$I_D$  Online drain current.

$I_{\rm DSS}$  Drain-source leakage current.

$I_{\rm GSS}$  Gate-source leakage current (static measurement).

$I_{\rm LOAD}$  Online load current.

Manuscript received December 19, 2019; revised May 29, 2020, September 18, 2020, and December 22, 2020; accepted January 24, 2021. Date of publication February 17, 2021; date of current version May 5, 2021. Recommended for publication by Associate Editor M. Nawaz. (Corresponding author: Julien Weckbrodt.)

Julien Weckbrodt and Stephane Azzopardi are with the Electricity and Electronics, Safran Tech, 92230 Chateaufort, France (e-mail: julien.weckbrodt@univ-nantes.fr; stephane.azzopardi@safrangroup.com).

Nicolas Ginot and Christophe Batard are with the Génie Electrique et Informatique Industrielle, IUT Nantes, 44000 Nantes, France (e-mail: nicolas.ginot@univ-nantes.fr; christophe.batard@univ-nantes.fr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2021.3056648.

Digital Object Identifier 10.1109/TPEL.2021.3056648

#### I. INTRODUCTION

THE very interesting electrical performances of silicon carbide (SiC) metal-oxide-semiconductor field-effect transistor (MOSFET) transistors make this component extremely promising for the future of power electronics in a wide range of applications. Indeed, the higher power density of SiC components and their characteristics under high temperature are appreciated for a compact design of power converters. Lots of works have been carried out for several years in order to highlight the limits in terms of lifespan as well as relevant ageing indicators. For example, power cycling, repetitive overcurrent, and repetitive short-circuit (SC) tests were applied to these components and their behavior until failure has been analyzed.

The channel resistance of a SiC MOSFET is considerably high compared to a silicon MOSFET. This is due to a lower inversion carrier mobility at the SiC/SiO<sub>2</sub> interface and electrons trapping resulting in the depletion of inversion charge density. In order to minimize the channel resistance, SiC MOSFETs are designed with a smaller gate oxide thickness compared to silicon ones. Due to a higher bandgap energy and a smaller oxide thickness, tunneling current through the gate oxide [1]–[4] and charge trapping in the gate oxide are reinforced [5], [6].

0885-8993 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Concerning ageing tests, the repetition of SCs is certainly the most severe one. The failure temperature was estimated at approximately  $650 \,^{\circ}\text{C} \pm 100 \,^{\circ}\text{C}$  near the aluminum metallization melting temperature [7]. As described in [8], two failure mechanisms have been pointed out during SC stress. The first failure mechanism is related to the increase of leakage current until the parasitic NPN transistor is turned on, leading to the destruction of the device. The second one is related to the degradation of: the gate oxide, source pads and the SiO<sub>2</sub>/SiC interface. These degradations are linked to the extremely high temperature level reached during SC tests and can result in strong degradation or permanent damages. Some papers, including [8] also reveal that during SC tests, tunneling currents result in a transient gate leakage current that has never been observed with silicon power devices [2], [9], [10].

These peculiarities are also put forward to explain a particular turn-ON failure mode which has been shown on some particular devices or under particular electrical constraints during SC [9], [11]. Nevertheless, it seems that this failure mode results in a resistive SC between gate and source which can be explained by aluminum melting resulting in a path between gate and source as depicted in [12].

Ageing tests have been performed using repetitive SC cycles. Some of them start with a very low SC duration and the pulse length is regularly increased until failure. In the case of 1.2 kV devices, the results clearly show that irreversible damage appears. The drain saturation current decreases and the gate leakage current increases. The drain current evolution is not continuous which may indicate a cumulative physical degradation of the device. At the same time a permanent leakage current in reverse bias also increases gradually. In the case of 10 kV SiC MOSFETs, an increase of the on-state resistance  $(R_{DS(on)})$ was observed without significant degradation of the threshold voltage ( $V_{\rm TH}$ ) or the gate-source leakage current ( $I_{\rm GSS}$ ). Failure analysis shows that aluminum metallization layer has undergone a severe reconstruction leading to the appearance of large voids at the contact interface which explains the  $R_{\rm DS(on)}$  evolution [12], [13]. Even if SiC MOSFETs are relatively robust to single pulse SC events up to about 50% of their nominal voltage rating [14], it has been highlighted that the device failure appears before 10  $\mu$ s which is the minimum duration a silicon insulated-gate bipolar transistor is able to sustain. It seems that the failure is related to the degradation of the gate structure due to the very high temperature reached during these tests. Other tests under repetitive SC conditions show different degradations leading to the increase of the threshold voltage and the gate-source leakage current. The gate structure is once again identified as the weakest point [14].

A similar analysis was done after overcurrent pulses [15]. The formation of a conductive path through the oxide yielding was observed leading to the inability to sustain drain—source voltage. It was concluded from experimental tests and simulation results that this failure mode is mainly caused by thermal issues due to the localized heat at the interface between the gate oxide and JFET region. After repetition of several SC events with high temperature variations, failure analysis has pointed out cracks around the oxide region of the degraded device but not in the

TABLE I

SIC MOSFET—Examples of Commercially Available Products

| Туре                    | Reference       | Manufacturer | I <sub>GSS</sub><br>datasheet |

|-------------------------|-----------------|--------------|-------------------------------|

| 1.2 kV / 12 A (TO-247)  | SCT10N120       | STmicroelec. | < 100 nA                      |

| 1.2 kV / 25 A (TO-247)  | LSIC1MO120E0080 | Littlefuse   | < 100 nA                      |

| 1.2 kV / 40 A (TO-247)  | SCH2080KE       | Rohm Co.     | < 100 nA                      |

| 1.2 kV / 40 A (TO-247)  | APT40SM120      | Microsemi    | < 100 nA                      |

| 1.2 kV / 60 A (TO-247)  | C2M0040120D     | Cree Inc.    | < 250 nA                      |

| 1.2 kV / 180 A (module) | BSM180D12P3C007 | Rohm Co.     | < 500 nA                      |

| 1.2 kV / 300 A (module) | CAS300M12BM2    | Cree Inc.    | < 100 nA                      |

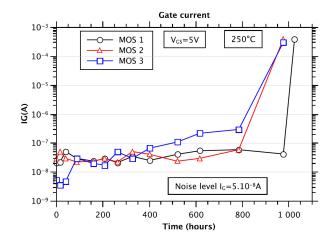

Fig. 1. Evolution of gate leakage current during an ageing test [20].

gate oxide itself even though gate oxide is often referred as the most sensitive part of the SiC MOSFETS [16], [17].

Other studies have pointed out that at relatively low stress (low bias voltage and short SC duration), when the effect of gate oxide degradation and metal reconstruction are eliminated, the ageing of the devices results in a  $V_{\rm TH}$  decrease and an  $I_{\rm DSS}$  increase due to the generation of holes in the oxide [5]. Authors show that the holes can be refilled with time and the degradation reversed when the device is placed under the ambient temperature of 200 °C. It has also been demonstrated that an injection of holes in the gate oxide is the dominant degradation mechanism during repetitive avalanche ageing, and also results in a  $V_{\rm TH}$  decrease [6].

Power cycling leads to an on-state resistance increase due to the ageing of the die and the bond wires. It seems that accelerated ageing has a significant effect in the degradation of the bond wires due to overheating [18]. In [19], ageing tests within safe operating area were performed and authors have showed that  $R_{\rm DS(on)}$  of SiC MOSFETs changes as the device ages, but they have pointed out that  $I_{GSS}$ ,  $I_{DSS}$ , and  $V_{TH}$  also evolve. The variations in  $I_{DSS}$ ,  $I_{GSS}$ , and  $V_{TH}$  indicate that the gate-oxide is the most affected area in SiC MOSFETs. Referring to the Table I, the  $I_{\rm GSS}$  parameter is typically in the nA-range. In [19]–[21], the authors demonstrated a remarkable evolution of  $I_{GSS}$  value at the end of the lifetime of the SiC power devices (up to a few mA). An example of gate current leakage monitoring during ageing tests is provided in Fig. 1. Due to a strong evolution during the ageing process, the gate leakage current is proposed as a practical degradation signature for health monitoring aspects.

The  $I_{\rm GSS}$  parameter represents the gate-source leakage current with the drain connected to the source. This nA-scale current

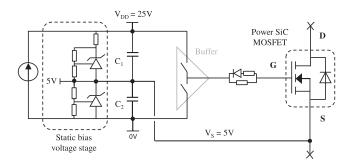

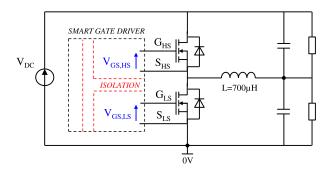

Fig. 2. Typical supply strategy for driving SiC power MOSFET.

is extremely low compared to the typical on-line drain current  $I_D$ .  $I_{GSS}$  is typically obtained by off-line measurement using a curve tracer or a fA-meter [19]. As a result, gate leakage current measurement during normal operation of the device under test (DUT) represents a real challenge. However, online monitoring of the gate leakage current could anticipate power converter failures. Studies have reported a method for online detection of the gate leakage current in SiC MOSFET [21]-[23]. This technique consists in measuring the gate resistance voltage using a differential amplifier to obtain the gate current. This circuit can be easily embedded in a gate driver but sub-mA currents cannot be measured by this method because of the low value of the gate resistance. In this article, an online method for gate leakage current estimation is presented. The proposed principle enables estimation of low leakage currents using a specific gate driver design.

Most of SiC Mosfet power modules require a +20 V/-5 V gate-source voltage for optimal switching, a single 25 V power supply is therefore used in gate drivers for driving SiC power Mosfet. A buffer is required in the gate driver to charge the gate-source capacitance  $C_{\rm GS}$  and the Miller capacitance  $C_{\rm GD}$  in order to switch the device as fast as possible. A command signal is applied on the buffer to drive the power component. In the design presented in Fig. 2, the peak currents are provided by capacitors  $C_1$  and  $C_2$ .

The average gate current is equal to zero in an ideal MOSFET due to the capacitive behavior of the gate-source interface. If the ground voltage (0 V) of the gate driver is chosen at the lowest potential of the drive circuit as shown in Fig. 2, the source voltage must be biased at 5 V by a static bias voltage stage. The 25 V power supply is generally obtained by an isolated dc–dc converter.

The proposed method is explained in the Section II. The implementation of the proposed method on a smart gate driver is presented in Section III. In Section IV, the experimental setup is described. Finally, experimental results are provided to demonstrate the feasibility of this new monitoring feature.

## II. THEORETICAL ANALYSIS OF THE PROPOSED METHOD

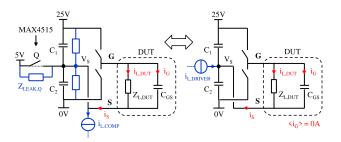

Since the direct measurement of gate leakage current is difficult for sub-mA values, an indirect method was investigated. The proposed method exploits the classical structure of gate drivers detailed in Fig. 2. The principle consists in disconnecting the

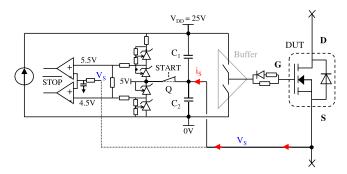

Fig. 3. Proposed integration method for gate leakage estimation.

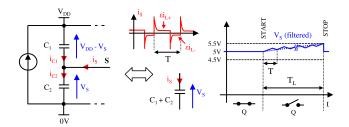

Fig. 4. Dynamic approach for gate leakage modeling.

Fig. 5. Leakage currents on the gate driver.

static bias voltage stage from the capacitive bridge  $(C_1, C_2)$  during the estimation process. Meanwhile, the source potential variation is monitored to deduce the gate leakage current. As shown in Fig. 3, during the estimation process, the source potential variation is enabled within a range of  $\Delta V_S = \pm 0.5 \text{ V}$  around its bias voltage 5 V. The time  $T_L$  required to reach this positive or negative threshold is then used to deduce the gate leakage current value. The estimation process is therefore based on the integration of a low current over a long period of time  $T_L$ .

For the leakage current analysis, a dynamic approach is proposed in Fig. 4, that leads to

$$i_{C1}(t) = C_1 \frac{d(V_{DD} - V_S)}{dt} = -C_1 \frac{dV_S}{dt}$$

(1)

$$i_{C2}(t) = -C_2 \frac{dV_S}{dt} \tag{2}$$

$$i_S(t) = i_{C2}(t) - i_{C1}(t) = (C_1 + C_2) \frac{dV_S}{dt}.$$

(3)

The current  $i_S$  can be expressed as a function of the gate leakage current  $i_{L,DUT}$ . Regarding the model proposed in Fig. 5, the gate current  $i_G$  is defined as the current required to charge

the gate-source capacitance under normal switching conditions

$$i_S(t) = i_G(t) + i_{L,DUT}(t), \langle i_G \rangle = 0$$

(4)

$$V_S = \frac{1}{C_1 + C_2} \int_0^{T_L} i_{L,\text{DUT}}(t) dt + V_S(t = 0). \quad (5)$$

The integration of (5) requires the modeling of the gate leakage current within the power semiconductor device. Considering a resistive model, the voltage variation after n period of the pulsewidth modulation (PWM) signal (*T*) can be expressed as follows:

$$\Delta V_{S,n} = \frac{1}{C_1 + C_2} \left[ n \int_0^{\alpha T} \varepsilon i_{L+} dt + n \int_{\alpha T}^T \varepsilon i_{L-} dt \right]$$

(6)

$$\Delta V_{S,n=T_L/T} = \frac{n T}{C_1 + C_2} \underbrace{\left[\alpha \varepsilon i_{L+} + (1 - \alpha) \varepsilon i_{L-}\right]}_{\langle i_S \rangle}$$

(7)

where  $\varepsilon i_{L+}$  and  $\varepsilon i_{L-}$  are, respectively, the gate leakage currents during the turn-ON and the turn-OFF. As a result, after  $T_L=n\,T$ , the resulting average leakage current measured  $I_{L,\mathrm{MES}}$  by the proposed method is obtained by using

$$\langle i_S \rangle = I_{L,\text{MES}} = I_{L,\text{DRIVER}} + I_{L,\text{DUT}} = (C_1 + C_2) \frac{\Delta V_S}{T_L}$$

(8)

where  $I_{L,\mathrm{DRIVER}}$  is the parasitic average leakage current due to the gate drive system and  $I_{L,\mathrm{DUT}}$  the gate leakage current of the DUT. For low leakage currents,  $T_L$  is typically very long compared to the switching period T of the PWM signal.

As described in Fig. 5, the resulting leakage current  $I_{L, \rm MES}$  represents the total leakage currents seen by the source (S) including the leakages of the system  $I_{L, \rm DRIVER}$  which itself includes leakages on the capacitors, the leakage current of Q, the input current of the comparator stage ( $i_{L, \rm COMP}$ ). As a result, a calibration (CAL) must be performed in order to optimize the precision of the gate leakage estimation system. The leakage value obtained at the CAL is then used as a reference for the entire lifetime of the DUT. Obviously, the leakage currents of the system will also vary during this period, so the leakage value obtained by this method can only estimate the real gate leakage current value in order to detect an evolution during the lifetime.

The proposed method can be implemented as an off-line as well as an online monitoring feature. Offline measurement can be performed when the power converter is not powered. During  $T_L$ , if  $I_{L,\mathrm{DRIVER}}$  is null, the source voltage increases when the DUT is turned-on ( $V_{\mathrm{GS,ON}}=20\,\mathrm{V}$ ) and decreases when the DUT is turned-OFF ( $V_{\mathrm{GS,OFF}}=-5\,\mathrm{V}$ ). The source voltage variation can be explained by the charge/discharge of  $C_1+C_2$  under constant leakage current, depending on the state of the DUT. For example, when the power transistor is switched on,  $C_1$  is discharged while  $C_2$  is charged due to a positive gate leakage current.

Although off-line measurement is interesting for a precise estimation of the gate leakage current, the most relevant application for the proposed method is online monitoring. In normal operation, the DUT can be driven by various types of signals corresponding to various applications. Considering a resistive behavior of the gate-source junction  $R_{\rm GS}$ , the theoretical average

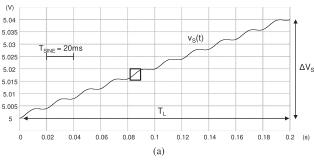

Fig. 6. Simulation of  $v_S(t)$  (a) and zoom at switching period scale (b) for a gate leakage current of 75 nA ( $R_{\rm GS}=1~{\rm M}\Omega$ ) using a PWM command signal.

leakage current obtained by the proposed method is expressed as follows:

$$I_{L,\mathrm{TH}} = \frac{1}{R_{\mathrm{GS}}} \left( \alpha \left( t \right) \cdot \left( V_{\mathrm{GS,ON}} - V_{\mathrm{GS,OFF}} \right) + V_{\mathrm{GS,OFF}} \right)$$

(9)

where  $\alpha(t)$  is the duty cycle of the gate-source voltage signal  $V_{GS}$  and  $V_{DD}$  is the supply voltage ( $V_{DD}=25$  V).

Consequently, for  $\alpha=20\%$ , the leakage currents are compensated during the switching period and the source voltage is stabilized at 5 V. For any other duty cycle value, a variation on the source voltage can be observed when there is a current leakage. For online monitoring, the efficiency of the proposed method depends on the application. However, in the case of a power inverter application, the duty cycle  $\alpha(t)$  is defined by

$$\alpha(t) = \frac{1 + m \cdot \cos(2\pi f t)}{2} \tag{10}$$

where m is the modulation coefficient and f the frequency of the modulating signal.

A simulation of the source voltage variation in power inverter mode is provided in Fig. 6. In this case, the average duty cycle is equal to 50% and the theoretical gate leakage current is defined as

$$I_{L,\text{TH}} = \frac{V_{\text{GS,ON}} + V_{\text{GS,OFF}}}{2 \cdot R_{\text{GS}}} = \frac{15}{2 \cdot R_{\text{GS}}}.$$

(11)

An offline characterization as well as an on-line estimation in a power inverter configuration can be realized using the circuit presented in Fig. 3. The proposed method is therefore particularly relevant for online monitoring considering a power inverter application. The major drawback of this method is the requirement of CAL.

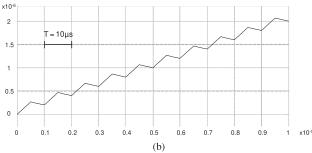

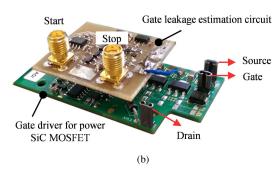

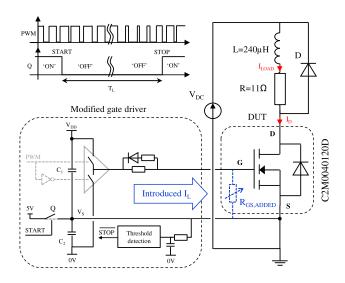

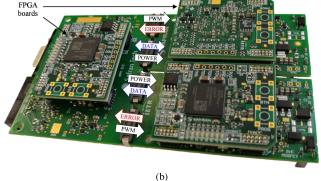

Fig. 7. Dedicated prototype to test the proposed solution. (a) Electronic diagrams. (b) Photograph of the prototype.

#### III. EXPERIMENTAL SETUP

The solution proposed in Section II was tested with an experimental bench, first using a specially dedicated prototype, then integrated in an industrial gate driver.

# A. Prototype Developed to Test the Proposed Solution

The proposed solution was implemented in a prototype as illustrated in Fig. 7. Only two signals are required for the gate leakage estimation method: a START signal to open the electrical switch Q and a STOP signal which interrupt the leakage estimation process when  $V_S$  reaches 4.5 or 5.5 V.

Tests have been performed in order to validate the proposed method. First, an additional gate-source resistance was used to simulate gate leakage current on the DUT, as shown in Fig. 8. The component tested is a discrete SiC power MOSFET (C2M0040120). Then, an "aged device" was tested using the proposed method. This sample was obtained after 480 k SC cycles, the energy corresponding to a single SC cycle is 0.27 J. SC of 1.5  $\mu$ s length were applied every 1.5 s during the ageing process in order to prevent overheating damages. The electrical stress causes an accelerated ageing of the gate-source interface as mentioned in the state of the art. The obtained sample was really precious in this experiment as this power transistor was damaged

Fig. 8. Experimental setup with gate leakage current adjustment for hypothesis validation.

Fig. 9. Source voltage variation during the estimation process for different gate leakage currents (DUT: C2M0040120).

but it was still working. Indeed, a gate leakage current of 2 mA is much more than the optimal value in a "new" component.

Online monitoring was tested with a modulated command signal with a duty cycle corresponding to (9). As illustrated in Fig. 8, a basic chopper circuit was used to test the switching cell as the gate leakage measurement is independent from the power circuit configuration. In this case, a 100 kHz PWM signal was chosen corresponding to a possible SiC power MOSFET application. The modulating signal was chosen with a frequency of 1 kHz.

The best precision is obtained when  $T_{\rm SINE} << T_L$  where  $T_{\rm SINE}$  is the period of the modulating signal.  $T_L$  is typically in the seconds scale, but it can be less than 1 s when an excessive leakage current is detected ( $I_{L,\rm MES} > 10~\mu\rm A$ ).

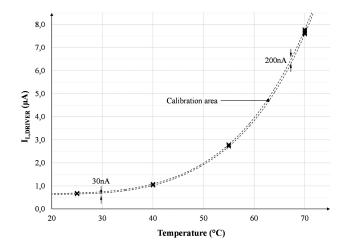

The capacitances  $C_1$  and  $C_2$  are realized by four capacitors of 4.7  $\mu$ F which makes  $C_1 + C_2 = 37.6 \mu$ F ( $\pm 10\%$ ). However, the capacitor value is a temperature-dependent parameter, so the nominal value was used as an approximation for the gate-leakage estimation protocol.

| Gate driver board                                    | PT62SCMD17          | CGD15HB62LP         | CGD15HB62P1         | This work           |

|------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|

| dv/dt immunity                                       | 50 kV/μs            | 100 kV/μs           | 50 kV/μs            | > 125 kV/µs         |

| Short-circuit detection                              | X                   | X                   | X                   | X                   |

| Soft Shut Down (SSD)                                 | -                   | X                   | -                   | X                   |

| Under Voltage Lockout (UVLO)                         | X                   | X                   | X                   | X                   |

| V <sub>DS(on)</sub> monitoring                       | threshold detection | threshold detection | threshold detection | precise measurement |

| Gate leakage current estimation                      | -                   | -                   | -                   | X                   |

| Communication features across the galvanic isolation | _                   | =                   | =                   | X                   |

TABLE II

COMPARISON OF PROTECTION FEATURES IN GATE DRIVER BOARDS

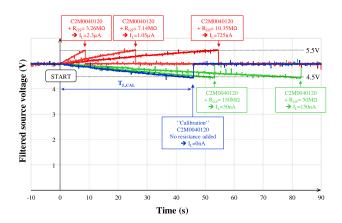

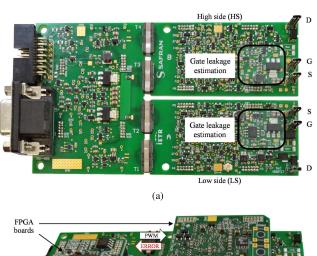

Fig. 10. Implementation in a smart driver board for health monitoring. (a) Top view. (b) Bottom view.

As shown in Fig. 9, the authorized source voltage variation was chosen at  $\Delta V = \pm 0.5 \text{ V}$  to ensure a  $V_{\rm GS}$  signal between -5.5 and +20.5 V in the worst case. The threshold value must be chosen taking into account the targeted performances of the estimation process and the safety conditions for the  $V_{\rm GS}$  signal.

#### B. Proposed Solution Integrated in an Industrial Gate Driver

The proposed solution was also implemented in a smart driver board which integrates Spartan-7 FPGA boards on the primary and secondary circuits. As illustrated in Fig. 10, this board was specifically designed for health monitoring and integrates advanced monitoring features, such as the proposed estimating method,  $V_{\rm DS(on)}$  measurement, communication features in addition to other conventional protection features (galvanic isolation, SC detection, soft shut-down...). Table II proposes a comparison between conventional gate driver boards and the board presented in Fig. 10. In this design, the FPGA are used for data management and leakage current calculation using (7).

The resources required by the calculation of the value of the gate leakage current depends on the targeted resolution. Indeed, if cpt is the counter size and dt is the temporal step of this counter (in seconds), the step in current in the worst case  $\Delta i_{L, \rm min}$  can be expressed as follows:

$$\Delta i_{L,\min} = 2 \cdot (C_1 + C_2) \cdot \frac{|\Delta V_S|}{T_{L,\max}} = 2 \cdot (C_1 + C_2) \cdot \frac{|\Delta V_S|}{cpt \cdot dt}.$$

(12)

Equation (12) is a consequence of the behavior of the voltage variation which can be positive or negative. Consequently, the worst case corresponds to the current value which cancel the (7). In this case, the voltage derivation  $\Delta V_S$  is theoretically equal to zero and  $T_L$  is infinite. In practice, the acquisition time is limited, the counter size and the step time are then defined to meet the targeted resolution. Equations (13) and (14) can be used to define these two parameters

$$dt = (C_1 + C_2) \cdot \frac{|\Delta V_S|}{i_{L,\text{max}}} \cdot \frac{\text{Res}}{1 + \text{Res}}$$

(13)

$$cpt = \frac{i_{L,\text{max}}}{i_{L,\text{min}}} \cdot \frac{1 + \text{Res}}{1 - \text{Res}} \cdot \frac{1}{\text{Res}}$$

(14)

where Res is the targeted resolution (%).

The proposed circuit requires a small number of components as this method requires no Adc converter for acquisition, the high logic level duration of the STOP signal is used to calculate the leakage current. However, the integration of FPGA is not mandatory for the proposed method since the duration of the measurement can be directly compared to the CAL one. The design of this board will not be more detailed in the present article since communication features and data management are not necessary to demonstrate the principle of gate leakage current estimation.

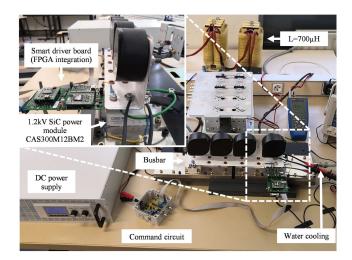

The board was also tested in a power inverter configuration using an inductance of 700  $\mu$ H as described in Figs. 11 and 12. The gate driver board was tested during operation at 47 kVAR under  $V_{\rm DC}=540$  V using a 100 kHz PWM signal with a modulation coefficient of 90%.

Since the hypothesis of a resistive gate-source junction during the ageing was confirmed, the same measurement protocol was used to test the proposed circuit on a power SiC MOSFET module (DUT: CAS300M12BM2). Additional gate-source resistances were used to emulate a gate leakage current during operation in power environment since it is impossible to control precisely the leakage currents of the DUT.

Fig. 11. Validation on a power SiC module (CAS300M12BM2).

Fig. 12. Power inverter with capacitive midpoint.

#### IV. RESULTS

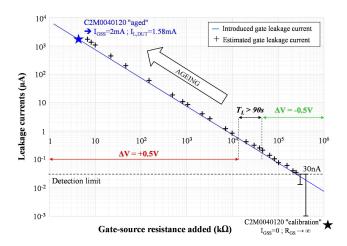

# A. Gate Leakage Current Emulation Using an External $R_{GS}$

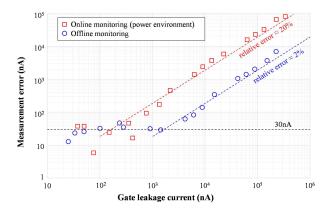

A CAL has been performed with a 1.2 kV power SiC MOSFET (C2M0040120), a component which has never been used in a power converter before. As  $I_{\rm GSS}$  is typically in the fA-range for "new" components, the source voltage variation observed at the CAL is mainly due to the leakages of the system  $I_{L,{\rm DRIVER}}$ . As shown in Fig. 9, the source voltage decreases during  $T_{L,{\rm CAL}}=45.5\,{\rm s}$  corresponding to  $I_{L,{\rm DRIVER}}=-413\,{\rm nA}$  on the test circuit. About 20 trials were performed in order to check the repeatability for the CAL:  $43\,{\rm s} < T_{L,{\rm CAL}} < 46.2\,{\rm s}$  was observed, corresponding to a leakage current between  $-437\,{\rm and}$   $-407\,{\rm nA}$  so the precision of the proposed method is maximum 30 nA at low current. The  $I_{L,{\rm DRIVER}}$  value is different from a circuit to another depending on the parasitic elements of the components used. A CAL at "new" state is therefore required to reach the minimal detection limit of 30 nA.

As explained in Section IV, external gate-source resistances  $R_{\rm GS}$  were added to reproduce the ageing of the DUT. The leakage currents values corresponding to the waveforms given in Fig. 9 are summed up in Table III. For example, the addition of a 150 M $\Omega$  gate-source resistance corresponds to a theoretical gate leakage current of  $I_{L,{\rm TH}}=50$  nA. The experimental results show a negative variation during 53 s which corresponds to  $I_{L,{\rm DUT}}=58$  nA after subtraction of the calibrated value. In

TABLE III

RESULTS CORRESPONDING TO THE WAVEFORMS

| $R_{GS}$ added $(\Omega)$                         | Introduced I <sub>L</sub>                      | $T_L$ $(\Delta V_S +/-)$                                        | $\begin{split} I_{L,MES} = \\ I_{L,DRIVER} + I_{L,DUT} \end{split}$ | Estimated I <sub>L,DUT</sub>                   |

|---------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|

| $CAL$ $(R_{GS} \rightarrow \infty)$               | 0 nA                                           | 45.5s (-)                                                       | -413 nA                                                             | 0 nA                                           |

| 150 MΩ<br>50 MΩ<br>10.35 MΩ<br>7.14 MΩ<br>3.26 MΩ | 50 nA<br>150 nA<br>725 nA<br>1.05 μA<br>2.3 μA | 53 s (-)<br>82.3 s (-)<br>54.5 s (+)<br>25.8 s (+)<br>8.6 s (+) | -355 nA<br>-229 nA<br>+345 nA<br>+729 nA<br>+2.19 μA                | 58 nA<br>184 nA<br>758 nA<br>1.14 μA<br>2.6 μA |

| "aged" device<br>(no extra R <sub>GS</sub> )      | 2 mA*                                          | 11.88 ms<br>(+)                                                 | +1.58 mA                                                            | 1.58 mA                                        |

$^*I_{\mathrm{GSS}} = 2 \,\mathrm{mA}$  measured using ammeter ( $V_{\mathrm{GS}} = 20 \,\mathrm{V}$ ); waveform in Fig. 14.

Fig. 13. Hypothesis validation using the gate leakage estimation circuit at 25 °C (online monitoring).

the case of an gate leakage current of 1.05  $\mu$ A, a positive variation was observed during 25.8 s which corresponds to  $I_{L,\mathrm{DUT}} = 1.14~\mu\mathrm{A}$ .

Results provided in Fig. 13 show the relevance of the proposed method. With the proposed circuit, a gate leakage current as low as 50 nA was clearly identified. However, the source potential variation can be positive or negative which means that for a particular gate leakage current value, the acquisition time is too long ( $T_L > 90$  s). In the investigated case, gate leakage currents between 200 and 500 nA cannot be automatically estimated using the presented method. In Fig. 13, the corresponding points where obtained by measuring the  $\Delta V_S$  value after 90 s. This problem can be solved by adding a positive leakage current to the system in order to have a positive variation during the CAL.

In this case, the source potential variation would be positive at any time ( $\Delta V_S = 0.5 \text{ V}$ ) and the acquisition time should be chosen ( $T_{L,\mathrm{CAL}} < 90 \text{ s}$ ) so that the gate leakage current could only result in a shorter acquisition time.

#### B. Validation of Hypothesis Using an "Aged" Component

The estimated value is related to the  $I_{\rm GSS}$  value but the gate leakage current obtained by this method is different as the measurement is realized under different conditions. A static measurement is required for  $I_{\rm GSS}$  characterization, whereas an on-line monitoring was performed in order to estimate the gate leakage current evolution.

Fig. 14. Source voltage variation with the "aged" device (C2M0040120).

Fig. 15. Comparison between offline and online monitoring at 25 °C using the proposed method (DUT: CAS300M12BM2).

As mentioned in Section III, an "aged" device (C2M0040120) was also tested to validate the hypothesis of a resistive behavior of the gate-source junction for "aged" devices. The component used was precisely characterized before the estimation process:  $I_{\rm GSS}=2$  mA was measured on this device using a fA-meter ( $V_{\rm GSS}=20$  V). A gate leakage current of 1.58 mA was found with the proposed estimation method. The associated waveform are presented in Fig. 14.

In this case, the source potential variation is positive and the acquisition time is very short ( $T_L=11.88~{\rm ms}$ ) compared to the CAL time  $T_{L,{\rm CAL}}$ . The measurement error is about 20% but the targeted application is health monitoring of power semiconductors so only the gate leakage current variation from the calibrated value is monitored. For example, a first warning threshold could be set at 1  $\mu$ A, then, a critical threshold could be set at 10  $\mu$ A. These values are chosen considering the DUT endurance tests. A precise measurement of the real value is not the objective of this article.

## C. Temperature and Precision Considerations

The measurements presented in Fig. 15 confirmed a detection limit about 30 nA and a relative error of 20% for the online monitoring mode. The offline measurement using the same method is more accurate than the online characterization as a relative error of 2% can be reached.

Fig. 16. Leakage current due to the measurement circuit versus temperature (CAL on the smart driver board).

In Fig. 16, the reproducibility of the CAL was tested under different temperatures to highlight the behavior of the parasitic leakages due to the circuit under temperature. The first limitation of this approach is therefore the behavior of the circuit leakages under temperature. The sensitivity of the measurement circuit to temperature is probably mainly due to the choice of the capacitors  $C_1$  and  $C_2$  (Ref: GRM21BR61H475KE51L) which were used to increase the density of integration in the board presented in Fig. 7. The choice of class I capacitors (ex: C0G) would be better for this circuit. A table of CAL under different temperatures can solve this issue at the price of the integration of a temperature, ten measurements were performed demonstrating once again a minimal precision of 30 nA.

Since the leakage current of the circuit depend on the leakages of each component, the  $I_{L,\mathrm{DRIVER}}$  value is not reproducible from a design to another, the calibrated value is valid only in a given board. Another limitation is the ageing of the components used for the estimation circuit itself, such as the capacitors  $C_1$  and  $C_2$ .

#### V. CONCLUSION

The gate leakage current is considered as a pertinent ageing indicator for SiC power MOSFET due to the thickness of the gate oxide and the larger bandgap of these transistors. This parameter is typically less than 100 nA in undamaged components, but it can rise until several  $\mu A$  or mA at the end of the lifetime of the device. Direct measurement of this sensitive parameter is impossible during normal operation because of the working environment and the low value of the leakage currents. A gate leakage estimation using an integration method has been proposed using a smart gate driver. The results demonstrated the ability to identify gate leakage currents as low as 50 nA from their calibrated value. The estimated value does not correspond to a precise measurement of  $I_{GSS}$  due to approximations but the proposed method can provide an estimation of the gate leakage currents during operation. The proposed method need to be tested directly in an accelerated ageing protocol to confirm the ability to detect an ageing on SiC devices. An attention has to be accorded to the choice of the measurement circuit components and their behavior under temperature. The proposed circuit can be easily embedded in a gate driver for an online monitoring application. As a result, the proposed solution offers new perspectives for health monitoring aspects in power electronics.

#### REFERENCES

- [1] R. Singh and A. R. Hefner, "Reliability of SiC MOS devices," *Solid-State Electron.*, vol. 48, no. 10/11, pp. 1717–1720, Oct./Nov. 2004.

- [2] T. T. Nguyen, A. Ahmed, T. V. Thang, and J. H. Park, "Gate oxide reliability issues of SiC MOSFETs under short-circuit operation," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2445–2455, May 2015.

- [3] F. Boige and F. Richardeau, "Gate leakage-current analysis and modelling of planar and trench power SiC MOSFET devices in extreme short-circuit operation," *Microelectron. Rel.*, vol. 76/77, pp. 532–538, Sep. 2017.

- [4] M. Riccio, V. d'Alessandro, G. Romano, L. Maresca, G. Breglio, and A. Irace, "A temperature-dependent SPICE model of SiC power MOSFETs for within and Out-of-SOA simulations," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 8020–8029, Sep. 2018.

- [5] X. Zhou, H. Su, Y. Wang, R. Yue, G. Dai, and J. Li, "Investigations on the degradation of 1.2-kV 4H-SiC MOSFETs under repetitive short-circuit tests," *IEEE Trans. Electron Devices*, vol. 63, no. 11, pp. 4346–4351, Nov. 2016.

- [6] J. Wei, S. Liu, S. Li, J. Fang, T. Li, and W. Sun "Comprehensive investigations on degradations of dynamic characteristics for SiC power MOSFETs under repetitive avalanche shocks," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2748–2757, Mar. 2019.

- [7] T. H. Duong, J. M. Ortiz, D. W. Berning, A. R. Hefner, S. H. Ryu, and J. W. Palmour, "Electro-thermal simulation of 1200v 4H-SiC MOSFET short-circuit SOA," in *Proc. 27th Int. Symp. Power Semicond. Devices IC's*, May 2015, pp. 217–220.

[8] G. Romano *et al.*, "Short-circuit failure mechanism of SiC power MOS-

- [8] G. Romano et al., "Short-circuit failure mechanism of SiC power MOS-FETs," in Proc. 27th Int. Symp. Power Semicond. Devices IC's, May 2015, pp. 345–348.

- [9] C. Chen, D. Labrousse, S. Lefebvre, M. Petit, C. Buttay, and H. Morel, "Study of short-circuit robustness of SiC MOSFETs, analysis of the failure modes and comparison with BJTs," *Microelectron. Rel.*, vol. 55, no. 9, pp. 1708–1713, Aug. 2015.

- [10] Z. Wang et al., "Temperature-dependent short-circuit capability of silicon carbide power MOSFETs," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1555–1566, Feb. 2016.

- [11] A. E. Awwad and S. Dieckerhoff, "Short-circuit evaluation and overcurrent protection for SiC power MOSFETs," in *Proc. 17th Eur. Conf. Power Electron. Appl.*, Sep. 2015.

- [12] C. Chen, "Studies of SiC power devices potential in power electronics for avionic applications," Ph.D. dissertation, Dept. Elect. Eng., Paris-Saclay Univ., Cachan, France, 2016.

- [13] E. P. Eni et al., "Short-circuit degradation of 10-kV 10-A SiC MOSFET," IEEE Trans. Power Electron., vol. 32, no. 12, pp. 9342–9354, Dec. 2017.

- [14] A. Castellazzi, A. Fayyaz, L. Yang, M. Riccio, and A. Irace, "Short-circuit robustness of SiC power MOSFETs: Experimental analysis," in *Proc. IEEE 26th Int. Symp. Power Semicond. Devices*, Jun. 2014, pp. 71–74.

- [15] J. A. Schrock et al., "Failure analysis of 1200 V/150 A SiC MOSFET under repetitive pulsed overcurrent conditions," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 1816–1821, Mar. 2016.

- [16] F. Boige, F. Richardeau, D. Tremouilles, S. Lefebvre, and G. Guibaud, "Investigation on damaged planar-oxide of 1200 V SiC power MOSFETs in non-destructive short-circuit operation," *Microelectron. Rel.*, vol. 76-77, pp. 500–506, Sep. 2017.

- [17] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Failure analysis of a degraded 1.2kV SiC MOSFET after short circuit at high temperature," in *Proc. IEEE Int. Symp. Phys. Failure Anal. Integr. Circuits*, Jul. 2018.

- [18] H. Luo, N. Baker, F. Iannuzzo, and F. Blaabjerg, "Die degradation effect on aging rate in accelerated cycling tests of SiC power MOSFET modules," *Microelectron. Rel.*, vol. 76–77, pp. 415–419, Sep. 2017.

- [19] T. A. Nguyen, S. Lefebvre, and S. Azzopardi, "Effect of short circuit aging on safe operating area of SiC MOSFET," *Microelectron. Rel.*, vol. 88-90, pp. 645–651, Sep. 2018.

- [20] R. Ouaida et al., "Gate oxide degradation of SiC MOSFET in switching conditions," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1284–1286, Dec. 2014.

- [21] F. Erturk, E. Ugur, J. Olson, and B. Akin, "Real-Time ageing detection of SiC MOSFETs," *IEEE Trans. Ind. Appl.*, vol. 55, no. 1, pp. 600–609, Jan./Feb. 2019.

- [22] F. Erturk and B. Akin, "A method for online ageing detection in SiC MOSFETs," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2017, pp. 3576–3581.

- [23] L. Chen, F. Z. Peng, and D. Cao, "A smart gate drive with self-diagnosis for power MOSFETs and IGBTs," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Feb. 2008, pp. 1602–1607.

**Julien Weckbrodt** was born in France in 1993. He received the M.Sc.Eng. degree in electrical engineering from the Polytechnical National Institute of Bordeaux in 2016, and the Ph.D. degree in electrical engineering at the University of Nantes, Nantes, France.

His work is supported by Safran Group. His research interests include gate drivers, WBG power semiconductors, and electromagnetic compatibility.

**Nicolas Ginot** was born in France, in 1977. He received the B.S. degree in engineering from the Ecole Polytechnique de l'Université de Nantes, Nantes, France, in 2001, and the Ph.D. degree in electrical engineering in 2004.

From 2001 to 2007, he was with the Industry on Military and Railway Power Electronic Converters. He is currently a Professor with the Institut Universitaire de Technologie, Nantes, France, and the Institute of Electronics and Telecommunications of Rennes, Rennes, France, where he works on communicating

system for power electronic applications and smart drivers.

**Christophe Batard** was born in France, in 1965. He received the Ph.D. degree in electrical engineering from the Institut National Polytechnique de Toulouse, Toulouse, France, in 1992.

He was a Postdoctoral Researcher with the University of Birmingham, Birmingham, U.K., for one year, where he worked on the modeling of power diodes. In 1993, he joined the Institut Universitaire de Technologie, Nantes, France, as an Assistant Professor. He then conducted research with the Institute of Electronics and Telecommunications of Rennes, where he works

on modeling of power converters, communicating system over high current, and power line communication in a power electronic environment.

Stephane Azzopardi received both the M.Sc.Eng. degree from the Graduate School of Engineering INSA of Toulouse, Toulouse, France, the M.S. degree from the University of Toulouse, Toulouse, France, in 1993 and the Ph.D. degree in electronics from the University of Bordeaux, Bordeaux, France, in 1998. He also received the HDR (qualification to drive research activities) in 2012.

Then, he spent two years as Post-doctorate with the Laboratory of Professor Kawamura at the Yokohama National University, Yokohama, Japan. In 2003,

he became an Associate Professor with the Graduate School of Engineering ENSEIRB-MATMECA in Bordeaux, Bordeaux, France. He joined the Research and Technology Center of Safran Group in September 2015, where he manages the expert team on "components, power modules and materials." His research interests include robustness and reliability of power semiconductor devices for aeronautical applications.