# RD53 analog front-end processors for the ATLAS and CMS experiments at the High-Luminosity LHC

L. Gaioni, M Manghisoni, V Re, E Riceputi, G Traversi, M B Barbero, D Fougeron, S Godiot, M Menouni, P Pangaud, et al.

#### ▶ To cite this version:

L. Gaioni, M Manghisoni, V Re, E Riceputi, G Traversi, et al.. RD53 analog front-end processors for the ATLAS and CMS experiments at the High-Luminosity LHC. 28th International Workshop on Vertex Detectors (Vertex 2019), Oct 2019, Lopud, Croatia. pp.021, 10.22323/1.373.0021. hal-03128915

# HAL Id: hal-03128915

https://hal.science/hal-03128915

Submitted on 2 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# RD53 analog front-end processors for the ATLAS and CMS experiments at the High-Luminosity LHC

```

L. Gaioni*a, M. Manghisonia, V. Rea, E. Riceputia, G. Traversia, M.B. Barberob,

D. Fougeron<sup>b</sup>, S. Godiot<sup>b</sup>, M. Menouni<sup>b</sup>, P. Pangaud<sup>b</sup>, A. Rozanov<sup>b</sup>, P. Breugnon<sup>b</sup>,

M. Bomben<sup>c</sup>, G. Calderini<sup>c</sup>, F. Crescioli<sup>c</sup>, O. Le Dortz<sup>c</sup>, G. Marchiori<sup>c</sup>, D. Dzahini<sup>d</sup>,

F.E. Rarbi<sup>d</sup>, R. Gaglione<sup>e</sup>, H. Krüger<sup>f</sup>, M. Daas<sup>f</sup>, Y. Dieter<sup>f</sup>, T. Hemperek<sup>f</sup>,

F. Hügging<sup>f</sup>, K. Moustakas<sup>f</sup>, D. Pohl<sup>f</sup>, P. Rymaszewski<sup>f</sup>, M. Standke<sup>f</sup>, M. Vogt<sup>f</sup>,

T. Wang<sup>f</sup>, N. Wermes<sup>f</sup>, M. Karagounis<sup>f1</sup>, A. Stiller<sup>f1</sup>, C. Marzocca<sup>g</sup>, G. De Robertis<sup>h</sup>,

F. Loddo<sup>h</sup>, F. Licciulli<sup>h</sup>, A. Andreazza<sup>i</sup>, V. Liberali<sup>i</sup>, A. Stabile<sup>i</sup>, L. Frontini<sup>i</sup>,

M. Bagatin<sup>1</sup>, D. Bisello<sup>1</sup>, S. Gerardin<sup>1</sup>, S. Mattiazzo<sup>1</sup>, A. Paccagnella<sup>1</sup>, D. Vogrig<sup>1</sup>,

S. Bonaldo<sup>1</sup>, N. Bacchetta<sup>1</sup>, G. Della Casa<sup>n</sup>, N. Demaria<sup>n</sup>, G. Mazza<sup>n</sup>, E. Monteil<sup>n</sup>,

L. Pacher<sup>n</sup>, A. Paternò<sup>n1</sup>, A. Rivetti<sup>n</sup>, M.D. Da Rocha Rolo<sup>n</sup>, L. Ratti<sup>o</sup>, C. Vacchi<sup>o</sup>,

K. Androsov<sup>p1</sup>, R. Beccherle<sup>p</sup>, G. Magazzu<sup>p</sup>, M. Minuti<sup>p</sup>, F. Morsani<sup>p</sup>, F. Palla<sup>p</sup>,

S. Poulios<sup>p</sup>, G.M. Bilei<sup>s</sup>, M. Menichelli<sup>s</sup>, D. Passeri<sup>t</sup>, P. Placidi<sup>t</sup>, D. Gajanana<sup>z</sup>,

V. Gromov<sup>z</sup>, B. van Eijk<sup>z</sup>, R. Kluit<sup>z</sup>, A. Vitkovskiy<sup>z</sup>, T. Benka<sup>z1</sup>, M. Havranek<sup>z1</sup>,

Z. Janoska<sup>z1</sup>, M. Marcisovsky<sup>z1</sup>, G. Neue<sup>z1</sup>, L. Tomasek<sup>z1</sup>, V. Kafka<sup>z2</sup>, V. Vrba<sup>z2</sup>,

I. Vila<sup>z3</sup>, E.M.S.Jiménez<sup>z3</sup>, E. Lopez-Morillo<sup>z4</sup>, F.R. Palomo<sup>z4</sup>, F. Muñoz<sup>z4</sup>,

D. Abbaneo<sup>z5</sup>, J. Christiansen<sup>z5</sup>, N. Emriskova<sup>z5</sup>, S. Orfanelli<sup>z5</sup>, S. Marconi<sup>z5</sup>,

L.M.Jara Casas<sup>z5</sup>, S. Bell<sup>z6</sup>, M.L. Prydderch<sup>z6</sup>, S. Thomas<sup>z6</sup>, D.C. Christian<sup>z7</sup>,

G.Deptuch<sup>z7</sup>, F. Fahim<sup>z7</sup>, J. Hoff<sup>z7</sup>, R. Lipton<sup>z7</sup>, T. Liu<sup>z7</sup>, T. Zimmerman<sup>z7</sup>, S. Miryala<sup>z7</sup>,

M. Garcia-Sciveres<sup>z8</sup>, D. Gnani<sup>z8</sup>, A. Krieger<sup>z8</sup>, K. Papadopoulou<sup>z8</sup>, T. Heim<sup>z8</sup>,

A. Dimitrievska<sup>z8</sup>, R. Carney<sup>z8</sup>, B. Nachman<sup>z8</sup>, C. Renteira<sup>z8</sup>, V. Wallangen<sup>z8</sup>,

M. Hoeferkamp<sup>z9</sup>, S. Seidel<sup>z9</sup>

```

- <sup>a</sup>INFN Sezione di Pavia and Università di Bergamo, Bergamo, Italy

- <sup>b</sup>Aix Marseille Université, CNRS/IN2P3, CPPM UMR 7346, 13288, Marseille, France

- <sup>c</sup> Laboratoire de Physique Nucléaire et de Hautes Energies (LPNHE) Paris, France

- <sup>d</sup>Laboratoire de Physique Subatomique et de Cosmologie (LPSC), Grenoble, France

- <sup>e</sup>Laboratoire d'Annecy-le-Vieux de Physique des Particules (LAPP), Annecy-le-Vieux, France

- <sup>f</sup>Rheinische Friedrich-Wilhelms-Universität Bonn Physikalisches Institut, Bonn, Germany

- <sup>f1</sup>Fachhochschule Dortmund, Germany

- <sup>g</sup>Politecnico di Bari, Bari, Italy

- <sup>h</sup>INFN Sezione di Bari, Bari, Italy

- <sup>i</sup>INFN Sezione di Milano and Università degli Studi di Milano, Milano, Italy

- <sup>1</sup> INFN Sezione di Padova and Università di Padova, Padova, Italy

- <sup>m</sup>INFN Sezione di Padova, Padova, Italy

- <sup>n</sup>INFN Torino, v.P.Giuria 1, 10125 Torino, Italy

- <sup>n1</sup>Politecnico di Torino and INFN Sezione di Torino, Torino, Italy

- <sup>o</sup>INFN Sezione di Pavia and Università di Pavia, Pavia, Italy

- <sup>p</sup>INFN Sezione di Pisa, Pisa, Italy

- <sup>p1</sup>INFN Pisa and Università di Siena, Siena, Italy

- <sup>q</sup>INFN Sezione di Pisa and Università di Pisa, Pisa, Italy

- <sup>s</sup>INFN Sezione di Perugia, Perugia, Italy

- <sup>t</sup>INFN Sezione di Perugia and Department of Engineering, Università di Perugia, Italy

- VINFN Sezione di Torino and University of Torino, Torino, Italy

- <sup>z</sup>National Institute for Subatomic Physics (NIKHEF), Amsterdam Netherlands

- <sup>z1</sup>Faculty of Nuclear Sciences and Physical Engineering of the Czech Technical University (FNSPE-CTU)

- <sup>z2</sup>Institute of Physics of the Academy of Sciences of the Czech Republic (IP-ASCR)

- <sup>z3</sup>Instituto de Fisica de Cantabria (IFCA, CSIC-UC), Santander, Spain

- <sup>z4</sup>Electronic Engineering Dept, School of Engineering, Sevilla University, Spain

- <sup>z5</sup>European Organization for Nuclear Research (CERN), Geneva, Switzerland

- z6 Science and Technology Facilities Council, Rutherford Appleton Laboratory, Chilton, Didcot, United Kingdom

- <sup>z7</sup>Fermi National Accelerator Laboratory (FNAL) Batavia, USA

- <sup>z8</sup>Lawrence Berkeley National Laboratory (LBNL), Berkeley, USA

- <sup>z9</sup>University of New Mexico (UNM), Albuquerque, USA

E-mail: luigi.gaioni@unibg.it

This work discusses the design and the main results relevant to the characterization of analog front-end processors in view of their operation in the pixel detector readout chips of ATLAS and CMS at the High-Luminosity LHC. The front-end channels presented in this paper are part of RD53A, a large scale demonstrator designed in a 65 nm CMOS technology by the RD53 collaboration. The collaboration is now developing the full-sized readout chips for the actual experiments. Some details on the improvements implemented in the analog front-ends are provided in the paper.

The 26th International workshop on vertex detectors October 13-18, 2019 Lopud, Croatia

<sup>\*</sup>Speaker.

### 1. Introduction

The Phase-II upgrades of ATLAS and CMS will require a complete new tracker with readout electronics facing striking requirements on particle rates and radiation hardness. The design of new pixel readout chips is being tackled in the framework of the RD53 collaboration [1], [2] using a 65 nm CMOS technology. The collaboration's goals, besides the development of the production chips for the high-luminosity upgrades of the experiments, include the detailed understanding of the radiation effects taking place at the 65 nm CMOS node [3], [4] and the design of a shared rad-hard IPs library.

The efforts of the collaboration led to the submission, in 2017, of RD53A, a large scale demonstrator chip integrating a  $400 \times 192$  pixels matrix. The chip includes a number of design variations, among which three different analog front-ends and two digital readout architectures, to allow for detailed performance comparisons. The RD53A chip has been thoroughly investigated during the last two years, and the three analog front-ends underwent a detailed review process in view of their integration in the production chips.

The design of the final chips is being carried out by the collaboration in a common design framework called RD53B, with two submissions, one for the ATLAS chip and the other for the CMS one, planned for November 2019 and April 2020, respectively.

## 2. RD53A analog front-ends

RD53A chip is mainly conceived to demonstrate in a large format IC the suitability of the chosen 65 nm technology for the HL-LHC upgrades of ATLAS and CMS in terms of radiation tolerance, stable low threshold operation and high hit and trigger rate capabilities. The main specifications of the chip are shown in Table 1. The chip includes a  $400 \times 192$  pixels matrix with a pitch of  $50 \, \mu \text{m} \times 50 \, \mu \text{m}$  and features, approximately, half the size of the production chips. The periphery is placed at the bottom of the chip and includes the circuitry needed to bias, configure, monitor and read out the matrix: the analog building blocks are integrated in a macroblock called analog chip bottom surrounded by the logic blocks, grouped in the so-called digital chip bottom. The wire bonding pads are organized as a single row at the bottom chip edge. A row of test pads, conceived for debugging purposes, is also integrated in the top region of the chip. RD53A is designed to op-

Specification Value Comments Hit rate 3 GHz/cm<sup>2</sup> Trigger rate 1 MHz max Trigger latency  $12.5 \mu s$ Hit loss < 1% at max hit rate Detection threshold  $< 600 e^{-}$ In-time threshold < 1200 e<sup>-</sup>  $< 10^{-6}$ Noise occupancy per pixel 50 fF load; in a 25 ns interval 500 Mrad ( $1 \times 10^{16}$ 1 Mev eq. n/cm<sup>2</sup>) Radiation tolerance (TID) replacement after ~5 years operation

**Table 1:** Main specifications of RD53A chip [5].

erate with serial powering and integrates shunt LDOs [6] already dimensioned for the production chip.

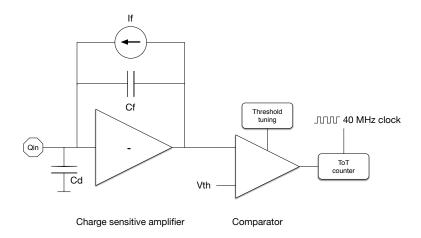

The RD53A matrix is divided into 3 regions featuring different analog front-ends, called synchronous (128 matrix columns), linear (136 columns) and differential (136 columns), sharing the general architecture shown in Fig. 1. The three front-ends feature a charge sensitive amplifier (CSA) connected to a threshold discriminator whose output drives a time-over-threshold (ToT) counter used for the analog-to-digital conversion of the signals. In RD53A the ToT is run at 40 MHz and provides 4 bits for digitization.

The synchronous front-end (SYNC) integrates a CSA with Krummenacher feedback [7] which provides, on one hand, a linear discharge of the CSA feedback capacitance and, on the other hand, a compact solution to cope with the large radiation-induced increase in the detector leakage current. A synchronous discriminator is AC-coupled to the preamplifier and includes an offset compensated differential amplifier and a positive feedback latch. The SYNC front-end does not require any inpixel DAC for local threshold adjustment, since tuning is performed by means of autozeroing. The SYNC can be operated in a fast ToT counting mode in which the latch is turned into a local oscillator running at up to 900 MHz.

The linear front-end (LIN) features a Krummenacher feedback preamplifier DC-coupled to a current comparator. The latter consists of a transconductance stage followed by a Träff amplifier [8] with low input impedance. Threshold tuning is performed by means of a 4-bit in-pixel current DAC based on a binary weighted architecture.

The differential front-end (DIFF) includes a continuous reset integrator with DC-coupled precomparator stage and a fully differential input comparator. The CSA stage integrates a constant current feedback capable of preventing the input from saturating in the presence of detector leakage currents of the order of few nanoamps. For larger currents, a leakage current compensation circuit, similar to the one integrated in the FEI4 chip [9], can be enabled. Local tuning of the threshold is performed by exploiting one 4-bit resistor ladder in each pre-comparator branch, resulting in an effective 5-bit adjustment.

Common to all front-ends is the calibration injection circuit, which makes it possible both to gen-

Figure 1: RD53A front-end architecture.

erate two consecutive signals with the same polarity and to inject a different amount of charge in neighbouring pixels at the same time. The three front-end designs feature approximately the same layout area and bump bond pads, making them easily interchangeable on the pixel matrix layout. The bias distribution follows the same organization for all three front-end flavours. Further details on the analog front-ends integrated in RD53A can be found in [10], [11], [12].

#### 3. Test results

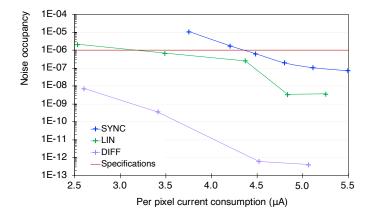

In view of the integration of the analog front-ends in the production chips, an extensive testing campaign has been carried out within the RD53, CMS and ATLAS communities. Among RD53A specifications, reported in Table 1, noise occupancy requirements set severe constraints on both noise and threshold dispersion performance of the analog front-ends. Equivalent noise charge (ENC) and threshold dispersion have been measured for bare chips and assemblies. In particular, tests have been performed on readout chip connected to  $50~\mu\text{m} \times 50~\mu\text{m}$  and  $100~\mu\text{m} \times 25~\mu\text{m}$  planar sensors. Measured ENCs are in general below 100 electrons r.m.s., except for the synchronous front-end assemblies, featuring an average ENC close to 120 electrons r.m.s. [13]. The noise occupancy of the three RD53A front-ends is shown in Fig. 2 as a function of the per-pixel analog current consumption. Data reported in the figure are relevant to front-ends connected to  $100~\mu\text{m} \times 25~\mu\text{m}$  planar sensors with a threshold set to 1200 electrons. The differential front-end features excellent noise performance, even at low current consumption. The linear and the synchronous front-ends have to be operated with larger currents,  $3.5~\mu\text{A}$  and  $4.5~\mu\text{A}$  respectively, in order not to exceed the  $10^{-6}$  noise occupancy specification.

At the HL-LHC, with its 25 ns bunch structure, the so-called in-time threshold is a key parameter. The absolute threshold does not depend on timing, and is defined as the input charge signal having a 50% probability of firing the discriminator. On the other hand, in-time threshold strongly depends on timing, and represents the minimum input signal that can be detected in the correct bunch crossing. Notice that, in general, a lower absolute threshold could be needed in order to achieve a given in-time threshold. A parameter called overdrive can thus be introduced, being simply the difference between the in-time and the absolute threshold. A 1200 e<sup>-</sup> minimum in-time threshold

Figure 2: Pixel noise occupancy as a function of the per-pixel analog current consumption.

|                          | SYNC | LIN | DIFF |

|--------------------------|------|-----|------|

| bare chip                | 0    | 147 | 17   |

| bare irradiated 500 Mrad | 1    | 146 | 33   |

| $50x50 \mu m^2$ sensor   | 0    | 341 | -    |

| $100x25 \mu m^2$ sensor  | 0    | 293 | 36   |

**Table 2:** Overdrive (in e<sup>-</sup>) for bare chips and assemblies tuned to 1000 and 1200 e<sup>-</sup> in-time threshold.

specification has been set for RD53A, with a maximum overdrive of  $600 \, e^-$ . Table 2 shows the overdrive of bare chips (also after X-ray irradiation with a total ionizing dose (TID) of  $500 \, \text{Mrad}$ ) tuned to an in-time threshold of  $1000 \, e^-$  and of assemblies tuned to  $1200 \, e^-$ . All the front-ends connected to sensors can be operated with an in-time threshold of  $1200 \, \text{electrons}$ , with the LIN featuring the largest overdrive and the SYNC an overdrive close to zero, thanks to the synchronous structure of its comparator.

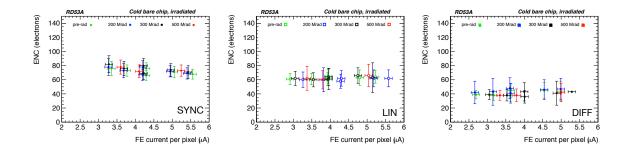

The radiation hardness properties of the RD53A chip have been thoroughly investigated in several irradiation campaigns during which the analog front-ends have been exposed to TIDs up to 1 Grad. In general, no major degradations in analog performance were detected after irradiation at temperatures compatible to the ones in use in the actual experiments, with all the three front-ends able to operate at low thresholds even at 1 Grad TID. As an example, Fig. 3 shows the ENC as a function of the pixel analog current consumption for different TIDs (200, 300 and 500 Mrad). Irradiation was performed with X-rays at cold, with RD53A powered on and read out continuously. No significant effects are detectable on the noise performance of the front-ends after irradiation [14].

#### 4. RD53B developments on analog front-ends

RD53A, with the very promising results emerged from its characterization, is out of doubt one of the most important milestones toward the development of the final chips for ATLAS and CMS, being developed in a common design framework called RD53B. The production chips will include all the RD53A elements with bug fixes and, where needed, technical improvements. A number of additional features will be implemented in RD53B designs [15], such as dedicated bias of edge and top pixels of the matrix, triple modular redundancy for pixel configuration and optimized data formatting and compression, just to name a few.

**Figure 3:** ENC as a function of the pixel analog current consumption for different TIDs.

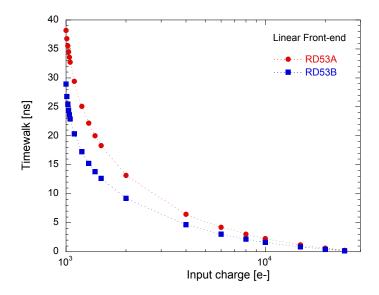

Figure 4: Time-walk as a function of input charge for the RD53A and RD53B versions of the linear frontend

After a detailed review process, the two experiments made their choice for the analog front-end integration in the production chips: the differential front-end will be integrated in the ATLAS chip, whereas the linear will be operated in CMS. The ATLAS choice was mainly driven by the excellent noise occupancy performance of the differential front-end, achieved even at rather low current consumption. On the other hand, the linear front-end has been recommended by the review committee as the lowest risk option for the integration in the production chips. Moreover, CMS requires a fast preamplifier return to baseline, with a target discharge rate of 3000 e<sup>-</sup>/25 ns which is at the limit for the DIFF, but which the LIN can accomplish with some margin. These arguments, along with the capability of the linear front-end to cope with large detector leakage currents, drove the CMS choice [13].

In the RD53B framework, a number of improvements of the analog front-ends are being implemented according to reviewers' comments and to experiment requirements. As far as the LIN is concerned, a weak point that emerged from the test campaign is its large overdrive. In RD53B, a partial re-design of the comparator transimpedance stage led to significant improvements of the time-walk performance of the front-end. It is worth mentioning that time-walk is strictly related to the overdrive and is defined, for a given input charge signal, as the difference between the time needed to fire the discriminator in response to that specific input signal and the one needed for an arbitrarily large signal. The improvement is clearly visible in Fig. 4, which shows the timewalk as a function of the input charge for the RD53A and RD53B versions of the linear front-end. The RD53B LIN will also include an improved, 5-bit threshold tuning DAC to reduce channel-to-channel dispersion of the threshold.

An issue related to the differential front-end is a large and systematic ToT dispersion, detected in the initial testing of the RD53A DIFF. Such a dispersion is actually due to a missing "place & route" constraint at the front-end output in the basic building block of the matrix, called core (a region of  $8\times8$  pixels). This, in turn, translated to varying load capacitances on the comparator outputs across

the core and, ultimately, in a systematic variation of the ToT. The issue has been easily fixed in RD53B by pre-placing and pre-routing digital buffers at the comparator outputs in the matrix core. For the differential front-end a pixel by pixel variation of the hit signal edges has been also detected [14] (the hit signal being the digital signal toggling for an input signal crossing the threshold). Such a digital signal is triggered, in the RD53A version of the DIFF, by the comparator output falling edge which features a very low slew rate, resulting in a large dispersion of the hit leading edge. In RD53B the hit signal will be triggered by the faster rising edge of the comparator output, making the timing dispersion of the RD53B DIFF comparable to the dispersion measured for the linear front-end.

#### 5. Conclusion

Future pixel detectors at the High-Luminosity LHC require a new generation of readout chips complying with tough requirements in terms of speed, noise, power consumption and radiation hardness. The design of such advanced chips is being tackled in the framework of the RD53 collaboration using a 65 nm CMOS technology. The collaboration submitted the RD53A demonstrator, a large scale chip that has been thoroughly characterized during the last two years, with very promising results. Three analog front-end flavours, called synchronous, linear and differential, were integrated in RD53A. The main analog performance has been assessed for each analog front-end. Very good noise properties, retained also after irradiation with X-rays for TIDs up to 1 Grad, have been obtained, in particular for the differential front-end. The success of RD53A is the baseline for the design of the pixel readout chips of CMS and ATLAS at the HL-LHC, being designed in a common framework called RD53B. ATLAS and CMS chips are planned to be submitted in November 2019 and April 2020 respectively, as implementations of the RD53B design, with the ATLAS chip featuring the differential front-end and the CMS integrating the linear front-end.

#### 6. Acknowledgement

This work was supported by H2020 Project AIDA-2020 under Grant 654168.

#### References

- [1] RD53 web site, http://rd53.web.cern.ch/rd53/

- [2] J. Christiansen and M. Garcia-Sciveres, 2013 RD Collaboration proposal: Development of pixel readout integrated circuits for extreme rate and radiation, CERN-LHCC-2013-008, http://cds.cern.ch/record/1553467?ln=en LHCC-P-006

- [3] L.M. Jara Casas et al., "Characterization of radiation effects in 65 nm digital circuits with the DRAD digital radiation test chip", *Journal of Instrumentation*, vol. 12, no. 02, C02039 (2017).

- [4] M. Menouni et al., "1-Grad total dose evaluation of 65 nm CMOS technology for the HL-LHC upgrades", *Journal of Instrumentation*, vol. 10 C05009, pp. 1-15, May 2015, doi:10.1088/1748-0221/10/05/C05009.

- [5] RD53A Integrated Circuit Specifications. ONLINE: https://cds.cern.ch/record/2113263/files/RD53A\_specs\_V3\_2.pdf.

- [6] M. Karagounis et al., "An integrated Shunt-LDO regulator for serial powered systems", *Proceedings of ESSCIRC 2009*, Athens, Greece, pg. 276-279 (2009).

- [7] F. Krummenacher, "Pixel detectors with local intelligence: an IC designer point of view", *Nucl. Instrum. and Methods*, vol. 305 (3), pp. 527-532, Aug. 1991, doi:10.1016/0168-9002(91)90152-G

- [8] H. Träff, "Novel Approach to High Speed CMOS Current Comparators", *Elect. Lett.*, vol. 28 no. 3, pp. 310-312, Jan. 1992, doi:10.1049/el:19920192.

- [9] M. Garcia-Sciveres et al., "The FE-I4 pixel readout integrated circuit", *Nucl. Instrum. and Methods*, vol. 636 (1), pp. S155-S159, Apr. 2011, doi:10.1016/j.nima.2010.04.101

- [10] L. Pacher et al., "A Low-Power Low-Noise Synchronous Pixel Front-End Chain in 65 nm CMOS Technology with Local Fast ToT Encoding and Autozeroing for Extreme Rate and Radiation at HL-LHC", proceeding of the 2015 IEEE Nuclear Science Symposium and Medical Imaging Conference (IEEE NSS/MIC), 2015 IEEE, doi:10.1109/NSSMIC.2015.7581969

- [11] L. Gaioni et al., "65 nm CMOS analog front-end for pixel detectors at the HL-LHC", *Journal of Instrumentation*, vol. 11 (2016), C02049. doi:10.1088/1748-0221/11/02/C02049

- [12] M. Garcia-Sciveres et al., "Results of FE65-P2 Pixel Readout Test Chip for High Luminosity LHC Upgrades", PoS ICHEP2016 272 (2016)

- [13] N. Emriskova et al., "Analog front-end characterization of the RD53A chip", presented at the 2019 Topical Workshop on Electronics for Particle Physics (TWEPP 2019).

- [14] A. Dimitrievska et al., "RD53A: a large-scale prototype chip for the phase II upgrade in the serially powered HL-LHC pixel detectors", *presented at the 15th Vienna Conference on Instrumentation (VCI 2019)*.

- [15] RD53B Design Requirements. ONLINE: https://cds.cern.ch/record/2663161/files/RD53B\_Requirements\_V3\_1.pdf