# Development of a CMOS-compatible carbon nanotube array transfer method

Chun Fei Siah, Lucas Yu Xiang Lum, Jianxiong Wang, Simon Chun Kiat Goh, Chong Wei Tan, Liangxing Hu, Philippe Coquet, Hong Li, Chuan Seng Tan, Beng Kang Tay

# ▶ To cite this version:

Chun Fei Siah, Lucas Yu Xiang Lum, Jianxiong Wang, Simon Chun Kiat Goh, Chong Wei Tan, et al.. Development of a CMOS-compatible carbon nanotube array transfer method. Micromachines, 2021, 12 (1), 95, 6 p. 10.3390/mi12010095 . hal-03127449

# HAL Id: hal-03127449 https://hal.science/hal-03127449

Submitted on 1 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

# Article Development of a CMOS-Compatible Carbon Nanotube Array Transfer Method

Chun Fei Siah <sup>1,†</sup>, Lucas Yu Xiang Lum <sup>1,†</sup>, Jianxiong Wang <sup>2</sup>, Simon Chun Kiat Goh <sup>2</sup>, Chong Wei Tan <sup>1</sup>, Liangxing Hu <sup>1</sup>, Philippe Coquet <sup>2,3</sup>, Hong Li <sup>2,4</sup>, Chuan Seng Tan <sup>1</sup>, and Beng Kang Tay <sup>1,2,\*</sup>

- <sup>1</sup> Centre for Micro- and Nano-Electronics (CMNE), School of Electrical and Electronic Engineering, Nanyang Technological University, 50 Nanyang Ave, Singapore 639798, Singapore; chunfei001@e.ntu.edu.sg (C.F.S.); e190013@ntu.edu.sg (L.Y.X.L.); ChongWei@ntu.edu.sg (C.W.T.); lxhu@ntu.edu.sg (L.H.); TanCS@ntu.edu.sg (C.S.T.)

- <sup>2</sup> CNRS-NTU-THALES Research Alliances/UMI 3288, Research Techno Plaza, 50 Nanyang Ave, Border X Block, Level 6, Singapore 637553, Singapore; jxwang@ntu.edu.sg (J.W.); singapore ach@ntu.edu.sg (G.C.K.C.); Philippe Consul@numeric(G.C.K.C.);

- simon.goh@ntu.edu.sg (S.C.K.G.); Philippe.Coquet@cnrs.fr (P.C.); ehongli@ntu.edu.sg (H.L.) Institut d'Electronique, de Micro Electronique et de Nanotechnologie (IEMN),

- CNRS UMR 8520-Université de Lille, 59650 Villeneuve d'Ascq, France

School of Mechanical and Aerospace Engineering, Nanyang Technological University, 50 Nanyang Ave,

- Singapore 639798, Singapore

- \* Correspondence: EBKTAY@ntu.edu.sg

- + Both authors contribute equally to this manuscript.

**Abstract:** Carbon nanotubes (CNTs) have, over the years, been used in research as a promising material in electronics as a thermal interface material and as interconnects amongst other applications. However, there exist several issues preventing the widespread integration of CNTs onto device applications, e.g., high growth temperature and interfacial resistance. To overcome these issues, a complementary metal oxide semiconductor (CMOS)-compatible CNT array transfer method that electrically connects the CNT arrays to target device substrates was developed. The method separates the CNT growth and preparation steps from the target substrate. Utilizing an alignment tool with the capabilities of thermocompression enables a highly accurate transfer of CNT arrays onto designated areas with desired patterns. With this transfer process as a starting point, improvement pointers are also discussed in this paper to further improve the quality of the transferred CNTs.

Keywords: carbon nanotubes; microelectronics fabrication; bonding; temperature

# 1. Introduction

In the past few decades, carbon nanotubes (CNTs) have stimulated a large interest in the research world for their material properties. The discovery of their extraordinary mechanical [1], electrical [2], and thermal [3] properties prophesized CNTs as the next revolutionary material in numerous applications such as interconnect [4], thermal management [5], field-emission [6], and on-board electromagnetic shielding [7].

The integration of CNTs into real-world applications is faced with several difficulties [8]. First, the high growth temperature of CNTs, over 600 °C, is not compatible with complementary metal oxide semiconductor (CMOS) device fabrication processes. Second, a diffusion barrier layer [9] between the catalyst and the growth substrate is required for the growth of CNTs using chemical vapor deposition (CVD). This leads to an additional interfacial resistance between the substrate and CNTs. Third, the CVD processes deposit by-products such as amorphous carbon (a–c) [10] from unconsumed process gases, which can short-circuit the metal electrodes present on the surface of the substrate, reducing yield and device performance. Fourth, micro-fabrication processes such as photolithography and chemical-mechanical polishing can also affect the quality of CNT growth [11]. The non-planar and complex geometries of fabricated microelectronic device substrates can also

Citation: Siah, C.F.; Lum, L.Y.X.; Wang, J.; Goh, S.C.K.; Tan, C.W.; Hu, L.; Coquet, P.; Li, H.; Tan, C.S.; Tay, B.K. Development of a CMOS-Compatible Carbon Nanotube Array Transfer Method. *Micromachines* **2021**, *12*, 95. https:// doi.org/10.3390/mi12010095

Received: 29 December 2020 Accepted: 16 January 2021 Published: 18 January 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). limit the quality of CNT growth. For example, a catalyst layer located deep inside a highaspect ratio via can be starved off the required carbon precursors for proper CNT growth. Lastly, in a CVD process, vertically-aligned CNTs (VACNTs) can only be deposited on a selected choice of substrates, typically SiO<sub>2</sub>/Si wafers or copper substrates that can allow for a high density of iron oxide clusters as nucleation sites for the growth of CNTs [12]. The chosen substrates must be stable to prevent the interaction and poisoning of the catalyst layer during CNT growth.

In this article, a method for the transfer of VACNTs is achieved by utilizing a solderbonding technique through flip-chip bonding. VACNT-based devices fabricated using the transfer method have the advantage of improved physical and electrical contact at CMOS-compatible temperatures without the need for complex pre-treatment of the target substrates. As the target substrate is excused from the CNT growth process, it does not undergo high fabrication temperatures and is not exposed to the a–c deposits that may compromise its reliability. This paper details the transfer method of VACNT arrays to target device substrates, followed by a discussion of the results and possible areas that can further improve the yield and quality of the VACNT transfer method.

## 2. Materials and Methods

## 2.1. Preparation of Carbon Nanotube on Donor Substrate

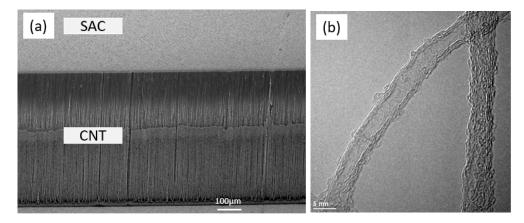

The catalyst layer for CNT growth was first prepared on a donor silicon substrate by depositing a 10 nm aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) as the diffusion barrier layer, followed by a 1 nm iron (Fe) catalyst layer by a physical vapor deposition (PVD) system. The Al<sub>2</sub>O<sub>3</sub>/Fe catalytic substrates were then placed into a commercial CNT growth system where acetylene is used as the carbon precursor at a growth temperature of 675 °C. CNT growth height was controlled by varying the growth time. After growth, the donor substrates were cooled down to room temperature before unloading. Transmission electron microscopy (TEM) characterization on the as-grown CNTs show multi-walled CNTs with an average diameter of 5 nm and an average number of five walls. Next, a layer of 35 nm titanium (Ti) followed by 1  $\mu$ m of tin-silver-copper alloy (SAC) was deposited using PVD with a patterned hard mask onto the as-grown CNTs to act as the binding material, where Ti serves as an adhesion layer between the CNTs and the SAC layer. As shown in Figure 1a, the deposited metal layers do not affect the vertical alignment of CNT.

**Figure 1.** (a) Silver-copper alloy (SAC) deposited on vertically-aligned carbon nanotube (VACNT) does not affect the alignment of the array; (b) Transmission electron microscopy (TEM) image of as-grown CNT.

#### 2.2. Preparation of Target Substrate

In order to bond the SAC-deposited CNTs to another substrate, a target substrate was prepared using ultra-violet (UV) photolithography to pattern the substrate before coating a  $35 \text{ nm Ti}/1 \mu \text{m}$  gold (Au) layer to define the desired regions of transfer. This metallization was chosen as it is a common material for electrodes whilst being resistant to oxidation at

the process temperatures (<300 °C). The target substrate used is a polished Si wafer with a smooth surface (average roughness < 5 nm).

#### 2.3. Transfer of Carbon Nanotubes

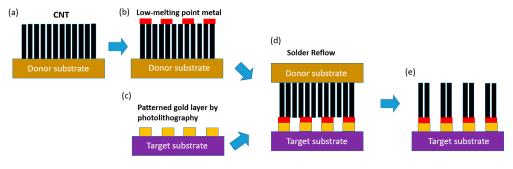

To transfer CNTs from the donor substrate to the target substrate, the CNTs need to be bonded to the target substrate. This is possible by placing the SAC-coated CNTs and Au-coated surface in contact before performing a solder reflow step as described in [13] at temperatures below 250 °C. The solder reflow process includes the steps: pre-heat; soaking; reflow; and cooling at designated temperatures. Each step needs to be carefully executed due to their impact on the wetting properties and microstructure of the solder, affecting the bonding quality. The solder reflow step is performed in the presence of an applied external load to ensure a good contact between CNTs and target substrate without air gaps. The transfer of CNTs onto their designated areas can be achieved with precision by using a flip-chip bonder. Finally, a separation process removes the donor and target substrate in opposite directions with a separation tool. A schematic of the CNT transfer method is prepared and shown in Figure 2.

**Figure 2.** Schematic of CNT transfer method: (**a**) vertically-aligned CNT growth; (**b**) evaporation of low-melting point metal such as solder through hard mask onto CNT array; (**c**) preparation of target substrate; (**d**) solder reflow process to bond the CNT array and target substrate; (**e**) separation of CNT array from donor substrate.

### 3. Results and Discussion

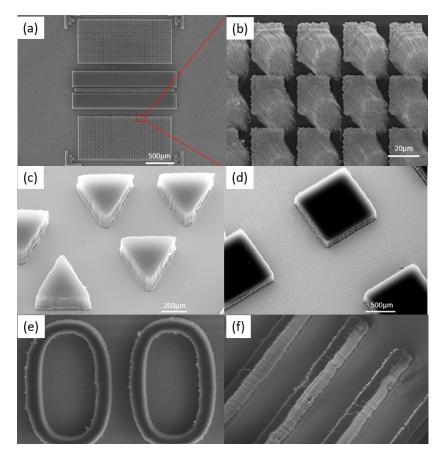

CNTs were bonded to an as-prepared target substrate by using a flip-chip bonder. A high precision and conformability can be achieved with the transfer onto the designated areas on the target substrates, as shown in Figure 3. In Figure 3a,b, the size of the transferred bumps is 25  $\mu$ m with a pitch of 10  $\mu$ m between surrounding bumps. Figure 3c-f show multiple shapes with sharp or rounded edges transferred with no change in the vertical alignment of CNTs. Since the target substrate is not exposed to CNT growth, it remains free of a-c deposits and continue to be so after the transfer process. No residue of SAC is visible on the target substrate, indicating a clean and controllable process.

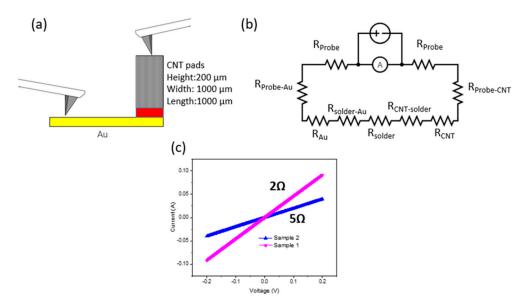

To characterize the electrical properties of the transferred CNTs, a current-voltage (IV) measurement was done on a 1 mm<sup>2</sup> transferred CNT pad with a transferred height of 200  $\mu$ m, to obtain the through-plane resistance of transferred CNTs. The measurement schematic with the structure is illustrated in Figure 4a. A voltage was applied between the two probes to measure the current that passed through the transferred CNT array, the CNT structure, followed by the Au-SAC interface and the gold electrode before terminating at the second probe.

**Figure 3.** (**a**,**b**) Transferred CNT with bump size of 25  $\mu$ m and a pitch of 10  $\mu$ m with surrounding bumps; (**c**–**f**) multiple shapes of transferred CNT—for (**e**,**f**) the width of the CNTs patterns are 200  $\mu$ m and the height of the CNT 500  $\mu$ m.

**Figure 4.** (a) Measurement setup to measure IV-response of transferred CNT array at given CNT dimension; (b) schematic of electrical connection in measurement setup; (c) measured IV-responses and corresponding resistances.

IV-responses on two CNT pads with a voltage sweep from -0.2 to 0.2 V gives a linear relationship. This shows the ohmic relationship of the bonding interface. A breakdown on every possible element contributing to resistance has been presented in Figure 4b. As

shown in Figure 4c, the calculated resistance ranges from 2 to 5  $\Omega$ . The resistances are still larger than pure metallic contacts and show room for improvement. Specifically, resistance in the contact can be improved by changing the binding material to one with a lower resistivity like the Sn-Au solder. If the Sn-Au solder is used, it has the benefit of a flux-less solder reflow process [14]. As the flux used in conventional solder reflow penetrates the CNT array when melted, causing densification and shape distortion. Another possible way to achieve a good electrical contact is by using the thermocompression bonding method. It has the advantage of reducing the material variety at the bonding interface. Thermocompression using an Au-Au interface [15] as the bonding interface between CNTs and the target substrate is achieved and intended to be used in thermal interface material (TIM) applications.

To improve conductivity of CNTs, the CNT array can also be treated with plasma prior to the deposition of the binding material to remove the closed caps of the CNTs, enabling the inner walls to contact the binding material [16] as well as improve the wettability of the CNTs to it [17]. The number of channels for electron conduction can be increased in this way and hence, the overall electrical conductivity of the transferred CNT array can be improved [18,19] to a limit of multichannel ballistic transport as referenced from a multitude of prior research. The measured conductance of multichannel ballistic transport is much greater than  $2G_0$ ; its relation is shown in Equation (1). Where  $G_0$  is the total conductance when the length of a conductor is smaller than the electron mean free path and the electron transport is ballistic, *e* is the free electron charge and h is plank's constant:

$$G_0 = \frac{2e^2}{h}.$$

(1)

By using the VACNT transfer method described above, the resultant joint between transferred CNTs and target substrate is CNT-Ti-SAC-Au. In comparison to a similar work by Liu et al. [20] that reported a CNT-Ti-Au-indium-Au contact, a reduction of one layer of binding material was achieved due to the higher hardness of SAC; the requirement of an additional Ti/Au reinforcement layer in the indium process is eliminated, whilst maintaining the transfer yield. The reduction in the number of metal junctions helps to decrease process varieties without negatively affecting the contact resistance. The use of SAC as the binding material also makes the transfer method a CMOS-compatible process as the reflow step is performed below 250 °C.

# 4. Conclusions

A CNT transfer method has been developed and shown to produce an ohmic electrical contact with a deposited gold layer, achieving a calculated resistance of <10  $\Omega$ . Furthermore, the transfer method separates the target substrate from CNT growth and hence, no a–c deposits can be found on the substrate. Using the transfer process as an example, a few pointers have been uncovered to improve the quality of transfer as well as the quality of the CNT structure, e.g., use of a binding material with lower resistances and plasma-treatment of the CNT arrays. By using the transfer method described above, the resultant joint is CNT-Ti-SAC-Au, which has lesser interfacial layers of binding material than reported in [20]. Since the SAC reflow step is performed below 250 °C, the transfer method developed using SAC is CMOS-compatible. Improvements in the CNT transfer technique will uncover opportunities in the commercial applications of CNTs, such as interconnects [4], thermal management [5], field-emission [6], and on-board electromagnetic shielding [7].

#### 5. Patent

The work described above is patented [21].

Author Contributions: Conceptualization, C.F.S., L.Y.X.L., and S.C.K.G.; methodology, J.W., C.F.S., and L.Y.X.L.; validation, C.W.T.; formal analysis, C.F.S.; investigation, C.F.S.; resources, L.H., H.L., and C.S.T.; writing—original draft preparation, C.F.S.; writing—review and editing, L.Y.X.L.; supervision,

P.C. and B.K.T.; project administration, J.W.; funding acquisition, C.W.T. All authors have read and agreed to the published version of the manuscript.

**Funding:** Please add: This research was funded by Singapore MOE Tier 2, MOE2018-T2-2-105 and Excelitas Technologies Singapore (EDB-IPP).

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Salvetat, J.-P.; Bonard, J.-M.; Thomson, N.; Kulik, A.; Forró, L.; Benoit, W.; Zuppiroli, L. Mechanical properties of carbon nanotubes. *Appl. Phys. A* **1999**, *69*, 255–260. [CrossRef]

- Ebbesen, T.W.; Lezec, H.J.; Hiura, H.; Bennett, J.W.; Ghaemi, H.F.; Thio, T. Electrical conductivity of individual carbon nanotubes. Nat. Cell Biol. 1996, 382, 54–56. [CrossRef]

- 3. Fujii, M.; Zhang, X.; Xie, H.; Ago, H.; Takahashi, K.; Ikuta, T.; Abe, H.; Shimizu, T. Measuring the Thermal Conductivity of a Single Carbon Nanotube. *Phys. Rev. Lett.* **2005**, *95*, 065502. [CrossRef] [PubMed]

- Soga, I.; Kondo, D.; Yamaguchi, Y.; Iwai, T.; Mizukoshi, M.; Awano, Y.; Yube, K.; Fujii, T. Carbon nanotube bumps for LSI interconnect. In Proceedings of the 2008 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008.

- 5. Peacock, M.A.; Roy, C.K.; Hamilton, M.C.; Johnson, W.; Knight, R.W.; Harris, D.K. Characterization of transferred vertically aligned carbon nanotubes arrays as thermal interface materials. *Int. J. Heat Mass Transf.* **2016**, *97*, 94–100. [CrossRef]

- 6. Zhao, N.; Chen, J.; Qu, K.; Khan, Q.; Lei, W.; Zhang, X. Stable electron field emission from carbon nanotubes emitter trans-ferred on graphene films. *Phys. E Low-Dimens. Syst. Nanostruct.* **2015**, *72*, 84–88. [CrossRef]

- Tan, D.; Yu, J.J.; Hee, D.; Lim, H.S.; Baillargeat, D.; Eudeline, P.; Tay, B.K. Improved RF Isolation Using Carbon Nanotube Fence-Wall for 3-D Integrated Circuits and Packaging. *IEEE Microw. Wirel. Compon. Lett.* 2015, 25, 355–357. [CrossRef]

- 8. Liu, J.; Jiang, D.; Fu, Y.; Wang, T. Carbon nanotubes for electronics manufacturing and packaging: From growth to integration. *Adv. Manuf.* **2013**, *1*, 13–27. [CrossRef]

- 9. Arcos, T.D.L.; Garnier, M.G.; Oelhafen, P.; Mathys, D.; Seo, J.W.; Domingo, C.; García-Ramos, J.V.; Sanchez-Cortes, S. Strong influence of buffer layer type on carbon nanotube characteristics. *Carbon* 2004, 42, 187–190. [CrossRef]

- Rinaldi, A.; Frank, B.; Su, D.S.; Hamid, S.B.A.; Schlögl, R. Facile Removal of Amorphous Carbon from Carbon Nano-tubes by Sonication. *Chem. Mater.* 2011, 23, 926–928. [CrossRef]

- Zhu, Y.; Tan, C.W.; Chua, S.L.; Lim, Y.D.; Tay, B.K.; Tan, C.S. Growth and fabrication of carbon-based three-dimensional heterostructure in through-silicon vias (TSVs) for 3D interconnects. In Proceedings of the 2017 IEEE 19th Electronics Packaging Technology Conference (EPTC), Singapore, 6–9 December 2017.

- 12. Mauron, P.; Emmenegger, C.; Züttel, A.; Nützenadel, C.; Sudan, P.; Schlapbach, L. Synthesis of oriented nanotube films by chemical vapor deposition. *Carbon* 2002, *40*, 1339–1344. [CrossRef]

- Siah, C.F.; Wang, J.; Roux-Levy, P.; Coquet, P.; Tay, B.K.; Baillargeat, D. Carbon Nanotube for Interconnects and Nano-Packaging Application. In Proceedings of the 2019 IEEE 21st Electronics Packaging Technology Conference (EPTC), Singapore, 4–6 December 2019.

- Yoon, J.W.; Chun, H.S.; Koo, J.M.; Jung, S.B. Au-Sn flip-chip solder bump for microelectronic and optoelectronic appli-cations. *Microsyst. Technol.* 2007, 13, 1463–1469. [CrossRef]

- 15. Cross, R.; Cola, B.A.; Fisher, T.; Xu, X.; Gall, K.; Graham, S. A metallization and bonding approach for high performance carbon nanotube thermal interface materials. *Nanotechnology* **2010**, *21*, 445705. [CrossRef] [PubMed]

- 16. Huang, S.; Dai, L. Plasma Etching for Purification and Controlled Opening of Aligned Carbon Nanotubes. *J. Phys. Chem. B* 2002, 106, 3543–3545. [CrossRef]

- 17. Li, P.; Lim, X.; Zhu, Y.; Yu, T.; Ong, C.-K.; Shen, Z.; Wee, A.T.S.; Sow, C.H. Tailoring Wettability Change on Aligned and Patterned Carbon Nanotube Films for Selective Assembly. *J. Phys. Chem. B* 2007, *111*, 1672–1678. [CrossRef] [PubMed]

- Li, H.J.; Lu, W.G.; Li, J.; Bai, X.D.; Gu, C. Multichannel Ballistic Transport in Multiwall Carbon Nanotubes. *Phys. Rev. Lett.* 2005, 95, 086601. [CrossRef] [PubMed]

- Zhu, L.; Hess, D.W.; Wong, C. In-Situ Opening Aligned Carbon Nanotube Films/Arrays for Multichannel Ballistic Transport in Electrical Interconnect. In Proceedings of the 56th Electronic Components and Technology Conference 2006, San Diego, CA, USA, 30 May–2 June 2006.

- Fu, Y.; Qin, Y.; Wang, T.; Chen, S.; Liu, J. Ultrafast Transfer of Metal-Enhanced Carbon Nanotubes at Low Temperature for Large-Scale Electronics Assembly. *Adv. Mater.* 2010, 22, 5039–5042. [CrossRef] [PubMed]

- 21. Wang, J.; Coquet, P.; Tay, B.K. Nanostructure Transfer Method. Singapore Patent 10201807403V, 29 August 2018.