## GaN-on-silicon transistors with reduced current collapse and improved blocking voltage by means of local substrate removal

Idriss Abid, Eleonora Canato, Matteo Meneghini, Gaudenzio Meneghesso, Kai Cheng, F Medjdoub

## ► To cite this version:

Idriss Abid, Eleonora Canato, Matteo Meneghini, Gaudenzio Meneghesso, Kai Cheng, et al.. GaN-on-silicon transistors with reduced current collapse and improved blocking voltage by means of local substrate removal. Applied Physics Express, 2021, 14 (3), pp.036501. 10.35848/1882-0786/abdca0. hal-03113165

## HAL Id: hal-03113165 https://hal.science/hal-03113165

Submitted on 24 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

https://doi.org/10.35848/1882-0786/abdca0

LETTER

## GaN-on-silicon transistors with reduced current collapse and improved blocking voltage by means of local substrate removal

Idriss Abid<sup>1\*</sup>, Eleonora Canato<sup>2</sup>, Matteo Meneghini<sup>2</sup>, Gaudenzio Meneghesso<sup>2</sup>, Kai Cheng<sup>3</sup>, and Farid Medjdoub<sup>1\*</sup><sup>10</sup>

<sup>1</sup>Institut d'Electronique, de Microélectronique et de Nanotechnologie, Centre National de la Recherche Scientifique (IEMN-CNRS), 59652 Villeneuve d'Ascq, France

<sup>2</sup>Department of Information Engineering, University of Padova, 35131 Padova, Italy

<sup>3</sup>Enkris Semiconductor, Inc., Suzhou, People's Republic of China

\*E-mail: idriss.abid.etu@univ-lille.fr; farid.medjdoub@iemn.fr

Received December 23, 2020; revised January 12, 2021; accepted January 14, 2021; published online January 29, 2021

We report on the demonstration of low trapping effects above 1200 V of GaN-on-silicon transistors using a local substrate removal (LSR) followed by a thick backside ultra-wide-bandgap AIN deposition. Substrate ramp measurements show reduced hysteresis up to 3000 V. It has been found that the LSR approach not only enables the extension operation voltage capabilities of GaN-on-silicon HEMTs with low on-resistance but also allow for the reduction of trapping effects directly affecting their dynamic behavior. This work points out that a large part of the electron trapping under high bias occurs at the AIN nucleation layer and Si substrate interface. © 2021 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

or future efficient and low-cost power electronics, GaN high-electron-mobility transistors (HEMTs) on silicon (Si) substrate are highly promising owing to their superior intrinsic properties such as large bandgap, high breakdown field strength and high electron saturation velocity.<sup>1-12</sup>) GaN-on-Silicon HEMTs offer the potential to revolutionize power electronics by enabling important energy savings and new flexibility for advanced power circuits.<sup>13</sup>) However, these types of devices suffer from poor critical electric field strength of the Si substrate together with a parasitic conduction at the buffer/substrate interface leading to device breakdown.<sup>14–17</sup>)

That is why, the highest reported three-terminal breakdown voltage (VBD) values for grounded GaN-on-Si HEMTs defined at an off-state leakage current of 1  $\mu$ A mm<sup>-1</sup> are still below 1.5 kV, which is basically limited by the Si substrate and material quality. Consequently, applications requiring voltage operation above 1 kV cannot currently be covered by GaN-on-Si HEMTs, although thicker buffers with high associated material quality have been developed.<sup>18–20</sup>

A solution to suppress the parasitic conduction phenomenon and thus enhance the breakdown voltage (BV) is to remove the Si substrate.<sup>21-24</sup> Indeed, the Si substrate removal around the drain electrode enabled electrical isolation of the gate and source contacts from the drain across the buffer layer/Si interface. Using this approach, GaN-on-Si based transistors with a significantly improved blocking voltage of 3000 V have been reported.<sup>25)</sup> Recently, we have demonstrated GaN-on-Si metal insulator semiconductor HEMTs (MISHEMTs) with LSR under the entire device followed by a backside deposition of the ultra-wide bandgap AlN material.<sup>26)</sup> The use of an in situ SiN gate dielectric and local substrate removal (LSR) technique combined with 15  $\mu$ m thick AlN layer enabled state-of-the-art GaN based HEMTs with remarkably low off-state leakage current  $(<1 \,\mu\text{A mm}^{-1})$  up to 3000 V. On the other hand, a key figure of merit for GaN power devices is the current collapse that hindered for instance the commercialization of 650 Vrated GaN-on-Si devices.

In this work, we assessed the DC, high voltage and dynamic characteristics of high voltage transistors with and without LSR. We demonstrate the possibility to benefit from low electron trapping effects on lateral GaN-on-Si based transistors while extending the blocking voltage capabilities as compared to transistors without LSR.

The AlGaN/GaN heterostructure has been grown by metalorganic chemical vapor deposition (MOCVD) on a 6 inch Si (111) substrate. The HEMT structure consists in a 5  $\mu$ m buffer thickness, a 310 nm undoped GaN channel followed by a 24 nm Al<sub>0.25</sub>Ga<sub>0.75</sub>N barrier layer and an 11 nm in situ Si<sub>3</sub>N<sub>4</sub> cap layer. Ohmic contacts were formed directly on top of the AlGaN barrier by alloying Ti/Al/Ni/Au stack using an 875 °C rapid thermal annealing resulting in contact resistances of  $0.3 \ \Omega$ . mm. Device isolation was performed by N<sub>2</sub> implantation. Hall measurements reveal a sheet carrier concentration of  $0.9\times 10^{13}\,\text{cm}^{-2}$  with a mobility of 2100  $\text{cm}^2\,\text{V}^{-1}\,\text{s}^{-1},$  and a sheet resistivity of 330  $\Omega/\Box$ . Metal-insulator-semiconductor (MIS) gate structure was employed by using Ni/Au metal stack inside the in situ Si<sub>3</sub>N<sub>4</sub> cap layer without any additional fieldplate. A 200 nm thick SiN film was deposited by plasma enhanced chemical vapor deposition (PECVD) as extra passivation. Once the front-side processing was completed, the Si substrate was locally etched up to the AlN nucleation layer around the entire device using a highly selective Bosch process etching. It is important to note that our mask design consists of devices with and without LSR patterns, which eliminates any processing or epi variation during the device characterization. Then, 15  $\mu$ m thick nanocolumnar crystalline AlN was deposited on the backside by physical vapor deposition (PVD) at 300 °C, which is post front-side process compatible as it complies with the thermal budget. The AlN film delivers a high breakdown field well-above 4 MV cm<sup>-1</sup> despite the low temperature deposition as checked through vertical measurements on a reference doped silicon wafer. Finally, 2  $\mu$ m of cupper is deposited on top of the PVD AlN into the backside trenches. Hall measurements remains identical after full backside processing and subsequent AIN and metal depositions.

Content from this work may be used under the terms of the Creative Commons Attribution 4.0 license. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. © 2021 The Author(s). Published on behalf of

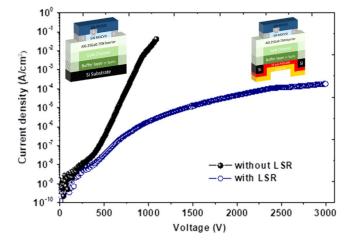

Fig. 1. (Color online) Room temperature vertical leakage characteristics of the AlGaN/GaN epitaxial structure with and without LSR.

As expected, the vertical leakage current measurements conducted on isolated patterns with LSR show a remarkable increase from 1000 V to above 3000 V (limitation of our setup) as compared to patterns without LSR (Fig. 1). This confirms the suppression of the substrate conduction phenomena and effectiveness of the AlN dielectric thick film.

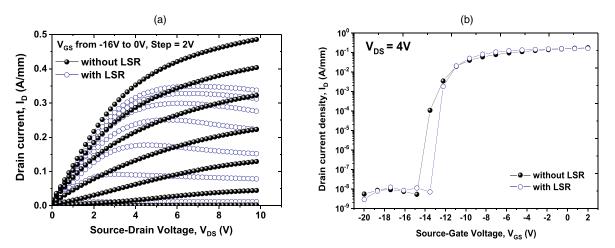

DC characterizations were carried out on devices with a gate width/length = 50  $\mu$ m/2  $\mu$ m and various gate-to-drain spacing (L<sub>GD</sub>) with and without LSR on the same wafer. Maximum current density of transistors with  $L_{GD} = 5 \ \mu m$  at  $V_{DS} = 10 \ V$ and  $V_{GS} = 0$  V decreased from 490 to 340 mA mm<sup>-1</sup> after the Si substrate removal under the active region due to self-heating [Fig. 2(a)]. It can be pointed out that a significant recovery of the maximum current density occurs after the Cu deposition, which in turn enables the reduction of self-heating.<sup>27,28)</sup> Consequently, a thicker Cu heat sink (>10  $\mu$ m) is expected to mitigate the current density reduction. Nevertheless, the extracted static specific on-resistance (R<sub>ON-STATIC</sub>) values are found to be below 10 m $\Omega$  cm<sup>-2</sup> in both cases. The corresponding transfer characteristics of AlGaN/GaN MISHEMTs with  $L_{GD}$  of 5  $\mu$ m are shown in Fig. 2(b). Despite a slight shift of the threshold voltage, it appears that the off-state leakage currents with and without LSR are similar and well-below  $0.1 \,\mu \text{A mm}^{-1}$  at low drain bias.

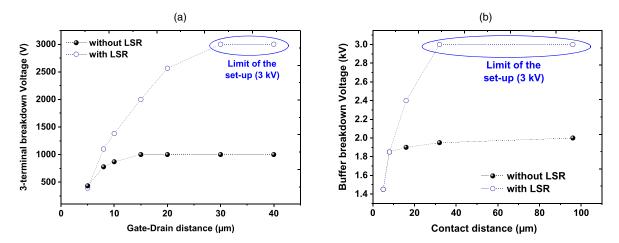

The three-terminal off-state leakage characteristics of the AlGaN/GaN MISHEMTs are plotted as a function of L<sub>GD</sub> in Fig. 3(a). The devices without LSR show a BV plateau around 1000 V due to the buffer thickness limitation. For devices with LSR, the BV as a function of the gate-drain distance increases almost linearly reaching more than 3000 V for large designs ( $L_{GD} > 30 \,\mu$ m). In the same way, lateral buffer BV conducted on isolated patterns as a function of contact distances with and without LSR show a strong improvement from 1900 V to well above 3000 V [Fig. 3(b)] with a reduction of the leakage current, confirming the suppression of the substrate conductive path contribution.

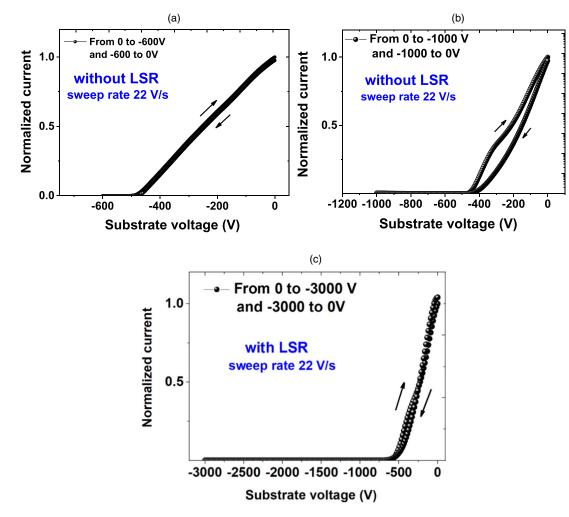

The substrate bias ramp technique has been shown to be very efficient in order to highlight the trapping effects and related current collapse in GaN-on-Si power switching transistors.<sup>29,30)</sup> As a matter of fact, in properly passivated structures, buffer charge storage is the main source of dynamic on-resistance.<sup>31)</sup> Substrate bias measurements have been performed on a Keysight B1505A Power Device Analyzer. Two ohmic contacts with a spacing of  $20 \,\mu m$ have been used and the bias is set at 1 V. By ramping the substrate to a high (negative) potential, mimicking the offstate operation under the drain contact in a transistor, any charge redistribution in the buffer upon reverse bias will change the electric field. As such, the buffer charge trapping or storage will be visible in the substrate ramp characteristic. This approach is surface insensitive and applies a 1-D vertical field. The sweep rate was set to  $22 \text{ V s}^{-1}$ . The devices without LSR reveals low hysteresis in the substrate ramps performed up to 600 V [see Fig. 4(a)]. This reflects the excellent material quality and the low charge storage within the heterostructure. Trapping effects are observed above 600 V as seen Fig. 4(b) through 1 kV substrate ramp measurements. Interestingly, the devices with LSR show low hysteresis and thus reduced charge storage all the way to 3000 V [Fig. 4(c)]. This means that the substrate removal followed by the additional thick AlN deposition not only preserve the integrity of a low charge trapping buffer but could also extend significantly the trap-free bias operation capability.

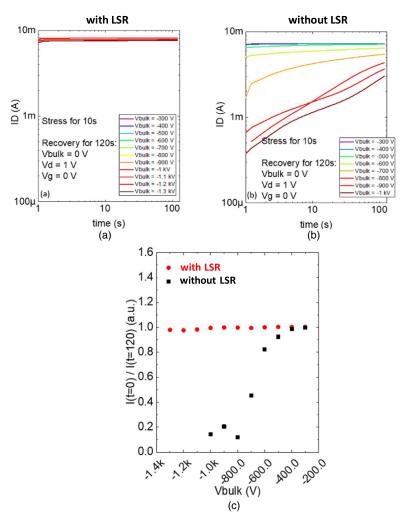

In order to verify these observations and further assess the trapping effects of transistors with and without LSR, we performed back-gating current transient measurements at room temperature on both samples. This technique allows to separate buffer charge trapping effects from surface ones. The measurement procedure is divided into stress and

Fig. 2. (Color online) (a)  $I_D - V_{DS}$  and (b) DC transfer characteristics of AlGaN/GaN MISHEMTs ( $L_{GD} = 5 \mu m$ ) with and without LSR characteristics. © 2021 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

036501-2

Fig. 3. (Color online) (a) Evolution of  $L_{GD}$ -dependent three-terminal breakdown voltage and (b) buffer breakdown versus contact distances of AlGaN/GaN MISHEMTs with and without LSR.

Fig. 4. (Color online) Substrate ramps performed on TLM for the AlGaN/GaN epitaxial structure (a) at 1000 V without LSR and (b) at 3000 V with LSR.

recovery phases. For the stress phase, the device is kept in trapping conditions for 10 s, during which a high electric field is induced on the buffer, as a result charge trapping occurs mainly in this region. Then, the recovery phase is immediately carried out by keeping the device in rest conditions. The recovery drain current transient is recorded for 120 s. Several bulk bias stresses are tested, from -200 V up to -1.3 kV. During the stress the drain, gate and source terminals are kept at 0 V, whereas during the recovery the drain terminal is at

1 V, the source at 0 V and the gate is at 0 V. The plots of the drain current transients as a function of time for the different bulk bias stress are reported in Figs. 5(a) and 5(b). In agreement with the substrate ramp characterizations, the back-gating measurements show no trapping effects all the way to 1.3 kV for devices with LSR with a monotonic behavior over time regardless of the back bias. On the other hand, the same devices without LSR under similar conditions deliver significant trapping above 600 V. Figure 5(c) © 2021 The Author(s). Published on behalf of

The Japan Society of Applied Physics by IOP Publishing Ltd

Fig. 5. (Color online) Back-gating current transient measurements with various trapping voltages and normalized current after stress as a function of the back bias of AlGaN/GaN MISHEMTs with and without LSR.

summarizes the back-gating transient measurements of devices with and without LSR by showing the normalized current after stress (initial current after stress over current after 120 s recovery) as a function of the back bias. The remarkable monotonic evolution of the current after stress for devices with LSR while observing a drastic drop for devices without LSR within the same wafer show that under high bias most of the electron trapping occurs at the AlN nucleation layer/silicon substrate vicinity.

In conclusion, current collapse characteristics of GaN-based MISHEMTs with and without LSR followed by thick PVD AIN and Cu deposition were investigated on the same wafer. Trapping effects directly affecting the dynamic behavior of power switching transistors have been studied by means of high voltage substrate ramps as well as back-gating current transient measurements. This work demonstrates that the substrate removal approach not only enables the drastic extension of operation voltage capabilities of GaN-on-Silicon HEMTs but also potentially enables a drastic trapping reduction. This key additional benefit provided by the LSR approach is attributed to the removal of the interface between the AlN nucleation layer and the silicon substrate. Further removal of the full AIN nucleation layer and eventually part of the transition layers may allow GaN devices with current collapse-free operating wellbeyond 1 kV. These results show that power applications above 1000 V covered currently by SiC and silicon-based devices could benefit from the high electron mobility offered by GaNon-silicon heterostructures enabling much lower R<sub>ON</sub>.

**Acknowledgments** This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 720527 (Inrel-NPower). This work is supported by the French RENATECH network and the French National grant ANR-17-CE05-00131 within the project called BREAKUP. The authors would also like to gratefully acknowledge the company Kyma for the thick PVD AlN deposition.

ORCID iDs Farid Medjdoub (b) https://orcid.org/0000-0002-4753-4718

- 1) B. J. Baliga, Semicond. Sci. Technol. 28, 074011 (2013).

- R. Kabouche, I. Abid, R. Püsche, J. Derluyn, S. Degroote, M. Germain, A. Tajalli, M. Meneghini, G. Meneghesso, and F. Medjdoub, Phys. Status Solidi 217, 1900687 (2019).

- 3) U. K. Mishra, P. Parikh, and Y. F. Wu, Proc. IEEE 90, 1022 (2002).

- 4) A. Tajalli et al., Materials 13, 194271 (2020).

- F. Medjdoub, M. Zegaoui, B. Grimbert, N. Rolland, and P. A. Rolland, Appl. Phys. Express 4, 124101 (2011).

- 6) B. Zou, H. Liang, and K. M. Lau, Phys. Status Solidi C 7, 2171 (2010).

- 7) H. Morkoç, S. Strite, G. B. Gao, M. E. Lin, B. Sverdlov, and M. Burns, J. Appl. Phys. 76, 1363 (1994).

- 8) D. Christy, A. Watanabe, and T. Egawa, AIP Adv. 4, 107104 (2014).

- Y. Dora, A. Chakraborty, L. Mccarthy, S. Keller, S. P. Denbaars, and U. K. Mishra. IEEE Electron Device Lett. 27, 713 (2006).

- 10) S. L. Selvaraj, A. Watanabe, A. Wakejima, and T. Egawa, IEEE Electron Device Lett. 33, 1375 (2012).

- 11) F. Medjdoub, J. Derluyn, K. Cheng, M. Leys, S. Degroote, D. Marcon, D. Visalli, M. Van Hove, M. Germain, and G. Borghs, IEEE Electron Device Lett. **31**, 111 (2010).

© 2021 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

- 12) J. Ma and E. Matioli, IEEE Electron Device Lett. 38, 367 (2017).

- 13) M. Meneghini, G. Meneghesso, and E. Zanoni, *Power GaN Devices Materials, Applications and Reliability* (Springer, Berlin, 2017).

14) D. Visalli et al., ECS Trans. 41, 101 (2011).

- H. Chandrasekar, K. N. Bhat, M. Rangarajan, S. Raghavan, and N. Bhat, Sci. Rep. 7, 15749 (2017).

- 16) D. Visalli et al., Appl. Phys. Express 4, 094101 (2011).

- 17) S. Arulkumaran, T. Egawa, S. Matsui, and H. Ishikawa, Appl. Phys. Lett. 86, 123503 (2005).

- 18) N. Ikeda, S. Kaya, J. Li, T. Kokawa, M. Masuda, and S. Katoh, 2009 21st Int. Symp. on Power Semiconductor Devices & IC's, 2009, p. 251.

- 19) S. L. Selvaraj, T. Suzue, and T. Egawa, IEEE Electron Device Lett. 30, 587 (2009).

- 20) D. Christy, T. Egawa, Y. Yano, H. Tokunaga, H. Shimamura, Y. Yamaoka, A. Ubukata, T. Tabuchi, and K. Matsumoto, Appl. Phys. Express 6, 026501 (2013).

- 21) P. Srivastava et al., IEEE Electron Device Lett. 32, 30 (2011).

- 22) N. Herbecq, I. Roch-Jeune, N. Rolland, D. Visalli, J. Derluyn, S. Degroote, M. Germain, and F. Medjdoub, Appl. Phys. Express 7, 034103 (2014).

- 23) P. Srivastava et al., 2011 Int. Electron Devices Meeting, 2011, p. 1961.

- 24) D. Visalli, M. Van Hove, P. Srivastava, J. Derluyn, J. Das, M. Leys, S. Degroote, K. Cheng, M. Germain, and G. Borghs, Appl. Phys. Lett. 97, 113501 (2010).

- 25) N. Herbecq, I. Roch-Jeune, A. Linge, B. Grimbert, M. Zegaoui, and F. Medjdoub, Electron. Lett 51, 1532 (2015).

- 26) E. Dogmus, M. Zegaoui, and F. Medjdoub, Appl. Phys. Express 11, 034102 (2018).

- 27) G. Pavlidis, D. Mele, T. Cheng, F. Medjdoub, and S. Graham, 2016 15th IEEE Intersociety Conf. on Thermal and Thermomechanical Phenomena in Electronic Systems, 2016, p. 1255.

- 28) G. Pavlidis, S. H. Kim, I. Abid, M. Zegaoui, F. Medjdoub, and S. Graham, IEEE Electron Device Lett. 40, 1060 (2019).

- 29) A. Stockman, M. Uren, A. Tajalli, M. Meneghini, B. Bakeroot, and P. Moens, 2017 47th European Solid-State Device Research Conf., 2017, p. 130.

- 30) H. Chandrasekar, M. J. Uren, A. Eblabla, H. Hirshy, M. A. Casbon, P. J. Tasker, K. Elgaid, and M. Kuball, IEEE Electron Device Lett. 39, 1558 (2018).

- M. Meneghini, A. Tajalli, P. Moens, A. Banerjee, E. Zanoni, and G. Meneghesso, Mater. Sci. Semicond. Process. 78, 118 (2018).