# **PALS:** Plesiochronous and Locally Synchronous Systems

Johannes Bund, Matthias Függer, Christoph Lenzen, Moti Medina, Will

Rosenbaum

## ▶ To cite this version:

Johannes Bund, Matthias Függer, Christoph Lenzen, Moti Medina, Will Rosenbaum. PALS: Plesiochronous and Locally Synchronous Systems. ASYNC 2020 - 26th IEEE International Symposium on Asynchronous Circuits and Systems, May 2020, Salt Lake City, United States. pp.36-43, 10.1109/ASYNC49171.2020.00013. hal-03070326

## HAL Id: hal-03070326 https://hal.science/hal-03070326v1

Submitted on 10 Feb 2025  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## PALS: Plesiochronous and Locally Synchronous Systems

Johannes Bund<sup>\*†</sup>, Matthias Függer<sup>‡</sup>, Christoph Lenzen<sup>\*</sup>, Moti Medina<sup>§</sup> and Will Rosenbaum<sup>\*</sup>

\*MPI for Informatics, Saarland Informatics Campus {jbund, clenzen, wrosenba}@mpi-inf.mpg.de

<sup>†</sup>Saarbrücken Graduate School of Computer Science

<sup>‡</sup>CNRS & LSV, ENS Paris-Saclay, Université Paris-Saclay & Inria

mfuegger@lsv.fr

<sup>‡</sup>Ben-Gurion University of the Negev

medinamo@bgu.ac.il

Abstract—Consider an arbitrary network of communicating modules on a chip, each requiring a local signal telling it when to execute a computational step. There are three common solutions to generating such a local clock signal: (i) by deriving it from a single, central clock source, (ii) by local, free-running oscillators, or (iii) by handshaking between neighboring modules.

Conceptually, each of these solutions is the result of a perceived dichotomy in which (sub)systems are either clocked or fully asynchronous, suggesting that the designer's choice is limited to deciding where to draw the line between synchronous and asynchronous design.

In contrast, we take the view that the better question to ask is *how* synchronous the system can and should be. Based on a distributed clock synchronization algorithm, we present a novel design providing modules with local clocks whose frequency bounds are almost as good as those of corresponding free-running oscillators, yet neighboring modules are guaranteed to have a phase offset substantially smaller than one clock cycle. Concretely, parameters obtained from a 15 nm ASIC implementation running at 2 GHz yield mathematical worst-case bounds of 30 ps on phase offset for a  $32 \times 32$  node grid network.

Index Terms-gradient clock synchronization, clocking, GALS

#### I. INTRODUCTION AND RELATED WORK

At surface level, the synchronous and asynchronous design paradigms seem to be opposing extremes. In their most pure forms, this is true: Early synchronous systems would wait for a clock signal to be propagated throughout the system and all computations of the current clock cycle to complete before moving on to the next; and delay-insensitive circuits make no assumptions on timing whatsoever, explicitly acknowleding completion of any computational step.

In reality, however, fully synchronous or asynchronous systems are the exception. It has long since become impractical to wait for the clock to propagate across a chip, and there are numerous clock domains and asynchronous interfaces in any offthe-shelf "synchronously" clocked computer [1]. On the other hand, delay-insensitive circuits [2] suffer from substantial computational limitations [3], [4], [5] and provide no timing guarantees, rendering them unsuitable for many applications – in particular the construction of a general-purpose computer. Accordingly, most real-world "asynchronous" systems will utilize timing assumptions on some components, which in fact could be used to construct a (possibly very primitive) clock.

As systems grow in size – physically or due to further miniaturization - maintaining the illusion of perfect synchronism becomes increasingly challenging. Due to various scalability issues, more and more compromises are made. A well-known such compromise gaining in popularity in recent years are Globally Asynchronous Locally Synchronous (GALS) systems [6], [7]. Here, several clock domains are independently clocked and communicate asynchronously via handshakes, where synchronizers are used to ensure sufficiently reliable clock domain crossing [7], [8]. While this approach resolves important scalability issues, arguably it does so by surrendering to them: between clock domains, all interaction is asynchronous. However, fixing a sufficiently small probability of synchronizer failure, communication latency becomes bounded, permitting bounded response times to internal and external events. Yet, as timing relations between different clock domains remain desirable. GALS systems with guaranteed frequency relations between clock domains (but without any bound on their phase offsets), so-called mesochronous architectures, have been conceived [7].

One might think that GALS systems exemplify a fundamental struggle between the synchronous and asynchronous paradigms. We argue that this dichotomy is false! Rather, choices between clocked and clockless designs are driven by tradeoffs between guarantees on response times, cost (in terms of energy, buffer size, area, etc.), and complexity of development. Ideally, we would like to provide the convenient synchronous abstraction to the developer, yet have the system respond quickly to external and internal events. Unfortunately, existing approaches behave less than ideal in this regard:

- Centralized clocking does not scale. In large systems, the resulting timing guarantees become too loose (requiring to make the system slow). Indeed, it has been shown that the achievable *local skew*, i.e., maximum phase offset between neighbors, in a grid *grows linearly* with the width of the grid; see Section V-B.

- A system-wide asynchronous design results in challenging development, especially when tight timing constraints are to be met. While in a clocked system one can bound response times by bounding the number of clock cycles for computation and communication, analyzing the (worst-

case) response time of a large-scale asynchronous system has to be performed bottom-up. In addition, without highly constraining design rules, it is difficult to ensure that waiting for acknowledgements does not delay the response to a highpriority local event or an external request for a significant time. Causal acknowledge chains can span the entire system, potentially resulting in *waiting times* that *grow linearly* with the system diameter.

- A GALS design ostensibly does not suffer from these issues, as each clock domain can progress on its own due to independent clocks.<sup>1</sup> However, clock domain crossings require synchronizers, incurring 2 or more clock cycles of additional latency. If synchronizers are placed in the data path, communication becomes slow, even if a simple command is to be spread across the chip or information is acquired from an adjacent clock domain.

- Alternative solutions that do not require synchronizers in the data path have been proposed in [11], [12]. The designs either skip clock cycles or switch to a clock signal shifted by half a period, when transmitter and receiver clock risk to violate setup/hold conditions. The indicating signal is synchronized without additional latency to the datapath. Depending on the implementation and intended guarantees, the additional latency is in the order of a clock period. While this can, in principle, be brought down to the order of setup/hold-windows, such designs would require considerable logical overhead and fine-tuning of delays. Further, note that an application of such a scheme has to periodically insert no-data packets. An application-level transmission may be delayed by such a timeslot. In [11] this additional delay can be up to two periods when the no-data packet is oversampled. Finally, note that a potential application that runs on top of this scheme and uses handshaking to make sure all its packets of a (logical) time step have arrived before the next time step is locally initiated faces the same problem as a fully asynchronous design, i.e., that the worstcase waiting time between consecutive time steps grows linearly with the system diameter.

*Our Contribution:* In this work, we present a radically different approach. By using a distributed clock synchronization algorithm, we essentially create a single, system-wide clock domain without needing to spread a clock signal from a single dedicated source with small skew. We employ results on *gradient clock synchronization (GCS)* by Lenzen et al. [13], in which the goal is to minimize the worst-case clock skew between adjacent nodes in a network. In our setting, the modules correspond to nodes, and they are connected by an edge if they directly communicate (i.e., exchange data). Thus, nodes of the clock synchronization algorithm communicate only if the respective nodes exchange data for computational functionality. This leads to an easy integration of our algorithm into the existing communication infrastructure.

The algorithm provides strong parametrized guarantees.

Consider a network of local clocks that are controlled by our GCS algorithm. Let D be the diameter of the network. Further, let  $\rho$  be the (unintended) drift of the local clock,  $\mu > 2\rho$  a freely chosen constant, and  $\delta$  an upper bound on how precisely the phase difference to neighbors is known. Then:

- The synchronized clocks are guaranteed to run at normalized rates between 1 and  $(1 + \mu)(1 + \rho)$ .

- The *local skew* is bounded by  $O(\delta \log_{\mu/\rho} D)$ .

- The global skew, i.e., the maximum phase offset between any two nodes in the system, is  $O(\delta D)$ .

In other words, the synchronized clocks are almost as good as free-running clocks with drift  $\rho$ , yet the local skew grows only logarithmically in the chip's diameter. The local and global skew bounds are optimal up to roughly factor 2 [13].

As a novel theoretical result, we improve the global skew bound by roughly factor 2 compared to [14]. This improvement brings our theoretical worst-case skew to within a factor of roughly 2 of the theoretical optimum (which is only known to be achieved by a significantly more complicated mechanism [13]). As a second theoretical contribution, we prove that a minor modification of the algorithm reduces the obtained local skew bound by an additive  $2\delta$ .

We can control the base of the logarithm in the local skew bound by choosing  $\mu$ . Picking, e.g.,  $\mu = 100\rho$  means that  $\log_{\mu/\rho} D \leq 1$  for any  $D \leq 100$ . Of course, the constants hidden in the *O*-notation matter, but they are reasonably small. Concretely, for a grid network of  $32 \times 32$  nodes in the 15 nm FinFET-based Nangate OCL [15], 2 GHz clock sources with an assumed drift of  $\rho = 10^{-5}$ , and  $\mu = 10^{-3}$ , our simple sample implementation guarantees that  $\delta \leq 5$  ps in the worst case. The resulting local skew is 30 ps, well below a clock cycle. We stress that this enables much faster communication than for handshake-based solutions incurring synchronizer delay.

Note that locking the local oscillators to a common stable reference does *not* require to balance the respective path delays, implying that our assumed  $\rho$  is very pessimistic. Smaller  $\rho$  (while keeping  $\mu$  fixed) increases the base of the logarithm, further improving scalability. To show that the asymptotic behavior is relevant already to current systems and with our pessimistic  $\rho$ , we compare the above results to skews obtained by clock trees in the same grid networks in Section V-B.

*Organization of this paper:* We present the GCS algorithm in Section II, stating worst-case bounds on the local and global skews proved in the appendix We then break down the algorithm into modules in Section III and discuss their implementation in Section IV. Section V presents Spice simulations for a network of four nodes, organized in a line and compares them to clock trees. We conclude in Section VI.

#### II. Algorithm

#### A. High-level Description

We give a high level description of our algorithm that achieves close synchronization between neighboring nodes in a network. We model the network as an undirected graph G = (V, E) where V is the set of nodes, and E is the

<sup>&</sup>lt;sup>1</sup>This is different for designs with pausible clocks [9], [10], rendering them even more problematic in this context.

set of edges (or links). Abstractly, we think of each node v as maintaining a *logical clock*, which we view as a function  $L_v: \mathbf{R}_{\geq 0} \to \mathbf{R}$ . That is for each (Newtonian) time  $t, L_v(t)$  is v's logical clock value at time t. The *local skew* is the maximum clock difference between neighbors:  $\mathcal{L}(t) = \max_{\{v,w\} \in E} \{|L_v(t) - L_w(t)|\}$ . The global skew is the maximum clock difference between any two nodes in the network:  $\mathcal{G}(t) = \max_{v,w \in V} \{|L_v(t) - L_w(t)|\}$ . The goal of our algorithm is for each node to compute a logical clock  $L_v(t)$  minimizing  $\mathcal{L}(t)$  at all times t, subject to the condition that all logical clocks progress at least at (normalized) rate  $1.^2$

We assume that each node v has an associated reference clock signal, which we refer to as v's hardware clock, denoted  $H_v(t)$ . For notational convenience,<sup>3</sup> we assume that the minimum (normalized) rate of  $H_v$  is 1, and its maximum rate is  $1 + \rho$ : for all  $v \in V$  and  $t, t' \in \mathbf{R}_{\geq 0}$

$$t' - t \le H_v(t') - H_v(t) \le (1 + \rho)(t' - t).$$

(1)

To compute a logical clock, after initially setting  $L_v(0) = H_v(0)$ , v adjusts the rate of  $L_v$  relative to the rate of  $H_v$  (where this rate itself is neither known to nor under the influence of the algorithm). Specifically, v can be either in slow mode or fast mode. In slow mode,  $L_v$  runs at the same rate as  $H_v$ , while in fast mode, v sets the rate of  $L_v$  to be  $1+\mu$  times the one of its hardware clock. Here,  $\mu$  is a parameter fixed by the designer. In order for the algorithm to work, a fast node must always run faster than a slow node—i.e.,  $\mu > \rho$ . We impose the stronger condition that  $\mu > 2\rho$ .

The GCS algorithm of Lenzen et al. [13] specifies conditions for a node to be in slow or fast mode that ensure asymptotically optimal local skew, provided that the global skew is bounded. The algorithm is parametrized by a variable  $\kappa \in \mathbf{R}^+$ , whose value determines the quality of synchronization.

**Definition 1.** Let  $\kappa \in \mathbf{R}^+$  be a parameter. We say that a node v satisfies the fast condition at time t if there exists a natural number  $s \in \mathbf{N}$  such that the following two conditions hold: **FC1** v has a neighbor x such that  $L_x(t) - L_v(t) \ge (2s+1)\kappa$  **FC2** all of v's neighbors y satisfy  $L_v(t) - L_y(t) \le (2s+1)\kappa$ . It satisfies the slow condition if there exists  $s \in \mathbf{N}$  such that: **SC1** v has a neighbor x such that  $L_v(t) - L_x(t) \ge 2s\kappa$ **SC2** all of v's neighbors y satisfy  $L_y(t) - L_v(t) \le 2s\kappa$ .

**Definition 2.** We say that an algorithm is a GCS algorithm with parameters  $\rho, \mu, \kappa$  if the following invariants hold, for every node  $v \in V$  and all times t, t':

I1  $\mu > \rho$ ,

**I2**  $H_v(t') - H_v(t) \le L_v(t') - L_v(t) \le (1+\mu)(H_v(t') - H_v(t))$

**I3** if v satisfies the fast condition throughout the interval [t, t'], then  $L_v(t') - L_v(t) = (1 + \mu)(H_v(t') - H_v(t))$

I4 if v satisfies the slow condition throughout the interval [t, t'], then  $L_v(t') - L_v(t) = H_v(t') - H_v(t)$ .

<sup>2</sup>Without the minimum rate requirement, the task becomes trivial: all nodes can simply set  $L_v(t) = 0$  for all times t to achieve perfect "synchronization." <sup>3</sup>It is common to assume a two-sided frequency error, i.e., a rate between  $1 - \rho$  and  $1 + \rho$ . However, the one-sided notation simplifies expressions. Translating between the two models is a straightforward renormalization. Invariants (I3) and (I4) still allow a node's clock  $L_v(t)$  to vary within the rates of the underlying hardware clock, which is assumed not be under the control of the algorithm.

**Theorem 1.** Suppose algorithm A is a GCS algorithm. Then A maintains global skew  $\mathcal{G}(t) \leq \frac{\mu \kappa D}{\mu - 2\rho}$  and local skew  $\mathcal{L}(t) \leq \left(2 \left\lceil \log_{\mu/\rho} \frac{\mu D}{\mu - 2\rho} \right\rceil + 1\right) \kappa$  for all sufficiently large t.

**Remark 1.** The precise local and global skew bounds achieved by a GCS algorithm at an arbitrary time t depend on the initial state of the system. GCS algorithms are selfstabilizing in the sense that starting from an arbitrary initial state, the algorithm will eventually achieve the skew bounds claimed in Thm. 1 (see [16]). In the appendix, we analyze the speed of convergence as function of local skew at initialization.

In order to fulfill the invariants of a GCS algorithm, each node v maintains estimates of the offsets to neighboring clocks. Specifically, for each neighboring node w, v computes an offset estimate  $\hat{O}_w(t) \approx L_w(t) - L_v(t)$ . Given offset estimates for each neighbor, the synchronization algorithm determines if v should run in fast mode by checking if the fast trigger (FT) is satisfied, as defined below. The trigger is parametrized by variables  $\kappa$  (as in the GCS algorithm) and  $\delta$ , whose values are determined by the quality of estimates of neighboring clock values.

**Definition 3.** We say that v satisfies the fast trigger, FT, if there exists  $s \in \mathbb{N}$  such that the following conditions hold:

**FT1**

$$O_{\max} \ge (2s+1)\kappa - \delta$$

,

**FT2**  $\widehat{O}_{\min} \ge -(2s+1)\kappa - \delta$ .

We are now in the position to formalize our GCS algorithm, OffsetGCS (Algorithm 1). OffsetGCS is simple: at each time, each node checks if it satisfies **FT**. If so, it runs in fast mode. Otherwise, the node runs in slow mode. As the decision to run fast or slow is a discrete decision, a hardware implementation will be prone to metastability [17]. We discuss how to work around this problem in Section III.

| lgorithm 1 OffsetGCS algorithm for node v                                                             |

|-------------------------------------------------------------------------------------------------------|

| 1: At each time $t$ do                                                                                |

| 2: $\widehat{Q}_{\min} \leftarrow \min_{w} \{ \widehat{Q}_{w}(t) \mid w \text{ is neighbor of } v \}$ |

| $\widehat{O}_{\max} \leftarrow \max_{w} \{ \widehat{O}_{w}(t) \mid w \text{ is neighbor of } v \}$    |

| 4: <b>if</b> v satisfies <b>FT then</b>                                                               |

| 5: <b>#</b> fast mode (rate in $[(1 + \mu), (1 + \rho)(1 + \mu)])$                                    |

| 6: rate of $L_v \leftarrow (1+\mu) \cdot \text{rate of } H_v$                                         |

| 7: else                                                                                               |

| 8: <b>#</b> slow mode (rate in $[1, (1 + \rho)]$ )                                                    |

| P: rate of $L_v \leftarrow$ rate of $H_v$                                                             |

In what follows, we show that for a suitable choice of parameters, OffsetGCS is a GCS algorithm in the sense of Def. 2. Thus, OffsetGCS maintains the skew bounds of Thm. 1.

## B. Analysis of the OffsetGCS algorithm

We denote an upper bound on the overall uncertainty of v's estimate of w by  $\delta$ :

$$\left|\widehat{O}_w(t) - (L_w(t) - L_v(t))\right| \le \delta.$$

(2)

In our analysis, it will be helpful to distinguish two sources of uncertainty faced by any implementation of the GCS algorithm. The first is the *propagation delay uncertainty*, which is the absolute timing variation in signal propagation adding to the measurement error. We use the parameter  $\delta_0 > 0$  to denote an upper bound on this value.

The second source of error is the time between initiating a measurement and actually "using" it in control of the logical clock speed. During this time, the logical clocks advance at rates that are not precisely known. Here, we can exploit that the maximum rate difference between any two logical clocks is  $(1+\rho)(1+\mu)-1 = \rho+\mu+\rho\mu$ . Thus, denoting the *maximum* end-to-end latency by  $T_{\text{max}}$ , this contributes an error of at most  $(\rho + \mu + \rho\mu)T_{\text{max}}$  at any given time. Time  $T_{\text{max}}$  includes the time for the logical clock to respond to control signal.

Once suitable values of  $\delta_0$  and  $T_{\max}$  are determined,  $\delta$  can be computed easily.

## **Lemma 1.** With $\delta = \delta_0 + (\rho + \mu + \rho\mu) \cdot T_{\text{max}}$ , Ineq. (2) holds.

Based on  $\delta$ , we now seek to choose  $\kappa$  as small as possible to realize the invariants given in Def. 2. The basic idea is to ensure that if a node v satisfies the fast condition at time t (which depends on the unknown phase difference), then it must satisfy the fast trigger (which is expressed in terms of the estimates  $\hat{O}_w$ ), thus ensuring that v is in fast mode at time t. In turn, if the slow condition is not satisfied, we must make sure that the fast trigger does not hold either.

**Lemma 2.** Suppose for all times t an implementation of OffsetGCS satisfies (2). Then for any

$$\kappa > 2\delta$$

(3)

and  $\mu > \rho$ , OffsetGCS is a GCS algorithm.

*Proof.* We verify the conditions of Def. 2. Conditions I1 and I2 are direct consequences of the algorithm specification. For Condition I3, suppose first that v satisfies the fast condition at time t. Therefore, there exists some  $s \in \mathbb{N}$ and neighbor w of v such that  $L_w(t) - L_v(t) \ge (2s + 1)\kappa$ . Therefore, by Ineq. 2,  $\hat{O}_w(t) \ge (2s + 1)\kappa - \delta$ , so that FT1 is satisfied. Similarly, since v satisfies the fast condition, all of its neighbors x satisfy  $L_v(t) - L_x(t) \le (2s + 1)\kappa - \delta$ . Therefore,  $\hat{O}_x(t) \ge -(2s + 1)\kappa$ , hence FT2 is satisfied for the same value of s and v runs in fast mode at time t.

It remains to show that if v satisfies the slow condition at time t, then it does not satisfy **FT** at time t (and, accordingly, is in slow mode). To this end suppose to the contrary that v satisfies **FT** at t. Since v satisfies the slow condition at time t,

$$\exists x \colon L_v(t) - L_x(t) \ge 2s\kappa - \delta \tag{4}$$

$$\forall y \colon L_y(t) - L_v(t) \le 2s\kappa + \delta. \tag{5}$$

Since v is assumed to satisfy **FT** at time t, combining FT1 and FT2 with (2) imply that there exists some  $s' \in \mathbf{N}$  with

$$\exists x \colon L_x(t) - L_v(t) \ge (2s'+1)\kappa - \delta \tag{6}$$

$$\forall y \colon L_v(t) - L_y(t) \le (2s'+1)\kappa + \delta. \tag{7}$$

Combining (5) and (6), we must have

$$(2s'+1)\kappa - \delta \le 2s\kappa + \delta,$$

hence  $2s'\kappa \leq 2s\kappa - \kappa + 2\delta$ . Since  $2\delta < \kappa$ , the previous expression implies that s' < s. Similarly, combining (4) and (7) gives  $2s\kappa - \delta \cdot T_{\max} \leq (2s' + 1)\kappa + \delta$ , hence  $2s\kappa \leq 2s'\kappa + 2\delta < 2(s'+1)\kappa$ . Thus, s < s'+1, or equivalently (since s and s' are integers), that  $s \leq s'$ . However, this final expression contradicts s' < s from before. Thus **FT** cannot be satisfied at time t if the slow condition is satisfied at time t, as desired.

Applying Thm. 1 and Lem. 2 we obtain:

**Corollary 1.** For suitable choices of parameters, OffsetGCS maintains local skew

$$\mathcal{L}(t) \le \left(2\left\lceil \log_{\mu/\rho}\left(\frac{\mu \cdot D}{\mu - 2\rho}\right)\right\rceil + 1\right)\kappa.$$

III. MODULES

For a hardware implementation of the OffsetGCS algorithm, we break down the distributed algorithm into modules. Per node, this will be a local clock and a controller. Per link, we have a time offset measurement module for each node connected via the link. For each module we specify its input and output ports, its functionality, and its delay. We further relate the delay  $T_{\rm max}$  from Section II to the module delays.

#### A. Local Clock

The clock signal of node v is derived from a tunable local clock oscillator. It has input MODE<sub>v</sub>, the mode signal (given by the controller; see Section III-C), and output CLK<sub>v</sub>, the clock signal. The mode signal MODE<sub>v</sub> is used to tune the frequency of the oscillator within a factor of  $1 + \mu$ . An oscillator responds within time  $T_{\text{osc}} \ge 0$ , i.e., switching between the two frequency modes takes at most  $T_{\text{osc}}$  time. We have four requirements to the local clock module:

- (C1) The initial maximum local skew is bounded by  $c \cdot \kappa$  for a parameter c > 0 depending on the implementation of the module.

- (C2) If MODE<sub>v</sub> is constantly 0 (respectively 1) during  $[t T_{osc}, t]$ , then the local oscillator is in *slow* (respectively *fast*) *mode* at time t and the rate of the local oscillator is in  $[1, 1 + \rho]$  (respectively  $[1 + \mu, (1 + \mu)(1 + \rho)]$ ).

- (C3) If MODE<sub>v</sub> is neither constantly 0 nor 1 during  $[t-T_{osc}, t]$ , then the local oscillator is unlocked and its rate is in  $[1, (1 + \mu)(1 + \rho)]$ .

- (C4) Clocks in slow mode are never faster than clocks in fast mode, hence  $\mu > \rho$ .

- Note that if (C2) does not apply, i.e., the mode signal is not stable, (C3) allows an arbitrary rate between fast and slow.

## B. Time Offset Measurement

In order to check whether the **FT** conditions are met, a node v needs to measure the current phase offset  $\hat{O}_w$  to each of its neighbors w. This is achieved by a time offset measurement module between v and each neighbor w. Note that the algorithm does not require a full access to the function  $\hat{O}_w$ , but only to the knowledge of whether  $\hat{O}_w$  has reached a bounded number of thresholds – we elaborate on this shortly.

The inputs of the module are the clock signal of v and w.

The outputs of the module are defined as follows. Let  $S = \{0, \ldots, \ell\}$  with  $\ell > 0$ . The output of the measurement module is a binary string of length  $2(\ell+1)$  bits where the first  $\ell+1$  bits, denoted as  $Q_w^i$ , are going from  $\ell$  to 0, followed by additional  $\ell+1$  bits, denoted as  $Q_w^{-i}$ , going from 0 to  $\ell$ . For example, a module with  $S = \{0, 1\}$  has 4 outputs with thresholds  $3\kappa - \delta$ ,  $\kappa - \delta$ ,  $-\kappa - \delta$ , and  $-3\kappa - \delta$ .

Let  $\varepsilon > 0$  be a (small) time. We require that output  $Q_w^{\pm i}$  is set to 1 if  $\widehat{O}_w(t) \ge \mp (2(i-1)+1)\kappa - \delta + \varepsilon$ . Output  $Q_w^{\pm i}$  is set to 0 if  $\widehat{O}_w(t) \le \mp (2(i-1)+1)\kappa - \delta$ . Otherwise,  $Q_w^{\pm i}$  is unconstrained, i.e., within  $\{0, M, 1\}$ . Here, M denotes a meta-/unstable signal between logical values 0 and 1. Intuitively,  $\varepsilon$ will account for setup/hold times that any realistic hardware implementation will have to account for.

We further require that  $\varepsilon < 2\kappa$ . This guarantees that at most one output is M at a time: Assume that bit  $Q_w^i$  is metastable, then  $\widehat{O}_w(t) \in (2(i-1)+1)\kappa - \delta + [0,\varepsilon]$ . Since the adjacent thresholds are  $2\kappa$  away, their corresponding outputs are either 0 or 1. In fact, by Eq. (3) and since  $\varepsilon \leq \delta_0$  (we account for setup/hold times in  $\delta_0$ ), we get that  $\varepsilon < \frac{\kappa}{2}$ , hence our requirement is satisfied.

Choosing  $\ell \geq \frac{\mathcal{L}/\kappa-1}{2}$ , where  $\mathcal{L}$  is the guaranteed local skew of the OffsetGCS algorithm, guarantees that the nodes will always be within the module's measurement range. Note that  $\mathcal{L}$  here needs to respect the initial local skew as well, i.e.,  $\mathcal{L}$ here is given by the bound from Cor. 1 plus the local skew on initialization (as we show in the appendix).

Given the above, the module outputs form a unary thermometer code of the phase difference between v and w's clocks. Moreover, since this module decides whether a subset of the thresholds are met or not, then inevitably, any implementation of this module (see Section IV) is susceptible to metastable upsets. If implemented correctly, one can leverage the output encoding, which is a unary thermometer code, and guarantee that at most one bit is in a metastable state, located conveniently between a prefix of 1's and a suffix of 0's.

Let  $T_{\text{meas}}$  denote the maximum end-to-end latency of the measurement module, i.e., an upper bound on the elapsed time from when  $Q_w^{\pm i}$  is set, to when the measurements are available at the output. More precisely, if  $Q_w^{\pm i}$  is set to  $x \in \{0, 1\}$  for the entire duration of an interval  $[t - T_{\text{meas}}, t]$ , then the corresponding output is x.

#### C. Controller

Each node v is equipped with a controller module. Its input is the (thermometer encoded) time measurement for each of v's neighbors, i.e., the outputs of the time offsets measurement module on each link connecting v to an adjacent node. It outputs the mode signal MODE<sub>v</sub>.

Denote by  $T_{cnt}$  the maximum end-to-end delay of the controller circuit, i.e., the delay between its inputs (the measurement offset outputs) and its output MODE<sub>v</sub>. The specification of the controllers interface is as follows:

- (L1) For  $t > T_{cnt}$ , if algorithm OffsetGCS continuously maps the rate of v to fast mode (resp. slow mode) during  $[t - T_{cnt}, t]$ , then  $MODE_v(t) = 1$  (resp.  $MODE_v(t) = 0$ )

- (L2) In all other cases, the output at time t is arbitrary, i.e., any value from  $\{0, M, 1\}$ .

## D. Putting it all together

The module specifications above, together, specify a realization of the OffsetGCS algorithm in hardware. The parameters of this hardware specification of OffsetGCS are:  $\delta_0$ ,  $\rho$ ,  $\mu$ , and  $T_{\text{max}}$ , where  $T_{\text{max}} = T_{\text{meas}} + T_{\text{cnt}} + T_{\text{osc}}$ . These parameters are mapped to parameters of Cor. 1 by applying Lem. 2.

## IV. HARDWARE IMPLEMENTATION

We have implemented the modules from Section III and compiled them into a system of 4 nodes, connected in a line from node 0 to node 3. To resemble a realistically sparse spacing of clocks, we placed nodes at distances of  $200 \,\mu$ m. Target technology was the 15 nm FinFET-based Nangate OCL [15]. The gate-level design was laid out and routed with Cadence Encounter, which was also used for extraction of parasitics and timing. Local clocks run at a frequency of approximately 2 GHz, controllable within a factor of  $1 + \mu \approx 1 + 10^{-4}$ . We use  $\mu = 10^{-4}$  here to make the interplay of  $\rho$  and  $\mu$  better visible in traces. We will discuss the gate-level design and its performance measures in the following.

### A. Gate-level Implementation

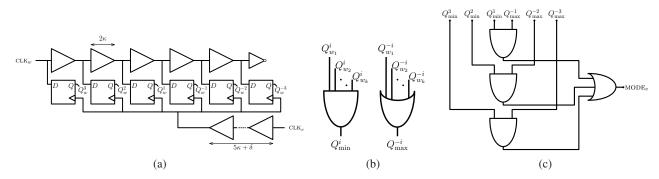

Figures 1a to 1c show the schematics of an implementation of the time offsets measurement module (Figure 1a), and the controller (Figures 1b and 1c).

As a local clock source, we used a ring oscillator with some of its inverters being starved-inverters to set the frequency to either fast mode or slow mode. Nominal frequency is around 2 GHz, controllable by a factor  $1 + \mu \approx 1 + 10^{-4}$  via the MODE<sub>v</sub> signal. We choose  $\rho \approx \mu/10 \approx 10^{-5}$ , assuming a moderately stable oscillator. While this is below drifts achievable with uncontrolled ring oscillators, one may lock the *frequency* of the ring oscillator to a stable external quartz oscillator, see e.g., [18]. For such an implementation, we only require a stable frequency reference for local clocks; the phase difference of the distributed clock signal between adjacent nodes (which may be large) is immaterial. If distributing a stable clock source to all nodes is not feasible or considered too costly for a design, one may choose a larger  $\mu$  resulting in a larger local and global skew bound; see Thm. 1 and Cor. 1.

We measure the logical clock value  $L_v(t)$  in terms of the time passed since its first active clock transition.

The time offset measurement module resembles a time to digital converter (TDC) in both its structure and function. The

Figure 1: Gate-level implementation of the OffsetGCS algorithm's modules. Sub-figure 1a shows a linear TDC-based circuitry for the module which measure the time offsets between nodes v and w. Buffers and inverters are used as delay elements the delay of which appears next to the corresponding delay element. Given node v's time offsets to its neighbors, the circuit in Sub-figure 1b computes the minimum and maximum threshold levels which have been reached. Sub-figure 1c shows the circuit that computes if the **FT** conditions are satisfied, i.e., if there is an  $S \in \{0, 1, 2\}$  that satisfies both **FT1** and **FT2**.

upper delay line in Figure 1a, fed by remote clock w, is tapped at intervals of  $2\kappa$ . The lower delay line is used to shift the module's own local clock v to the middle of the delay line (plus some  $\delta$  offset) so that phase differences can be measured both in the negative and positive direction. The module in Figure 1a is instantiated for  $S = \{0, 1, 2\}$  with 6 taps for threshold levels. In fact, in our hardware implementation we set  $S = \{0, 1\}$ , as even for  $\mu/\rho = 10$  this is sufficient for networks of diameter up to around 80 (see how to choose this set of thresholds in the specification of this module in Sec. III).

If both clocks are perfectly synchronized, i.e.,  $L_v = L_w$ , then the state of the flip-flops will be  $Q^3Q^2Q^1Q^{-1}Q^{-2}Q^{-3} =$ 111000 after a rising transition of CLK<sub>v</sub>. Now, assume that clock w is earlier than clock v, say by a small  $\varepsilon > 0$  more than  $\kappa + \delta$  ps. Then  $L_w = L_v + \kappa - \delta + \varepsilon$ . For the moment assuming that we do not make a measurement error, we get  $\widehat{O}_w = L_w - L_v = \kappa - \delta + \varepsilon$ . From the delays in Figure 1a one verifies that in this case, the flip-flops are clocked before clock w has reached the second flip-flop with output  $Q^1$ , resulting in a snapshot of 110000. Likewise, an offset of  $\widehat{O}_w = L_w - L_v =$  $3\kappa - \delta + \varepsilon$  results in a snapshot of 100000, etc.

However, care has to be taken for non-binary outputs. Given the output specification above, one can verify that measurements are of the form 1\*0\* or 1\*M0\*.

The circuit in Figure 1b then computes the minimum and the maximum of the thermometer codes (by AND and OR gates), determining the thresholds reached by the furthest node ahead and behind v (while possibly masking metastable bits); compare this with lines 2 and 3 in OffsetGCS (Algorithm 1). Figure 1c finally computes the mode signal of v from the thermometer codes, namely verifying whether there is an  $s \in \{0, 1, 2\}$  that satisfies *both* triggers; compare this with **FT1** and **FT2** in Def. 3.

*a) Timing Parameters:* We next discuss how the modules' timing parameters relate to the extracted physical timing of the above design.

The time required for switching between oscillator modes  $T_{\rm osc}$  is about the delay of the ring oscillator, which in our case is about  $1/(2 \cdot 2 \,\text{GHz}) = 250 \,\text{ps}$ . The measurement latency

$T_{\rm meas}$  plus the controller latency  $T_{\rm cnt}$  are given by a clock cycle (500 ps) plus the delay (25 ps) from the flip-flops through the AND/OR circuitry in Figures 1b and 1c to the mode signal. In our case, delay extraction of the circuit yields  $T_{\rm meas} + T_{\rm cnt} < 500 \, {\rm ps} + 25 \, {\rm ps}$ . We thus have,  $T_{\rm max} < T_{\rm meas} + T_{\rm cnt} + T_{\rm osc} = 775 \, {\rm ps}$ .

The propagation delay uncertainty,  $\delta_0$ , in measuring if  $\hat{O}_w$ has reached a certain threshold is given by the uncertainties in latency of the upper delay chain plus the lower delay chain in Figure 1b. For the described naive implementation using an uncalibrated delay line, this would be problematic. With an uncertainty of  $\pm 5\%$  for gate delays, and starting with moderately sized  $\kappa$  and thus length of delay chains, extraction of minimum and maximum delays showed that the constraints for  $\delta$  and  $\kappa$  from Lem. 2 were not met. Successive cycles of increasing  $\delta$  and  $\kappa$  on the uncertainty  $\delta_0$  with a too large factor. Rather, delay variations (of the entire system) have to be less than  $\pm 1\%$  for the linear offset measurement circuit, depicted in Sub-figure 1a, to fulfill Lem. 2's requirements.

#### B. Improvements

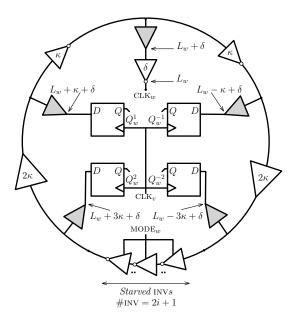

Figure 2 shows an improved TDC-type offset-measurement circuit that does not suffer from the problem above. Conceptually the TDC of node v that measures offsets w.r.t. node w is integrated into the local ring oscillator of neighboring node w. If w has several neighbors, e.g., up to 4 in a grid, they share the taps, but have their own flip-flops within node w. The Figure shows a design for  $S = \{0, 1\}$  with 4 taps, as used in our setup.

Integration of the TDC into w's local ring oscillator greatly reduces uncertainties at both ends: (i) the uncertainty at the remote clock port (of node w) is removed to a large extent, since the delay elements which are used for the offset measurements are part of w's oscillator, and (ii) the uncertainty at the local clock port is greatly reduced by removing the delay line of length  $5\kappa + \delta$ . Remaining timing uncertainties are the latency from taps to the D-ports of the flip-flops and from

Figure 2: Improved offset measurement implementation. The delays of each delay element are written inside it. The gray buffers at the offset measurement taps decouple the load of the remaining circuitry. At the bottom of the ring oscillator an odd number of starved inverters used to set slow or fast mode for node w. The phase offset that we measure in each tap is written next to the corresponding flip-flop. The delay elements at the top are inverters instead of buffers to achieve a latency of  $\kappa = 10$  ps. We inverted the clock output to account for the negated signal at the tap of clock w at the top.

clock v to the CLK-ports of the flip-flop. Timing extraction yielded  $\delta_0 < 4 \text{ ps}$  in presence of  $\pm 5\%$  gate delay variations.

From Lem. 2, we thus readily obtain  $\kappa \approx 10 \,\mathrm{ps}$  and  $\delta \approx 5 \,\mathrm{ps}$  which matched the previously chosen latencies of the delay elements. Applying Thm. 1 and Cor. 1 finally yields a bounds of  $1.223\kappa D = 12.23D \,\mathrm{ps}$  on the global skew and of  $(2\lceil \log_{10}(1.223D) \rceil + 1)\kappa$  on the local skew. For our design with diameter D = 3 this makes a maximum global skew of 36.69 ps and a maximum local skew of  $3\kappa = 30 \,\mathrm{ps}$ . Note that considerably larger systems, e.g., a grid with side length of W = 32 nodes and diameter D = 2W - 2 = 62, still are guaranteed to have a maximum local skew of  $3\kappa = 30 \,\mathrm{ps}$  – and for  $\mu = 10^{-3}$ , the base of the logarithm becomes 100.

## V. SIMULATION AND COMPARISON TO CLOCK TREES

## A. Spice Simulations on a Line Topology

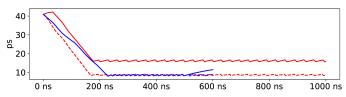

We ran Spice simulations with Cadence Spectre of the postlayout extracted design for 4 nodes arranged in a line, as described in Section IV. The line's nodes are labeled 0 to 3. For the simulations, we set  $\mu = 10\rho$  instead of  $100\rho$ , resulting in slower decrease of skew, to better observe how skew is removed. We simulated two scenarios where node 1 is initialized with an offset of 40 ps ahead of (resp. behind) all other nodes. Simulation time is 1000 ns ( $\approx 2000 \text{ clock cycles}$ ) for the first and 600 ns for the second scenario.

Figure 3: Spice simulation of the line topology. Node 1 has been initialized with a skew of 40 ps ahead of the other nodes. Nodes from left to right: (i) 1 before 0, 2, 3, (ii) 1 before 0, 2 before 3, (iii) 1 before 0, 2 before 3.

Figure 4: Maximum local skew (dotted) and global skew (solid) for the scenarios of node 1 initially being ahead (red) and behind (blue) of all other nodes.

Figure 3 shows the clock signals of nodes 0 to 3 at three points in time for the first scenario: (i) shortly after the initialization, (ii) around 100 ns, and (iii) after 175 ns.

For the mode signals, in the first scenario, we observe the following: Since node 1 is ahead of nodes 0 and 2, node 1's mode signal is correctly set to 0 (slow mode) while node 0 and 2's mode signals are set to 1 (fast mode). Node 3 is unaware that node 1 is ahead since it only observes node 2. By default its mode signal is set to slow mode. When the gap to 2 is large enough it switches to fast mode. This configuration remains until nodes 0 and 2 catch up to 1, where they switch to slow mode, to not overtake node 1. Again node 3 sees only node 2 which is still ahead and switches only after it catches up to 2.

Figure 4 (red lines) depicts the dynamics of the maximum local and global skews for the first scenario. Observe that, from the beginning the local skew decreases until it reaches less than 9 ps. It then remains in an stable oscillatory state where it increases until the algorithm detects and reduces the local skew. This is well below our worst-case bound of 30 ps on the local skew. The global skew first increases, as node 3 does not switch to fast mode immediately. Scenario two shows a similar behaviour (blue lines in Figure 4).

#### B. Comparison to Clock Tree

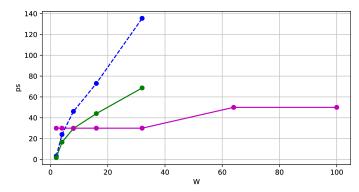

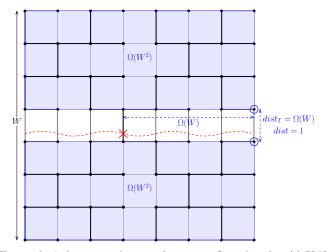

For comparison, we laid out a grid of  $W \times W$  flip-flops, evenly spread in  $200 \,\mu m$  distance in x and y direction across the chip. The data port of a flip-flop is driven by the OR of the up to four adjacent flip-flops. Clock trees were synthesized and routed with Encounter Cadence, with the target to minimize local skews. Delay variations on gates and nets were set to  $\pm 5\%$ . The results are presented in Figures 5. For comparison, we plotted local skews guaranteed by our algorithm for the same grids with parameters extracted from the implementation described in Section IV. Observe the linear growth of the local clock skew and the logarithmic growth of the local skew in our implementation. The figure also shows the skew for a clock tree with delay variations of  $\pm 10\%$ . This comparison

Figure 5: Local skew (ps) between neighboring flip-flops in the  $W \times W$  grid. Clock tree with  $\pm 5\%$  delay variation (solid green) and our algorithm with  $\pm 5\%$  delay variation (solid magenta). The dotted line shows the clock tree with  $\pm 10\%$ delay variation, demonstrating linear growth of the skew also in a different setting. Clock trees are shown up to W = 32after which Encounter ran out of memory.

is relevant, as  $\delta_0$  is governed by *local* delay variations, which can be expected to be smaller than those across a large chip.

It is worth mentioning that it has been shown that no clock tree can avoid the local skew being proportional to W [19].

It is worth mentioning that one can show that for *any* clock tree there are *always* two nodes in the grid that have local skew which is proportional to W. This follows from the fact that there are always two neighboring nodes in the grid which are in distance proportional to W from each other in the clock tree [19], [20]. Accordingly, uncertainties accumulate in a worst case fashion to create a local skew which is proportional to W; this behavior can be observed in Figure 6.

To gain intuition on this result, note that there is always an edge that, if removed (see the edge which is marked by an X in Figure 6), partitions the tree into two subtrees each spanning an area of  $\Omega(W^2)$  and hence having a shared perimeter of length  $\Omega(W)$ . Thus, there must be two adjacent nodes, one on each side of the perimeter, at distance  $\Omega(W)$  in the tree.

Our algorithm, on the other hand, manages to reduce the local skew exponentially to being proportional to  $\log W$ .

#### VI. CONCLUSION

Low skew between neighboring nodes in a chip allows for efficient low-latency communication and provides the illusion of a single clock domain. A classical solution for this problem is to use a clock tree. However, clock trees inevitably produce local skews which are proportional to the diameter of the chip. We propose a solution based on a distributed clock synchronization algorithm. Its main idea is to control the local clocks of each node by measuring the time offsets from its neighbors and switching between fast and slow clock rates.

We compare our implementation to tool-generated 2 GHz clock trees for  $W \times W$  grids in 15 nm technology. Asymptotically, the implementation improves over the clock tree exponentially. Our simulations show an improvement of roughly 50% on the local skew already for W = 32.

Figure 6: A low stretch spanning tree of an  $8 \times 8$  grid [21]. The bold lines depict the spanning tree, i.e., our clock tree in this example. The two neighboring nodes that are of distance 13 in the tree are circled (at the middle right side of the grid).

The algorithmic approach is highly robust. It does not rely on a single node or link, and can stabilize to small skews even under poor initialization conditions. In particular, it will recover from transient faults, and can handle the loss of individual nodes or links by adding simple detection mechanisms [16]. Moreover, it is known how to integrate new or recovering links or nodes by a simple mechanism without interfering with the skew bounds [16]. Thus, our approach provides a flexible and resilient alternative to classic designs.

In future work, we intend to design a full implementation including suitable (locked) oscillators. As demonstrated by the work of Mota et al. [18], systems with much smaller values of  $\rho$  than  $10^{-5}$  are feasible. Consequently, even a simple design is likely to result in sufficiently stable local time references. However, a challenge here is that the oscillators need to be locked to a (frequency) reference. This prevents directly adjusting their phase, which would be in conflict with their locking. This issue can be resolved by using a digitally controlled oscillator derived from the local clock. Such a design is possible using synchronizers (which however would increase  $T_{\rm max}$ ), or could make use of metastability-containing techniques in the vein of Függer et al. [22].

Acknowledgments. We thank the reviewers for their valuable feedback, and in particular the third reviewer for pointers to related work. This research has received funding from the European Research Council (ERC) under the European Unions Horizon 2020 research and innovation programme (grant agreement No 716562), the Israel Science Foundation under Grant 867/19, ANR grant FREDDA (ANR-17-CE40-0013), and the Digicosme working group HicDiesMeus.

#### References

- [1] H. D. Foster, "Trends in functional verification: A 2014 industry study," in 52nd Annual Design Automation Conference. ACM, 2015, p. 48.

- [2] A. J. Martin, "Compiling communicating processes into delayinsensitive vlsi circuits," *Dist. comp.*, vol. 1, no. 4, pp. 226–234, 1986.

- [3] —, "The limitations to delay-insensitivity in asynchronous circuits," in *Beauty is our business*. Springer, 1990, pp. 302–311.

- [4] R. Manohar and Y. Moses, "The eventual c-element theorem for delayinsensitive asynchronous circuits," in 23rd IEEE International Symposium on Asynchronous Circuits and Systems. IEEE, 2017, pp. 102–109.

- [5] —, "Asynchronous signalling processes," in 25th IEEE Int. Symposium on Asynchronous Circuits and Systems. IEEE, 2019, pp. 68–75.

- [6] D. M. Chapiro, "Globally-asynchronous locally-synchronous systems." Stanford Univ CA Dept of Computer Science, Tech. Rep., 1984.

- [7] P. Teehan, M. Greenstreet, and G. Lemieux, "A survey and taxonomy of gals design styles," *IEEE Design & Test of Computers*, vol. 24, no. 5, pp. 418–428, 2007.

- [8] R. Dobkin, R. Ginosar, and C. P. Sotiriou, "Data synchronization issues in gals socs," in *10th International Symposium on Asynchronous Circuits* and Systems. IEEE, 2004, pp. 170–179.

- [9] K. Y. Yun and R. P. Donohue, "Pausible clocking: A first step toward heterogeneous systems," in *Proc. Int. Conference on Computer Design. VLSI in Computers and Processors.* IEEE, 1996, pp. 118–123.

- [10] X. Fan, M. Krstić, and E. Grass, "Analysis and optimization of pausible clocking based gals design," in *IEEE International Conference on Computer Design*. IEEE, 2009, pp. 358–365.

- [11] L. R. Dennison, W. J. Dally, and D. Xanthopoulos, "Low-latency plesiochronous data retiming," in *Proceedings Sixteenth Conference on Advanced Research in VLSI*. IEEE, 1995, pp. 304–315.

- [12] A. Chakraborty and M. R. Greenstreet, "Efficient self-timed interfaces for crossing clock domains," in 9th International Symposium on Asynchronous Circuits and Systems. IEEE, 2003, pp. 78–88.

- [13] C. Lenzen, T. Locher, and R. Wattenhofer, "Tight Bounds for Clock Synchronization," *Journal of the ACM*, vol. 57, no. 2, pp. 1–42, 2010.

- [14] F. Kuhn and R. Oshman, "Gradient Clock Synchronization Using Reference Broadcasts," in *Principles of Distributed Systems*, 13th International Conference, 2009, pp. 204–218. [Online]. Available: https://doi.org/10.1007/978-3-642-10877-8\_17

- [15] M. Martins, J. M. Matos, R. P. Ribas, A. Reis, G. Schlinker, L. Rech, and J. Michelsen, "Open cell library in 15nm freepdk technology," in *Proceedings of the 2015 Symposium on International Symposium on Physical Design*. ACM, 2015, pp. 171–178.

- [16] F. Kuhn, C. Lenzen, T. Locher, and R. Oshman, "Optimal gradient clock synchronization in dynamic networks," *CoRR*, vol. abs/1005.2894, 2010. [Online]. Available: http://arxiv.org/abs/1005.2894

- [17] L. R. Marino, "General Theory of Metastable Operation," *IEEE Transactions on Computers*, vol. 30, no. 2, pp. 107–115, 1981.

- [18] M. Mota, J. Christiansen, S. Debieux, V. Ryjov, P. Moreira, and A. Marchioro, "A flexible multi-channel high-resolution time-to-digital converter asic," in *IEEE Nuclear Science Symp.*, vol. 2, 2000, pp. 9–155.

- [19] Fisher and Kung, "Synchronizing Large VLSI Processor Arrays," *IEEE Transactions on Computers*, vol. C-34, no. 8, pp. 734–740, 1985.

- [20] P. Boksberger, F. Kuhn, and R. Wattenhofer, "On the approximation of the minimum maximum stretch tree problem," *Technical report/ETH*, *Department of Computer Science*, vol. 409, 2003.

- [21] M. James, "Linear solver in linear time." [Online]. Available: https://www.i-programmer.info/news/181-algorithms/5573-linear-solver-i

- [22] M. Függer, A. Kinali, C. Lenzen, and B. Wiederhake, "Fast All-Digital Clock Frequency Adaptation Circuit for Voltage Droop Tolerance," in *Symp. on Asynchronous Circuits and Systems*, 2018.

- [23] W. Rudin, Principles of Mathematical Analysis, 3rd ed. New York: McGraw-Hill Education, 1976.

#### APPENDIX A

#### **PROOF OF LEMMA 1**

*Proof.* Consider the estimate  $\widehat{O}_w(t)$  that the algorithm uses at node v for neighbor w at time t. By definition of  $T_{\max}$ , the measurement is based on clock values  $L_v(t_v)$  and  $L_w(t_w)$ for some  $t_v, t_w \in [t - T_{\max}, t)$ . Without loss of generality, we assume that to measure whether  $L_w - L_v \ge T \in \mathbf{R}$ , the signals are sent at logical times satisfying  $L_w(t_w) - T = L_v(t_v)$ .<sup>4</sup> Denote by  $t'_v \in (t_v, t)$  and  $t'_w \in (t_w, t)$  the times when the respective signals arrive at the data or clock input, respectively, of the register<sup>5</sup> indicating whether  $\widehat{O}_w \ge T$  for a given threshold T. By definition of  $\delta_0$ , we have that

$$|t'_v - t_v - (t'_w - t_w)| \le \delta_0.$$

Note that the register indicates  $\widehat{O}_w(t) \ge T$ , i.e., latches 1, if and only if  $t'_w < t'_v$ .<sup>6</sup> Thus, we need to show

$$L_w(t) - L_v(t) \ge T + \delta \implies t'_w < t'_v$$

$$L_w(t) - L_v(t) \le T - \delta \implies t'_w > t'_v$$

Assume first that  $L_w(t) - L_v(t) \ge T + \delta$ . Then, using I4 and that  $L_w(t_w) - T = L_v(t_v)$ , we can bound

$$T + \delta \leq L_w(t) - L_v(t) \\ \leq L_w(t_v) - L_v(t_v) + ((1 + \mu)(1 + \rho) - 1)(t - t_v) \\ = L_w(t_v) - L_w(t_w) + T + (\mu + \rho + \rho\mu)(t - t_v) \\ \leq t_v - t_w + T + (\mu + \rho + \rho\mu)(t - \min\{t_v, t_w\}) \\ < t_v - t_w + T + (\mu + \rho + \rho\mu)T_{\text{max}}.$$

Hence,

$$t'_{w} - t'_{v} \ge t_{w} - t_{v} - \delta_{0} > \delta - \delta_{0} - (\mu + \rho + \rho \mu)T_{\max} = 0.$$

For the second implication, observe that it is equivalent to

$$L_v(t) - L_w(t) \ge -T + \delta \implies t'_v > t'_w.$$

As we have shown the first implication for any  $T \in \mathbf{R}$ , the second follows analogously by exchanging the roles of v and w.

## APPENDIX B Proof of Theorem 1

In this appendix, we prove Theorem 1. We assume that at (Newtonian) time t = 0, the system satisfies *some* bound on local skew. The analysis we provide shows that the GCS algorithm maintains a (slightly larger) bound on local skew for all  $t \ge 0$ . An upper bound on the local skew also bounds the number of values of s for which FC or SC (Definition 1) can hold, as a large s implies a large local skew. (For example, if a node v satisfies FC1 for some s, then v has a neighbor xsatisfying  $L_x(t) - L_v(t) \ge (2s+1)\kappa$ , implying that  $\mathcal{L}(t) \ge c$  $(2s+1)\kappa$ .) Accordingly, an implementation need only test for values of s satisfying  $|s| < \frac{1}{2\kappa} \mathcal{L}_{\max}$ , where  $\mathcal{L}_{\max}$  is an upper bound on the local skew. Our analysis also shows that given an arbitrary initial global skew  $\mathcal{G}(0)$ , the system will converge to the skew bounds claimed in Theorem 1 within time  $O(\mathcal{G}(0)/\mu)$ . We note that the skew upper bounds of Theorem 1 match the lower bounds of [13] up to a factor of approximately 2, and these lower bounds apply even under the assumption of initially perfect synchronization (i.e., systems with  $\mathcal{L}(0) =$ G(0) = 0.

<sup>5</sup>We assume a register here, but the same argument applies to any stateholding component serving this purpose in the measurement circuit.

<sup>&</sup>lt;sup>4</sup>One can account for asymmetric propagation times by shifting  $L_w(t_w)$  and  $L_v(t_v)$  accordingly, so long as this is accounted for in  $T_{\text{max}}$  and carry out the proof analogously.

<sup>&</sup>lt;sup>6</sup>For simplicity of the presentation we neglect the setup/hold time  $\varepsilon$  (accounted for in  $\delta_0$ ) and metastability; see Section III for a discussion.

Our analysis also assumes that logical clocks are differentiable functions. This assumption is without loss of generality: By the Stone-Weierstrass Theorem (cf. Theorem 7.26 in [23]) every continuous function on a compact interval can be approximated arbitrarily closely by a differentiable function.

We will rely on the following technical result. We provide a proof in Section B-E.

**Lemma 3.** For  $k \in \mathbb{Z}$  and  $t_0, t_1 \in \mathbb{R}_{\geq 0}$  with  $t_0 < t_1$ , let  $\mathcal{F} = \{f_i \mid i \in [k]\}$ , where each  $f_i \colon [t_0, t_1] \to \mathbb{R}$  is a differentiable function. Define  $F \colon [t_0, t_1] \to \mathbb{R}$  by  $F(t) = \max_{i \in [k]} \{f_i(t)\}$ . Suppose  $\mathcal{F}$  has the property that for every i and t, if  $f_i(t) = F(t)$ , then  $\frac{d}{dt}f_i(t) \leq r$ . Then for all  $t \in [t_0, t_1]$ , we have  $F(t) \leq F(t_0) + r(t - t_0)$ .

Throughout this section, we assume that each node runs an algorithm satisfying the invariants stated in Definition 2. By Lemmas 1 and 2, Algorithm 1 meets this requirement if  $\kappa > 2\delta + 2(\rho + \mu + \rho\mu)T_{max}$ .

#### A. Leading Nodes

We start by showing that skew cannot build up too quickly. This is captured by analyzing the following functions.

**Definition 4** ( $\Psi$  and Leading Nodes). For each  $v \in V$ ,  $s \in \mathbb{N}$ , and  $t \in \mathbb{R}_{>0}$ , we define

$$\Psi_{v}^{s}(t) = \max_{w \in V} \{ L_{w}(t) - L_{v}(t) - 2s\kappa d(v, w) \},\$$

where d(v, w) denotes the distance between v and w in G. Moreover, set

$$\Psi^{s}(t) = \max_{v \in V} \{\Psi^{s}_{v}(t)\}$$

Finally, we say that  $w \in V$  is a leading node if there is some  $v \in V$  satisfying

$$\Psi_v^s(t) = L_w(t) - L_v(t) - 2s\kappa d(v, w) > 0$$

Observe that any bound on  $\Psi^s$  implies a corresponding bound on  $\mathcal{L}$ : If  $\Psi^s(t) \leq \kappa$ , then for any adjacent nodes v, wwe have  $L_w(t) - L_v(t) - 2s\kappa \leq \Psi^s(t) \leq \kappa$ . Therefore,  $\Psi^s(t) \leq \kappa \implies \mathcal{L} \leq (2s+1)\kappa$ . Our analysis will show that in general,  $\Psi^s(t) \leq \mathcal{G}_{\max}/\sigma^s$  for every  $s \in \mathbf{N}$  and all times t. In particular, considering  $s = \lceil \log_{\mu/\rho} \mathcal{G}_{\max}/\kappa \rceil$  gives a bound on  $\mathcal{L}$  in terms of  $\mathcal{G}_{\max}$ . Because  $\mathcal{G}(t) = \Psi^0(t)$ , the skew bounds will then follow if we can suitably bound  $\Psi^0$  at all times.

Note that the definition of  $\Psi_v^s$  is closely related to the definition of the slow condition. In fact, the following lemma shows that if w is a leading node, then w satisfies the slow condition. Thus,  $\Psi^s$  cannot increase quickly: **I4** (Def. 2) then stipulates that leading nodes increase their logical clocks at rate at most  $1 + \rho$ . This behavior allows nodes in fast mode to catch up to leading nodes.

**Lemma 4** (Leading Lemma). Suppose  $w \in V$  is a leading node at time t. Then  $\frac{d}{dt}L_w(t) = \frac{d}{dt}H_w(t) \in [1, 1 + \rho]$ .

*Proof.* By I4, the claim follows if w satisfies the slow condition at time t. As w is a leading node at time t, there are  $s \in \mathbf{N}$  and  $v \in V$  satisfying

$$\Psi_{v}^{s}(t) = L_{w}(t) - L_{v}(t) - 2s\kappa d(v, w) > 0.$$

In particular,  $L_w(t) > L_v(t)$ , so  $w \neq v$ . For any  $y \in V$ , we have

$$L_w(t) - L_v(t) - 2s\kappa d(v, w) = \Psi_v^s(t)$$

$$\geq L_y(t) - L_v(t) - 2s\kappa d(y, w).$$

Rearranging this expression yields

$$L_w(t) - L_y(t) \ge 2s\kappa(d(v, w) - d(y, w)).$$

In particular, for any  $y \in N_v$ ,  $d(v, w) \ge d(y, w) - 1$  and hence

$$L_y(t) - L_w(t) \le 2s\kappa,$$

i.e., SC2 holds for s at w.

Now consider  $x \in N_v$  so that d(x, w) = d(v, w) - 1. Such a node exists because  $v \neq w$ . We obtain

$$L_w(t) - L_y(t) \ge 2s\kappa.$$

Thus SC1 is satisfied for s, i.e., indeed the slow condition holds at w at time t.

Lemma 4 can readily be translated into a bound on the growth of  $\Psi_w^s$  whenever  $\Psi_w^s > 0$ .

**Lemma 5** (Wait-up Lemma). Suppose  $w \in V$  satisfies  $\Psi_w^s(t) > 0$  for all  $t \in (t_0, t_1]$ . Then

$$\Psi_w^s(t_1) \le \Psi_w^s(t_0) - (L_w(t_1) - L_w(t_0)) + (1+\rho)(t_1 - t_0).$$

*Proof.* Fix  $w \in V$ ,  $s \in \mathbb{N}$  and  $(t_0, t_1]$  as in the hypothesis of the lemma. For  $v \in V$  and  $t \in (t_0, t_1]$ , define the function  $f_v(t) = L_v(t) - 2s\kappa d(v, w)$ . Observe that

$$\max_{v \in V} \{ f_v(t) \} - L_w(t) = \Psi_w^s(t) \,.$$

Moreover, for any v satisfying  $f_v(t) = L_w(t) + \Psi_w^s(t)$ , we have  $L_v(t) - L_w(t) - 2s\kappa d(v, w) = \Psi_w^s(t) > 0$ . Thus, Lemma 4 shows that v is in slow mode at time t. As (we assume that) logical clocks are differentiable, so is  $f_v$ , and it follows that  $\frac{d}{dt}f_v(t) \le 1+\rho$  for any  $v \in V$  and time  $t \in (t_0, t_1]$ satisfying  $f_v(t) = \max_{x \in V} \{f_x(t)\}$ . By Lemma 3, it follows that  $\max_{v \in V} \{f_v(t)\}$  grows at most at rate  $1 + \rho$ :

$$\max_{v \in V} \{ f_v(t_1) \} \le \max_{v \in V} \{ f_v(t_0) \} + (1+\rho)(t_1 - t_0) \,.$$

We conclude that

$$\Psi_w^s(t_1) - \Psi_w^s(t_0) = \max_{v \in V} \{f_v(t_1)\} - L_w(t_1) - (\max_{v \in V} \{f_v(t_0)\} - L_w(t_0)) \leq (1+\rho)(t_1 - t_0) - (L_w(t_1) - L_w(t_0)),$$

which can be rearranged into the desired result.

**Corollary 2.** For all  $s \in \mathbf{N}$  and times  $t_1 \ge t_0$ ,  $\Psi^s(t_1) \le \Psi^s(t_0) + \rho(t_1 - t_0)$ .

*Proof.* Choose  $w \in V$  such that  $\Psi^s(t_1) = \Psi^s_w(t_1)$ . As  $\Psi^s_w(t) \ge 0$  for all times t, nothing is to show if  $\Psi^s(t_1) = 0$ . Let  $t \in [t_0, t_1)$  be the supremum of times from  $t' \in [t_0, t_1)$  with the property that  $\Psi^s_w(t') = 0$ . Because  $\Psi^s_w$  is continuous,  $t \neq t_0$  implies that  $\Psi^s_w(t) = 0$ . Hence,  $\Psi^s_w(t) \le \Psi^s_w(t_0)$ . By **I2** and Lemma 5, we get that

$$\begin{split} \Psi^{s}(t_{1}) &= \Psi^{s}_{w}(t_{1}) \\ &\leq \Psi^{s}_{w}(t) - (L_{w}(t_{1}) - L_{w}(t)) + (1 + \rho)(t_{1} - t) \\ &\leq \Psi^{s}_{w}(t) + \rho(t_{1} - t) \\ &\leq \Psi^{s}_{w}(t_{0}) + \rho(t_{1} - t_{0}) \\ &\leq \Psi^{s}(t_{0}) + \rho(t_{1} - t_{0}). \end{split}$$

Trailing Nodes

As  $L_w(t_1) - L_w(t_0) \ge t_1 - t_0$  at all times by **I2**, Lemma 7 implies that  $\Psi^s$  cannot grow faster than at rate  $\rho$  when  $\Psi^s(t) >$ 0. This means that nodes whose clocks are far behind leading nodes can catch up, so long as the lagging nodes satisfy the fast condition and thus run at rate at least  $1 + \mu$  by **I3**. Our next task is to show that "trailing nodes" always satisfy the fast condition so that they are never too far behind leading nodes. The approach to showing this is similar to the one for Lemma 5, where now we need to exploit the fast condition.

**Definition 5** ( $\Xi$  and Trailing Nodes). *For each*  $v \in V$ ,  $s \in \mathbb{N}$ , *and*  $t \in \mathbb{R}_{>0}$ , *we define*

$$\Xi_v^s(t) = \max_{w \in V} \{ L_v(t) - L_w(t) - (2s+1)\kappa d(v,w) \},\$$

where d(v, w) denotes the distance between v and w in G. Moreover, set

$$\Xi^s(t) = \max_{v \in V} \{\Xi^s_v(t)\}$$

Finally, we say that  $w \in V$  is a trailing node at time t, if there is some  $v \in V$  satisfying

$$\Xi_v^s(t) = L_v(t) - L_w(t) - (2s+1)\kappa d(v,w) > 0.$$

**Lemma 6** (Trailing Lemma). If  $w \in V$  is a trailing node at time t, then  $\frac{d}{dt}L_w(t) = (1+\mu)\frac{d}{dt}H_w(t) \in [1+\mu, (1+\rho)(1+\mu)].$

*Proof.* By I3, it suffices to show that w satisfies the fast condition at time t. Let s and v satisfy

$$L_{v}(t) - L_{w}(t) - (2s+1)\kappa d(v,w)$$

=  $\max_{x \in V} \{L_{v}(t) - L_{x}(t) - (2s+1)\kappa d(v,x)\} > 0.$

In particular,  $L_v(t) > L_w(t)$ , implying that  $v \neq w$ . For  $y \in V$ , we have

$$L_{v}(t) - L_{w}(t) - (2s+1)\kappa d(v,w) \\ \ge L_{v}(t) - L_{y}(t) - (2s+1)\kappa d(v,y).$$

Thus for all neighbors  $y \in N_w$ ,

$$L_y(t) - L_w(t) + (2s+1)\kappa(d(v,y) - d(v,w)) \ge 0.$$

It follows that

$$\forall y \in N_v \colon L_w(t) - L_y(t) \le (2s+1)\kappa,$$

i.e., FC2 holds for s. As  $v \neq w$ , there is some node  $x \in N_v$  with d(v, x) = d(v, w) - 1. Thus we obtain

$$\exists x \in N_v \colon L_y(t) - L_w(t) \ge (2s+1)\kappa,$$

showing FC1 for s, i.e., indeed the fast condition holds at w at time t.

Using Lemma 6, we can show that if  $\Psi_w^s(t_0) > 0$ , w will eventually catch up. How long this takes can be expressed in terms of  $\Psi^{s-1}(t_0)$ , or, if s = 0,  $\mathcal{G}$ .

**Lemma 7** (Catch-up Lemma). Let  $s \in \mathbb{N}$  and  $v, w \in V$ . Let  $t_0$  and  $t_1$  be times satisfying that

$$t_1 \ge t_0 + \frac{\Xi_v^s(t_0)}{\mu}$$

Then

$$L_w(t_1) \ge t_1 - t_0 + L_v(t_0) - (2s+1)\kappa d(v,w).$$

*Proof.* W.l.o.g., we may assume that  $t_1 = t_0 + \Xi_v^s(t_0)/\mu$ , as **I2** ensures that  $\frac{d}{dt}L_w(t) \ge 1$  at all times, i.e., the general statement readily follows. For any  $x \in V$ , define

$$f_x(t) = t - t_0 + L_v(t_0) - L_x(t) - (2s+1)\kappa d(v,x).$$

Again by I2, it thus suffices to show that  $f_w(t) \leq 0$  for some  $t \in [t_0, t_1]$ .

Observe that  $\Xi_{x}^{s}(t_{0}) = \max_{x \in V} \{f_{x}(t_{0})\}$ . Thus, it suffices to show that  $\max_{x \in V} \{f_{x}(t)\}$  decreases at rate  $\mu$  so long as it is positive, as then  $f_{w}(t_{1}) \leq \max_{x \in V} \{f_{x}(t_{1})\} \leq 0$ . To this end, consider any time  $t \in [t_{0}, t_{1}]$  satisfying  $\max_{x \in V} \{f_{x}(t)\} > 0$ and let  $y \in V$  be any node such that  $\max_{x \in V} \{f_{x}(t)\} = f_{y}(t)$ . Then y is trailing, as

$$\Xi_v^s(t) = \max_{x \in V} \{ L_v(t) - L_x(t) - (2s+1)\kappa d(v,x) \}$$

=  $L_v(t) - L_v(t_0) - (t-t_0) + \max_{x \in V} \{ f_x(t) \}$

=  $L_v(t) - L_v(t_0) - (t-t_0) + f_y(t)$

=  $L_v(t) - L_y(t) - (2s+1)\kappa d(v,y)$

and

$$\Xi_v^s(t) = L_v(t) - L_v(t_0) - (t - t_0) + \max_{x \in V} \{f_x(t)\}$$

>  $L_v(t) - L_v(t_0) - (t - t_0) \ge 0.$

Thus, by Lemma 6 we have that  $\frac{d}{dt}L_y(t) \ge 1 + \mu$ , implying  $\frac{d}{dt}f_y(t) = 1 - \frac{d}{dt}L_y(t) \le -\mu$ .

To complete the proof, assume towards a contradiction that  $\max_{x \in V} \{f_x(t)\} > 0$  for all  $t \in [t_0, t_1]$ . Then, applying Lemma 3 again, we conclude that

$$\Xi_{v}^{s}(t_{0}) = \max_{x \in V} \{f_{x}(t_{0})\}$$

>  $-(\max_{x \in V} \{f_{x}(t_{1})\} - \max_{x \in V} \{f_{x}(t_{0})\})$

$\geq \mu(t_{1} - t_{0}) = \Xi_{v}^{s}(t_{0}),$

i.e., it must hold that  $f_w(t) \leq \max_{x \in V} \{f_x(t)\} \leq 0$  for some  $t \in [t_0, t_1]$ .

## B. Base Case and Global Skew

We now prove that if  $\Psi^s(0)$  is bounded for some  $s \in \mathbf{N}$ , it cannot grow significantly and thus remains bounded. This will both serve as an induction anchor for establishing our bound on the local skew and for bounding the global skew, as  $\Psi^0(t) = \mathcal{G}(t)$ . In addition, we will deduce that even if the initial global skew  $\mathcal{G}(0)$  is large, at times  $t \geq \mathcal{G}(0)/\mu$ ,  $\mathcal{G}(t)$  is bounded by  $\mathcal{G}_{\max} = (1 - 2\rho/\mu)\kappa D$ .

To this end, we will apply Lemma 7 in the following form.

**Corollary 3.** Let  $s \in \mathbf{N}$  and  $t_0$ ,  $t_1$  be times satisfying

$$t_1 \ge t_0 + \frac{\Psi^s(t_0)}{\mu}.$$

Then, for any  $w \in V$  we have

$$L_w(t_1) - L_w(t_0) \ge t_1 - t_0 + \Psi_w^s(t_0) - \kappa \cdot D.$$

*Proof.* If  $\Psi_w^s(t_0) - \kappa \cdot D \leq 0$ , the claim is trivially satisfied due to **I2** guaranteeing that  $\frac{d}{dt}L_w(t) \geq 1$  at all times t. Hence, assume that  $\Psi_w^s(t_0) - \kappa \cdot D > 0$  and choose any v so that

$$\Psi_w^s(t_0) = L_v(t) - L_w(t) - 2s\kappa d(v, w).$$

We have that

$$\Xi_v^s(t_0) \ge L_v(t) - L_w(t) - (2s+1)\kappa d(v,w)$$

$$\ge L_v(t) - L_w(t) - 2s\kappa d(v,w) - \kappa \cdot D$$

$$= \Psi_w^s(t_0) - \kappa \cdot D.$$

As trivially  $\Psi^s(t_0) \ge \Xi^s(t_0) \ge \Xi^s_v(t_0)$ , we have that  $t_1 \ge t_0 + \Xi^s_v(t_0)/\mu$  and the claim follows by applying Lemma 7.  $\Box$

Combining this corollary with Lemma 5, we can bound  $\Psi^s$  at all times.

**Lemma 8.** Fix

$$s \in \mathbf{N}$$

. If  $\Psi^s(0) \le \kappa \cdot D/(1 - \rho^2/\mu^2)$ , then

$\Psi^s(t) \le \frac{\mu}{\mu - \rho} \cdot \kappa \cdot D$ .

at all times t. Otherwise,

$$\Psi^{s}(t) \leq \begin{cases} \left(1 + \frac{\rho}{\mu}\right) \cdot \Psi^{s}(0) & \text{if } t \leq \frac{\Psi^{s}(0)}{\mu} \\ \kappa \cdot D + \frac{\rho}{\mu} \cdot \left(1 + \frac{\rho}{\mu}\right) \cdot \Psi^{s}(0) & \text{else.} \end{cases}$$

*Proof.* For  $t \leq \Psi^s(0)/\mu$ , the claim follows immediately from Corollary 2 (and possibly using that  $\Psi^s(0) \leq \kappa \cdot D/(1 - \rho^2/\mu^2))$ . Concerning larger times, denote by *B* the bound that needs to be shown and suppose that  $\Psi^s(t_1) = B + \varepsilon$  for some  $\varepsilon > 0$  and minimal  $t_1 > \Psi^s(0)/\mu$ . Choose  $w \in V$  so that  $\Psi^s_w(t_1) = \Psi^s(t_1)$  and  $t_0$  such that  $t_1 = t_0 + \Psi^s(t_0)/\mu$ . Such a time must exist, because the function  $f(t) = t_1 - t - \Psi^s(t)/\mu$ is continuous and satisfies

$$f(t_1) = -\frac{\Psi^s(t_1)}{\mu} < 0 < t_1 - \frac{\Psi^s(0)}{\mu} = f(t_0).$$

We apply Lemma 5 and Corollary 3, showing that

$$\begin{split} \Psi_w^s(t_1) &\leq \Psi_w^s(t_0) - (L_w(t_1) - L_w(t_0)) + (1+\rho)(t_1 - t_0) \\ &\leq \kappa \cdot D + \rho(t_1 - t_0) \\ &= \kappa \cdot D + \frac{\rho}{\mu} \Psi^s(t_0). \end{split}$$

We distinguish two cases. If  $\Psi^s(0) \leq \kappa \cdot D/(1-\rho^2/\mu^2)$ , we have that

$$\Psi^s(t_0) < \frac{\mu}{\mu - \rho} \cdot \kappa \cdot D + \varepsilon,$$

because  $t_0 < t_1$ , leading to the contradiction

$$\frac{\mu}{\mu-\rho}\cdot\kappa\cdot D+\varepsilon=\Psi^s(t_1)<\left(1+\frac{\rho}{\mu-\rho}\right)\cdot\kappa\cdot D+\varepsilon.$$

On the other hand, if  $\Psi^s(0) > \kappa \cdot D/(1 - \rho^2/\mu^2)$ , this is equivalent to

$$\kappa \cdot D + \frac{\rho}{\mu} \cdot \left(1 + \frac{\rho}{\mu}\right) \cdot \Psi^s(0) > \left(1 + \frac{\rho}{\mu}\right) \cdot \Psi^s(0).$$

Hence,

$$\Psi^{s}(t_{0}) < \kappa \cdot D + \frac{\rho}{\mu} \cdot \left(1 + \frac{\rho}{\mu}\right) \cdot \Psi^{s}(0) + \varepsilon$$

and we get that

$$\begin{aligned} \kappa \cdot D &+ \frac{\rho}{\mu} \cdot \left( 1 + \frac{\rho}{\mu} \right) \cdot \Psi^s(0) + \varepsilon \\ &= \Psi^s(t_1) \\ &< \kappa \cdot D + \frac{\rho}{\mu} \cdot \left( \kappa \cdot D + \frac{\rho}{\mu} \cdot \left( 1 + \frac{\rho}{\mu} \right) \cdot \Psi^s(0) + \varepsilon \right). \end{aligned}$$

This implies the contradiction

$$\Psi^s(0) < \frac{\kappa \cdot D}{1 + \rho/\mu} + \frac{\rho}{\mu} \cdot \Psi^s(0)$$

to

$$\Psi^{s}(0) > \kappa \cdot D/(1 - \rho^{2}/\mu^{2}).$$

**Corollary 4.** Abbreviate  $q = \frac{\rho}{\mu} \cdot \left(1 + \frac{\rho}{\mu}\right)$  and assume that  $q \leq \frac{3}{4}$ . For  $i, s \in \mathbb{N}$  and times  $t \geq 4(\Psi^s(0) + i \cdot \kappa \cdot D)/\mu$ , it holds that

$$\Psi^{s}(t) \leq \frac{\kappa D}{1-q} + q^{i} \left(1 + \frac{\rho}{\mu}\right) \Psi^{s}(0).$$

*Proof.* Consider the series given by  $x_0 = (1+\rho/\mu)\Psi_0^s$ ,  $x_{i+1} = \kappa \cdot D + qx_i$ ,  $t_0 = 0$ , and  $t_{i+1} = t_i + \frac{x_i}{\mu}$ . By applying Lemma 8 with time 0 replaced by time  $t_i$  (i.e., shifting time) and  $\Psi^s(0)$  by  $x_i$ , we can conclude that  $x_i$  upper bounds  $\Psi^s(t)$  at times  $t \ge t_i$ . Simple calculations show that  $x_i \le \frac{\kappa D}{1-q} + q^i \Psi^s(0)$  and  $t_i \le 4(\Psi^s(0) + i \cdot \kappa \cdot D)/\mu$ , so the claim follows.

In particular,  $\Psi^s$  becomes bounded by  $(1 + O(\rho/\mu))\kappa D$  within  $O(\Psi^s(0)/\mu)$  time. Plugging in s = 0, we obtain a bound on the global skew.

**Corollary 5.** If

$$\frac{\rho}{\mu} \cdot \left(1 + \frac{\rho}{\mu}\right) \leq \frac{3}{4}$$

, it holds that

$$\mathcal{G}(t) \leq \frac{\kappa D}{1-q} + q^i \left(1 + \frac{\rho}{\mu}\right) \mathcal{G}(0)$$

at all times  $t \geq 4(\mathcal{G}(0) + i \cdot \kappa \cdot D)/\mu$ .

*Proof.* By applying Corollary 4 for s = 0, noting that  $\mathcal{G}(t) = \Psi^0(t)$ .

#### C. Bounding the Local Skew

In order to bound the local skew, we analyze the *average* skew over paths in G of various lengths. For long paths of  $\Omega(D)$  hops, we will simply exploit that we already bounded the global skew, i.e., the skew between *any* pair of nodes. For successively shorter paths, we inductively show that the average skew between endpoints cannot increase too quickly: reducing the length of a path by factor  $\sigma$  can only increase the skew between endpoints by an additive constant term. Thus, paths of constant length (in particular edges) can only have a(n average) skew that is logarithmic in the network diameter.

In order to bound  $\Psi^s$  in terms of  $\Psi^{s-1}$ , we need to apply the catch-up lemma in a different form.

**Corollary 6.** Let  $s \in \mathbb{Z}$  and  $t_0$ ,  $t_1$  be times satisfying

$$t_1 \ge t_0 + \frac{\Psi^{s-1}(t_0)}{\mu}$$

Then, for any  $w \in V$  we have

$$L_w(t_1) - L_w(t_0) \ge t_1 - t_0 + \Psi_w^s(t_0).$$

*Proof.* We have that  $\Psi^{s-1}(t_0) \ge \Xi^{s-1}(t_0)$  and there is some  $v \in V$  satisfying

$$\Psi_w^s(t_0) = L_v(t_0) - L_w(t_0) - 2s\kappa d(v, w)$$

We apply Lemma 7 to  $t_0$ ,  $t_1$ , v, w and level s - 1, yielding that

$$L_w(t_1) - L_w(t_0)$$

$$\geq t_1 - t_0 + L_v(t_0) - L_w(t_0) - (2s - 1)\kappa d(v, w)$$

$$\geq t_1 - t_0 + L_v(t_0) - L_w(t_0) - 2s\kappa d(v, w)$$

$$= t_1 - t_0 + \Psi_w^s(t_0).$$

Combining this corollary with Lemma 5, we can bound  $\Psi^s$  at all times.

**Lemma 9.** Fix  $s \in \mathbb{Z}$  and suppose that  $\Psi^{s-1}(t) \leq \psi^{s-1}$  for all times t. Then

$$\Psi^{s}(t) \leq \begin{cases} \Psi^{s}(0) + \frac{\rho}{\mu} \cdot \psi^{s-1} & \text{if } t \leq \frac{\psi^{s-1}}{\mu} \\ \frac{\rho}{\mu} \cdot \psi^{s-1} & \text{else.} \end{cases}$$

*Proof.* For  $t \leq \psi^{s-1}/\mu$ , the claim follows immediately from Corollary 2. To show the claim for  $t > \psi^{s-1}/\mu$ , assume for contradiction that it does not hold true and let  $t_1$  be minimal such that there  $\Psi^s(t_1) > \rho \psi^{s-1}/\mu + \varepsilon$  for some  $\varepsilon > 0$ . Thus, there is some  $w \in V$  so that

$$\Psi_w^s(t_1) = \Psi^s(t_1) = \frac{\rho}{\mu} \cdot \psi^{s-1} + \varepsilon.$$

Applying Corollary 6 with  $t_0 = t_1 - \psi^{s-1}/\mu$  together with Lemma 5 yields the contradiction

$$\begin{split} \Psi^s_w(t_1) &\leq \Psi^s_w(t_0) - (L_w(t_1) - L_w(t_0)) + (1+\rho)(t_1 - t_0) \\ &\leq \rho(t_1 - t_0) \\ &= \frac{\rho}{\mu} \cdot \psi^{s-1}. \end{split}$$

**Corollary 7.** Fix  $s \in \mathbf{N}$ . Suppose that  $\Psi^s(t) \leq \psi^s$  for all times t and that  $\mathcal{L}(0) \leq 2(s+1)\kappa$ . Then

$$\Psi^{s'}(t) \le \left(\frac{\rho}{\mu}\right)^{s'-s} \psi^s$$

for all  $s' \ge s$  and times t.

*Proof.* Observe that  $\mathcal{L}(0) \leq 2(s+1)\kappa$  implies that  $\Psi^{s'}(0) = 0$  for all s' > s. Thus, the statement follows from Lemma 9 by induction on s', where  $\psi^{s'} = \rho \cdot \psi^{s'-1}/\mu$  and the base case is s' = s.

**Corollary 8.** Fix  $s \in \mathbf{N}$ . Suppose that  $\Psi^s(t) \leq \psi^s$  for all times t. Then

$$\Psi^{s'}(t) \le \left(\frac{\rho}{\mu}\right)^{s-s} \psi^s$$

for all  $s' \ge s$  and times  $t \ge \psi^s/(\mu - \rho)$ .

*Proof.* Consider the times

$$t_{s'} = \sum_{i=1}^{s'-s} \left(\frac{\rho}{\mu}\right)^i \cdot \frac{\psi^s}{\mu} \le \frac{\psi^s}{\mu} \cdot \frac{1}{1-\rho/\mu} = \frac{\psi^s}{\mu-\rho}.$$

We apply Lemma 9 inductively, where in step s' > s we shift times by  $-t_{s'}$ . Thus, all considered times fall under the second case of Lemma 9, i.e., the initial values  $\Psi^{s'}(0)$  (or rather  $\Psi^{s'}(t_{s'})$ ) do not matter.

## D. Putting Things Together

It remains to combine the results on global and local skew to derive bounds that depend on the system parameters and initialization conditions only. First, we state the bounds on global and local skew that hold at all times. We emphasize that this bound on the local skew also bounds up to which level  $s \in \mathbf{N}$  the algorithm needs to check **FT**1 and **FT**2, as larger local skews are impossible.

**Theorem 2.** Suppose that  $\mathcal{L}(0) \leq (2s+1)\kappa$  for some  $s \in \mathbb{N}$ . Then

$$\mathcal{G}(t) \le \left(2s + \frac{\mu}{\mu - \rho}\right) \kappa D$$

and  $\mathcal{L}(t) \le \left(2s + \left\lceil \log_{\mu/\rho} \frac{\mu D}{\mu - \rho} \right\rceil + 1\right) \kappa$

for all  $t \in \mathbf{R}_{\geq 0}$ .

*Proof.* As  $\mathcal{L}(0) \leq (2s+1)\kappa$ , we have that

$$\Psi^{s}(0) \le \max_{v,w \in V} \{d(v,w)\} \cdot \kappa = \kappa \cdot D.$$

By Lemma 8, hence  $\Psi^s(t) \leq \frac{\mu}{\mu - \rho} \cdot \kappa \cdot D$  at all times t. Thus,

$$L_v(t) - L_w(t) - 2s\kappa D \le L_v(t) - L_w(t) - 2s\kappa d(v, w)$$

$$\le \Psi^s(t)$$

$$\le \frac{\mu}{\mu - \rho} \cdot \kappa \cdot D$$

□ for all  $v, w \in V$  and times t, implying the stated bound on the global skew.

Concerning the local skew, apply Corollary 7 with  $\psi^s = \frac{\mu}{\mu - \rho} \cdot \kappa \cdot D$  and  $s' = s + \left\lceil \log_{\mu/\rho} \frac{\mu D}{\mu - \rho} \right\rceil$ , yielding that

$$\Psi^{s'}(t) \le \left(\frac{\rho}{\mu}\right)^{\lceil \log_{\mu/\rho}(\psi^s/\kappa) \rceil} \psi^s \le \kappa$$

Hence, for all neighbors  $v, w \in V$  and all times t,

$$L_v(t) - L_w(t) - 2s'\kappa = L_v(t) - L_w(t) - 2s'\kappa d(v,w)$$

$$\leq \Psi^{s'}(t) \leq \kappa,$$

implying the claimed bound on the local skew.

Theorem 2 bounds the number of levels  $s \in \mathbf{N}$  for which the algorithm needs to check **FT**1 and **FT**2, depending on the local skew at initialization. It also shows that, if the system can be initialized with local skew at most  $\kappa$ , the system maintains the strongest bounds the algorithm guarantees at all times.

**Corollary 9.** Suppose that  $\mathcal{L}(0) \leq \kappa$ . Then

$$\begin{split} \mathcal{G}(t) &\leq \frac{\mu}{\mu - \rho} \cdot \kappa D \\ and \qquad \mathcal{L}(t) &\leq \left( \left\lceil \log_{\mu/\rho} \frac{\mu D}{\mu - \rho} \right\rceil + 1 \right) \kappa \end{split}$$

for all  $t \in \mathbf{R}_{\geq 0}$ .

If such highly accurate initialization is not possible, the algorithm will converge to the bounds from Corollary 9.