# Design, Fabrication and Characterization of Surface Electrode Ion Trap Integrated with TSV

Peng Zhao, Jing Tao, Hong Yu Li, Yu Dian Lim, Luca Guidoni, Chuan Seng Tan

## ▶ To cite this version:

Peng Zhao, Jing Tao, Hong Yu Li, Yu Dian Lim, Luca Guidoni, et al.. Design, Fabrication and Characterization of Surface Electrode Ion Trap Integrated with TSV. IEEE 21st Electronics Packaging Technology Conference (EPTC 2019), Dec 2019, Singapour, Singapore. pp.13-17, 10.1109/EPTC47984.2019.9026716. hal-03066897

# HAL Id: hal-03066897 https://hal.science/hal-03066897v1

Submitted on 15 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Design, Fabrication and Characterization of Surface Electrode Ion Trap Integrated with TSV

Peng Zhao<sup>1</sup>, Jing Tao<sup>1</sup>, Hong Yu Li<sup>2</sup>, Yu Dian Lim<sup>1</sup>, Luca Guidoni<sup>3</sup> and Chuan Seng Tan<sup>1</sup>

- <sup>1</sup>Nanyang Technological University, Singapore, 639798

- <sup>2</sup>Institute of Microelectronics, Agency for Science, Technology and Research (A\*STAR), Singapore 117685

- <sup>3</sup>Laboratoire Matériaux et Phénomènes Quantiques, Université Paris Diderot, France, 75205

- \*Email: tancs@ntu.edu.sg

#### **Abstract**

Further miniaturization of surface electrode ion trap is restricted by wire bonding connection. To resolve this restriction, integration of conventional surface electrode ion trap with through silicon via (TSV) interconnects is proposed and preliminarily demonstrated. Located directly underneath the DC and RF electrodes, TSVs can transmit the electrical signal from interposer to the electrodes on the top. In this work, electrostatic simulation and fabrication processes are introduced to justify the feasibility of this integration. From the electrical characterization (I-V and C-V tests) results, TSV-integrated ion trap exhibits smaller leakage current and lower capacitance than its wire bonding counterparts due to the elimination of large surface area.

#### Introduction

As compared to conventional quadrupole or liner ion trap [1], surface electrode (SE) ion trap (also known as planar Paul trap) has been reported to exhibit superior scalability, flexibility and compatibility with the state-of-the-art CMOS fabrication technologies. Therefore, SE ion trap is one of promising approaches to realizing large-scale quantum computing. Utilizing the combined electric field induced by co-planar static (DC), radio frequency (RF), and ground (GND) surface electrodes, the charged particle can be confined above the electrode surface, where optical addressing will be exerted for quantum information processing [2]. For further scaling of planar Paul trap, the surface electrodes should be miniaturized with compact trap configurations. However, conventional wire bonding on planar Paul trap occupies a relatively large surface area and disrupts the optical addressing, limiting its miniaturizations [3]. Furthermore, wire bonding is technically challenging in some specific SE configurations, such as ring traps [4, 5]. Thus, to mitigate this issue, we proposed a design that uses TSV to replace wire bonding in electrical signals delivery, providing a fine-pitch I/O path from the interposer on the bottom die to surface electrode on the top die. In addition, the use of interposer can offer SE ion trap with higher functional flexibility without extra surface electrode configuration modification.

Differing from through silicon oxide via [5] and polysilicon filled via [6], a completely CMOS-compatible copper-filled TSV integrating with SE ion trap is introduced in this study. In this work, the trap integrated with TSV is denoted as "TSV trap". We demonstrated the design, simulation, fabrication and initial electrical characterization of the TSV trap.

## **Proposed Design and Modeling**

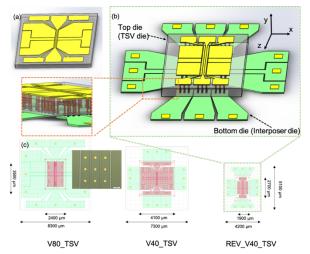

One advantage of using TSV in surface electrode ion trap is the scalability, where ~90% of original surface area can be eliminated as compared to its wire bonding counterparts. At the same time, large electric parasitic resistance and inductance induced by long wire bonding will be reduced. Therefore, based on the configuration of planar Paul traps design [7], configuration-modified SE traps with integrated TSVs stacking on silicon interposer are

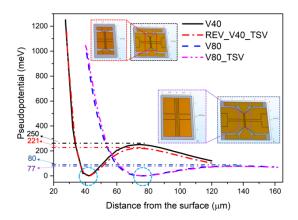

correspondingly designed as illustrated in Fig. 1. According to different RF electrode width (40 and 80 μm), the planar traps are labeled as V40 and V80, respectively. For V40, two types of TSV traps are developed. The first type with modified geometry is shown in Fig. 1(b) and labeled as REV\_V40\_TSV. The original wire bonding pads are removed for all DC and RF electrodes and additional small pads are designed for landing TSV arrays on the top die. In the other type (labeled as V40 TSV), the full geometrical dimensions of planar die are maintained. For V80, due to the relatively large RF/DC line width (80 μm), TSVs can be accommodated directly underneath these electrodes. Therefore, all wire-bonding pads and connecting lines are eliminated without adding additional pads. This design is labeled as V80\_TSV. The geometry parameters of planar and TSV traps are summarized in Table I. According to analytic solution [8, 9] in typical five-wire electrode configuration [10], the ion trapping height is a factor solely determined by the dimension of the three central electrodes (2 RF, 1 GND). In addition, if the ion specie (88Sr+ in this work), operating amplitude and frequency for RF signal are fixed in ion-trapping operations, the trapping depth can be determined. In other words, these two factors in ion trap have no direct relation with the size or shape of the outer DC/GND electrodes. However, the abovementioned can only be established with the assumptions that the length of center electrodes is infinite and the gaps between them are infinitely small. In actual design and experimental conditions, both assumptions are unachievable. Therefore, it is necessary to perform a numerical simulation to figure out the possible effect of the modification of surface electrode geometry on the ion trapping height and trapping depth. Three-dimensional models before and after modification are built accordingly. A RF voltage with 200 V amplitude (peak to peak) and 56 MHz is applied on two RF electrodes simultaneously, while other electrodes are set as ground. Based on the obtained electric field above the electrode surface, pseudopotential at the trap point is derived and compared along y-axis (see Fig. 2). The trapping height is the distance from pseudopotential minimum to the electrode surface, while the trapping depth is the pseudopotential difference between saddle point and trap point. From the simulation results, it is postulated that trapping heights (42 µm for V40, and 76 µm for V80) are maintained and changes in trapping depth are negligible.

## **Fabrication of TSV Trap**

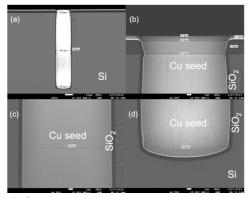

The fabrication uses completely CMOS-compatible processes on a 12-inch silicon wafer. TSV is designed with 100  $\mu m$  height and an aspect ratio of 5. Three geometrical measurements on the TSV opening diameter are performed at the top (16.9  $\mu m$ ), middle (19.1  $\mu m$ ), and bottom (18.2  $\mu m$ ) part of TSV to evaluate its diameter uniformity. After via etching, silicon oxide liner, Ti barrier layer and Cu seed layer are conformally deposited along the TSV pillars. To ensure the TSVs' dielectric strength is sufficiently high, a thick SiO2 liner of 750 nm is used. The morphological features of the TSV opening are showed in Fig. 3. After Cu electroplating, Cu CMP, SiN cap deposition, oxide opening and etching, SiN etching and surface electrode patterning are carried out sequentially at the front side of the top die. Next, a handle wafer is bonded to the front side of the top die, and back side processes including wafer thinning, dielectric pattering and micro bump forming are performed. The fabrication of interposer die is also carried out simultaneously. In the end, top die and interposer die will be bonded together.

### **Electrical Characterization and Discussion**

During ion trap testing, RF signal with ~150 V amplitude is transmitted from interposer to the RF electrodes through TSVs, which will be a major challenge for dielectric liner (SiO2) of

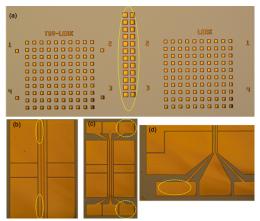

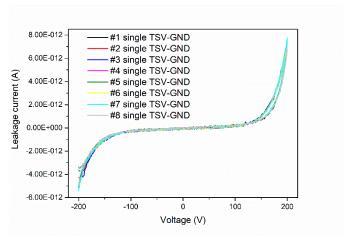

TSVs. To assess the reliability of the TSV liner, a leakage current test is conducted. As illustrated in Fig. 4 (a), a standard TSV array for TSVs leakage current test is designed within the top die [11]. Since the routing interconnects of TSV array on the back side is not completed at the time of this writing, leakage current measurement on single TSV is carried out with this structure.

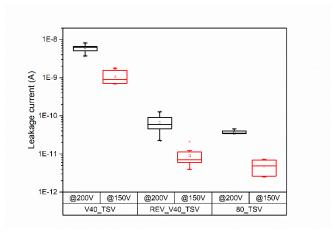

To evaluate the leakage property of TSV array, leakage current for RF electrodes in various ion trap configurations (Fig. 4 (b-d)) are measured and compared. As shown in Fig. 6, for RF electrodes in V80\_TSV (10 TSVs) and REV\_V40\_TSV (12 TSVs), the leakage currents are  $6 \times 10$ -11 and  $9 \times 10$ -11 A, respectively, at 200 V. The total leakage current can be anticipated to correlate linearly with the number of parallel-connected TSVs. The high RF electrode leakage current of V40\_TSV (20 TSVs accommodated) may be attributed to the much larger surface area of V40\_TSV. However, if the peak voltage is set as 150 V, all the leakage currents show a significant decline as shown in Fig. 6.

## **Capacitance Measurement and Discussion**

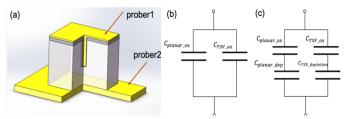

As capacitance is a key factor that determines the RF performance of ion trap, the capacitance value of traps with varying size is investigated. In addition, for TSV traps, the TSV induced capacitance should also be considered. Therefore, CV measurement is conducted on TSV traps and planar traps. To simplify the analytic model, similarly, the single metal oxide semiconductor (MOS) capacitance between surface electrode (RF) and grounding is firstly extracted and measured on the same test vehicles used in IV measurement (Fig. 7 (a)). The CV measurement was conducted with a voltage sweep from -30 to 30 V at AC frequency of 100 kHz. The capacitance curves for both planar TSV traps are plotted in Fig. 8.

The capacitance of TSV traps consists of two components, planar surface and TSVs. These two capacitors are in parallel as illustrated in the schematic (Fig. 7(b)). In the accumulation regime, oxide capacitance will dominate for both components. For planar capacitor, the capacitance per area (C\_(planar\_ox)) can be calculated using equation (1):

$$[ C] _(planar_ox) = \varepsilon_ox/t_ox$$

(1)

where  $\varepsilon$ \_ox is the dielectric constant and t\_ox (3  $\mu$ m) is the thickness of oxide layer. For TSV capacitor, the capacitance for each TSV (C\_(TSV\_ox)) is expressed in equation (2) given by [14]:

$$C_{TSV_ox} = (2\pi\epsilon_o x I_{TSV})/(In_{O}(R_o x/R_copper))$$

(2)

where I\_TSV (100  $\mu$ m) is the length of TSV, R\_ox (10.75  $\mu$ m) is the radius of TSV trench (as etched) and R\_copper (10  $\mu$ m) is the radius of copper core.

When the gate voltage exhibits high negative values (for n-type substrate), a depletion layer will be formed in two spots, under the planar oxide layer and around TSV oxide liner. Thus, the capacitance of depletion layers will come into effect. Under this circumstance, the model should be modified where depletion layer capacitance is added in series with the original oxide capacitance as shown in Fig. 7(c). In the depletion regime, the thickness of depletion layers w\_dep is a key factor and it can be expressed in equation (3) given by [15]:

$$w_{dep}=V((2\varepsilon_{Si} 2\phi_{B})/(qN_{d}))$$

(3)

where  $\epsilon$ \_Si is dielectric constant of silicon,  $\phi$ \_B is the bulk potential and N\_d is donor concentration. To determine the value of N\_d, a spreading resistance profile is carried out from the trap surface down to 110  $\mu$ m depth of silicon substrate to cover the whole TSV length. It is found that the doping concentration is consistent along vertical direction with ~7 × 1013 cm-3 concentration.

The depletion layers thickness w\_dep is calculated to be 2.92  $\mu$ m, similar to the planar oxide layer thickness (3  $\mu$ m) but four times of TSV dielectric liner thickness (0.75  $\mu$ m). This indicates that during depletion, the total capacitance of TSV will be dominated by TSV's depletion layer capacitance and consequently be lowered by ~25%. Nevertheless, the total capacitance of planar MOS will be maintained as the capacitance of planar depletion layer is much higher, relative to the oxide capacitance itself. This explains C-V curve shapes obtained in Fig. 8.

According to the surface area and TSV number per RF electrode, the capacitance of different-size ion traps can be analytically calculated using formulas listed above. In conjunction to the measurement outcomes, the results are summarized in Table II. The calculated capacitance values show a good match with the measured values. From the compiled outcomes, it can be postulated that higher capacitance is obtained from samples with larger surface area and more TSVs.

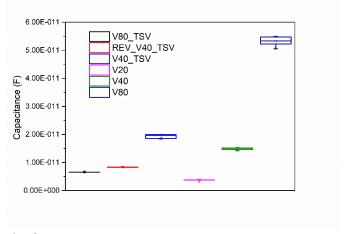

To evaluate the uniformity of the fabrication, a series of C-V measurements are conducted on dies from across the entire wafer. As shown in Fig. 9, the capacitance deviation is rather small for all investigated trap designs. This reflects high consistency and repeatability of trap fabrication across the whole wafer.

From C-V measurement, it is observed that though TSVs can increase the capacitance, the elimination of surface electrode area will evidently decrease it. Therefore, the TSV traps can result in better RF performance compared to their planar counterparts. In the future design, a surface electrode with a smaller area and less TSVs will be preferred.

#### **Conclusions**

Co-integration of TSVs and SE ion trap has been explored. Numerical modeling suggests that the modification of surface electrode configuration has negligible effect on the trapping height and trapping depth. Leakage current measurement shows that TSVs can withstand at least 200 V voltage and maintain a leakage current of 7 × 10-12 A. With the use of TSVs, surface electrode area can be scaled down significantly due to the omission of wire bonding pads. Thus, the overall capacitance has been reduced though TSVs are added. A better RF performance is expected for SE traps integrated with TSV. The given model of TSVs and surface electrode capacitance serve as a guideline for the future improvement and developments of ion trap designs.

### **Acknowledgments**

We acknowledge the funding support from A\*STAR Quantum Technology for Engineering (A1685b0005) for this work. Special appreciation to Dr. Lin Ye for his help in C-V and I-V measurement.

#### References

- 1. W. Paul, "Electromagnetic traps for charged and neutral particles," Reviews of modern physics, Vol. 62, No. 3 (1990), pp. 531.

- 2. D. Stick et al., "Ion trap in a semiconductor chip," Nature Physics, Vol. 2, No. 1 (2006), pp. 36.

- 3. C. D. Bruzewicz et al., "Trapped-ion quantum computing: Progress and challenges," Applied Physics Reviews, Vol. 6, No. 2 (2019), pp. 021314.

- 4. H.-K. Li et al., "Realization of translational symmetry in trapped cold ion rings," Physical review letters, Vol. 118, No. 5 (2017), pp. 053001.

- 5. B. Tabakov et al., "Assembling a ring-shaped crystal in a microfabricated surface ion trap," Physical Review Applied, Vol. 4, No. 3 (2015), pp. 031001.

- 6. N. D. Guise et al., "Ball-grid array architecture for microfabricated ion traps," Journal of Applied Physics, Vol. 117, No. 17 (2015), pp. 174901.

- 7. J. Tao et al., "Fabrication and Characterization of Surface Electrode Ion Trap for Quantum Computing," 2018 IEEE 20th Electronics Packaging Technology Conference (EPTC), Singapore, May. 2018, pp. 363-366.

- 8. M. House, "Analytic model for electrostatic fields in surface-electrode ion traps," Physical Review A, Vol. 78, No. 3 (2008), pp. 033402.

- 9. J. H. Wesenberg, "Electrostatics of surface-electrode ion traps," Physical Review A, Vol. 78, No. 6 (2008), pp. 063410.

- 10. J. Chiaverini et al., "Surface-electrode architecture for ion-trap quantum information processing," arXiv preprint quant-ph/0501147, (2005).

- 11. X. Zhang et al., "Heterogeneous 2.5 D integration on through silicon interposer," Applied Physics Reviews, Vol. 2, No. 2 (2015), pp. 021308.

- 12. M. Farooq et al., "3D copper TSV integration, testing and reliability," 2011 international electron devices meeting, 2011, pp. 7.1. 1-7.1. 4.

- 13. K. K. Mehta et al., "Ion traps fabricated in a CMOS foundry," Applied Physics Letters, Vol. 105, No. 4 (2014), pp. 044103.

- 14. G. Katti et al., "Electrical modeling and characterization of through silicon via for three-dimensional ICs," IEEE Transactions on Electron Devices, Vol. 57, No. 1 (2009), pp. 256-262.

- 15. C. Hu, Modern semiconductor devices for integrated circuits. Prentice-Hall (New Jersey 2010), pp. 157-190.

Table I. Trap Geometry Specifications

| Trap name   | RF     | RF    | Electrode | Area      |

|-------------|--------|-------|-----------|-----------|

|             | line   | line  | area      | reduction |

|             | length | width | $(mm^2)$  |           |

|             | (µm)   | (µm)  |           |           |

| V40         | 1460   | 40    | 12.40     | 79%       |

| REV_V40_TSV | 1460   | 40    | 2.56      |           |

| V80         | 2920   | 80    | 53.56     | 90%       |

| V80_TSV     | 2920   | 80    | 5.32      |           |

Table II. Capacitance computation and measurement results

|                                                | V40 TS  | REV V40 | V80 TSV | V80     |

|------------------------------------------------|---------|---------|---------|---------|

|                                                | V       | TSV     | 100_151 | , 00    |

| Surface area per<br>RF electrode<br>(µm²)      | 1070300 | 330700  | 233600  | 4569600 |

| TSV number per electrode                       | 20      | 12      | 10      | 0       |

| Computed capacitance (pF), accumulation regime | 18.32   | 7.40    | 5.69    | 51.90   |

| Measured capacitance (pF), accumulation regime | 19.30   | 8.31    | 6.60    | 53.30   |

| Computed capacitance (pF), depletion regime    | 12.15   | 4.58    | 3.46    | 43.20   |

| Measured capacitance (pF), depletion regime    | 14.60   | 6.48    | 4.65    | 49.20   |

- Fig. 1. 3D model and layout of TSV trap design, (a) planar trap (V40) and (b) TSV trap (REV\_V40\_TSV) stacked on an interposer die with TSV connections and (c) layouts for different-size TSV traps.

- Fig. 2. Trapping height and trapping depth comparison (before and after configuration modification) for different-size ion traps.

- Fig. 3. Scanning Electron Microscope (SEM) images of TSV opening (a) overall, (b) top, (c) middle and (d) bottom of TSV.

- Fig. 4. Optical images of (a) single TSV, (b) V80\_TSV, (c) REV\_V40\_TSV and (d) left corner of V40\_TSV. Marked areas are the position of TSVs under test.

The test vehicles for TSV leakage current test are illustrated in Fig. 7 (a). A metal pad serving as grounding plane is placed directly under the chip. One prober is contacted on the surface of top die, while the other prober is contacted on the grounding pad. In this case, leakage current from TSVs can be directly measured. Applying a dual voltage sweep ranging from - 200 to 200 V with 2 V step, the leakage current of a single TSV is plotted in Fig. 5. From the 8 repeated measurements, it is observed that single TSV exhibits a maximum leakage current at about  $7 \times 10$ -12 A. From the measurement results, it can be postulated that the dielectric liner of TSV is able to sustain voltage range of -200 to 200 V and the leakage current level agrees well with Farooq et al. and Mehta et al.[12, 13].

- Fig. 5. Repetitive test results for leakage current of single TSV.

- Fig. 6. Statistics summary for leakage current of different-size ion traps @ 150 and 200V.

- Fig. 7. (a) Schematic of test vehicle, (b) circuit mode at accumulation regime of TSV traps and (c) circuit model at depletion regime of TSV traps.

- Fig. 8. Typical C-V curves for planar and TSV traps.

- Fig. 9. Statistics summary for capacitance measurement results.

Fig. 1

Fig. 2

Fig3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9