# High Power AlN/GaN HEMTs with record power-added-efficiency >70% at 40 GHz

Kathia Harrouche, Riad Kabouche, Etienne Okada, F Medjdoub

### ▶ To cite this version:

Kathia Harrouche, Riad Kabouche, Etienne Okada, F Medjdoub. High Power AlN/GaN HEMTs with record power-added-efficiency >70% at 40 GHz. IEEE/MTT-S International Microwave Symposium (IMS 2020), Aug 2020, Los Angeles, CA, United States. Session Tu3H - Advances in Microwave Semiconductor Devices, paper Tu3H-2, 285-288, 10.1109/IMS30576.2020.9223971. hal-03043653

## HAL Id: hal-03043653 https://hal.science/hal-03043653v1

Submitted on 8 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### High Power AlN/GaN HEMTs with record power-added-efficiency >70% at 40 GHz

Kathia Harrouche, Riad Kabouche, Etienne Okada, Farid Medjdoub

CNRS-IEMN, Institut d'Electronique, de Microélectronique et de Nanotechnologie, 59652 Villeneuve-d'Ascq, France

Abstract—We report on breakthrough power-added-efficiency (PAE) Q-band performances using a vertically scaled AlN/GaN HEMT technology. The comparison between a 3 nm and 4 nm barrier thickness shows both superior performance and robustness for the thinner barrier layer attributed to the reduced mechanical strain into the heterostructure. Large signal characteristics at 40 GHz revealed an outstanding PAE of 73% at V<sub>DS</sub> = 30V associated to an output power density > 5 W/mm in pulsed mode. Also, the load-pull measurements mapping across the 4-inch wafer demonstrates a high uniformity and reproducibility of the results. Consequently, significantly improved PAE can be expected for next generation of high power MMICs operating in the millimeter-wave range.

*Keywords*—GaN, HEMTs, AlN/GaN, output power density (Pout), power added efficiency (PAE), Q-band.

#### I. INTRODUCTION

GaN technology has been commercially available for about a decade and is being used for power applications into the millimeter-wave (mm-wave) range owing to its outstanding material properties. In this context, the power-added-efficiency (PAE) becomes a key parameter in order to support complex wave forms with high peak-to-average ratio and large instantaneous bandwidth required for 5G applications for instance. Overall, a high PAE is mandatory in order to reduce the power dissipation, which is a major issue for next generation of compact solid state power amplifiers. Due to its high electron velocity and high breakdown voltage, GaN-based material is well suited for future power amplifier requirements which will enable newer emerging applications. High electron mobility transistors (HEMTs) on SiC substrate have already demonstrated attractive efficiencies in the mm-wave range [1]-[5]. However, state-of-the-art GaN HEMT PAE performances are typically limited to below 50% in the Ka-band and above, especially for significant power density > 2 W/mm. This is mainly due to the lack of power gain, the enhanced trapping effects and reduced electron confinement when downscaling the device size or the self-heating.

Ultrathin barrier AlN/GaN heterostructure is promising for mm-wave range because of the possibility to highly scale the epitaxial structure while still benefiting from a high polarization (i.e. high current density). In this work, a comparison of device performances of two HEMT structures using 3 nm and 4 nm AlN barrier layer is reported with the aim of pushing the PAE limit of mm-wave GaN-based HEMTs.

#### II. DEVICES TECHNOLOGY

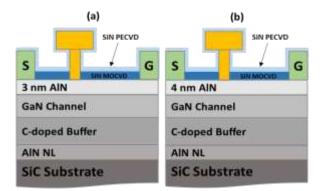

The heterostructure has been grown by metal organic chemical vapour deposition (MOCVD) on 4-inch SiC substrates. Fig. 1 shows the schematic cross section of the HEMT structures based on an AlN nucleation layer, a carbondoped GaN buffer layer followed by a 100 nm GaN channel. The GaN channel thickness has been optimized with respect to the trade-off between deep-level-traps generation and a proper electron confinement. Two different AlN barrier thickness 3 nm (Fig. 1.a) and 4 nm (Fig. 1.b) have been used in order to study the impact on the device performances considering that residual strain is highly dependent on the barrier thickness in such a material system. Finally, a 10 nm thick in-situ Si<sub>3</sub>N<sub>4</sub> was deposited for both structures as early passivation as well as to reduce the surface trapping. The source drain ohmic contacts have been formed by etching the in-situ Si<sub>3</sub>N<sub>4</sub> layer followed by a Ti/Al/Ni/Au metallization annealed at 850°C for structure (a) and 875°C for structure (b). Then, asymmetric self-aligned Ni/Au T-gates have been used to maintain a high breakdown voltage. The gate-to-drain distances (L<sub>GD</sub>) were 1 and 2 µm and the gate length was 110 nm. Finally, the devices were passivated with 200 nm PECVD Si<sub>3</sub>N<sub>4</sub>.

Fig. 1. Schematic cross section of the fabricated (a) 2x50  $\mu m$ , 3 nm AlN/GaN HEMT (b) 2x50  $\mu m$  4 nm AlN/GaN HEMT.

#### III. RESULTS AND DISCUSSION

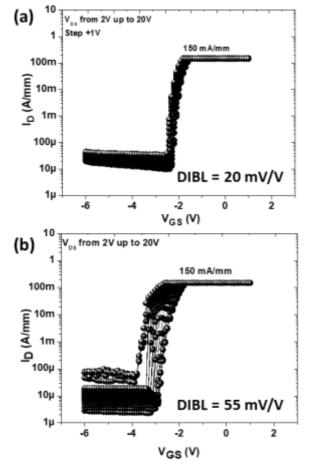

Fig. 2 shows the transfer characteristics with a compliance fixed at 150 mA/mm and swept from  $V_{DS} = 2V$  to 20V for both devices in order to evaluate the electron confinement. Fig. 2a shows an excellent electron confinement for the 3 nm AlN barrier structure reflected by a low DIBL of 14 mV/mm. On the other hand, the 4 nm AlN barrier structure shows a rather poor electron confinement with a much higher DIBL of 55 mV/mm. Also, we observed a systematic degradation of the drain leakage current as a function of the drain bias. This degradation is attributed to the higher residual strain when using thicker

barrier layer as the critical thickness of AlN on GaN is about 2 to 3 nm.

Large signal performances have been assessed at 40 GHz. For all load-pull measurements, the impedance matching has been tuned to favor the PAE. Fig. 3.a shows CW and pulsed power performances at  $V_{DS} = 20V$  of a 4 nm AlN/GaN HEMT with  $L_G = 110$  nm and  $L_{GD} = 2 \,\mu$ m. Under pulsed operation, a saturated  $P_{OUT}$  of 3.2 W/mm associated to a peak PAE of 60% has been achieved. However, due to the trapping effects the PAE drops to 45% in CW mode with a saturated  $P_{OUT}$  of 2.9 W/mm. Despite the attractive power performance, a strong degradation of the drain leakage current on the transfer characteristics is observed after the load-pull measurements at  $V_{DS} = 20$  V as shown in Fig. 3.b. Again, it appears that the strain increases considerably with the AlN barrier thickness enhancing the defect density into the barrier layer thus dramatically reducing the device robustness.

Fig. 2. Transfer characteristics with a compliance fixed at 150 mA/mm and  $V_{DS}$  swept from 2V to 20V for 2x50  $\mu m$  3 nm AlN/GaN HEMT (a) and 4 nm AlN/GaN HEMT (b)

On the other hand, the 3 nm AlN barrier structure using identical design and processing shows a high PAE of 65% and 53% with a saturated  $P_{OUT}$  of 3.3 W/mm and 2.5 W/mm in pulsed mode and CW, respectively (see Fig. 4.a). Interestingly, the transfer characteristics after load-pull measurements at  $V_{DS}$

= 20V show no-degradation of drain leakage current in pulsed mode and a slight increase in CW as seen in Fig. 4.b. This confirms that the thinner barrier layer reduces the mechanical strain leading to a lower defect density, thus resulting in a significantly improved device robustness as compared to thicker barrier.

Fig. 3. CW and pulsed power performances of a 4 nm AlN/GaN HEMT 2x50  $\mu$ m with L<sub>G</sub> = 110 nm and L<sub>GD</sub> = 2  $\mu$ m at V<sub>DS</sub> = 20V (a) and Transfer characteristic before and after load-pull measurements at V<sub>DS</sub> = 20V (b).

Fig. 4. CW and pulsed power performances of a 3 nm AlN/GaN HEMT 2x50  $\mu$ m with L<sub>G</sub> = 110 nm and L<sub>GD</sub> = 2  $\mu$ m at V<sub>DS</sub> = 20V (a) and Transfer characteristic before and after load-pull measurements up to V<sub>DS</sub> = 20V (b).

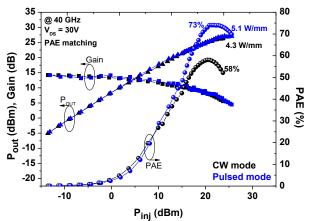

Further scaling of the 3 nm AlN/GaN device design (shorter  $L_{GD}$ ) enabled a record PAE for GaN HEMT at 40 GHz. Fig. 5 shows the CW and pulsed power performances at  $V_{DS} = 30$  V of devices with  $L_G = 110$  nm and  $L_{GD} = 1 \ \mu$ m. An outstanding peak PAE of 73% associated to a saturated P<sub>OUT</sub> above 5 W/mm was achieved under pulsed operation. CW PAE was close to 60% with a P<sub>OUT</sub> of 4.3 W/mm. Moreover, as previously discussed no-degradation of the devices has been observed after load-pull measurements up to  $V_{DS} = 30$ V although a shorter design has been used.

Fig. 5. CW and pulsed power performances of a 3 nm AlN/GaN HEMT 2×50  $\mu$ m with L<sub>G</sub> = 110 nm and L<sub>GD</sub> = 2  $\mu$ m at V<sub>DS</sub> = 30V.

Fig. 6. CW (a) and Pulsed (b),  $P_{\text{OUT}}$  and PAE as a function of  $V_{\text{DS}}$  for 3 nm and 4 nm AlN/GaN HEMT.

The power performance comparisons between the 3 nm and 4 nm AlN/GaN structures in CW and pulsed mode are reported in Fig. 6. At low drain bias voltage ( $V_{DS} < 15$  V), we observed no differences between the 2 structures in terms of power performances both in CW (Fig. 6a) and pulsed mode (Fig. 6b). In contrast, for higher drain bias ( $V_{DS} > 15$  V) an increasing gap appears especially for the PAE as a function of  $V_{DS}$ . To a large extent, this can be attributed to the degradation of the DC characteristics after load-pull measurements of the 4 nm AlN/GaN structure.

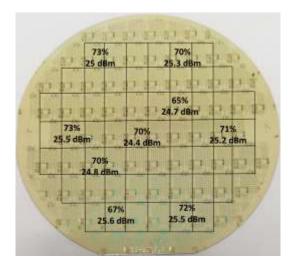

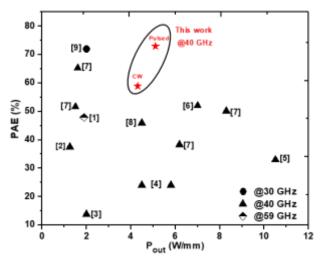

Fig. 7 shows the large signal manual mapping across the 4-inch 3 nm AlN/GaN wafer. Several tenths of devices with similar design ( $2\times50 \ \mu\text{m}$ ,  $L_G = 110 \ nm$ ,  $L_{GD} = 1 \ \mu\text{m}$ ) have been measured across the wafer at 40 GHz with  $V_{DS} = 20 \ V$  under pulsed operation. We clearly observe an excellent yield and uniformity illustrated by a stable PAE/P<sub>OUT</sub> combination (mean PAE ~ 70%, mean P<sub>out</sub> ~ 25 dBm). This power performance combination sets a new benchmark in Q-band as highlighted in Fig. 8.

Fig. 7. Manuel mapping of 40 GHz pulsed large signal performances at  $V_{DS}$  = 20V of the 3 nm AlN/GaN wafer with  $L_G$  = 110 nm and  $L_{GD}$  = 1  $\mu$ m (PAE matching).

Fig. 8. Benchmark of GaN HEMT devices in Ka and Q-band.

#### IV. CONCLUSION

In this work, we performed a comparison between two AlN/GaN HEMT structures on 4-inch SiC substrate using a 3 nm and 4 nm barrier thickness. The power performances of both structures demonstrated the benefit of the AlN barrier layer. However, the 4 nm AlN/GaN structure shows a poor device robustness with a strong degradation after large signal measurements. On the other hand, the 3 nm AlN/GaN structure delivered unprecedented performances at 40 GHz with high drain bias on the full 4-inch wafer while showing a promising device robustness. This is attributed to the strain reduction when using thinner AlN barrier layer (closer to the critical thickness). These results pave the way for next generation of high power MMICs operating in the millimeter-wave range with significantly higher efficiencies than current state-of-theart.

REFERENCES

- M. Micovic *et al.*, "GaN DHFETs Having 48% Power Added Efficiency and 57% Drain Efficiency at V-Band," *IEEE Electron Device Lett.*, vol. 38, no. 12, pp. 1708–1711, 2017.

- [2] T. V Johnson *et al.*, "SiN x / InAlN / AIN / GaN MIS-HEMTs With 10.8 THz . V Johnson Figure of Merit," *IEEE ELECTRON DEVICE Lett.*, vol. 35, no. 5, pp. 527–529, 2014.

- [3] D. Marti et al., "150-GHz Cutoff Frequencies and 2-W / mm Output Power at 40 GHz in a Millimeter-Wave AlGaN / GaN HEMT Technology on Silicon," *IEEE ELECTRON DEVICE Lett.*, vol. 33, no. 10, pp. 1372–1374, 2012.

- [4] S. Tirelli *et al.*, "AllnN-Based HEMTs for Large-Signal Operation at 40 GHz," vol. 60, no. 10, pp. 3091–3098, 2013.

- [5] T. Palacios et al., "High-Power AlGaN / GaN HEMTs for Ka-Band Applications," *IEEE ELECTRON DEVICE Lett.*, vol. 26, no. 11, pp. 781–783, 2005.

- [6] R. Kabouche *et al.*, "High Efficiency AlN/GaN HEMTs for Q-Band Applications with an Improved Thermal Dissipation," *Int. J. High Speed Electron. Syst.*, vol. 28, no. 1–2, pp. 1–11, 2019.

- [7] K. Harrouche, R. Kabouche, E. Okada, and F. Medjdoub, "High Performance and Highly Robust AlN / GaN HEMTs for Millimeter-Wave Operation," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 1145– 1150, 2019.

- [8] E. Dogmus, R. Kabouche, A. Linge, E. Okada, M. Zegaoui, and F. Medjdoub, "High power, high PAE Q-band sub-10 nm barrier thickness AlN/GaN HEMTs," *Phys. Status Solidi A*, vol. 214, no. 8, pp. 1–4, 2017.

- [9] J. Moon et al., "High-speed Linear GaN Technology with a record Efficiency in Ka-band," in EUMW conference, 2019.