# Verilog-A model for avalanche dynamics and quenching in Single-Photon Avalanche Diodes

Y. Oussaiti, D. Rideau, J.R. Manouvrier, V. Quenette, H. Wehbe-Alause, B. Mamdy, A. Lopez, G. Mugny, M. Agnew, E. Lacombe, et al.

## ▶ To cite this version:

Y. Oussaiti, D. Rideau, J.R. Manouvrier, V. Quenette, H. Wehbe-Alause, et al.. Verilog-A model for avalanche dynamics and quenching in Single-Photon Avalanche Diodes. 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Sep 2020, Kobe, Japan. pp.145-148, 10.23919/SISPAD49475.2020.9241648 . hal-03029924

# HAL Id: hal-03029924 https://hal.science/hal-03029924

Submitted on 16 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Verilog-A modeling of avalanche dynamics and quenching in Single-Photon Avalanche Diodes

Y. Oussaiti<sup>1,2</sup>, D. Rideau<sup>1</sup>, J.R. Manouvrier<sup>1</sup>, V. Quenette<sup>1</sup>, H. Wehbe-Alause<sup>1</sup>, B. Mamdy<sup>1</sup>, A. Lopez<sup>1</sup>, G. Mugny<sup>1</sup>,

M. Agnew<sup>1</sup>, E. Lacombe<sup>1</sup>, J. Grebot<sup>1</sup>, P. Dollfus<sup>2</sup>, M. Pala<sup>2</sup>

<sup>1</sup> STMicroelectronics – 38920 Crolles, France.

<sup>2</sup> Centre de Nanosciences et de Nanotechnologies – 91120 Palaiseau, France.

Email: yassine.oussaiti@st.com

Abstract—We present a SPAD Verilog-A model accounting for the temporal avalanche buildup and its statistics. This physics-based approach is benched on TCAD mixed-mode analyzing predictions, as well as measurements. The buildup that can be in the order of 50-100ps, affects the pulse width distribution which is experimentally verified. Furthermore, we address in details the voltage swing across the device from the avalanche to its quenching, with a view on power consumption impact. This model can help a chip designer to optimize circuits for quenching the diode.

## I. INTRODUCTION

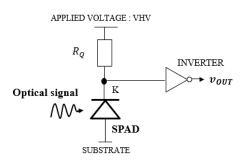

**S** ingle-Photon Avalanche Diodes (SPADs) are reversebiased p-n junctions particularly profitable in Geiger mode. At this regime and when a large voltage is applied, the electric field in the depletion layer becomes strong enough that the charge carriers may acquire sufficient energy to trigger an avalanche through impact ionization mechanisms. Hence, when an absorbed photon leads to a photo electronhole pair generation, an avalanche current rises swiftly and it has to be quenched using external readout electronics (Fig.1). Literature enumerates different types of quenching circuits for which a specific application is best-suited [1], and the SPAD related physics is reviewed by Spinelli and Lacaita [2]. Nowadays, these devices are gaining popularity in automotive industry (Light Detection and Ranging systems [3]) and time-of-flight imaging [4].

This paper introduces a new VerilogA model to assess the SPAD devices buildup and its statistics. For accurate behavior description, we developed a Verilog-A diode model including the underlying physics and calibrated on Technology Computer Aided-Design (TCAD) [5]. Simulations confronted with measurements show an impact on the pulse width distribution, which will be discussed. Additionally, we investigated the voltage swing on the SPAD sensing node. This phenomenon is due to carriers overflow and has a value larger than the excess bias as it has been also demonstrated in [6]. This voltage drop impacts the power consumption and experimental data attests its relevance. Consequently, we discuss the qualitative outputs which in turn will allow us to evaluate the validity of the approach.

### II. MODEL DESCRIPTION

As a representative device, we consider a SPAD with a large collection volume [7]. The currents follow:

$$\int \frac{dI_e}{dt} = [M_e. I_e + M_h. I_h - I_e]/\tau_e \text{, for electrons}$$

$$\frac{dI_h}{dt} = [M_e. I_e + M_h. I_h - I_h]/\tau_h \text{, for holes}$$

$\tau_i$  is the transit time and  $M_i$  the multiplication factor (*i* represents *e* for electrons and *h* for holes). When an electron-hole pair is created, a current  $I_0 = \frac{q.v_s}{w}$  ( $v_s$  is the carriers saturation velocity, q the elementary charge and *W* the effective multiplication region width) can initiate the avalanche. Hence, the total current  $I_T = I_e + I_h$  that is a succession of ionizations  $I_T = I_0(1 + M + M^2 + M^3 + ...)$  can be written in a familiar way as:  $I_T = \frac{I_0}{1-M}$  where  $M = M_e + M_h$ .

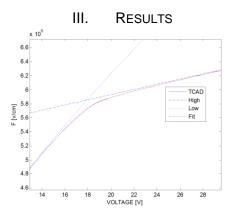

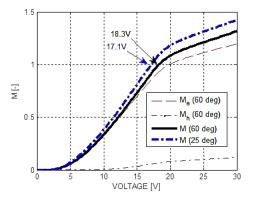

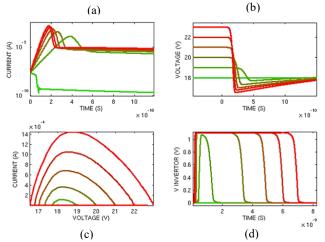

The coefficient  $M_i = \alpha_i \cdot w_i$  depends on  $w_n$  and  $w_p$  [8], as well as on the electric field through:  $\alpha_i = a_i . exp\left(\frac{-b_i}{E}\right) (a_i \text{ and } b_i)$ bi are constants determined Van Overstraeten-de Man model [9]). Therefore, an accurate estimation of the maximum electric field variation with the diode biasing is compulsory. Even though analytical models exist in certain simple cases (e.g. abrupt junction), we used an empirical method that reproduces well-calibrated TCAD predictions on more complex SPAD architectures. As can be seen in Fig.2, a change in the slope of the field versus voltage is observed at  $\sim$ 17V, which occurs when the device starts to deplete its collection volume. Fig.3 shows M as a function of voltage, with  $w_n = 0.0736 \,\mu m$  and  $w_p = 0.092 \,\mu m$ , one obtains *M*=1 for a voltage  $V_B$ = 17.1 V (25°C) which is close to the experimental breakdown voltage value. Fig.4 (top) shows the SPAD current and voltage for various applied biasing as a function of time: the buildup takes typically  $\sim 150 ps$  at operational voltage ( $\sim$ 23V), and can be even larger for lower biasing which is in line with TCAD simulations (not shown). After the avalanche triggering, the rising current is lowered below the breakdown voltage and the diode rearmed. Fig.4 (bottom) shows the SPAD current-voltage characteristics as well as the output pulse width. As can be noticed, the current swing exceeds the excess bias by a factor  $\sim 1.4$ , which has also been recently reproduced in Ref.[6].

Fig. 1. SPAD diode connected to a high quench resistance  $R_Q \sim 500 \ K\Omega$  from the cathode node K. After avalanche triggering, generated charges accumulate and give rise to a measurable current which will be lowered and the device brought to its quiescent state. The inverter component allowing a square output pulse, reflects the swing voltage and hence, the overall time constant of the circuit.

Fig. 2. The empirical model of the electric field (red dashed line) implemented in a Verilog-A code and expressed through a polynomial exploiting the high and low values of the field range. This model is calibrated on TCAD (solid).

Fig. 3. The mean multiplication factor versus voltage, for two temperatures. M= 1 corresponds to  $V_B$ = 17.1 volts at 25°C,

Fig.4: (a) The current buildup evolution with applied voltage (b) The voltage drop seen from the SPAD cathode exhibiting a swing. (c) SPAD I-V curve. (d) The output pulse  $v_{out}$ .

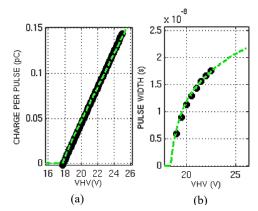

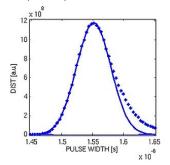

This swing voltage denoted  $V_{KMAX}$ , affects the charge per pulse  $C_{PP}$  (reflecting the power consumption) since  $C_{PP} = C_K \cdot V_{KMAX}$  where  $C_K$  is the total capacitive charge in the cathode node (including parasitic). Fig.5. shows the evolution of  $C_{PP}$  with voltage *VHV*: as  $V_{KMAX}$  increases with applied excess bias,  $C_{PP}$  increases as well. Similarly, the Pulse width distribution, which can be inferred from the statistics of the buildup dynamics itself, is accounted for using a statistical distribution of  $\alpha$  as testified in Fig.6.

Fig. 5. (a) The charge per pulse  $C_{PP}$  and (b) the pulse width versus VHV: Verilog-A model (dashed) versus. measurements (symbols).

Fig. 6. Pulse width distribution. Solid curve refers to Verilog-A model, symbols to measurements.

### IV. CONCLUSION

We have developed a physics-based Verilog-A model for SPADs accounting for the buildup of the avalanche and its statistics. The model compares favorably with more complex TCAD mixed-mode predictions, but also with experimental data. This SPAD model allows SPICE simulations of realistic circuits, including quenching and sensing transistors. It provides an accurate way to estimate the power consumption and the voltage swing on the sensing node.

#### REFERENCES

[1] S. Cova, M. Ghioni, A. Lacaita, C. Samori, and F. Zappa, "Avalanche photodiodes and quenching circuits for single photon detection," Applied Optics, vol. 35, no. 12, pp. 1956–1976, 1996.

[2] A. Spinelli and A.L. Lacaita, "Physics and numerical simulation of Single Photon Avalanche Diodes," IEEE transactions on electron devices, vol. 44, No. 11, pp. 1931-1943, November 1997

[3] I. Takai, H. Matsubara, M. Soga, M. Ohta, M. Ogawa, T. Yamashita, "Single-photon avalanche diode with enhanced NIR-sensitivity for automotive LIDAR systems", Sensors, vol. 16, no. 4, pp. 459, 2016.

[4] F. Mattioli Della Rocca, T. A. Abbas, N. A. W. Dutton and R. K. Henderson, "A high dynamic range SPAD pixel for time of flight imaging," 2017 IEEE SENSORS, Glasgow, 2017, pp. 1-3.

[5] Synopsys, Inc. Version O-2018.06, June 2018.

[6] Inoue, A., Okino, T.,Koyama, S., "Modeling and Analysis of Capacitive Relaxation Quenching in a Single Photon Avalanche Diode (SPAD) Applied to a CMOS Image Sensor", Sensors 2020, 20, 3007.

[7] C. Veerappan and E. Charbon, "A Low Dark Count p-i-n Diode Based SPAD in CMOS Technology," in *IEEE Transactions on Electron Devices*, vol. 63, no. 1, pp. 65-71, Jan. 2016, doi: 10.1109/TED.2015.2475355.

[8] G.J.Rees and J.P.R David, "Nonlocal impact ionization and avalanche multiplication". Journal of Physics D: Applied Physics, IOP Publishing, 2010, 43 (24), pp.243001.

[9] R. van Overstraeten and H. de Man, "Measurement of the Ionization Rates in Diffused Silicon p-n Junctions," Solid-State Electronics, vol. 13, no. 1, pp. 583–608, 1970.