## Role played by the nanowire/nanowire junctions in the electrical properties of semiconductor percolating silicon nanowire networks

Maxime Legallais, Thi Thu Thuy Nguyen, Thibauld Cazimajou, Mireille Mouis, Tabassom Arjmand, Bassem Salem, Céline Ternon

#### ▶ To cite this version:

Maxime Legallais, Thi Thu Thuy Nguyen, Thibauld Cazimajou, Mireille Mouis, Tabassom Arjmand, et al.. Role played by the nanowire/nanowire junctions in the electrical properties of semiconductor percolating silicon nanowire networks. Journal of Applied Physics, 2020, 128 (20), pp.204501. 10.1063/5.0023322 . hal-03024377

### HAL Id: hal-03024377 https://hal.science/hal-03024377

Submitted on 25 Nov 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. the online version of record will be different from this version once it has been copyedited and typeset.

is the author's peer reviewed, accepted manuscript. However, the online version of record will be diff PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

# Journal of Applied Physics

Publishing

# Role played by the nanowire/nanowire junctions in the electrical properties of semiconductor percolating silicon nanowire networks.

Maxime Legallais<sup>1,2</sup>, Thi Thu Thuy Nguyen<sup>1</sup>, Thibauld Cazimajou<sup>2</sup>, Mireille Mouis<sup>2</sup>, Tabassom Arjmand<sup>1,2,3</sup>,

Bassem Salem<sup>3</sup>, and Céline Ternon<sup>1\*</sup>

<sup>1</sup>Univ. Grenoble Alpes, CNRS, Grenoble INP\*, LMGP, F-38000 Grenoble, France <sup>2</sup>Univ Grenoble Alpes, CNRS, Grenoble INP\*, IMEP-LaHC, F-38000 Grenoble, France <sup>3</sup>Univ Grenoble Alpes, CNRS, LTM, F-38000 Grenoble, France \*Institute of Engineering Univ. Grenoble Alpes \*Email: celine.ternon@grenoble-inp.fr

#### Abstract

In this paper, we highlight the key role played by Si nanowire/nanowire junctions in the electrical performance of field-effect transistors (FETs) based on percolating Si nanowire (SiNW) networks, also called nanonets. Using our original technological process to fabricate simultaneously numerous silicon nanonetbased transistors with variable geometry, we thoroughly investigated in this paper their electrical properties for various channel lengths, from 5 to 100µm. Particularly, we evidenced a clear transition in the FET performance, when NW/NW junctions are involved in the conduction path. On one hand, for channel length shorter than that of nanowires (NWs), the devices are called Multiple-Parallel-Channel FETs (MPC-FETs) as NWs directly bridge the channel, and they exhibit poor electrical performance in terms of OFF current, ONto-OFF ratio and subthreshold slope. On the other hand, for channel length longer than that of nanowires (NWs), the devices are called Nanonet-FETs (NN-FETs) as the current flows through percolating paths made of NWs and NW/NW junctions and the performance are considerably enhanced. By combining our structural knowledge of the material with experimental observations of electrical properties and modelling results, by relying on the percolation theory, the model for electrical transport in polycrystalline silicon and the principle of potential barrier lowering by field effect, we propose the Junction Driven Percolation mechanism. It explains the role played by the nanowire/nanowire junctions in the electrical properties of semiconductor percolating nanowire network and how they drastically enhanced the electrical properties of nanowire-based field-effect transistors despite the disorder introduced by the increasing number of nanowires. As a consequence, by controlling properly the junction interfaces and device geometry for a given NW density, thanks to NW/NW junctions, the NN-based devices are a valuable and promising alternative to improve the electrical performances of NW-based devices for future developments.

#### **Keywords**

Polycrystalline silicon nanowire network – junctions – grain boundary – potential energy barrier – field effect transistor – electrical transport – nanonets

ot Physics

Journal

plied

Publishing

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

#### I. Introduction

Field effect transistors (FETs) based on a randomly oriented nanostructure networks, called nanonets<sup>1,2</sup>, have been proposed as an interesting alternative to single nanostructure-based devices. In addition to benefiting from the semiconducting properties of each nanostructure, this network configuration gives additional features such as facility of integration<sup>3</sup>, mechanical flexibility<sup>4,5</sup>, optical transparency<sup>5,6</sup>, fault tolerance and high reproducibility<sup>1,7</sup>. Moreover, network density and device geometry (length and width) of FETs allow to tune the electrical performances which offers another considerable degree of freedom compared to single nanostructure-based devices<sup>8,9</sup>. Reported nanonet-based field effect transistors using various nanostructures such as carbon nanotubes<sup>8,9</sup> (CNTs), zinc oxide nanowires<sup>10–13</sup> (ZnO NWs) or aligned tin oxide nanowires<sup>14</sup> (SnO<sub>2</sub> NWs) have shown interesting performances in terms of ON current, ON-to-OFF ratio, subthreshold slope and hysteresis. In these particular transistors, current flows through conducting paths that involve nanostructures as well as nanostructure-to-nanostructure junctions.

The percolation theory<sup>15,16</sup> has been extensively employed to describe the behavior of these nanowire networks. In the literature, the junctions were either assumed non-resistive and then only nanowires were considered<sup>17,18</sup>; or they were assumed to play an important role in the conduction of the network<sup>17–22</sup>. Recently, Benda et al<sup>23</sup> proposed a simpler expression to model the effective network resistance using network geometry as well as physical parameters (wire resistivity, wire/wire junctions and metallic electrode/wire junctions). In addition, Vodolazskaya et al<sup>24</sup> have also taken into account the effect of tunneling trough junctions where the nanowires were made of conductive core and soft shell. To model CNTbased network field effect transistor, Alam and coworkers<sup>25–27</sup> have introduced a charge-transfer coefficient at the junctions between the tubes. Since then, this charge transfer coefficient was widely used in the literature to explain a large quantity of data arising from CNT-nanonet FET, as reviewed by Rouhi et al<sup>9</sup>. However, although this model is satisfactory at the network scale, some physical phenomena are not taken into account such as CNT surface states, gating effects in metallic CNTs or electrical behavior of tube-to-tube junction resistance. In addition, the Ohmic or Schottky nature of CNT-to-CNT contacts<sup>28</sup> is also ignored. However, knowing that a CNT network is composed of four different electrical components –semiconducting and metallic nanotubes, Ohmic and Schottky contacts- it is undoubtedly difficult to explain and model correctly the electrical behavior of this kind of nanonet FETs. Therefore, studying the electrical properties of FETs based on other semiconducting nanostructures may bring new insights in the understanding of these network-based transistors.

In our group, we have developed all the technological bricks necessary for the development of transistors based on silicon nanowire networks whose channel length can vary from a few micrometers to millimeters and whose properties are reproducible and stable even in the air<sup>3,5,29</sup>. Therefore, we are able to tune the

ot Physics

Publishing

This i

Journal

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

average number of junctions per percolation path using different channel lengths and thus to gradually increase the number of junctions between source and drain contacts, starting with devices without junctions, to some with a few units and finally some with several dozen of junctions. On one hand, by analyzing experimental results with the help of a Lambert W function-based compact model, we have reported that the variation of Si nanonet-FET electrical parameters with geometry and nanowire density can be explained by the threshold voltage dispersion of individual nanowires<sup>30</sup>. On the other hand, we have recently shown, via temperature-dependent electrical characterizations, that the low-field effective mobility of Si nanonet-FET increases with temperature<sup>31,32</sup>. A stronger dependence has been found for long channel (>> nanowire length) than short channel (shorter or equivalent to nanowire length), which has been explained by a thermally activated behavior resulting from the presence of an energy barrier at NW/NW junctions. A bimodal distribution composed of high barriers of about 40-70 meV and low barriers with a height close to 0eV had been able to provide reasonable agreement with experimental results.<sup>31</sup>

On the basis of statistical electrical characteristics, we highlight in this paper the relationship between the number of junctions along conduction paths, estimated by Monte-Carlo simulations, and the electrical characteristics of Si-NN FETs (ON current, OFF current and subthreshold slope). This new findings in combination with our previous work<sup>31,32</sup> lead us to suggest a physical model, that we call Junction Driven Percolation, to explain the role of junctions and their major impact on device properties. As a consequence, we demonstrate that by controlling properly junction interfaces and device geometry, it is possible to significantly enhance Si nanonet-FETs electrical performance.

#### II. Experimental details

#### A. Device fabrication.

Randomly oriented silicon nanowire networks, called nanonets, were integrated into field effect transistors with a bottom gate configuration trough standard optical lithography techniques<sup>3</sup>. The Vapor-Liquid-Solid<sup>33</sup> method was used for the growth of silicon nanowires (SiNWs). A dewetted gold thin film and silane were used as catalyst and precursor respectively, without intentionally introducing any doping gas. In these growth conditions, SiNWs presented a vertical growth along the <111> axis and a P-type doping<sup>34</sup> in the range of 10<sup>16</sup> cm<sup>-3</sup>. Gold catalyst was then etched with a sequence of hydrofluoric acid treatment (HF) followed by gold etchant (KI-I<sub>2</sub> based solution). After SiNW dispersion into deionized water using sonication, the amount of SiNWs in solution was controlled by absorption spectroscopy. The suspension is then diluted to reach an absorption of 0.06 at 400nm<sup>7</sup>. 10 mL of the colloidal suspension were filtered through a nitrocellulose membrane in order to self-assemble the network on the filter whose diameter is 5cm. Finally, a piece of filter is cut and the nanonet was transferred, by filter dissolution, onto 1×1 cm<sup>2</sup> coupons of heavily doped silicon capped by a 200-nm thick silicon nitride layer. The detailed process can be found in Serre et al<sup>7</sup>. As a result of the process, a homogeneous nanonet of about 7×7 mm<sup>2</sup> with a physical density of 0.23 NWs.µm<sup>-2</sup> is present at the surface of the substrate. In order to stabilize the electrical properties in air, SiNW/SiNW of Physics

Journal

plied

Publishing

This i

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

junctions were sintered at low temperature via our previously reported process<sup>29</sup>. As shown in Ternon et al<sup>29</sup>, in the absence of oxide shell around SiNWs and for diameter in the tens of nanometers, local atomic diffusion occurs at temperature as low as 400°C resulting in the formation of necks at the NW/NW junctions. This phenomenon is called "sintering". As a consequence of this sintering, the NN, which was an assembly of discrete NWs after assembly and transfer on the substrate, becomes a polycrystalline material in which the NWs remain monocrystalline and are the grains of the polycrystalline material while the NW/NW junctions are the grain boundaries. To quickly resume the process, the native silicon dioxide was first removed by HF treatment and a 1-minute annealing was immediately performed in nitrogen at 400°C to sinter the NW/NW junctions. Due to air break after annealing, another HF treatment was realized before alumina passivation via the atomic layer deposition method in a Fiji F200 Cambridge Nanotech apparatus. An 8-nm thick layer requiring 80 cycles was deposited at 250°C using trimethylaluminum and water as precursors. This passivation layer significantly enhances the NN-FET electrical performance by improving the Si/alumina interface in comparison with Si/native oxide interface<sup>35</sup>. Electrical contacts were defined into standard reversal photoresist using Süss Microtec MJB3 apparatus and, then, alumina coating in the photoresist openings was removed with HF treatment. Right after, 100 nm of nickel followed by 50 nm of gold were ebeam evaporated. The source and drain contacts were revealed through a lift-off method. Finally, the samples were annealed at 400°C in nitrogen in order to enhance the electrical contact between the metals and SiNWs via silicidation mechanism<sup>3</sup>. Although this thermal process is identical to the sintering process, it will have no impact on the junctions. Indeed, during the silicidation, the NN is coated with alumina oxide which prevents surface diffusion of the silicon atoms and thus makes low-temperature sintering impossible<sup>29</sup>.

#### B. Morphological characterizations.

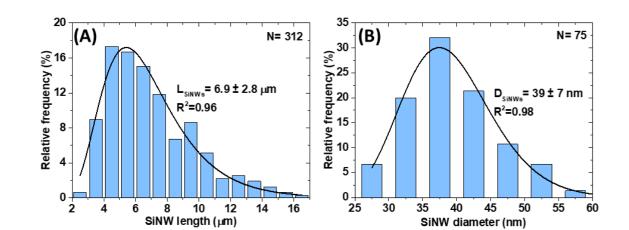

The morphological characterizations of Si nanonets and transistors were performed by scanning electron microscopy (SEM) with a Hitachi S4100. The analysis of SEM images was realized with the ImageJ software. Statistics relative to the length and width of NWs (Figure 1) were deduced from the analysis of dozens of SEM images: the length of 312 NWs and the diameter of 75 NWs randomly chosen were measured and compiled in the distribution. As fully detailed in Serre et al. <sup>7</sup>, the SiNW density in nanonets was assessed by several SEM image analysis from the coverage area,  $\tau$ , defined as the ratio between the surface covered by NWs and the total surface of the sample. We have shown that this coverage area is proportional to the volume of filtered solution,  $V_{filtered}$ , following an equation dependent on the population of nanowires, here :  $\tau = 0.63 \times V_{filtered}$ . Then the physical NW density can be estimated by calculating the ratio between the coverage area and the surface covered by each nanowire, using average diameter,  $d_{NW}$ , and length,  $L_{NW}$ , of SiNWs (Figure 1):  $d = \frac{\tau}{d_{NW}L_{NW}}$ . For the NWs used in this study, a filtered volume of 10 mL gives a homogenous density of 0.23 NWs.µm<sup>-2</sup>.

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

Figure 1: Statistics relative to (A) the length ( $L_{SiNWs}$ ) and (B) the diameter ( $D_{SiNWs}$ ) of SiNWs in nanonet. Both parameters were fitted with a log-normal function. 'N' indicates the number of measured nanowires.

In the frame of the percolation theory, the critical percolation density,  $d_c$ , defined as the density at which there is a probability of one half to have at least one percolation path connecting the two electrodes, is an important parameter. According to Li and Zhang<sup>36</sup>, for a given NW length,  $\ell$  and no length dispersion, the critical percolation density can be calculated as:  $d_c = \frac{5.637}{\ell^2}$ . Taking into account the average NW length,  $L_{NW}$ , the critical percolation density for electrical conduction in our case would be 0.12 NWs.µm<sup>-2</sup>. According to this value, the nanonets studied in this work are in the percolation regime which extend from the critical density (0.12 NWs. $\mu$ m<sup>-2</sup>) to 5 to 7 times its value (0.6 to 0.84 NWs. $\mu$ m<sup>-2</sup>)<sup>26</sup>. However, one has to take into account two important considerations. First of all, contrary to the modelled case, the experimental population of nanowires is widely dispersed (Figure 1), which has a strong impact on the percolation threshold<sup>37</sup>. Secondly, there may be a difference between the physical density corresponding to the nanowires actually present on the surface, as described above, and the electrical density corresponding to the nanowires that actually play an electrical role within the network. Indeed, in the case of semiconductor nanowires, we have noticed through the study of percolation that the density was often overestimated due to the fact that some nanowires are too resistive to participate in conduction. As a consequence, for a given physical density, to assess the conduction regime, percolating or ohmic, we rely on the finite size scale relationship according to which the conductance of the nanonet is inversely proportional to the length of the channel at the exponent m, called scaling exponent<sup>16,25–27</sup>. For high densities, m = 1 and the material behaves like a thin film. When m > 1, the network is in the percolating regime.

#### C. Electrical characterizations.

Electrical characterizations were carried out with a Karl Süss probe station controlled by a HP4155A parameter analyzer in ambient dark environment at room temperature. Transfer characteristics were recorded from positive to negative gate voltages with a constant drain voltage of -4V or -1V depending on experiments. As previously reported for bare-SiNWs, transistors displayed p-type operation and were operated from the depletion regime in the OFF state to the accumulation regime in the ON state<sup>3</sup>.

#### D. Monte-Carlo Simulations.

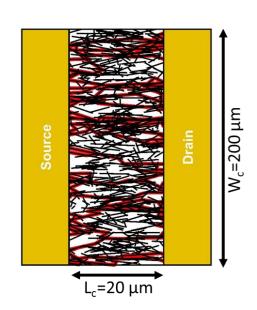

Monte-Carlo simulations were carried out on Matlab R2016a to gain information about the percolation paths of one given nanonet. Silicon nanowires were considered as sticks<sup>20</sup> and were uniformly oriented and generated within an area defined by the channel length ( $L_c$ ) and width ( $W_c$ ). The experimental transistor geometry and nanonet morphology were used. Channel width was set at 200 µm while channel length, defined as the distance between source and drain contacts, varied from 5 µm to 100 µm. Sticks were

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

generated with random position and orientation and their length distribution followed a Gaussian law. As is the case experimentally, the NW length mean value is 6.9  $\mu$ m and the standard deviation 2.8  $\mu$ m and the stick density was set at 0.23 sticks. $\mu$ m<sup>-2</sup>. Right after, the location of all stick/stick and stick/contact intersections was calculated through mathematical matrix technique<sup>38</sup>. Each stick in contact with one or other of the metal electrodes is considered to be the starting point of a potential percolation path. Then, from the coordinates of all intersections, percolating paths from the source to the drain and vice-versa are determined on the basis of Dijkstra's algorithm, which is a usual technique to find out the shortest path from one point to another<sup>39</sup>. To stick to our experimental assumption that NW/NW junctions are the driving mechanism of the conduction in the network, this algorithm was modified in order to first minimize the number of stick/stick intersections and then minimize the distance traveled (See Supporting Information S1). Thus, for each stick directly contacted to either source or drain, all the possible percolating paths that reach the opposite contact were first determined while minimizing the number of stick/stick intersections. Out of all these possibilities, the shortest one was then extracted (Figure S1). Figure 2 gives an example of a randomly generated nanonet (one iteration) for which all the percolation paths, as previously defined, are highlighted in bold red. For each iteration corresponding to a random realization, the main calculated output parameters were the number of percolating paths,  $N_{pp}$ , and for each path k ( $k \in [1, N_{pp}]$ ), the number of stick/stick intersections,  $N_{ssi}^k$  and the length of the path,  $L_{pp}^k$ . For short channel length (smaller than the NW length), the number of directly bridging sticks, N<sub>bs</sub>, was also determined. For each length of channel, the random realization was carried out a number of times, called number of iteration, N<sub>iter</sub> and ranging from 10 to 100 in order to increase the accuracy of the values found (Table 1). For each length, on one hand, the average number of percolating path,  $\langle N_{pp} \rangle$  or the average number of bridging stick,  $\langle N_{bs} \rangle$  is calculated on the number of iteration ( $N_{iter} \in [10, 100]$ , Table 1). On the other hand, the average junction number per path,  $\langle N_i \rangle$  and the average length of path,  $\langle L_p \rangle$  are calculated by averaging over the total number of paths,  $N_{pp}^{total}$ , i.e.  $N_{pp}^{total} = \sum_{k=1}^{N_{iter}} N_{pp}^k = N_{iter} \times \langle N_{pp} \rangle$  ( $N_{pp}^{total} \in [1\ 895, 17\ 224]$ , Table 1). For each geometry, the number of iterations has been chosen so that, for the average junction number, the standard deviation is less than 4% of the mean value.

Figure 2 : Highlighting of the percolation paths (in bold red) for a stick density of 0.15 sticks. $\mu$ m<sup>-2</sup>. For reasons of clarity, a density lower than 0.23 sticks. $\mu$ m<sup>-2</sup> has been considered and different scales have been chosen for the ordinate and abscissa, giving the impression of preferential orientation of the sticks. The length of the system is 20  $\mu$ m for a width of 200  $\mu$ m.

Table 1: Number of iterations and outputs for the Monte Carlo simulations of the transistor as a function of channel length. The density was 0.23 sticks. $\mu$ m<sup>-2</sup> and the channel width was 200  $\mu$ m. For each geometry, the number of iteration has been chosen so that, for the average junction number, the standard deviation is less than 4% of the mean value. NA stand for Not Applicable.

| Channel length (µm) | 5 | 10 | 15 | 20 | 30 | 50 | 100 |

|---------------------|---|----|----|----|----|----|-----|

|---------------------|---|----|----|----|----|----|-----|

This i

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

| Iteration number ( $N_{iter}$ )                                                                                                   | 100      | 100     | 100      | 50       | 50       | 50       | 10        |

|-----------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------|----------|----------|----------|-----------|

| Number of direct bridging NWs, $\langle N_{bs}  angle$                                                                            | 36.7±4.8 | 2.3±1.5 | 0        | 0        | 0        | 0        | 0         |

| Total number of percolation paths, $N_{pp}^{total} = \sum_{k=1}^{N_{iter}} N_{pp}^{k}$ $= N_{iter} \times \langle N_{pp} \rangle$ | NA       | NA      | 17224    | 8879     | 9164     | 9509     | 1895      |

| Average junction number per path, $\langle N_j  angle$                                                                            | NA       | NA      | 3.8±0.1  | 5.2±0.2  | 7.8±0.2  | 12.9±0.2 | 25.9±0.3  |

| Average length of percolation path, $\langle L_p  angle$ (µm)                                                                     | NA       | NA      | 19.2±0.4 | 25.5±0.4 | 37.8±0.5 | 62.2±0.5 | 123.7±0.6 |

#### E. Finite element modelling.

In order to illustrate the formation of the energy barrier at NW/NW junctions and their dependence with substrate bias (acting as gate bias), we performed simple simulations of a 1D gate/gate dielectric/NW/NW stack which represents the simplest model of one NW/NW junction in the nanonet. This was done by solving Poisson equation using the FlexPDE Finite Element Model (FEM) builder for partial differential equations solution. We considered Boltzmann statistics for the holes. All interfaces were assumed ideal, except for the interface between the two nanowires where a uniform density of interface traps in the bandgap, N<sub>it</sub>, was assumed. The surface charge at this interface was calculated as:

$$Q_{s} = q \cdot N_{it} \cdot (\varphi_{s} - \varphi_{F})$$

(1)

where q is the elementary charge,  $\phi_F$  is the difference between Fermi level and intrinsic level in the neutral bulk (function of P-type doping level), and  $\phi_s$  is the surface potential resulting from surface band bending, calculated from the difference between the energy of the intrinsic level at the surface and its value in the neutral bulk (local potential). This charge was accounted for as a discontinuity in the normal component of the electric displacement at the interface. Reader can refer to Supporting Information for details.

#### III. Results and discussion

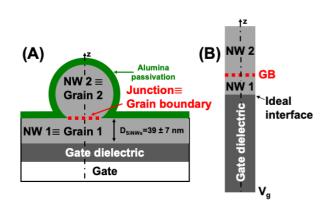

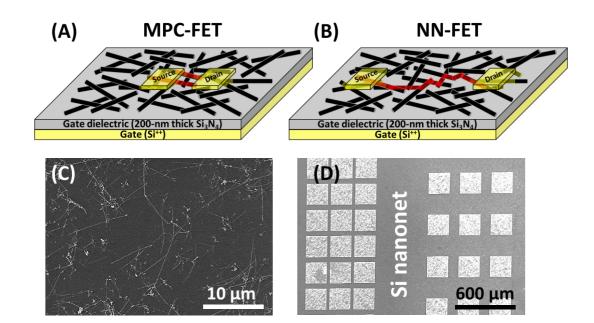

As detailed in the previous section, the field effect transistors (FETs) manufactured for this work necessitate only standard and low temperature (<400°C) microelectronic technologies. The integration process consists of six main stages: (i) nanowire synthesis; (ii) nanonet self-assembly; (iii) nanonet transfer on substrate; (iv) NW/NW junction sintering; (v) passivation of the nanonet with alumina; (vi) source and drain contact definition and silicidation. The FETs were designed in the bottom gate configuration. The length of the transistor channel was defined by the distance between source and drain and varied, for this study, between 5 and 100  $\mu$ m, while the channel width was set at 200  $\mu$ m. Taking into account SiNW length values, which ranged from 2  $\mu$ m to 16  $\mu$ m (Figure 1(A)), with respect to channel length, two kinds of transistors were obtained. (i) When the inter-electrode distance was smaller than maximum nanowire length, the transistor channel consisted of parallel nanowires and the device was called Multiple-Parallel-Channel FET (MPC-FET) (Figure 3(A)). (ii) For an inter-electrode distance larger than nanowire length, the channel consists of several percolation paths. Each path was made of a series of SiNWs separated by SiNW/SiNW junctions whose number depends on channel length. This type of device was named nanonet-FET (NN-FET) (Figure 3(B)).

**MPC-** and **NN-FET Morphology and Geometry**. In Figure 3, scanning electron microscopy images illustrate a typical silicon nanowire network right after transfer (Figure 3(C)) and after its further integration into field effect transistors (Figure 3(D)). In nanonets, the mean length and diameter of the silicon nanowires (SiNWs) are  $L_{SiNWs}$ =6.9 µm and  $D_{SiNWs}$ =39 nm, with a standard deviation of 2.8 µm and 7 nm, respectively, as shown in Figure 1. All SiNWs are single crystals with <111> growth direction<sup>29</sup> and are laid randomly on the substrate so that the <111> direction is parallel to the substrate surface. As a result, nanowires are randomly oriented relative to each other. Thus, during the sintering step, which is necessary to stabilize the electrical properties of the network<sup>29</sup>, there is a crystallographic mismatch at the NW/NW junctions which results in the formation of grain boundaries<sup>29</sup>. Therefore, a Si nanonet is a polycrystalline silicon network composed of grains –the monocrystalline silicon nanowires– separated by grain boundaries –the SiNW/SiNW junctions. All the nanonets studied in this work exhibit a constant density of 0.23 NWs.µm<sup>-2</sup>.

Figure 3: (A-B) Schemes of the two possible transistor configurations based on Si nanonet: (A) Multiple-Parallel-Channel FET (MPC-FET) and (B) Nanonet-FET (NN-FET). For MPC-FET, current can flow through SiNWs directly bridging the source and the drain whereas, for NN-FETs, the current must flow via percolating paths that involve SiNWs and SiNW/SiNW junctions. The channel length ( $L_c$ ), corresponding to the Source-Drain distance, varies from 5  $\mu$ m to 100  $\mu$ m whereas the channel width ( $W_c$ ) is fixed at 200  $\mu$ m. (C) SEM image of a typical Si nanonet elaborated with 10 mL of colloidal SiNW suspension corresponding to a density of 0.23 NWs. $\mu$ m<sup>-2</sup>. (D) SEM top-view of Si nanonet field effect transistor after processing. The 200  $\mu$ m x 200  $\mu$ m squares correspond to the Source/Drain contact pads.

If we consider the nanowire length dispersion, it is possible to state that a channel length of 5  $\mu$ m is associated with an MPC-FET. Then, for 14% of the NW population (Figure 1(A)), NW length exceeds 10  $\mu$ m, so that the devices with 10 $\mu$ m channel lengths will have a high probability of being MPC-FETs but with a reduced number of parallel nanowires. Finally, all the devices with a channel longer than 15  $\mu$ m will be NN-FETs because less than 1% of the NWs are longer than 15  $\mu$ m (Figure 1(A)).

**Percolating Channel Modeling**. In order to define more precisely the nature and dominant composition of the transistor channels, Monte-Carlo simulations were carried out according to the principle of stick percolation<sup>15,16,20</sup>. The experimental characteristics of our devices were used to set up the simulations: nanowire length distribution, nanonet density and transistor geometry (fixed width, variable length). For each Monte Carlo-generated nanonet, when they exist, the position of each NW/NW junction was

ot Physics

Journal

plied

Publishing

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

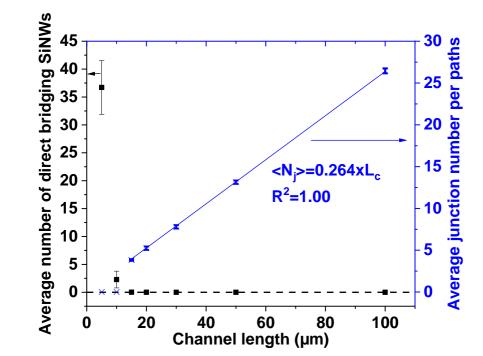

determined. Likewise, all the percolation paths connecting the source to the drain were defined. Each of these paths was optimized on the basis of two criteria: minimizing first the number of junctions, then the length of the path as described in the experimental section. Finally, for each randomly simulated nanonet, we determined the number of nanowires directly bridging source and drain and the number of junctions per path, which was determined by first minimizing the number of stick/stick intersections and then minimizing the distance traveled. The operation was repeated a sufficient number of times so that the standard deviation on the number of junctions per percolation path and the average number of nanowires bridging source and drain are presented in Figure 4 as a function of channel length. As expected, the transistors are MPC-FETs when channel length is 5 and 10  $\mu$ m with an average of 37 and 2 NWs directly bridging the two electrodes, respectively. Above 15  $\mu$ m, the transistors are NN-FETs without bridging nanowires and with a number of junctions per path and increasing up to 26 for a 100  $\mu$ m long channel. In addition, beyond 15  $\mu$ m, the number of junctions per path exhibits a good linear correlation with channel length despite the large standard deviation of SiNW length (2.8  $\mu$ m).

Figure 4: Average number of direct bridging SiNWs (left axis) and average junction number per percolating paths ( $\langle N_j \rangle$ , right axis) as a function of the channel length ( $L_c$ ) using Monte-Carlo simulations. For all of these simulations, the experimental parameters of the transistor geometry and nanonet morphology were chosen. The channel width was set at 200 µm while the channel length varies from 5 µm to 100 µm. For the nanonet morphology, nanowires are considered as sticks with a length of 6.9 ± 2.8 µm and SiNW density corresponds to 23x10<sup>6</sup> SiNWs.cm<sup>-2</sup>. Beyond 15 µm,  $\langle N_j \rangle$  exhibits a good linear correlation with the channel length despite the high standard deviation of SiNW length (2.8 µm).

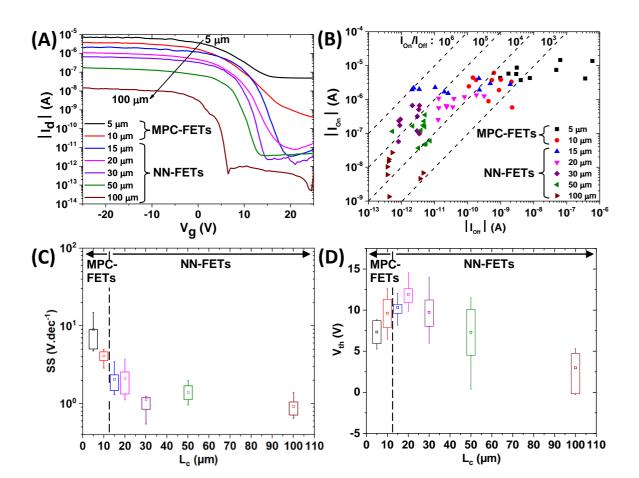

**MPC-FET and NN-FET Electrical Behavior**. Figure 5(A) shows the typical evolution of the transfer characteristics when channel length varies between 5 and 100  $\mu$ m. In addition to an expected decrease of ON current from about 8  $\mu$ A down to 20 nA, a surprising and significant diminution of the subthreshold slope and of the OFF current were observed when increasing channel length. To accurately determine the impact of channel length on electrical properties, ON current (defined as  $I_d$  at  $V_g = -25 V$ ,  $V_d = -4 V$ ), OFF current (extracted in the OFF state), subthreshold slope and threshold voltage (extracted by extrapolation in linear region in linear scale) were carefully extracted for approximately seventy transistors. In Figure 5(B), where each characterized transistor was placed in the  $I_{On}/I_{Off}$  plane, an interesting trend is observed. First, when channel length varies from 5  $\mu$ m to 20  $\mu$ m, the OFF current decreases very strongly over five orders of magnitude while the ON current decreases slightly, which results in a drastic increase in the ON-to-OFF ratio. On the contrary, for channels longer than 30  $\mu$ m, the OFF current remains stable at values as low as 10<sup>-13</sup>-10<sup>-12</sup> A while the ON current begins to decrease rapidly. Therefore, in terms of ON-to-OFF ratio, an optimum emerges for a channel length of 30  $\mu$ m, with outstanding values exceeding 10<sup>5</sup>. Similarly from Figure 5(C), a clear improvement in the subthreshold slope is observed when  $L_c$  varies from 5  $\mu$ m to 20  $\mu$ m down to about

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

1 V.dec<sup>-1</sup> for devices longer than 30  $\mu$ m. Finally, the threshold voltage increases when  $L_c$  raises from 5 to 20  $\mu$ m and then it monotonously decreases when  $L_c$  is longer than 20 $\mu$ m (Figure 5(D)). It should be noticed that the values of  $V_{th}$  for devices with  $L_c = 5 - 10 \,\mu$ m should be used with caution as its extraction is highly imprecise due to their weak current modulation as well as their high subthreshold slope. According to these experimental results, channel length drastically impacts the electrical characteristics of FETs and the best performance, in terms of ON-to-OFF ratio and subthreshold slope, were obtained for 30  $\mu$ m-long channel FET for the given NW density and length.

Figure 5: Study of transistor electrical properties for various channel lengths. (A) Typical transfer characteristics from 5 to 100  $\mu$ m at  $V_d = -4 V$ . (B) ON current ( $I_{On}$ ) as a function of OFF current ( $I_{Off}$ ). The ON current is defined as  $I_d$  at  $V_g = -25 V$ ,  $V_d = -4 V$ . (C) subthreshold slope (SS) and (D) threshold voltage ( $V_{th}$ ) for various channel lengths extracted for about seventy transistors. For (B), the ON-to-OFF ratio ( $I_{On}/I_{Off}$ ) is indicated by the dashed lines.

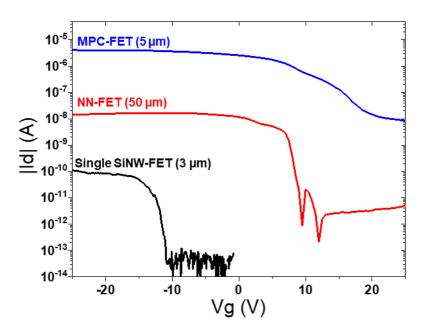

According to these results, the MPC-FETs performance are worse than that of NN-FETs. To better understand such a degradation, single SiNW-FETs have been fabricated for comparison with MPC-FETs and NN-FETs, as displayed in Figure 6. One can notice that the performance of the single NW-FET (Figure 6) are good with ON-to-OFF ratio about 10<sup>4</sup>, an OFF current in 10<sup>-14</sup> A range and a subthreshold slope of about 210mV.dec<sup>-1</sup>. As a consequence, the high OFF current level and the bad subthreshold slope in the MPC-FET (Figure 6) cannot be directly attributed to the individual SiNW properties. Moreover, according to the modelling, the number of direct bridging SiNWs in MPC-FET for the experimental density of 0.23 NWs.μm<sup>-2</sup> is about 37 (Figure 4). Then, one has to keep in mind that the NW diameter dispersion is wide (Figure 1) and that it implies a significant variation in nanowire threshold voltage<sup>29</sup>. As a consequence, the MPC-FETs properties are the results of the superposition of almost 40 NW-FETs in parallel, which contributes to explain the higher lon value for MPC-FET than for single NW-FET, but also the subthreshold slope degradation, as detailed in the last part of the paper. By comparison, the NN-FET performance (Figure 6) with a channel length of 50μm are as interesting as that of the single NW-FET with a channel length of 3μm.

# Figure 6 : Typical transfer characteristic at $V_d$ =-1V for Single SiNW-FET with L<sub>c</sub>= 3µm (black), MPC-FET with L<sub>c</sub>= 5µm (blue), NN-FET with L<sub>c</sub>=50µm (red). Color on-line.

In the literature, similar trends of the ON-to-OFF ratio were observed for field effect transistors made of carbon nanotube (CNTs) networks<sup>40,41</sup> when the channel length decreases. According to these authors, this trend is linked to the systematic presence of metallic CNTs among the semiconducting CNTs. Indeed, for a given ratio of metallic CNT (typically <1/3), the probability to form metallic conducting paths increases when channel length decreases. As a result, a drastic augmentation in the OFF current occurs and therefore a decrease in the ON-to-OFF ratio, just as we observe with our experimental results. Nevertheless, none of the

ot Physics

Journal

plied

Publishing

This i

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

SiNWs involved in the nanonet studied here is metallic as their non-intentionally P-type doping level<sup>34</sup>, in the range of 10<sup>16</sup> at.cm<sup>-3</sup>, is far from the degenerated range<sup>42</sup>. As a consequence, the hypothesis proposed for the CNT case is not applicable to explain the observed degradation when the channel length decreases and other phenomena have to be taken into account. Particularly, thorough studies of silver nanowire<sup>22</sup> and CNT<sup>8,28,43</sup> networks showed that, in case of metallic nanowire network, junctions between nanostructures play an essential role in the network conduction. Indeed, even in low proportion, high resistive junctions may limit the ultimate conduction in the overall network.

As far as we know, no studies of the electrical properties of the silicon NW/NW junctions have been specifically reported in the literature. However, according to our previous reported work<sup>29</sup>, when NW/NW sintering occurs at 400°C for 1 minute, as done in this work, a neck appears where the two NWs are touching each other and the neck size at the junction is about 10% of the SiNW diameter. Thus, at each junction, the charge carriers cross an area 100 times smaller in section than that of the nanowire. The resistance being inversely proportional to the section, the lineic junction resistance will be thereby at least two orders of magnitude higher than SiNW lineic resistance itself. Moreover, thanks to the HRTEM observations<sup>28</sup>, we evidenced the presence of crystallographic defects at the junctions, essentially dislocations, which are expected to feature a large density of traps, leading to the formation of energy barriers along the conduction paths. In addition to these purely material considerations, we have recently shown, via temperature electrical characterizations, that the low field effective mobility of Si nanonet-FET increases with the temperature<sup>31,32</sup>. It has been found that the results can be explained by the presence of energy barriers at NW/NW junctions. Moreover, the observed trends have suggested that these energy barriers might feature a bimodal distribution, with high barriers of about 40-70 meV and low barriers with a height close to 0eV. As a consequence, the role of junctions have to be explored in connection with the studied regime of the FETs, ON state, commutation state and OFF-state.

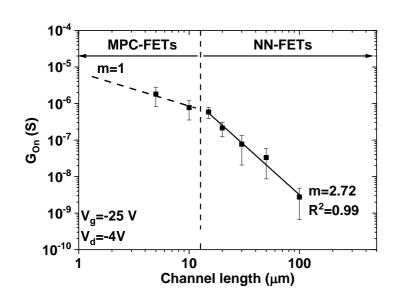

**Experimental investigation of junction contribution in the ON state.** The behavior of one particular junction can be investigated with the four-probe technique<sup>22</sup>. However, such experimental setup gives information about one junction only when hundreds of junctions can be involved in a NN-based FET. The strategy we developed here was to gradually increase the length of the channel FET in the range 5-100 µm so that more and more junctions were involved in conducting paths. According to the work of Alam *et al*<sup>25-27</sup>, the study of the network conductance in the ON state gives information about the electrical properties of junctions with respect to that of nanostructures. Such conductance ( $G_{On}$ ) is defined as the ratio between the drain current in the ON state (Figure 5(B)) and the drain voltage ( $V_d = -4 V$ ). For the current extractions in the ON state, a gate voltage of -25 V was chosen as it is far from the typical threshold voltage (0-12V) of our devices (Figure 5(D)). The conductance, depicted in Figure 7 as a function of channel length, exhibits a clear deviation to the main trend when channel length is shorter than the NW length ( $L_c \leq 10 \mu m$ ). According to the Monte-Carlo simulations, which account for the experimental distribution in SiNW length and for FET geometry (Figure 4),

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

Publishing

This i

the deviation to the trend corresponds to the involvement of NWs directly bridging the two metallic contacts. Indeed from 5  $\mu$ m to 10  $\mu$ m, about 37 to 2 NWs directly bridge the electrodes (MPC-FET) whereas, beyond 15  $\mu$ m long channel, charge carriers have to cross at least one junction to flow from source to drain (NN-FET).

Figure 7: This figure displays the evolution of the ON conductance, ratio between the ON current at gate voltage of - 25V and the drain voltage (-4V), with the channel length. For MPC-FETs (5 and 10 $\mu$ m) the standard scaling low materialized by dashed line is reported and applies quite well: the conductance is inversely proportional to the channel length. For NN-FETs, as predicted by the percolation theory whereby the conductance is inversely proportional to the channel length at the scaling exponent 'm', the conductance can be well fitted with linear equation beyond 15  $\mu$ m, giving a conductance exponent of 2.72 and suggesting that the electrical density is closed to the percolation threshold.

According to the percolation theory<sup>16,25–27</sup>, for NN-FETs, the network conductance can be described by the finite size scale relationship:  $G_{On} \propto \frac{1}{L_{SiNWs}} \left(\frac{L_{SiNWs}}{L_c}\right)^m$ .  $L_{SiNWs}$  represents the nanowire length and m is a percolating parameter, called scaling exponent (m > 1), which depends on stick density. For high densities, m = 1 and the material behaves like a thin film. When m > 1, the network is in the percolating regime. In this frame and according to simulations carried out by Pimparkar and Alam<sup>27</sup> for CNT nanonet-based FETs, the scaling law applies with m = 1 for MPC-FETs and with  $m \ge 1$  for NN-FETs. Moreover, in systems, where the dimensionless charge-transfer coefficient between tubes<sup>27</sup> ( $R_{NW}/R_{junctions}$ ) is close to 1, no discontinuity is observed at the transition between short-channel and long-channel devices, whereas in case of low charge transfer coefficient ( $< 10^{-1}$ ), an important discontinuity is noticed. Obviously, the absence of discontinuity in Figure 7 suggests that in the ON-state of the NN-FETs the NW/NW junctions are quite good and allow good conduction. For MPC-FETs (channel length  $\leq 10\mu$ m), due to the low number of experimental points, no fit is applied but the standard scaling low according to which the conductance is inversely proportional to the channel length is reported and is in quite good accordance with the experimental results. In contrast, for NN-FETs (channel length >  $10\mu$ m), the material is clearly in the percolating regime with a scaling exponent m equal to 2.72. As a conclusion, we have here the confirmation that, in the percolation regime, once the NN-FETs are in the ON-state, the NW/NW junctions are not a limiting mechanism. The step forward, described in the following, is then to determine the role played by the presence of energy barriers at NW/NW junctions and particularly how they impact the subthreshold slope and the OFF current. At least and as developed below, an important element to understand is whether the junctions are responsible for the better performance of long channel devices (NN-FET) compared to short channel devices (MPC-FET) (Figure 5).

**Si nanonet as Si polycrystalline thin film.** Because of the sintering step and as shown by our previous microstructural study<sup>29</sup>, the Si nanonet is in fact a polycrystalline silicon network composed of grains – monocrystalline SiNWs – and grain boundaries – SiNW/SiNW junctions. Therefore, we propose to adapt the

ot Physics

Journal

plied

Publishing

This i

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

well-known barrier model developed for the electrical transport in polycrystalline silicon<sup>44,45</sup> to the percolating SiNW network. According to Seto's model<sup>44</sup>, the presence of dangling bonds located at the grain boundaries results in the formation of energy levels in the bandgap, which are capable of trapping and detrapping free carriers. The associated grain boundary charge builds an energy barrier which prevents the injection of low energy carriers from one grain to the other. In addition, for poly-Si field-effect-transistor, it has been shown that<sup>46,47</sup>: (*i*) the grain boundary (GB) potential barrier height is modified by the gate bias; (*ii*) the GB potential barrier helps in the suppression of off-current and in the improvement of subthreshold behavior. More recently, with the same argues, Liu et al<sup>48</sup> demonstrated that the energetic barriers present at the grain boundaries of printed polycrystalline ZnO nanowires suppress the OFF current in the devices. Keeping in mind that the spatial arrangement of gate, grains and GBs in a nanonet is not the same as in a poly-Si film or in polycrystalline ZnO NWs, and considering the grain boundary height barrier modification by field effect, we propose in the following a physical model to understand the role of the NW/NW junctions in the electrical behavior of Si NN-FETs.

**Physical model for Si NN-FET.** A full modelling of hole transport through a nanonet and of the role of NW/NW junctions would require quite involved simulation approaches which are beyond the scope of this paper. However, some rough trends can be drawn based on simple considerations. In the following, we will discuss a very simple model for a NW/NW junction in the nanonet, which corresponds to the crossover of two nanowires with substrate voltage control (Figure 8(A)). As for polycrystalline silicon<sup>44</sup>, NW/NW junctions are expected to feature a large density of traps, leading to the formation of energy barriers. With the aim of evidencing rough trends, we used FlexPDE to solve the 1D Poisson equation under the assumption of a uniform density of states N<sub>it</sub> at the grain boundary. The modelled structure was a typical MIS stack composed of bottom substrate contact, gate dielectric (200-nm thick silicon nitride) and two stacked nanowires separated by a grain boundary (Figure 8(B)). All other interfaces were considered as ideal. The reference potential was taken at flat band ( $V_{fb}$ ). The diameter of the bottom NW (NW1) was taken equal to the mean experimental value (40 nm) while the diameter of the top nanowire (NW2) was set at 100 nm to reach equilibrium. All details about the equations solved and their limiting conditions are given in Supporting Information S2.

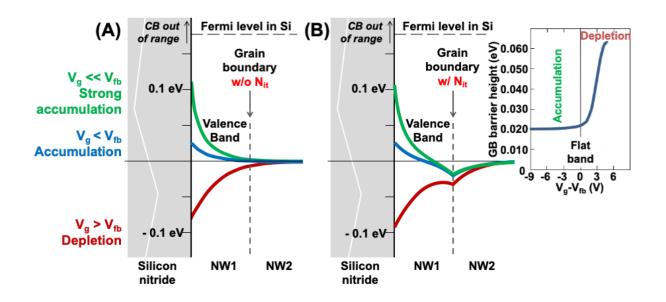

Figure 9 depicts the valence band diagram after 1D Poisson equation resolution (A) without and (B) with a GB interface state density of  $5 \times 10^{11} cm^{-2}$ .  $eV^{-1}$  for three different values of gate voltages ( $V_a$ ) which were

Figure 8: (A) Schematic representation of the crossover between two nanowires, one sectioned along its length (NW1) and the other one across (NW2). Substrate bias acts as a gate bias in this bottom-gate FET configuration. (B) Simplified 1D scheme used to calculate charge and potential distribution at the centerline of NWs crossover. The simulated stack consisted of 200nm Si<sub>3</sub>N<sub>4</sub> (gate dielectric), 40nm Si (NW1), 100nm Si (NW2). A density of interface states  $N_{it}$  was assumed at the grain boundary between NW1 and NW2. All other interfaces were assumed ideal. Gate voltage (Vg) values are calculated with reference to flat band conditions.

ot Physics

Journal ( Applied F

Publishing

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

taken in depletion regime ( $V_g$ - $V_{fb}$ =1.73V), accumulation regime ( $V_g$ - $V_{fb}$ =-1.03V) and strong accumulation regime ( $V_g$ - $V_{fb}$ =-9,31V). In the absence of interface states (Figure 9(A)), the GB is ideal and the two NWs act as a single semiconducting region. A classical upward (downward) band bending is observed in accumulation (depletion) regime. With interface states (Figure 9(B)), a potential energy barrier builds up at the GB and the influence of gate voltage on the top nanowire NW2 is mostly screened by interface charge modulation. Barrier height was calculated as the difference between the position of the valence band at the GB which were calculated in the presence and in the absence of interface states. As shown in the inset of Figure 9(B), this barrier height depended on gate voltage, with smaller values in accumulation than in depletion.

Figure 9(B) shows that the crossover between two nanowires is expected to add a potential barrier along current paths in any case, due to the weaker control of the gate on the top nanowire. However, even if hole concentration is smaller at the level of NW2, both nanowires operate in the same regime. The presence of GB traps would add an interesting feature as it builds a depleted region across the current path. Conduction is then primarily limited by the junctions, so that we may define a concept of "Junction Driven Percolation" to describe this system, with a threshold voltage at junctions ( $V_{th}^{j}$ ) smaller than that of nanowires ( $V_{th}^{NW}$ ). In accumulation, ON current should be relatively unaffected by GB traps as long as the barrier height added by GB traps is smaller than thermal voltage<sup>46,47</sup>. In contrast, the larger barrier in depletion would be in favor of reduced OFF current and steeper subthreshold slope.

Figure 9: Valence band diagrams obtained after the resolution of 1D Poisson equation (A) without and (B) with a GB interface state density ( $N_{it}$ ) of  $5 \times 10^{11} cm^{-2} eV^{-1}$  for three different conditions: depletion ( $V_g$ - $V_{fb}$ =1.73V), accumulation ( $V_g$ - $V_{fb}$ =-1.03V) and strong accumulation ( $V_g$ - $V_{fb}$ =-9,31V). Values of energies on the y-axis are provided with the usual sign convention (positive energies upwards for electrons). Holes energies have the opposite sign (positive energies downwards for holes). The inset for (B) represents the evolution of the GB barrier height as a function of  $V_g$ - $V_{fb}$ , hole convention is used.

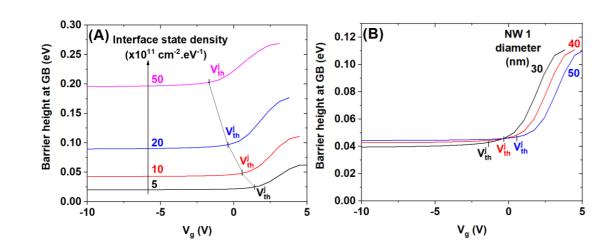

For a better understanding of the GB role, we investigated in Figure 10 the influence of (A) interface state density and (B) NW1 diameter on the junction threshold voltage  $V_{th}^{j}$ .  $V_{th}^{j}$  is defined as the voltage below which gate control of NW2 becomes screened by GB traps and potential barrier at the GB reaches its minimum value. On one hand, as expected, in Figure 10(A), the increase in interface state density at GB translates into an elevation of the potential barrier height so that percolation path opening occurs at lower gate voltage impacting the threshold voltage and subthreshold behavior of the NNFET. In our previous experimental work, from temperature measurement of low field effective mobility<sup>31,32</sup>, we have reported barrier height values in the range of  $0.040 - 0.070 \ eV$ , which, according to the present simulation (Figure 10(A)), might correspond to an interface state density at the NW/NW junctions in the range  $10^{12} - 2 \times 10^{12} \ cm^{-2} \ eV^{-1}$ , although this comparison should be taken with much care considering the rough assumptions laying behind the 1D simulation of barrier height done here and the fact that the bimodal distribution of experimental barrier

heights proposed in [32] was only the simplest assumption that was able to fit experimental dependence of I-V characteristics with temperature. Nonetheless 1D simulation can provide information about trends. The impact of NW diameter on the barrier height is shown on Figure 10(B). The increase of the NW1 diameter shifts the curves, and the junction threshold voltage  $V_{th}^{j}$ , towards positive values while the barrier in accumulation regime remains almost constant. As a conclusion, on the basis of the resolution of the 1D Poisson equation, we demonstrate that the junction threshold voltage  $V_{th}^{j}$  is directly linked to interface state density at the GB and to bottom NW diameter. This junction threshold voltage is shifted towards low values when interface state density increases or NW diameter decreases.

Figure 10: Evolution of the GB barrier height as a function of gate voltage for (A) different interface state densities and (B) different NW1 diameters as obtained from numerical finite elements simulations. For (A), the NW1 diameter was set at 40 nm while for (B) interface state density was  $10 \times 10^{11} \ cm^{-2} \ eV^{-1}$ . The junction threshold voltage  $V_{th}^{j}$ corresponding to the barrier lowering is indicated on the curve.  $V_{th}^{j}$  is defined as the voltage below which gate control of NW2 becomes screened by GB traps and potential barrier at the GB reaches its minimum value.

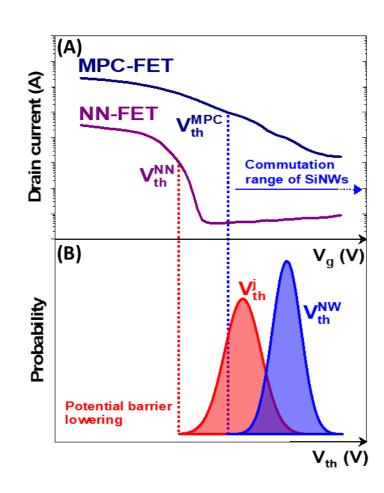

Now that the role of the NW/NW junctions is clearly defined and translated in terms of junction threshold voltage, we can consider a nanonet involving many nanowires and junctions by relying on statistics. First, the nanonet is composed of NWs that exhibit diameter dispersion (Figure 1(B)). Second, because of such NW diameter dispersion, the grain boundaries formed at NW/NW junctions upon sintering<sup>29</sup> are not homogenous and the interface state density is different from one junction to another. The first consequence of the NW diameter dispersion is a significant variation in nanowire threshold voltage<sup>30</sup>. The second consequence, observed in Figure 10, is that the junction threshold voltage  $(V_{th}^{j})$  is affected by both interface state density and NW diameter. For the sake of simplicity, Gaussian distributions were assumed both for nanowire threshold voltage  $V_{th}^{NW}$  (plotted in blue in Figure 11(B)) and for junction threshold voltage  $V_{th}^{j}$  (plotted in red in Figure 11(B)). The reasoning would be the exactly the same with other distributions. In accordance with the above stated arguments, in average, the junction threshold voltage is below that of NW ( $\langle V_{th}^{j} \rangle < \langle V_{th}^{NW} \rangle$ ), but the two distributions can overlap.

According to the percolation theory, conduction in nanonet occurs through several conduction paths (Figure 2), whose number depends on nanonet density, channel width and length and each of them is composed of  $\langle N_j \rangle$  junctions and  $\langle N_j \rangle + 1$  NWs (Table 1). On the basis of the Junction Driven Percolation mechanism, when sweeping the gate voltage from the OFF state to the ON state (gate voltage larger to smaller than flat band voltage), each conduction path remains in the OFF state until the junction with the lowest junction threshold voltage in the path turns to the ON-state. Finally, the NN-FET turns from the OFF to the ON state as soon as a first conduction path is turned to the ON-state. As a consequence, when the number of NW involved is sufficiently important to rely on statistics, the NN threshold voltage ( $V_{th}^{NN}$ ) corresponds to the lower edge of the  $V_{th}^{j}$  distribution, independently of the NW characteristic (purple curve in Figure 11(A)). This has two

important consequences for the electrical performance of the NN-FETs. First, as an NN-FET can turn to the ON-state only if the lowest  $V_{th}^{j}$  from one percolating path has been overcome, an abrupt commutation from the OFF to the ON state is expected, and thereby a good subthreshold slope. Second, such an abrupt commutation is only possible if the behavior relies on statistics, that is to say, if the ratio  $L_c/L_{SiNWs}$  is sufficiently large so that numerous NWs and junctions are involved in conduction. However, it is difficult to quantify exactly in terms of probability the limit at which a finite size NN obeys to statistical laws. Therefore, we prefer to rely on our experimental results as we were able to observe this phenomenon (Figure 5).

Indeed, in Figure 5(C) and (D), we observe the decrease of the subthreshold slope and of the threshold voltage when the ratio  $L_c/L_{SiNWs}$  is increasing from 2 (L<sub>channel</sub>=15µm) to 15 (L<sub>channel</sub>=100µm). Thus, as the channel length rises, more and more junctions are involved in each percolation path (Figure 4) and the probability that each path contains a junction with a very low threshold voltage  $V_{th}^{j}$  increases. Consequently, the resulting threshold voltage of the transistor is shifted toward lower values and the subthreshold slope improves.

Figure 11: Schematic representation of the Junction Driven Percolation mechanism for MPC-FET and NN-FET. In panel A, typical experimental output characteristic for MPC-FET and NN-FET were used to illustrate our explanations. Due to SiNW diameter dispersion, Gaussian distributions were assumed for  $V_{th}^{NW}$  and  $V_{th}^{j}$  (panel B). As the potential barrier lowering at the junction occurs only once the apparition of hole accumulation in NWs,  $V_{th}^{j}$  is lower than  $V_{th}^{NW}$  for P-type doped SiNWs. Therefore, the highest junction potential barrier of each percolating path, thereby the lowest  $V_{th}^{j}$ , will limit the conduction in the network. This limitation results in low OFF current and steep transistor commutation for NN-FET (panel A, purple triangles). On the contrary, for MPC-FET, conduction is driven by direct bridging SiNWs. Due to  $V_{th}^{NW}$  dispersion, each bridging SiNW progressively turns ON when sweeping the gate voltage from highly positive down to negative values. MPC-FETs display thus high OFF current and poor commutation (panel A, dark blue squares).  $V_{th}^{NN}$  and  $V_{th}^{MPC}$  are the resulting threshold voltages for NN-FET and MPC-FET, respectively.

**MPC-** versus NN-FETs. With the help of this physical model for nanonets, we can now interpret the substantial differences of electrical performances between MPC-FETs and NN-FETs (Figure 5) in terms of absence or presence of NW/NW junctions, respectively. In the schematic representation in Figure 11(A) are reported the typical transfer characteristics for an MPC-FET (dark blue line and square) and an NN-FET (purple line and triangles) with respect to illustrative Gaussian distributions for the NW and junction threshold voltages.

For the MPC-FETs, current flows directly from the source to the drain via several bridging SiNWs and no junction is involved in the conduction. Due to the SiNW threshold voltage dispersion<sup>30</sup>, each SiNW contributing to the conduction commutes from the OFF to the ON state for different gate voltages (Figure 11(B)). First, as soon as one bridging SiNW is turned ON, current can flow between the contacts and the current increases meaningfully. As a consequence, the MPC-FET electrical characteristic arises from the superposition of the electrical characteristic of each SiNW bridging the source and the drain. Thus, when sweeping the gate voltage from highly positive down to negative voltage, the progressive commutation of

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This i

each SiNW from the OFF to the ON state drastically degrades the subthreshold slope of the MPC-FET. Finally, the MPC-FET is fully ON, when the last NW is turned ON.

By contrast, for the NN-FETs, SiNW/SiNW junctions are the key element that governs the conduction by the previously described limiting mechanism (Junction Driven Percolation). As stated above, the current cannot flow through a given percolation path until all the junction barriers have been lowered, which results in a significantly lower OFF current than for the MPC-FETs (Figure 11), a better subthreshold slope and a lower threshold gate voltage, provided that enough nanowires are involved in each conduction path and that the nanonet's behavior follows statistical laws, that is to say, the NN is large enough to involve numerous NWs and junctions. In our experimental conditions, it seems that a channel length of 30µm is needed to fulfil this condition.

To sum up, our conduction model, the Junction Driven Percolation, that combines the percolation theory<sup>15,16</sup>, the concept of polycrystalline silicon electrical transport<sup>44</sup> and the principle of potential barrier lowering by field effect<sup>46</sup> is well suited to explain the much better electrical performance of the NN-FETs compared to the MPC-FETs, including the better OFF state and the improved subthreshold slope (Figure 5).

Optimum in the electrical performances of NN-FETs. In Figure 5, we experimentally observed that an optimum channel length emerges in terms of ON-to-OFF ratio and subthreshold slope at 30 µm. For the shorter NN-FETs, only few SiNW/SiNW junctions are involved in each conducting path: as shown in the Monte-Carlo simulations (Figure 4), 4 to 5 junctions are typically involved in each conduction path for a channel length of about 15 to 20 µm. From a statistical point of view, such a small number of junctions does not allow to cover uniformly the whole  $V_{th}^{j}$  distribution (Figure 11) and hence does not guarantee that the lower edge of the Gaussian distribution is represented. As a consequence, the Junction Driven Percolation mechanism is not fully operational, which results only in a small reduction of the OFF current and of the subthreshold slope. On the other hand, by increasing channel length, the number of junctions within each percolation path rises (Figure 4). As a result, the Gaussian distribution of  $V_{th}^{j}$  can be covered more uniformly and the probability of finding, in each percolation path, a junction with the lowest junction threshold voltage of the Gaussian distribution increases. According to the experimental results (Figure 5), 30 µm is the minimal channel length necessary to stabilize the OFF current at a very low value (10<sup>-13</sup>-10<sup>-12</sup> A) and to meet the most abrupt subthreshold slope, around 1V.dec<sup>-1</sup> (Figure 5(B) and (C)). So, according to the Monte-Carlo simulations (Figure 4), a minimum of 8 SiNW/SiNW junctions is required to ensure statistically a low  $V_{th}^{j}$  in each percolation path and to fully benefit from the Junction Driven Percolation mechanism. However, beside this beneficial effect of the increasing number of junctions in the percolation paths, according to the percolation theory and the scaling law, the ON current decreases quickly when channel length increases (Figure 7). The combination of these two opposite effects results in the existence of an optimal channel length for a given channel width and a given nanowire density, leading to best performance for the nanonet based

Publishing

transistor. We are currently exploring the role of nanowire density and our initial results suggest that the optimal channel length strongly depends on the NW density and increases with it. Moreover, based on our simulations, we can also assume that the optimal channel length depends on the NW length.

#### Conclusions

Using our original technological process to fabricate long-channel silicon nanonet-based transistors, we thoroughly investigated in this paper their electrical properties for various channel lengths. A strong correlation between channel length and transistor parameters (OFF current, ON current, ON-to-OFF ratio and subthreshold slope) were highlighted. According to these results, we experimentally showed that nanowire/nanowire junctions play a fundamental role in the electrical conduction of the overall network through a limiting mechanism. On the basis of the percolation theory<sup>15,16</sup> combined with a model for electrical transport adapted from that in polycrystalline silicon<sup>44</sup> and with the principle of potential barrier lowering by field effect<sup>46</sup>, we proposed the Junction Driven Percolation mechanism in which each junction is considered as a potential barrier that can be lowered by field effect.

Using this approach, we suggest that the significant enhancement and stabilization of electrical performance observed experimentally with channel length increase are directly linked to the nanowire/nanowire junctions. On the basis of this model and of our experimental evidences, we show that junctions play a key role in the behavior of transistors as they improve significantly the electrical performances by minimizing and stabilizing the OFF current as well as the subthreshold slope. As a consequence, by controlling properly the junction interfaces and device geometry, Si nanonet-FET electrical properties can be significantly enhanced. NW/NW junctions can be seen as a promising alternative to improve the electrical performances of NW-based devices provided that enough nanowires and junction are involved in each conduction path and that the nanonet behavior follows statistical laws. On the basis of this work, the impact of the SiNW density on the FET electrical performance will be investigated.

#### **Supplementary Material**

The online version of this article contains supplementary material about the percolation path determination in the Monte-Carlo simulations and that gives Details on FEM simulation used for 1D Poisson equation for Fig. 9 and Fig. 10 in paragraph « Physical model for Si NN-FET ».

#### Acknowledgments

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

Publishing

This i

CEPTED MANUSCRIP is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

This work has received funding from the EU H2020 RIA project Nanonets2Sense under grant agreement n°688329. This work was partly supported by the French RENATECH network. This work has received funding from the EU H2020 ERA-NET project Convergence. This work benefited from the facilities and expertise of the OPE)N(RA characterization platform of FMNT (FR 2542, fmnt.fr) supported by CNRS, Grenoble INP and UGA and PTA (Upstream Technological Platform), cooperated by CNRS Renatech and CEA Grenoble, France. The authors want to thank Maryline Bawedin (IMEP-LaHC) for fruitful discussion.

#### Data availability statements

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### References

<sup>1</sup> G. Grüner, J. Mater. Chem. **16**, 3533 (2006).

<sup>2</sup> G. Grüner, Sci. Am. **296**, 76 (2007).

<sup>3</sup> M. Legallais, T.T.T. Nguyen, M. Mouis, B. Salem, E. Robin, P. Chenevier, and C. Ternon, Solid. State. Electron. 143, 97 (2018).

<sup>4</sup> Q. Cao, H.S. Kim, N. Pimparkar, J.P. Kulkarni, C. Wang, M. Shim, K. Roy, M.A. Alam, and J.A. Rogers, Nature 454, 495 (2008).

<sup>5</sup> T.T.T. Nguyen, T. Cazimajou, M. Legallais, T. Arjmand, V.H. Nguyen, M. Mouis, B. Salem, E. Robin, and C. Ternon, Nano Futur. 3, 025002 (2019).

<sup>6</sup> D. Langley, G. Giusti, C. Mayousse, C. Celle, D. Bellet, and J.P. Simonato, Nanotechnology **24**, 452001 (2013).

<sup>7</sup> P. Serre, M. Mongillo, P. Periwal, T. Baron, and C. Ternon, Nanotechnology **26**, 1 (2015).

<sup>8</sup> L. Hu, D.S. Hecht, and G. Grüner, Chem. Rev. **110**, 5790 (2010).

<sup>9</sup> N. Rouhi, D. Jain, and P.J. Burke, ACS Nano **5**, 8471 (2011).

<sup>10</sup> S.H. Dalal, H.E. Unalan, Y. Zhang, P. Hiralal, L. Gangloff, A.J. Flewitt, G.A.J. Amaratunga, and W.I. Milne, in Carbon Nanotub. Assoc. Devices, edited by M. Razeghi, D. Pribat, and Y.H. Lee (2008), pp. 1–7.

<sup>11</sup> B. Sun and H. Sirringhaus, Nano Lett. **5**, 2408 (2005).

<sup>12</sup> H.E. Unalan, Y. Zhang, P. Hiralal, S. Dalal, D. Chu, G. Eda, K.B.K. Teo, M. Chhowalla, W.I. Milne, and G.A.J. Amaratunga, Appl. Phys. Lett. 94, 163501 (2009).

<sup>13</sup> F. Morisot, V.H. Nguyen, C. Montemont, T. Maindron, D. Muñoz-Rojas, M. Mouis, M. Langlet, and C. Ternon, Nanotechnology 30, 385202 (2019).

<sup>14</sup> C. Sun, N. Mathews, M. Zheng, C.H. Sow, L.H. Wong, and S.G. Mhaisalkar, J. Phys. Chem. C **114**, 1331 (2010).

<sup>15</sup> G.E. Pike and C.H. Seager, Phys. Rev. B **10**, 1421 (1974).

<sup>16</sup> D. Stauffer and A. Aharony, *Introduction To Percolation Theory*, Second Edi (London: Taylor and Francis, 1994).

<sup>17</sup> J. Hicks, A. Behnam, and A. Ural, Phys. Rev. E **79**, 1 (2009).

<sup>18</sup> M. Žeželj and I. Stanković, Phys. Rev. B **86**, 1 (2012).

This i

Physics

lied

Journal

Physics

Publishing

This i

Journal

is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

<sup>19</sup> C. Gomes da Rocha, H.G. Manning, C. O'Callaghan, C. Ritter, A.T. Bellew, J.J. Boland, and M.S. Ferreira, Nanoscale **7**, 13011 (2015).

<sup>20</sup> I. Balberg, N. Binenbaum, and C.H. Anderson, Phys. Rev. Lett. **51**, 1605 (1983).

<sup>21</sup> J. Hicks, J. Li, C. Ying, and A. Ural, J. Appl. Phys. **123**, 204309 (2018).

<sup>22</sup> A.T. Bellew, H.G. Manning, C. Gomes da Rocha, M.S. Ferreira, and J.J. Boland, ACS Nano **9**, 11422 (2015).

<sup>23</sup> R. Benda, E. Cancès, and B. Lebental, J. Appl. Phys. **126**, 044306 (2019).

<sup>24</sup> I. V. Vodolazskaya, A. V. Eserkepov, R.K. Akhunzhanov, and Y.Y. Tarasevich, J. Appl. Phys. **126**, 244903 (2019).

<sup>25</sup> S. Kumar, J.Y. Murthy, and M.A. Alam, Phys. Rev. Lett. **95**, 1 (2005).

<sup>26</sup> C. Kocabas, N. Pimparkar, O. Yesilyurt, S.J. Kang, M.A. Alam, and J.A. Rogers, Nano Lett. **7**, 1195 (2007).

<sup>27</sup> N. Pimparkar and M.A. Alam, IEEE Electron Device Lett. **29**, 1037 (2008).

<sup>28</sup> M.S. Fuhrer, J. Nygård, L. Shih, M. Forero, Y.G. Yoon, M.S.C. Mazzoni, H.J. Choi, J. Ihm, S.G. Louie, A. Zettl, and P.L. McEuen, Science (80-.). **288**, 494 (2000).

<sup>29</sup> C. Ternon, P. Serre, J.M. Lebrun, V. Brouzet, M. Legallais, S. David, T. Luciani, C. Pascal, T. Baron, and J.M. Missiaen, Adv. Electron. Mater. **1**, 1 (2015).

<sup>30</sup> T. Cazimajou, M. Legallais, M. Mouis, C. Ternon, B. Salem, and G. Ghibaudo, Solid. State. Electron. **143**, 83 (2018).

<sup>31</sup> T. Cazimajou, M. Legallais, T.T.T. Nguyen, M. Mouis, C. Ternon, B. Salem, and G. Ghibaudo, in 2019 Jt. Int. EUROSOI Work. Int. Conf. Ultim. Integr. Silicon (IEEE, 2019), pp. 1–4.

<sup>32</sup> T. Cazimajou, M. Mouis, M. Legallais, T.T.T. Nguyen, C. Ternon, B. Salem, and G. Ghibaudo, Solid. State. Electron. **168**, 107725 (2020).

<sup>33</sup> R.S. Wagner and W.C. Ellis, Appl. Phys. Lett. **4**, 89 (1964).

<sup>34</sup> G. Rosaz, B. Salem, N. Pauc, P. Gentile, A. Potié, A. Solanki, and T. Baron, Semicond. Sci. Technol. **26**, 085020 (2011).

<sup>35</sup> M. Legallais, T.T.T. Nguyen, T. Cazimajou, M. Mouis, B. Salem, and C. Ternon, Mater. Chem. Phys. J. **238**, 121871 (2019).

<sup>36</sup> J. Li and S.L. Zhang, Phys. Rev. E **80**, 040104 (2009).

<sup>37</sup> D.P. Langley, M. Lagrange, N.D. Nguyen, and D. Bellet, Nanoscale Horizons **3**, 545 (2018).

<sup>38</sup> U. Murat Erdem, (2010) Intersection of line segments, MATLAB Central File Exchange, version 1.10.

<sup>39</sup> J. Kirk, (2007) Dijkstra's Algorithm, MATLAB Central File Exchange, version 1.30.

<sup>40</sup> Y. Ono, S. Kishimoto, Y. Ohno, and T. Mizutani, Nanotechnology **21**, 205202 (2010).

<sup>41</sup> C. Wang, J. Zhang, K. Ryu, A. Badmaev, L.G. De Arco, and C. Zhou, Nano Lett. **9**, 4285 (2009).

<sup>42</sup> M.N. Alexander and D.F. Holcomb, Rev. Mod. Phys. **40**, 815 (1968).

<sup>43</sup> A. Buldum and J.P. Lu, Phys. Rev. B **63**, 161403 (2001).

<sup>44</sup> J.Y.W. Seto, J. Appl. Phys. **46**, 5247 (1975).

<sup>45</sup> T.I. Kamins, J. Appl. Phys. **42**, 4357 (1971).

<sup>46</sup> T.S. Li and P.S. Lin, IEEE Electron Device Lett. **14**, 240 (1993).

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0023322

<sup>47</sup> P.M. Walker, H. Mizuta, S. Uno, Y. Furuta, and D.G. Hasko, IEEE Trans. Electron Devices **51**, 212 (2004).

<sup>48</sup> X. Liu, L. Gu, Q. Zhang, J. Wu, Y. Long, and Z. Fan, Nat. Commun. **5**, 4007 (2014).

AIP ADPlishing Applied Physics

Journal of Applied Physics