## An Efficient Thermal Model for Multifinger SiGe HBTs Under Real Operating Condition

Nidhin K, Shubham Pande, Shon Yadav, Suresh Balanethiram, Deleep R Nair, Sebastien Fregonese, Thomas Zimmer, Anjan Chakravorty

### ▶ To cite this version:

Nidhin K, Shubham Pande, Shon Yadav, Suresh Balanethiram, Deleep R Nair, et al.. An Efficient Thermal Model for Multifinger SiGe HBTs Under Real Operating Condition. IEEE Transactions on Electron Devices, 2020, 67 (11), pp.5069-5075. 10.1109/TED.2020.3021626. hal-03015948

HAL Id: hal-03015948

https://hal.science/hal-03015948

Submitted on 20 Nov 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# An Efficient Thermal Model for Multifinger SiGe HBTs under Real Operating Condition

Nidhin K, Shubham Pande, Shon Yadav, Suresh Balanethiram, Deleep R Nair, Sebastien Fregonese, Thomas Zimmer, *Senior Member, IEEE* Anjan Chakravorty, *Member, IEEE*

Abstract—In this work, we present a simple analytical model for electrothermal heating in multifinger bipolar transistors under realistic operating condition where all fingers are heating simultaneously. The proposed model intuitively incorporates the effect of thermal coupling among the neighboring fingers in the framework of self-heating bringing down the overall model complexity. Compared to the traditional thermal modeling approach for an n-finger transistor where the number of circuit nodes increases as  $n^2$ , our model requires only n-number of nodes. The proposed model is scalable for any number of fingers and with different emitter geometries. The model is validated with 3D thermal simulations and measured data from STMicroelectronics B4T technology. The Verilog-A implemented model simulates 40% faster than the conventional model in a transient simulation of a five-finger transistor.

Index Terms—SiGe HBTs, multifinger transistor, electrothermal effect, thermal modeling, self-heating, thermal resistance.

#### I. Introduction

SILICON germanium heterojunction bipolar transistors (SiGe HBTs) are popularly used as power amplifiers in the RF front end modules. Power amplifiers are often expected to have large emitter area in order to allow large amount of currents. However, large emitter widths lead to a higher base resistance resulting in a lower maximum oscillation frequency  $(f_{max})$  of the device. Therefore, it has been a common practice to partition a large emitter into smaller fingers each having small enough emitter width  $(W_E)$  leading to a multi-finger transistor. Although in such a structure, each emitter finger is electrically isolated by shallow trenches (ST), they are thermally coupled through the common Silicon substrate.

Self heating is a serious problem in modern bipolar transistors where lateral dimensions are significantly scaled down and additional trench isolations are used. In case of multi-finger transistors, additional thermal coupling from nearby fingers further increases the device temperature. Conventionally, this additional increment in temperature is captured by considering

Nidhin K, S. Pande, D. R. Nair, A. Chakravorty are with the Department of Electrical Engineering, IIT Madras, Chennai 600036 India. email: anian@ee.iitm.ac.in.

- S. Balanethiram is with the Department of Electronics and Communication Engineering, IIIT Tiruchirappali, Trichy 620015. email: sureshbalanethiram@gmail.com

- S. Yadav is with Globalfoundries, Bangalore.

- S. Fregonese, and T. Zimmer are with IMS Laboratory, University of Bordeaux, 33400 Talence, France. email: sebastien.fregonese@ims-bordeaux.fr, thomas.zimmer@ims-bordeaux.fr.

This work was supported in part by the EU under Project Taranto, in part by ISRO project ELE/17-18/176/ISRO/ANJA and in part by Department of Science and Technology, India, under Project EMR/2016/004726. The authors would like to thank STMicroelectronics for providing the B9MW wafer.

thermal coupling effects from other nearby fingers. For the calculation of the overall temperature at a finger, thermal effect of each finger is considered at a time and finally all effects are added up assuming the validity of superposition. The temperature dependence of thermal conductivity makes the temperature-power relationship nonlinear. This makes the straightforward application of superposition to include both the self-heating and thermal coupling effects in calculating the overall finger temperature questionable. The real operating condition within a power amplifier circuit exciting all the fingers in a multi-finger transistor together instead of exciting one finger at a time was elaborated in [1]. A state-of-theart static thermal model to cater the self-heating as well as thermal coupling effects in an n-finger transistor requires  $n^2$ number of nodes as reported in [2]. Besides, modeling thermal coupling using voltage controlled-voltage-sources (VCVS) in series with the self-heating resistances degrades the speed performance of a thermal network as illustrated in [3].

In this work, we present an intuitive thermal model to predict the overall temperature at each finger in a multifinger transistor when all the fingers are excited together. Unlike the conventional methods, our model uses no VCVS as the thermal coupling effects are considered within the framework of selfheating. Eventually, the use of superposition can be avoided altogether resulting in just 'n' number of nodes for an n-finger transistor. The proposed model also considers the temperaturedependent thermal conductivity of the semiconductor material and does not need to use any superposition theorem to calculate the overall device temperature at any finger. The paper is organized as follows. Section II presents the elaborate model formulation with a hint towards model implementation. Section III presents a detailed model validation against 3D TCAD simulation and experimental data. The speed performance of the proposed model is also compared with the conventional thermal model. Finally, we present our conclusions in section IV.

#### II. MODEL FORMULATION

Electrothermal effect in HBTs causes heat generation at the base-collector junction. Most of the generated heat flows down towards the substrate contact because of the high thermal resistance offered by the upward path due to the interlayer dielectric of the back-end-of-line (BEOL) structures as reported in [1], [4], [5]. Therefore, the upward heat-flow is neglected in the initial analysis and is added later by adding an effective BEOL thermal resistance in parallel. In the front-end-of-line (FEOL) portion, the base and emitter regions are also

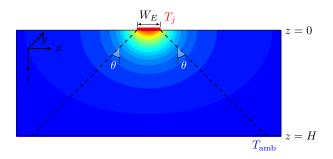

Fig. 1. Cross sectional view of a single finger bipolar transistor structure with no trench isolation showing heat source, heat sink, isothermal lines and the imaginary boundaries.

neglected because of their negligible thickness. This allows us to model the emitter finger as a rectangular heat source on a semi-infinite substrate as shown in Fig 1. Note that the effect of base and emitter region can always be clubbed with the BEOL thermal resistance. For modeling purpose, it is assumed that the bottom of the substrate is maintained at an ambient temperature  $(T_{amb})$  and the substrate extends to infinity in the lateral directions. In case of multifinger transistor, multiple heat sources are to be considered simultaneously under real operating condition. The modern application circuits such as power amplifiers are equipped with temperature insensitive bias techniques to ensure a near constant operating current [6]-[9]. Adopting such biasing techniques in a multifinger transistor yields similar amount of collector current  $(I_C)$ through all the fingers at a given collector-emitter voltage  $(V_{CE})$ . This leads to an identical amount of power dissipation  $(P_{\rm diss})$  in each finger (since  $P_{\rm diss} \approx I_C \times V_{CE}$ ). Accordingly the modeling framework presented in this work assumed that identical amount of  $P_{\rm diss}$  is generated at each finger.

Fig. 1 depicts the heat spread from a single heat source in a semi-infinite environment. Vertical position (z) dependent temperature variation, T(z), inside the system from the heat source (at a temperature  $T_j$ ) to the heat sink (at  $T_{\rm amb}$ ) is indicated by the isothermal contours. In order to obtain a simplified model for T(z) in such a system, a single heat-spreading angle  $(\theta)$  under conical approximation is used defining the imaginary thermal boundary [10]. If  $P_{\rm diss}$  is the power dissipated by the heat source, using average thermal conductivity formulation [11], the temperature variation along the z-direction (T(z)) can be written as

$$T(z) = \left[ T_{\text{ref}}^{1-\alpha} + P_{\text{diss}} f_G(z) \frac{1-\alpha}{\beta} \right]^{1/(1-\alpha)} \tag{1}$$

where  $T_{\rm ref}=T_{\rm amb}$  at z=H (signifying a heat-sink at the substrate contact).  $\alpha$ ,  $\beta$  are the parameters of temperature dependent thermal conductivity in Silicon,  $\kappa_{si}(T)=\beta T^{-\alpha}$  [12].  $f_G(z)$  signifies the position dependent geometry factor of the heat spread [13]. First, T(z) is evaluated at the heat sink (z=H) with  $T_{\rm ref}=T_{\rm amb}$  in (1). Eventually, for calculating  $T(z-\Delta z)$ , T(z) from the previous calculation is taken as  $T_{\rm ref}$  in (1). This is repeated to obtain the temperature variation for all z in the system from heat sink to the heat source.

The above formulation can be generalized for an asymmetric heat spread of a planar heat source with W as width in the x-direction and L as length in the y-direction. In that case,

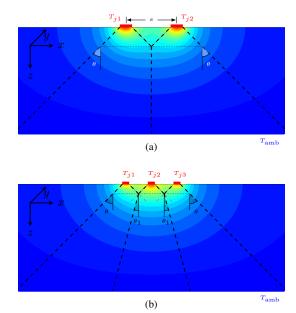

Fig. 2. Cross sectional view of (a) two-finger and (b) three-finger transistor structure with no trench isolation showing heat source, heat sink, isothermal lines and the imaginary boundaries.

the position-dependent cross-sectional area of the heat spread can be written as [14]

$$A(x, y, z) = (W + (H - z)\Theta_x).(L + (H - z)\Theta_y)$$

(2)

with

$$\Theta_x = \tan(\theta_{x,l}) + \tan(\theta_{x,r})$$

and  $\Theta_y = \tan(\theta_{y,l}) + \tan(\theta_{y,r})$

(3)

where H is the total height of the heat spread. Here  $\theta_{x,l}(\theta_{y,l})$  and  $\theta_{x,r}(\theta_{y,r})$  are the heat spreading angles on the left and right sides along  $W_E$   $(L_E)$  respectively. Resultant geometry factor can be obtained as

$$f_G(z) = \int_0^z \frac{dz'}{A(x, y, z')} = \frac{\ln\left[\frac{W(L + z\Theta_x)}{L(W + z\Theta_y)}\right]}{W\Theta_y - L\Theta_x}.$$

(4)

This equation presents a generic formulation and can be used to estimate the geometry factor of any asymmetric heat spread. Note that (4) need not be used in case of vertical heat spread, where a simple ratio between the height and the cross sectional area yields  $f_G(z)$ . Accordingly, the depth-dependent temperatures (including that at the heat source, z=0) can be obtained using (1). Note that our aim is to find out the finger temperature i.e., at z=0 and as such there is no need to compute any other T(z). However, this calculation is exercised in order to showcase the model's capability to capture the underlying physics and accordingly gain a confidence on the proposed model.

Estimation of the temperatures becomes difficult for a system with two or more heat sources. Consider a case in which two heat sources (having same area) each dissipating a power of  $P_{\rm diss}$  are kept close to each other (with centre-to-centre spacing s in between them) along the x-direction as shown in Fig. 2(a). Similar to the single-heat-source structure, total heat spread of the system can be shown by dashed lines with spreading angle  $\theta$  (which may be equal to  $45^{\circ}$ ) [10], [15]. For such a system, one can obtain the rise in temperature by

considering this overall heat spread and total power dissipation of  $2P_{\rm diss}$ . Alternatively, one can also obtain temperature rise at one finger by defining individual heat spread. As the structure is symmetric, one can intuitively say that  $T_1(z) = T_2(z)$ . Hence, the total heat spread in the x-z plane must be divided into identical halves as shown by the dashed line in Fig. 2(a). The vertical thermal boundary or zero spreading angle from the z-point where the spread of the two heat sources intersect essentially ensures equal heat flow volume in this case. This divided heat-flow volume with power dissipation  $P_{\rm diss}$  yields the same finger temperatures. In case of a system with three heat sources as shown in Fig. 2(b), the thermal boundaries of heat source in the middle are governed by two adjacent heat sources. On the other hand, for the first and third heat sources, only one thermal boundary depends on the adjacent (middle) heat source and the other boundary is defined by a heat spreading line of  $\theta$ . Depending on the spreading angles for individual heat sources, this framework can allow a higher temperature rise at the second heat source compared to the other two. However the first and third heat sources have an equal rise in temperature  $(T_1 = T_3)$  due to identical boundary conditions. This is also evident from the identical isothermal lines (obtained from TCAD simulation) under the first and third heat sources as shown in Fig. 2(b). Under the second heat source, these lines appear more crowded indicating a higher temperature than the rest.

In order to accurately predict the temperature at each finger, an effective heat spreading angle  $(\theta_1)$  has to be defined between the adjacent heat sources as shown by the dashed lines in Fig. 2(b). Prior to the intersection of the heat sources, the spreading angles of all the heat sources were same  $\theta$ . If  $\theta_1$  is estimated accurately, separate geometry factors corresponding to all heat sources can be obtained. Since all the fingers are dissipating the same amount of power and since the heat flux is continuous, the same amount of heat flux lines must be crossing the x-y plane at the depth of intersection of the flux lines from different fingers. Therefore, estimation of  $\theta_1$  can be guided by a principle based on the symmetric total spreading as elaborated below. In case of two-finger device, the first heat spread in Fig. 2(a) is characterized by  $\theta$  on one side and  $0^{\circ}$  on other. A similar approach follows for the second heat spread as well. Therefore, both the spreads have effective spreading angle of  $\theta + 0^{\circ}$ . In case of three-finger device (Fig. 2(b)), heat spread for the first finger has an angle of  $\theta$  in one side and  $-\theta_1$  in the other. Similarly for the second finger, the angle is  $\theta_1$  in both the sides. Equating the effective total angles of the two fingers results into  $\theta - \theta_1 = 2 \times \theta_1$  yielding  $\theta_1 = \theta/3$ . Therefore, the essential principle is to find out the total heat spreading angle associated with each finger and to equate them in order to obtain the effective heat spreading between the adjacent heat sources. Extending this technique to a system with n number of fingers, one can obtain a single equation for heat spreading angles as

$$\theta_i = \frac{\theta}{n} \, (n-2i) \qquad i=1,2,3,...\frac{n}{2} \text{ for even } n,$$

$$i=1,2,3,...\frac{n-1}{2} \text{ for odd } n.$$

Here  $\theta$  is the angle of outer heat spreading for the corner fingers. Note that the constant spreading angle framework does not always ensure  $\theta=45^{\circ}$  as have been reported in several cases [15]–[17]. While testing against TCAD simulation (as presented in the next section) we have found that in most of the geometries  $\theta=46^{\circ}$  yields excellent accuracy. Once the heat spreading angles are obtained, they are used to compute the cross-sectional area of each heat spread and the geometry factors corresponding to each heating finger using (2) to (4) and subsequently the temperature at each finger using (1).

In practice, each transistor finger is to be modeled using separate electrical model where a thermal sub-circuit is available in order to capture the self-heating effect. Conventionally the thermal coupling effect is captured by using a more complicated thermal network that uses voltage-controlled voltage sources [2]. In the present work, since we have computed the geometry factor  $(f_G)$  for each heating finger, the corresponding thermal resistance is easily obtained and can be used within the already existing self-heating network. This way one can get rid of the thermal coupling network altogether and reduce the overall node-count of the thermal network from  $n^2$  (required for conventional model) to just n for an n-finger transistor. The resulting improvement in the simulation speed will be discussed in the next section.

#### III. MODEL EVALUATION

#### A. Comparison with 3D TCAD simulation

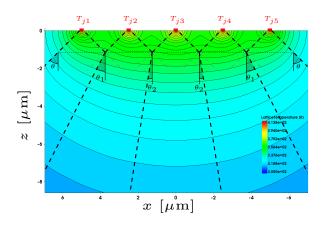

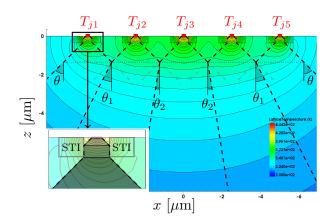

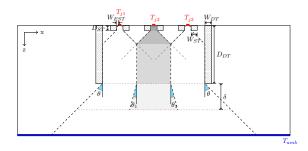

First, we test our proposed model against 3D TCAD thermal simulation results of multifinger SiGe HBT structures having no trench isolation. Using Synopsys Sentaurus [18], we simulated a single finger structure and four multifinger structures with two, three, four and five fingers, respectively, having an emitter area  $(A_E)$  of  $0.2 \times 5 \,\mu\text{m}^2$  for each finger. Following the modeling framework, each heat source of area  $0.2 \times 5 \,\mu\text{m}^2$  corresponding to each transistor finger is located at the top of the Silicon substrate. A constant power of 30 mW is dissipated at each heating finger. This simulation scenario is illustrated through a cross-sectional view (x-z)plane) of a 5-finger structure in Fig. 3. Each finger is isolated from the neighboring finger with a centre-to-centre spacing of  $s=2.5\,\mu\mathrm{m}$ . The total simulated area of the substrate is  $300\times300\,\mathrm{um}^2$  with a Silicon thickness of 100 um. In the TCAD simulation, values for the temperature coefficients of thermal conductivity for Silicon,  $\alpha = 1.263$  and  $\beta = 2099$ are used. For all the TCAD simulations, the bottom surface is maintained at ambient temperature ( $T_{\rm amb}$ =300 K) and the heat source injects a constant uniform heat flux into the silicon substrate. All other surfaces, including the part of the top surface not covered by the heat source, are considered adiabatic.

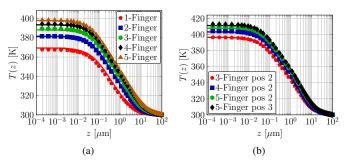

Fig. 4(a) compares our model results for the z-dependent temperature variation along the middle of the heat source (T(z)) with TCAD simulation data corresponding to a single finger structure and corner (first) fingers in case of multifinger structures, without any trench isolation. Similarly, Fig. 4(b) compares our model results for the T(z) variation with TCAD simulation data corresponding to the internal fingers in multifinger structures without any trench isolation. Note that for

Fig. 3. The imaginary boundary used in the model overlaid on the TCAD simulated temperature profile in the x-z plane of a 5-finger device without any trenches.  $\theta_1$  and  $\theta_2$  can be calculated using (5). For  $\theta=46^\circ$ , the resulting values are  $\theta_1=27.6^\circ$  and  $\theta_2=9.2^\circ$ .

Fig. 4. T(z) variation at the middle of (a) corner (first) fingers (b) inner fingers in multifinger structures without any trench isolation: a comparison between TCAD simulation (symbols) and proposed model (lines).

optimum model fitting, we have used  $\theta=46^\circ$  for all the structures. Accordingly the spreading angles of internal fingers are calculated using (5). Excellent model agreement with the TCAD simulated T(z) data for all the structures builds up our confidence in the calculation of all the heat spreading angles corresponding to each finger and subsequently the imaginary boundaries. This motivates us to extend our modeling framework for shallow trench isolated (STI) isolated multifinger transistor structures as detailed below.

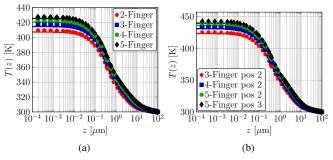

In case of multifinger structure with STI, each finger is housed within a STI with a constant finger-edge to trenchedge distance of  $0.14\,\mu m$  along both x- and y-directions. Cross sectional view of an ST-isolated 5-finger HBT structure simulated in TCAD is shown in Fig. 5. Corresponding to STMicroelectronics B4T technology, the width (and height) of STI is chosen as 0.45 µm (and 0.36 µm) [19]. The material chosen for the trench has very low thermal conductivity (SiO<sub>2</sub> with  $\kappa = 0.014 \,\mathrm{W/cm}$ -K) compared to that of the substrate material (Silicon). The dimensions of the substrate, emitter finger(s) and finger spacing remain identical with the previous study carried out for no-trench devices. A constant power of 30 mW is dissipated at each finger for the TCAD simulation as well as for the model. In this case, the heat flow volume of each finger is divided into three regions as shown in Fig. 5. The symmetric trapezoidal volume within STI, followed by

Fig. 5. The imaginary boundary used in the model overlaid on the TCAD simulated temperature profile in the x-z plane of a 5-finger device with STI. Inset shows the region near STI.

Fig. 6. T(z) variation at the middle of (a) corner fingers (b) inner fingers in multifinger structures with STI: a comparison between TCAD simulation (symbols) and proposed model (lines).

the cuboidal volume within STI, and the rest below STI. Note that in order to evaluate the temperature profile in the section below STI, one can apply the proposed model from the bottom of STI to the heat sink in the same fashion as explained in the no-trench case. Temperature profile within STI can be obtained following the technique generally applied for calculating the self-heating temperature since no effect of thermal coupling from other fingers need to be considered within this heat flow volume. A simple depth/area ratio is used to calculate  $f_G(z)$  inside the cuboidal section and (4) is used for the remaining sections.

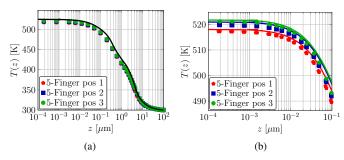

Fig. 6(a) compares our modeling results for the T(z) variation with the 3D TCAD simulation data corresponding to the corner fingers in case of multifinger structures with STI. Thermal boundaries corresponding to the internal fingers from the bottom of the STI are estimated using (5). Eventually using  $\theta$  and  $\theta_i$  in (4) and then using (4) in (1) the overall temperature profile is obtained. In Fig. 6(b), we compare our modeling results for T(z) variation with the TCAD simulation data corresponding to the internal fingers in multifinger structures with STI. Excellent model agreement is observed both in Fig. 6(a) and (b). Although our model assumes the STI to be a prefect thermal insulator, TCAD simulation considers a slight heat leakage through the STI due to the non-zero  $\kappa$  of SiO<sub>2</sub>. However, model correlation with TCAD data justifies our approximation of the perfect insulator used for SiO<sub>2</sub>. This

Fig. 7. TCAD simulated temperature contours in the x-z plane obtained by taking a cut-plane across the middle of the fingers for a 5-finger device with both STI and DTI.

observation allows us to consider perfect thermal insulator for all the trenches in subsequent simulation and model.

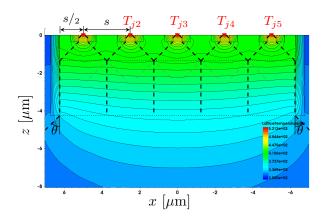

As a next step, we test our model for multifinger transistor system where each finger is individually surrounded by STI and the whole transistor is housed within a deep trench isolation (DTI). Like in previous case, the emitter finger and STI are separated with a constant edge-to-edge distance of  $0.14\,\mu m$  along both x- and y-directions. The distance between the inside edge of DTI and the midpoint of the corner emitter finger in the x-direction (along the emitter width) is exactly half of the finger-to-finger spacing (s). However, STI and DTI are located side-by-side in the y-direction (along the emitter length). Cross sectional view of the DTI five-finger structure simulated in TCAD is shown in Fig. 7. The width and height of STI remain unaltered from the previous simulation. The width (and height) of DTI is taken as 0.5 μm (4.26 μm). The dimensions of the substrate, emitter fingers, spacing between the fingers and the amount of power dissipated at each finger are not altered from the previous study.

Here we divide the heat flow volume of each finger into six sections: two inside STI, three in-between STI and DTI (due to different relative distance between STI and DTI in x- and y-directions), and one below DTI. Inside DTI, the temperature profile of each finger will be the same as the heat flow volume of individual finger is identical. The corresponding geometry factor  $f_G(z)$  is evaluated with a symmetric lateral spread of  $\theta$  (=46°) or by a simple depth/area ratio (as applicable in different sections) and eventually the T(z) profile is obtained using (1). For the section below DTI, it can be assumed that the bottom of DTI acts as a single heat source dissipating  $n \times P_{\rm diss}$  power, where n is the number of fingers. Since the heat flow volume inside the DTI region is equally shared among the fingers, this assumption leads to the prediction of the same temperature at the bottom of DTI and identical T(z)for all fingers. Black line in Fig. 8(a) shows a prediction for our T(z) model under this assumption where TCAD results for different fingers of a five-finger structure with DTI are also plotted. Even though the model predicts the same temperature for all the fingers unlike TCAD simulation, the prediction is quite close.

Fig. 8. T(z) variation at the middle of the fingers in 5-finger structure with STI and DTI: a comparison between TCAD simulation (symbols) and (a) the proposed model with  $\delta=0$  (line); (b) the proposed model with  $\delta=5\,\mu\mathrm{m}$ .

Fig. 9. Cross sectional view of a three-finger transistor structure with STI and DTI showing the depth  $\delta$  under the DTI where the proposed angle theory can be applied.

If we closely examine the isothermal lines just below DTI in Fig. 7, we find that the lines are not strictly horizontal, hence the T(x) cannot be the same just below the DTI till certain depth (say,  $\delta$ ). Therefore, we can apply our proposed angle theory conceptualized in (5) to take care of the asymmetric heat spreading within this vertical region (from the bottom of DTI to a depth of  $\delta$  below DTI). The value of  $\delta$  is taken as 5  $\mu$ m and is found to remain unaltered for different finger dimensions and STI-to-DTI distances. A single section (with  $nP_{\rm diss}$  total power) is assumed below this region as shown in Fig. 9 in order to evaluate the overall temperature at each finger. Fig. 8(b) compares this refined model for T(z) variation with TCAD simulation data. It is observed that the model is in excellent agreement with the TCAD simulated results.

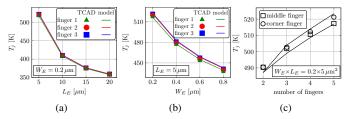

In order to investigate the model scalability, TCAD simulations of ST and DT-isolated transistor structures with different emitter dimensions and number of fingers were carried out. Figs. 10 (a), (b) and (c) show the variation of finger temperatures with emitter length (for a fixed  $W_E=0.2\,\mu\text{m}$ ), emitter width (for a fixed  $L_E=5\,\mu\text{m}$ ) and number of emitter fingers (for fixed  $W_E=0.2\,\mu\text{m}$  and  $W_E=5\,\mu\text{m}$ ). Figs. 10 (a) and (b) present the results of three different fingers in 5-finger structures, whereas Fig. 10 (c) depicts the temperatures of middle and corner fingers for different multifinger devices. The proposed model (solid lines) demonstrates an excellent agreement with the TCAD results (symbols). Maximum modeling error in Fig. 10 (c) appears to be less than 1.5%.

Fig. 10. Variation of finger temperature (a) with emitter length (for a five-finger device with fixed  $W_E=0.2\,\mu\mathrm{m}$ ), (b) with emitter width (for a five-finger device with fixed  $L_E=5\,\mu\mathrm{m}$ ), (c) with number of emitter fingers (for multifinger devices with  $W_E=0.2\,\mu\mathrm{m}$  and  $L_E=5\,\mu\mathrm{m}$ ): comparison of modeling results (lines) with TCAD simulations (symbols).

#### B. Validation with Measurement

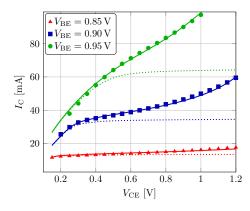

On-wafer measurement was carried out on a DTI five-finger SiGe HBT. Measurements were done at 300 K using a SUSS MicroTec probing station equipped with a thermal chuck. The emitter fingers of the transistor (each having  $W_E \times L_E = 0.23 \times 5 \, \mu \text{m}^2$ ) are electrically isolated but thermally coupled within the DTI. Each one of the five emitters has independent probing access (although all fingers are excited together in this study), the collector is common for all the fingers and the bases are all grounded as detailed in [20].

The proposed thermal model is implemented in Verilog-A and is connected as the self-heating sub-circuit to each of the five transistors. HICUM/L2 parameters are used for the electrical network [21]. The parameters for the thermal network including the BEOL thermal resistance are extracted following the methodology presented in [22]. Circuit simulations are carried out with circuit simulator QuesStudio [23].

Fig. 11 shows the measured (symbols) output characteristics of a 5-finger SiGe HBT structure fabricated in STMicroelectronics B4T technology [19]. Solid lines show the circuit simulation results with proposed thermal sub-circuit and dotted lines show the same with self-heating turned-off. Excellent model correlation with the experimental data is observed. In the given constant voltage bias condition, different fingers dissipate different amounts of power because slightly different temperatures across the fingers affect the corresponding collector current differently. In this situation, the present modeling framework tends to overestimate the temperature difference between the fingers. However, the circuit simulation results reveal only 5% difference between the maximum and minimum finger temperatures. The actual difference can be even lower.

Note that for this five-finger transistor, only five self-heating thermal networks were needed, thus avoiding the need of any complicated thermal coupling circuit altogether. In order to quantify the speed improvement of our model over the state-of-the-art thermal model for multifinger transistor [2], quasistationary and transient simulations of a 5-finger SiGe HBT are carried out for both the models using QucsStudio. HICUM/L2 parameters are used for electrical network of the transistor while only static part of the thermal subcircuit is implemented for both the models. In case of quasistationary sweep of  $V_{BE}$  from 0 to 0.9 V with 10000 steps, our model simulates 10% faster than the state-of-the-art. For a transient simulation with

Fig. 11. Output characteristics of a 5-finger SiGe HBT structure fabricated in STMicroelectronics B4T technology [19]: comparison of circuit simulation results with proposed thermal model (solid line) with measured data (symbols). Dotted lines show circuit simulation results with no thermal model.

0.9 V pulse with 400 ns width and 40 ns rise time, our model simulates 40% faster than the state-of-the-art.

#### IV. CONCLUSION

We have presented a simple, analytical, thermal model for multifinger SiGe HBTs. The proposed model is highly accurate as it considers the temperature dependence of thermal conductivity of silicon and at the same time requires no extra circuit node to account for the thermal coupling effects between nearby fingers. Other than the dissipated power, the input for the model are the dimensions and relative locations of emitter fingers and different trenches in order to compute the temperature at each finger. The model is implemented within the framework of existing self-heating sub-circuit of the main electrical model of bipolar transistor. A high level of model accuracy is observed when compared against 3D TCAD simulation as well as actual electrical measurements. The model is found to simulate 40% faster than the stateof-the-art thermal coupling model while tested for transient simulation.

#### REFERENCES

- [1] A. Dwivedi, A. Chakravorty, R. D'Esposito, A. K. Sahoo, S. Fregonese, and T. Zimmer, "Effects of BEOL on self-heating and thermal coupling in SiGe multi-finger HBTs under real operating condition," *Solid-State Electronics*, vol. 115, pp. 1–6, 2016. doi: 10.1016/j.sse.2015.09.016

- [2] D. J. Walkey, T. J. Smy, R. G. Dickson, J. S. Brodsky, D. T. Zweidinger, and R. M. Fox, "Equivalent circuit modeling of static substrate thermal coupling using VCVS representation," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 9, pp. 1198–1206, 2002. doi: 10.1109/JSSC.2002.801200

- [3] S. Balanethiram, A. Chakravorty, R. D'Esposito, S. Fregonese, and T. Zimmer, "Efficient modeling of static self-heating and thermalcoupling in multi-finger SiGe HBTs," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting (BCTM)*, 2015, pp. 68–71. doi: 10.1109/BCTM.2015.7340557

- [4] A. K. Sahoo, S. Fregonese, M. Weis, C. Maneux, N. Malbert, and T. Zimmer, "Impact of back-end-of-line on thermal impedance in SiGe HBTs," in *Proc. International Conference on Simulation of Semi*conductor Processes and Devices (SISPAD), 2013, pp. 188–191. doi: 10.1109/SISPAD.2013.6650606

- [5] R. D'Esposito, S. Fregonese, T. Zimmer, and A. Chakravorty, "Dedicated test-structures for investigation of the thermal impact of the BEOL in advanced SiGe HBTs in time and frequency domain," in 2016 International Conference on Microelectronic Test Structures (ICMTS), 2016, pp. 28–31. doi: 10.1109/ICMTS.2016.7476168

- [6] Wei-Chun Hua, Hung-Hui Lai, Po-Tsung Lin, Chee Wee Liu, Tzu-Yi Yang, and Gin-Kou Ma, "High-linearity and temperature-insensitive 2.4 GHz SiGe power amplifier with dynamic-bias control," in 2005 IEEE Radio Frequency integrated Circuits (RFIC) Symposium Digest of Papers, 2005, pp. 609–612. doi: 10.1109/RFIC.2005.1489887

- [7] E. Jarvinen, S. Kalajo, and M. Matilainen, "Bias circuits for GaAs HBT power amplifiers," in 2001 IEEE MTT-S International Microwave Sympsoium Digest (Cat. No.01CH37157), vol. 1, 2001, pp. 507–510 vol.1. doi: 10.1109/MWSYM.2001.966942

- [8] X. Yang, T. Sugiura, N. Otani, T. Murakami, E. Otobe, and T. Yoshi-masu, "5-GHz band SiGe HBT linear power amplifier IC with novel CMOS active bias circuit for WLAN applications," in 2014 9th European Microwave Integrated Circuit Conference, 2014, pp. 428–431. doi: 10.1109/EuMC.2014.6986700

- [9] Youn Sub Noh and Chul Soon Park, "PCS/W-CDMA dual-band MMIC power amplifier with a newly proposed linearizing bias circuit," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 9, pp. 1096–1099, 2002. doi: 10.1109/JSSC.2002.801169

- [10] J. Holway, L. H. and M. G. Adlerstein, "Approximate formulas for the thermal resistance of IMPATT diodes compared with computer calculations," *IEEE Transactions on Electron Devices*, vol. 24, pp. 156– 159, Feb. 1977. doi: 10.1109/T-ED.1977.18696

- [11] S. Balanethiram, A. Chakravorty, R. D'Esposito, S. Fregonese, D. Céli, and T. Zimmer, "Accurate modeling of thermal resistance for on-wafer SiGe HBTs using average thermal conductivity," *IEEE Trans. on electron devices*, vol. 64, no. 9, pp. 3955–3960, 2017. doi: 10.1109/TED.2017.2724939

- [12] T. T. Nghiêm, J. Saint-Martin, and P. Dollfus, "Electro-thermal simulation based on coupled Boltzmann transport equations for electrons and phonons," *Journal of Computational Electronics*, vol. 15, no. 1, pp. 3–15, 2016. doi: 10.1007/s10825-015-0773-2

- [13] S. Yadav and A. Chakravorty, "A pragmatic approach to modeling self-heating effects in SiGe HBTs," *IEEE Transactions on Electron Devices*, vol. 64, no. 12, pp. 4844–4849, 2017. doi: 10.1109/TED.2017.2765283

- [14] G.-b. Gao, M. S. Ünlü, H. Morkoc, and D. L. Blackburn, "Emitter ballasting resistor design for, and current handling capability of Al-GaAs/GaAs power heterojunction bipolar transistors," *IEEE Trans. Electron Devices*, vol. 38, no. 2, pp. 185–196, 1991. doi: 10.1109/16.69894

- [15] R. David, "Computerized thermal analysis of hybrid circuits," *IEEE Transactions on Parts, Hybrids, and Packaging*, vol. 13, no. 3, pp. 283–290, 1977. doi: 10.1109/TPHP.1977.1135213

- [16] C. R. Zimmer, "Computer simulation of hybrid integrated circuits including combined electrical and thermal effects," *ElectroComponent Science and Technology*, vol. 10, no. 2-3, pp. 171–176, 1983. doi: 10.1155/apec.10.171

- [17] F. N. Masana, "A closed form solution of junction to substrate thermal resistance in semiconductor chips," *IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part A*, vol. 19, no. 4, pp. 539–545, 1996. doi: 10.1109/95.554935

- [18] Synopsys TCAD, "Sentaurus: Sentaurus device user guide, release H-2013.03," 2013.

- [19] A. Chantre, P. Chevalier, T. Lacave, G. Avenier, M. Buczko, Y. Campidelli, L. Depoyan, L. Berthier, and C. Gacquière, "Pushing conventional SiGe HBT technology towards "Dotfive" terahertz," in *Proc. The 5th European Microwave Integrated Circuits Conference*, 2010, pp. 21–24.

- [20] M. Weiss, A. K. Sahoo, C. Maneux, S. Fregonese, and T. Zimmer, "Mutual thermal coupling in SiGe: C HBTs," in *Proc. Symposium on Microelectronics Technology and Devices (SBMicro)*, 2013, pp. 1–4. doi: 10.1109/SBMicro.2013.6676131

- [21] M. Schröter and A. Chakravorty, Compact Hierarchical Bipolar Transistor Modeling with HICUM. World Scientific, 2010. [Online]. Available: https://doi.org/10.1142/7257

- [22] S. Balanethiram, R. D'Esposito, A. Chakravorty, S. Fregonese, and T. Zimmer, "Extraction of BEOL contributions for thermal resistance in SiGe HBTs," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 1380– 1384, 2017. doi: 10.1109/TED.2016.2645615

- [23] M. Margraf. Quesstudio a free and powerful circuit simulator. [Online]. Available: http://dd6um.darc.de/QuesStudio/