# Random Probing Security: Verification, Composition, Expansion and New Constructions

Sonia Belaïd, Jean-Sébastien Coron, Emmanuel Prouff, Matthieu Rivain, Abdul Rahman Taleb

### ► To cite this version:

Sonia Belaïd, Jean-Sébastien Coron, Emmanuel Prouff, Matthieu Rivain, Abdul Rahman Taleb. Random Probing Security: Verification, Composition, Expansion and New Constructions. CRYPTO 2020 - 40th Annual International Cryptology Conference, Aug 2020, Santa Barbara, CA / Virtual, United States. pp.339-368, 10.1007/978-3-030-56784-2\_12. hal-02984491

# HAL Id: hal-02984491 https://hal.science/hal-02984491v1

Submitted on 31 Oct 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Random Probing Security: Verification, **Composition**, Expansion and New Constructions

Sonia Belaïd<sup>1</sup>, Jean-Sébastien Coron<sup>2</sup>, Emmanuel Prouff<sup>3,4</sup>, Matthieu Rivain<sup>1</sup>, and Abdul Rahman Taleb<sup>1</sup>

> <sup>1</sup> CryptoExperts, France <sup>2</sup> University of Luxembourg <sup>3</sup> ANSSI, France

<sup>4</sup> Sorbonne Universités, UPMC Univ Paris 06, POLSYS, UMR 7606, LIP6, F-75005, Paris, France

{sonia.belaid,matthieu.rivain,abdul.taleb}@cryptoexperts.com

<sup>5</sup> jean-sebastien.coron@uni.lu <sup>6</sup> emmanuel.prouff@ssi.gouv.fr

Abstract. The masking countermeasure is among the most powerful countermeasures to counteract side-channel attacks. Leakage models have been exhibited to theoretically reason on the security of such masked implementations. So far, the most widely used leakage model is the probing model defined by Ishai, Sahai, and Wagner at (CRYPTO 2003). While it is advantageously convenient for security proofs, it does not capture an adversary exploiting full leakage traces as, e.g., in horizontal attacks. Those attacks target the multiple manipulations of the same share to reduce noise and recover the corresponding value. To capture a wider class of attacks another model was introduced and is referred to as the random probing model. From a leakage parameter p, each wire of the circuit leaks its value with probability p. While this model much better reflects the physical reality of side channels, it requires more complex security proofs and does not yet come with practical constructions.

In this paper, we define the first framework dedicated to the random probing model. We provide an automatic tool, called VRAPS, to quantify the random probing security of a circuit from its leakage probability. We also formalize a composition property for secure random probing gadgets and exhibit its relation to the strong non-interference (SNI) notion used in the context of probing security. We then revisit the expansion idea proposed by Ananth, Ishai, and Sahai (CRYPTO 2018) and introduce a compiler that builds a random probing secure circuit from small base gadgets achieving a random probing expandability property. We instantiate this compiler with small gadgets for which we verify the expected properties directly from our automatic tool. Our construction can tolerate a leakage probability up to  $2^{-8}$ , against  $2^{-25}$  for the previous construction, with a better asymptotic complexity.

Keywords: Compiler, Masking, Automated verification, Random probing model

#### 1 Introduction

Most cryptographic algorithms are assumed to be secure against *black-box* attacks where the adversary is limited to the knowledge of some inputs and outputs to recover the manipulated secrets. However, as revealed in the late nineties [21], when implemented on physical devices, they become vulnerable to the more powerful *side-channel attacks* which additionally exploit the physical emanations such as temperature, time, power consumption, electromagnetic radiations.

As such attacks may only require cheap equipment and can be easily mounted in a short time interval, the community had to adapt quickly by looking for efficient countermeasures. The most widely deployed approach to counteract side-channel attacks was simultaneously introduced in 1999 by Chari et al. [12] and by Goubin and Patarin [18] and is now called *masking*. Basically, the idea is to split each sensitive variable x of the implementation into n shares such that n-1 of them are generated uniformly at random and the last one is computed as the combination of x and all the previous shares according to some group law \*. When \* is the (bitwise) addition, we talk about *linear sharing* (aka Boolean masking). The adversary thus needs to get information on all the shares of x to recover information on the sensitive value. This countermeasure is really simple to implement for linear operations which are simply applied on each share separately. However, things are getting trickier for non-linear operations where it is impossible to compute the result without combining shares.

To reason about the security of masked implementations, the community introduced leakage models. One of the most broadly used is the *probing model*, introduced by Ishai, Sahai, and Wagner [20]. In a nutshell, a circuit is claimed to be *t*-probing secure if the exact values of any set of *t* intermediate variables do not reveal any information on the secrets. As leakage traces are assumed to reveal noisy functions of the manipulated data, this model is motivated by the difficulty to recover information from the combination of *t* variables from their noisy functions in masking schemes (as *t* grows). Nevertheless, the probing model fails to capture the huge amount of information resulting from the leakage of all manipulated data, and in particular from the repeated manipulation of identical values (see horizontal attacks in [7]). Therefore, after a long sequence of works building and analyzing masking schemes with respect to their security in the probing model [25, 15, 9], the community is now looking for security in more practical models.

The noisy leakage model was originally considered by Chari et al. in [12] and was later formalized by Prouff and Rivain in [24] as a specialization of the only computation leaks model [23] in order to better capture the reality of the physical leakage. Informally, a circuit is secure in the noisy leakage model if the adversary cannot recover the secrets from a noisy function of each intermediate variable of the implementation. While realistic, this model is not convenient for security proofs, and therefore masking schemes continued to be verified in the probing model relying on the not tight reduction that was formally established by Duc, Dziembowski, and Faust [17].

The latter reduction actually came with an intermediate leakage model, called *random probing model*, to which the security in the noisy leakage model reduces to. In the random probing model, each intermediate variable leaks with some constant leakage probability *p*. A circuit is secure in this model if there is a negligible probability that these leaking wires actually reveal information on the secrets. It is worth noting that this notion advantageously captures the horizontal attacks which exploit the repeated manipulations of variables throughout the implementation. Classical probing-secure schemes are also secure in the random probing model but the tolerated leakage probability (a.k.a. leakage rate) might not be constant which is not satisfactory from a practical viewpoint. Indeed, in practice the side-channel noise might not be customizable by the implementer.

Only a few constructions [1, 3, 2] tolerate a constant leakage probability. These three constructions are conceptually involved and their practical instantiation is not straightforward. The first one from Ajtai et al. and its extension [3] are based on expander graphs. The tolerated probability is not made explicit. The third work [2] is based on multi-party computation protocols and an expansion strategy; the tolerated probability is around  $2^{-26}$  and for a circuit with |C| gates, the complexity is  $\mathcal{O}(|C| \cdot \operatorname{poly}(\kappa))$  for some parameter  $\kappa$  but the polynomial is not made explicit.

Following the long sequence of works relying on the probing security, formal tools have recently been built to supervise the development of masking implementations proven secure in the probing model. Namely, verification tools are now able to produce a security proof or identify potential attacks from the description of a masked implementation at up to some masking orders (i.e., < 5) [4, 14, 11]. In the same vein, compilers have been built to automatically generate masked

implementations at any order given the high level description of a primitive [5, 11, 10]. Nevertheless, no equivalent framework has yet been proposed to verify the security of implementations in the random probing model.

**Our contributions.** In this paper, we aim to fill this huge gap by providing a framework to verify, compose, and build random probing secure circuits from simple gadgets. Our contributions are three-fold.

Automatic verification tool. As a first contribution, we define a verification method that we instantiate in a tool to automatically exhibit the random probing security parameters of any small circuit defined with addition and multiplication gates whose wires leak with some probability p. In a nutshell, a circuit is (p, f)-random probing secure if it leaks information on the secret with probability f(p), where f(p) is the failure probability function. From these notations, our tool named VRAPS (for Verifier of Random Probing Security), based on top of a set of rules that were previously defined to verify the probing security of implementations [4], takes as input the description of a circuit and outputs an upper bound on the failure probability function. While it is limited to small circuits by complexity, the state-of-the-art shows that verifying those circuits can be particularly useful in practice (see e.g. the maskVerif tool [4]), for instance to verify gadgets and then deduce global security through composition properties and/or low-order masked implementations. The source code of VRAPS is publicly available.<sup>7</sup>

Composition and expanding compiler. We introduce a composition security property to make gadgets composable in a global random probing secure circuit. We exhibit the relation between this new random probing composability (RPC) notion and the strong non-interference (SNI) notion which is widely used in the context of probing security [5]. Then, we revisit the modular approach of Ananth, Ishai, and Sahai [2] which uses an expansion strategy to get random probing security from a multi-party computation protocol. We introduce the expanding compiler that builds random probing secure circuits from small base gadgets. We formalize the notion of random probing expandability (RPE) and show that a base gadget satisfying this notion can be securely used in the expanding compiler to achieve arbitrary/composable random probing security. As a complementary contribution, our verification tool, VRAPS, is extended to verify the newly introduced RPC and RPE properties.

Instantiation. We instantiate the expanding compiler with new constructions of simple base gadgets that fulfill the desired RPE property, which is verified by VRAPS. For a security level  $\kappa$ , our instantiation achieves a complexity of  $\mathcal{O}(\kappa^{7.5})$  and tolerates a constant leakage probability  $p \approx$  $0.0045 > 2^{-8}$ . In comparison, and as a side contribution, we provide a precise analysis of the construction from [2] and show that it achieves an  $\mathcal{O}(\kappa^{8.2})$  complexity for a much lower tolerated leakage probability ( $p \approx 2^{-26}$ ). Finally, we note that our framework probably enables more efficient constructions based on different base gadgets; we leave such optimizations open for future works.

#### 2 Preliminaries

Along the paper,  $\mathbb{K}$  shall denote a finite field. For any  $n \in \mathbb{N}$ , we shall denote [n] the integer set  $[n] = [1, n] \cap \mathbb{Z}$ . For any tuple  $\boldsymbol{x} = (x_1, \ldots, x_n) \in \mathbb{K}^n$  and any set  $I \subseteq [n]$ , we shall denote

<sup>&</sup>lt;sup>7</sup> See https://github.com/CryptoExperts/VRAPS

$\boldsymbol{x}|_{I} = (x_{i})_{i \in I}$ . Any two probability distributions  $D_{1}$  and  $D_{2}$  are said  $\varepsilon$ -close, denoted  $D_{1} \approx_{\varepsilon} D_{2}$ , if their statistical distance is upper bounded by  $\varepsilon$ , that is

$$SD(D_1; D_2) := \frac{1}{2} \sum_x |p_{D_1}(x) - p_{D_2}(x)| \le \varepsilon$$

,

where  $p_{D_1}(\cdot)$  and  $p_{D_1}(\cdot)$  denote the probability mass functions of  $D_1$  and  $D_2$ .

#### 2.1 Circuit Compilers

In this paper, an *arithmetic circuit* over a field  $\mathbb{K}$  is a labeled directed acyclic graph whose edges are *wires* and vertices are *arithmetic gates* processing operations over  $\mathbb{K}$ . We consider three types of arithmetic gate:

- an addition gate, of fan-in 2 and fan-out 1, computes an addition over  $\mathbb{K}$ ,

- a multiplication gate, of fan-in 2 and fan-out 1, computes a multiplication over  $\mathbb{K}$ ,

- a copy gate, of fan-in 1 and fan-out 2, outputs two copies of its input.

A randomized arithmetic circuit is equipped with an additional type of gate:

- a random gate, of fan-in 0 and fan-out 1, outputs a fresh uniform random value of K.

A (randomized) arithmetic circuit is further formally composed of input gates of fan-in 0 and fanout 1 and output gates of fan-in 1 and fan-out 0. Evaluating an  $\ell$ -input *m*-output circuit *C* consists in writing an input  $\boldsymbol{x} \in \mathbb{K}^{\ell}$  in the input gates, processing the gates from input gates to output gates, then reading the output  $\boldsymbol{y} \in \mathbb{K}^m$  from the output gates. This is denoted by  $\boldsymbol{y} = C(\boldsymbol{x})$ . During the evaluation process, each wire in the circuit is assigned with a value on  $\mathbb{K}$ . We call the tuple of all these wire values a *wire assignment* of *C* (on input  $\boldsymbol{x}$ ).

**Definition 1 (Circuit Compiler).** A circuit compiler is a triplet of algorithms (CC, Enc, Dec) defined as follows:

- CC (circuit compilation) is a deterministic algorithm that takes as input an arithmetic circuit C and outputs a randomized arithmetic circuit  $\hat{C}$ .

- Enc (input encoding) is a probabilistic algorithm that maps an input  $x \in \mathbb{K}^{\ell}$  to an encoded input  $\widehat{x} \in \mathbb{K}^{\ell'}$ .

- Dec (output decoding) is a deterministic algorithm that maps an encoded output  $\widehat{y} \in \mathbb{K}^{m'}$  to a plain output  $y \in \mathbb{K}^m$ .

These three algorithms satisfy the following properties:

- Correctness: For every arithmetic circuit C of input length  $\ell$ , and for every  $x \in \mathbb{K}^{\ell}$ , we have

$$\Pr\left(\mathsf{Dec}(\widehat{C}(\widehat{x})) = C(x) \mid \widehat{x} \leftarrow \mathsf{Enc}(x)\right) = 1, \text{ where } \widehat{C} = \mathsf{CC}(C).$$

- **Efficiency:** For some security parameter  $\lambda \in \mathbb{N}$ , the running time of  $\mathsf{CC}(C)$  is  $\mathsf{poly}(\lambda, |C|)$ , the running time of  $\mathsf{Enc}(\boldsymbol{x})$  is  $\mathsf{poly}(\lambda, |\boldsymbol{x}|)$  and the running time of  $\mathsf{Dec}(\widehat{\boldsymbol{y}})$  is  $\mathsf{poly}(\lambda, |\widehat{\boldsymbol{y}}|)$ , where  $\mathsf{poly}(\lambda, q) = O(\lambda^{k_1} q^{k_2})$  for some constants  $k_1, k_2$ .

#### 2.2 Linear Sharing and Gadgets

In the following, the *n*-linear decoding mapping, denoted LinDec, refers to the function  $\bigcup_n \mathbb{K}^n \to \mathbb{K}$  defined as

$\mathsf{LinDec}: (x_1, \ldots, x_n) \mapsto x_1 + \cdots + x_n ,$

for every  $n \in \mathbb{N}$  and  $(x_1, \ldots, x_n) \in \mathbb{K}^n$ . We shall further consider that, for every  $n, \ell \in \mathbb{N}$ , on input  $(\hat{x}_1, \ldots, \hat{x}_\ell) \in (\mathbb{K}^n)^\ell$  the *n*-linear decoding mapping acts as

LinDec :

$$(\widehat{x}_1, \ldots, \widehat{x}_\ell) \mapsto (\text{LinDec}(\widehat{x}_1), \ldots, \text{LinDec}(\widehat{x}_\ell))$$

.

Let us recall that for some tuple  $\hat{x} = (x_1, \ldots, x_n) \in \mathbb{K}^n$  and for some set  $I \subseteq [n]$ , the tuple  $(x_i)_{i \in I}$  is denoted  $\hat{x}|_I$ .

**Definition 2 (Linear Sharing).** Let  $n, \ell \in \mathbb{N}$ . For any  $x \in \mathbb{K}$ , an *n*-linear sharing of x is a random vector  $\hat{x} \in \mathbb{K}^n$  such that  $\text{LinDec}(\hat{x}) = x$ . It is said to be uniform if for any set  $I \subseteq [n]$  with |I| < n the tuple  $\hat{x}|_I$  is uniformly distributed over  $\mathbb{K}^{|I|}$ . A *n*-linear encoding is a probabilistic algorithm LinEnc which on input a tuple  $\mathbf{x} = (x_1, \ldots, x_\ell) \in \mathbb{K}^\ell$  outputs a tuple  $\hat{\mathbf{x}} = (\hat{x}_1, \ldots, \hat{x}_\ell) \in (\mathbb{K}^n)^\ell$  such that  $\hat{x}_i$  is a uniform *n*-sharing of  $x_i$  for every  $i \in [\ell]$ .

In the following, we shall call an  $(n\text{-share}, \ell\text{-to-}m)$  gadget, a randomized arithmetic circuit that maps an input  $\hat{x} \in (\mathbb{K}^n)^{\ell}$  to an output  $\hat{y} \in (\mathbb{K}^n)^m$  such that  $x = \text{LinDec}(\hat{x}) \in \mathbb{K}^{\ell}$  and  $y = \text{LinDec}(\hat{y}) \in \mathbb{K}^m$  satisfy y = g(x) for some function g. In this paper, we shall consider gadgets for three types of functions (corresponding to the three types of gates): the addition  $g: (x_1, x_2) \mapsto x_1 + x_2$ , the multiplication  $g: (x_1, x_2) \mapsto x_1 \cdot x_2$  and the copy  $g: x \mapsto (x, x)$ . We shall generally denote such gadgets  $G_{\text{add}}$ ,  $G_{\text{mult}}$  and  $G_{\text{copy}}$  respectively.

**Definition 3 (Standard Circuit Compiler).** Let  $\lambda \in \mathbb{N}$  be some security parameter and let  $n = \text{poly}(\lambda)$ . Let  $G_{add}$ ,  $G_{mult}$  and  $G_{copy}$  be n-share gadgets respectively for the addition, multiplication and copy over  $\mathbb{K}$ . The standard circuit compiler with sharing order n and base gadgets  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$  is the circuit compiler (CC, Enc, Dec) satisfying the following:

- 1. The input encoding Enc is an n-linear encoding.

- 2. The output decoding Dec is the n-linear decoding mapping LinDec.

- 3. The circuit compilation CC consists in replacing each gate in the original circuit by an n-share gadget with corresponding functionality (either  $G_{add}$ ,  $G_{mult}$  or  $G_{copy}$ ), and each wire by a set of n wires carrying a n-linear sharing of the original wire. If the input circuit is a randomized arithmetic circuit, each of its random gates is replaced by n random gates, which duly produce a n-linear sharing of a random value.

For such a circuit compiler, the correctness and efficiency directly holds from the correctness and efficiency of the gadgets  $G_{add}$ ,  $G_{mult}$  and  $G_{copy}$ .

#### 2.3 Random Probing Leakage

Let  $p \in [0, 1]$  be some constant leakage probability parameter. This parameter is sometimes called *leakage rate* in the literature. Informally, the *p*-random probing model states that during the evaluation of a circuit *C* each wire leaks its value with probability *p* (and leaks nothing otherwise), where all the wire leakage events are mutually independent.

In order to formally define the random-probing leakage of a circuit, we shall consider two probabilistic algorithms: - The *leaking-wires sampler* takes as input a randomized arithmetic circuit C and a probability  $p \in [0, 1]$ , and outputs a set  $\mathcal{W}$ , denoted as

$\mathcal{W} \leftarrow \mathsf{LeakingWires}(C, p)$ ,

where  $\mathcal{W}$  is constructed by including each wire label from the circuit C with probability p to  $\mathcal{W}$  (where all the probabilities are mutually independent).

- The assign-wires sampler takes as input a randomized arithmetic circuit C, a set of wire labels  $\mathcal{W}$  (subset of the wire labels of C), and an input  $\boldsymbol{x}$ , and it outputs a  $|\mathcal{W}|$ -tuple  $\boldsymbol{w} \in (\mathbb{K} \cup \{\bot\})^{|\mathcal{W}|}$ , denoted as

$$oldsymbol{w} \leftarrow \mathsf{AssignWires}(C, \mathcal{W}, oldsymbol{x})$$

,

where  $\boldsymbol{w}$  corresponds to the assignments of the wires of C with label in  $\mathcal{W}$  for an evaluation on input  $\boldsymbol{x}$ .

We can now formally define the random probing leakage of a circuit.

**Definition 4 (Random Probing Leakage).** The *p*-random probing leakage of a randomized arithmetic circuit C on input  $\mathbf{x}$  is the distribution  $\mathcal{L}_p(C, \mathbf{x})$  obtained by composing the leaking-wires and assign-wires samplers as

$$\mathcal{L}_p(C, \boldsymbol{x}) \stackrel{id}{=} \mathsf{AssignWires}(C, \mathsf{LeakingWires}(C, p), \boldsymbol{x})$$

.

Remark 1. By convention the output wires of C (*i.e.* the wires incoming output gates) are excluded by the LeakingWires sampler whereas the input wires of C (*i.e.* the wires connecting input gates to subsequent gates) are included. Namely the output set  $\mathcal{W}$  of LeakingWires(C, p) does not include any output wire label of C. This is because when composing several circuits (or gadgets), the output wires of a circuit are the input wires in a next circuit. This also relates to the widely admitted *only computation leaks* assumption [23]: the processing of a gate leaks information on its input values (and information on the output can be captured through information on the input).

**Definition 5 (Random Probing Security).** A randomized arithmetic circuit C with  $\ell \cdot n \in \mathbb{N}$ input gates is  $(p, \varepsilon)$ -random probing secure with respect to encoding Enc if there exists a simulator Sim such that for every  $\mathbf{x} \in \mathbb{K}^{\ell}$ :

$$\operatorname{Sim}(C) \approx_{\varepsilon} \mathcal{L}_p(C, \operatorname{Enc}(\boldsymbol{x}))$$

. (1)

A circuit compiler (CC, Enc, Dec) is  $(p, \varepsilon)$ -random probing secure if for every (randomized) arithmetic circuit C the compiled circuit  $\hat{C} = CC(C)$  is  $(p, |C| \cdot \varepsilon)$ -random probing secure where |C| is the size of original circuit.

As in [2] we shall consider a simulation with abort. In this approach, the simulator first calls the leaking-wires sampler to get a set  $\mathcal{W}$  and then either aborts (or fails) with probability  $\varepsilon$  or outputs the exact distribution of the wire assignment corresponding to  $\mathcal{W}$ . Formally, for any leakage probability  $p \in [0, 1]$ , the simulator Sim is defined as

$$\mathsf{Sim}(\widehat{C}) = \mathsf{Sim}\mathsf{AW}(\widehat{C}, \mathsf{LeakingWires}(\widehat{C}, p)) \tag{2}$$

where SimAW, the *wire assignment simulator*, either returns  $\perp$  (simulation failure) or a perfect simulation of the requested wires. Formally, the experiment

$$\mathcal{W} \leftarrow \mathsf{LeakingWires}(\widehat{C}, p)$$

out  $\leftarrow \mathsf{SimAW}(\widehat{C}, \mathcal{W})$

leads to

$\Pr[out = \bot] = \varepsilon \quad \text{and} \quad \left(out \mid out \neq \bot\right) \stackrel{\text{id}}{=} \left(\mathsf{AssignWires}(\widehat{C}, \mathcal{W}, \mathsf{Enc}(\boldsymbol{x})) \mid out \neq \bot\right) \,. \tag{3}$

It is not hard to see that if we can construct such a simulator SimAW for a compiled circuit  $\widehat{C}$ , then this circuit is  $(p, \varepsilon)$ -random probing secure.

#### **3** Formal Verification

In this section we show how to compute the simulation failure probability f(p) as a function of the leakage probability p for the base gadgets. Since even for simple gadgets this tasks would be difficult to perform by hand, we use a formal verification tool to compute f(p).

#### 3.1 Simulation Failure probability

We first derive an upper bound on the simulation failure probability as a function of the leakage probability p. We consider a compiled circuit  $\hat{C}$  composed of s wires labeled from 1 to s and a simulator SimAW as defined in previous section. For any sub-set  $\mathcal{W} \subseteq [s]$  we denote by  $\delta_{\mathcal{W}}$  the value defined as follows:

$$\delta_{\mathcal{W}} = \begin{cases} 1 & \text{if } \mathsf{Sim}\mathsf{AW}(\widehat{C}, \mathcal{W}) = \bot, \\ 0 & \text{otherwise.} \end{cases}$$

The simulation failure probability  $\varepsilon$  in (3) can then be explicitly expressed as a function of p. Namely, we have  $\varepsilon = f(p)$  with f defined for every  $p \in [0, 1]$  by:

$$f(p) = \sum_{\mathcal{W} \subseteq [s]} \delta_{\mathcal{W}} \cdot p^{|\mathcal{W}|} \cdot (1-p)^{s-|\mathcal{W}|} \quad .$$

(4)

Letting  $c_i$  be the number of sub-sets  $\mathcal{W} \subseteq [s]$  of cardinality *i* for which  $\delta_{\mathcal{W}} = 1$ , namely for which the simulation fails, we have  $c_i = \sum_{|\mathcal{W}|=i} \delta_{\mathcal{W}}$  and hence (4) simplifies to

$$f(p) = \sum_{i=1}^{s} c_i \cdot p^i \cdot (1-p)^{s-i} .$$

(5)

For any circuit  $\widehat{C}$  achieving *t*-probing security, the values  $\delta_{\mathcal{W}}$  with  $|\mathcal{W}| \leq t$  are equal to zero, and therefore the corresponding  $c_i$ 's are zero, which implies the following simplification:

$$f(p) = \sum_{i=t+1}^{s} c_i \cdot p^i \cdot (1-p)^{s-i}$$

Moreover, by definition, the coefficients  $c_i$  satisfy:

$$c_i \leqslant \binom{s}{i} \tag{6}$$

which leads to the following upper-bound for f(p):

$$f(p) \leq \sum_{i=t+1}^{s} {s \choose i} \cdot p^{i} \cdot (1-p)^{s-i}$$

Example: evaluating f(p) for the 2-share ISW multiplication gadget (ISW-2). This gadget takes at input the 2-sharings  $(x_0, x_1)$  and  $(y_0, y_1)$  of x and y respectively, and outputs the 2-sharing

$$(z_0, z_1) = (x_0 \cdot y_0 + r_0, x_1 \cdot y_1 + r_0 + x_0 \cdot y_1 + x_1 \cdot y_0)$$

where  $r_0$  is a random value. The processing is composed of the following intermediate results, where each variable is assigned a wire:

When the same variable is involved as input of several operations, a copy gadget (with 1 input wire and 2 output wires) is applied to duplicate it. Consequently, each new use of the same variable as input of an operation adds 2 wires to the final count of overall wires. It may be checked that the circuit corresponding to ISW-2 is composed of 21 wires, excluding the 2 output wires. Since it is 1-SNI but not 2-SNI, every set with a single wire can be simulated, which is not the case for all pairs of wires. Actually, 51 among the latter pairs cannot be simulated. If we continue the test for the sets of cardinality from 3 to 21, we get the following list of coefficients  $c_i$ ,  $1 \le i \le 21$ , computed with the verification tool described in the next section: 0, 51, 754, 4827, 18875, 52994, 115520, 203176, 293844, 352702, 352715, 293930, 203490, 116280, 54264, 20349, 5985, 1330, 210, 21, 1. Directly injecting these coefficients in (5) gives the expression of f(p) for ISW-2.

#### 3.2 Verification method

For any compiled circuit  $\widehat{C}$  and any simulator defined as in Section 2.3, the computation of the function f(p) for any probability p essentially amounts to computing the values of the coefficients  $c_i$ 's appearing in (5). If no assumption is made on the circuit, this task seems difficult to carry out by hand. Actually, it may be checked that an exhaustive testing of all the possible tuples of wires for a gadget with s wires has complexity lower bounded by  $2^s$ , which gives  $2^{21}$  for a simple gadget like the ISW multiplication gadget with two shares per input. Here, we introduce a verification tool, that we call VRAPS, enabling to automatically test the perfect simulation for any set of wires of size lower than or equal to some threshold  $\beta$ . The role of the latter threshold is simply to control the verification duration (which can be long if the circuit to test is complex). Our tool implicitly defines a simulator that may fail with a probability  $\varepsilon = f(p)$  satisfying (5).

The verification tool takes as input the representation of a compiled circuit  $\widehat{C}$  and a test parameter  $\beta$ , and outputs the list of coefficients  $c_1, ..., c_\beta$ . It is assumed that  $\widehat{C}$  takes as input the *n*-linear encoding  $\text{Enc}(\boldsymbol{x})$  of vector  $\boldsymbol{x} = (x_1, \ldots, x_\ell)$  defined in  $\mathbb{K}^\ell$ . It is moreover assumed that  $\widehat{C}$ is composed of *s* wires respectively denoted by  $w_1, ..., w_s$ . In the following, we consider *s*-tuples in the form of  $u = (u_1, \ldots, u_s) \in \{0, 1\}^s$  together with the common rule  $u' \subset u$  iff for every  $i \in [s]$ ,  $u'_i = 1 \Rightarrow u_i = 1$  (in this case u' will be said to be included in u). An *s*-tuple u for which there exists an assignment of the wires in  $\mathcal{W} = \{w_i; i \in [s], u_i = 1\}$  such that the simulation fails shall be called a *failure tuple*. Such a tuple shall be said to be *incompressible* if no tuple  $t' \subset t$  is a failure tuple. The main idea of the proposed verification tool is to test the simulation failure only on incompressible failure tuples whose Hamming weight ranges from 1 to  $\beta$ . The steps are described in Algorithm 1.

#### Algorithm 1 Verification tool

| <b>Input:</b> a compiled circuit $\hat{C}$ with <i>s</i> wires and a thr<br><b>Output:</b> a list of $\beta$ coefficients $c_1,, c_{\beta}$ | reshold $\beta \leqslant s$                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|                                                                                                                                             |                                                                          |

| 1: $\ell_p \leftarrow []$                                                                                                                   | $\triangleright$ will be used to store a list of failure tuples          |

| 2: $\boldsymbol{c} \leftarrow (0, \dots, 0)$                                                                                                | $\triangleright$ will be used to store the output coefficients           |

| 3: for $h = 1$ to $\beta$ do                                                                                                                |                                                                          |

| 4: $\ell_h \leftarrow listTuples(s,h)$                                                                                                      | $\triangleright$ list of s-tuples of Hamming weight h                    |

| 5: $(\ell_h^p, \ell_h^{f_1}) \leftarrow eliminateFromSmaller(\ell_h, \ell_p)$                                                               | $\triangleright$ select tuples including an incompressible failure tuple |

| 6: $\ell_h^{f_2} \leftarrow failureTest(\widehat{C}, \ell_h^p)$                                                                             | $\triangleright$ identify failure tuples in $\ell_h^p$                   |

| $7: \qquad \ell_p \leftarrow \ell_p \cup \ell_h^{f_2}$                                                                                      | $\triangleright$ update list of incompressible failure tuples            |

| 8: $oldsymbol{c} \leftarrow updateCoeffs(oldsymbol{c}, \ell_h^{f_1} \cup \ell_h^{f_2})$                                                     | $\triangleright$ update coefficients                                     |

| 9: end for                                                                                                                                  |                                                                          |

| 10: return <i>c</i>                                                                                                                         |                                                                          |

The function listTuples outputs the list of all s-tuples with Hamming weight h with  $h \in [s]$ . The function eliminateFromSmaller takes as input the list  $\ell_h$  of current tuples of Hamming weight h and the list of incompressible failure tuples  $\ell_p$ . It returns two lists:

- $-\ell_h^{f_1}$ : the elements of  $\ell_h$  which are not incompressible (*i.e.* which include at least one element from  $\ell_p$ )

- $-\ell_h^p$ : the elements of  $\ell_h$  which are incompressible (*i.e.*  $\ell_h \setminus \ell_h^{f_1}$ )

The function failureTest takes as input the second list  $\ell_h^p$  and checks if a perfect simulation can be achieved for each wire family  $\mathcal{W}$  corresponding to a tuple in  $\ell_h^p$ . Basically, for each wire family, a sequence of rules taken from maskVerif [4] is tested to determine whether  $\mathcal{W}$  can be perfectly simulated. It outputs  $\ell_h^{f_2}$ , the list of incompressible failure *s*-tuples of Hamming weight *h*. In a nutshell, each wire  $w_i$  in  $\mathcal{W}$  is considered together with the algebraic expression  $\varphi_i(\cdot)$  describing its assignment by  $\widehat{C}$  as a function of the circuit inputs and the random values returned by the random gates, then the three following rules are successively and repeatedly applied on all the wires families  $\mathcal{W}$  (see [4] for further details):

- rule 1: check whether all the expressions  $\varphi_i(\cdot)$  corresponding to wires  $w_i$  in  $\mathcal{W}$  contain all the shares of at least one of the coordinates of  $\boldsymbol{x}$ ;

- rule 2: for every  $\varphi_i(\cdot)$ , check whether a random r (*i.e.* an output of a random gate) additively masks a sub-expression e (which does not involve r) and appears nowhere else in the other  $\varphi_i(\cdot)$

with  $j \neq i$ ; in this case replace the sum of the so-called sub-expression and r by r, namely  $e + r \leftarrow r;$

rule 3: apply mathematical simplifications on the tuple.

Function updateCoeffs takes as input the current array of  $\beta$  coefficients  $c_i$  for  $1 \leq i \leq \beta$  and the concatenation of both lists of potential failure tuples  $\ell_h^{f_1}$  and  $\ell_h^{f_2}$ . For each failure tuple, these coefficients are updated.

Link with the tool maskVerif. This tool was introduced in [4] to automatically and formally verify higher-order masking implementations, and has further been improved to verify the t-NI and t-SNI security properties. Essentially, this tool verifies each property by analyzing the dependency of sets of fixed number of wires (say t) with a specific number of input shares. In our case, the size of the wires' sets which must be tested (to decide whether the corresponding coefficient  $c_i$  must be incremented or not) is a priori not bounded, or (for efficiency reasons) is bounded by a threshold  $\beta$ that is not a security parameter but an efficiency one. Moreover, our testing must take intermediate failures into account. Although maskVerif does not directly allows to answer our specific needs, we could have exploited its rules directly in our tool with dedicated add-ons. However we wanted to provide an easy-to-understand global tool and we therefore re-implemented the common parts (essentially those enabling to decided whether a given set of wires can be simulated or not).

**Optimization 1 (grouping the wires).** In most of the compiled circuits that we usually considered, several wires are always assigned the same value. Grouping those wires altogether allows us to significantly reduce the number of wires to be considered by the verification tool. Let us denote by  $s^*$  the number of groups, by  $\alpha_i$  the size of the *i*-th group and by  $w_i$  a representative of the *i*-th group. Then, Algorithm 1 can be almost directly applied to the shortened list of  $s^*$  wires (instead of s). The single main difference is that the updateCoeffs procedure also takes into account the weights  $\alpha_i$  when updating the coefficients  $c_i$ . For instance, considering h = 3, and the tuple (1, 1, 1, 0, ..., 0)with respective weights  $\alpha_1 = 2$  (for  $w_1$ ),  $\alpha_2 = 1$  (for  $w_2$ ) and  $\alpha_3 = 3$  (for  $w_3$ ), the function would increase  $c_3$  with 6,  $c_4$  with 6,  $c_5$  with 4 and  $c_6$  with 1. The latter evaluation is performed using a recursive function which evaluates the number of partitions of an integer j into h parts with the constraints that each part should be at least one. When this optimization is applied, it may be observed that the updateCoeffs procedure also starts to update some coefficients  $c_i$  for  $i > \beta$ . These updated coefficients can be used as lower bounds of the final  $c_i$  values. They will be called  $c_i^{inf}$  in the rest of this paper.  $c_i^{sup}$  will be used to denote the maximal possible value for  $c_i$ , namely the binomial coefficient  $\binom{s}{i}$ .

Optimization 2 (using the 'longest failure tuple'). To build all the potential failure tuples, a strategy consists in exhaustively testing all the s-tuples with Hamming weight below the Hamming weight of the longest *incompressible attack tuple*. Once this set, let say  $\mathcal{U}_{inc}$ , has been built, the set of all potential failure tuples can be deduced by executing the following procedure:

- for one  $u_{\text{inc}} \in \mathcal{U}_{\text{inc}}$  define  $\mathcal{U}_{\text{failure}} = \{u \in \{0, 1\}^s; u_{\text{inc}} \subset u\}.$ - for every new  $u_{\text{inc}} \in \mathcal{U}_{\text{inc}}$ , update  $\mathcal{U}_{\text{failure}} = \mathcal{U}_{\text{failure}} \cup \{u \in \{0, 1\}^s; u_{\text{inc}} \subset u\}$

**Implementation.** An implementation of Algorithm 1 has been developed in Python. This tool, named VRAPS, has been open sourced at:

https://github.com/CryptoExperts/VRAPS

**Small examples.** In order to illustrate our automatic verification of gadgets in the random probing model, we give the list of coefficients and the subsequent failure functions obtained for three known gadgets from the literature, namely the 2-share and 3-share multiplication gadgets introduced by Ishai, Sahai, and Wagner in [20] and a 3-share multiplication gadget from [8] with an optimal number of random variables to achieve security in the 2-probing model. Descriptions for these three gadgets are given below together with an approximation of the corresponding failure function f produced by our tool. Operations are performed according to the standard priority rules. Sharings  $\boldsymbol{x}$  and  $\boldsymbol{y}$  denote the inputs, sharings  $\boldsymbol{z}$  denote the outputs, and  $r_i$  are random variables. Copy gates are implicit when variables are used more than once. Hereafter  $\mathcal{O}(p^5)$  is to be interpreted as p tends to 0.

2-share ISW multiplication gadget (ISW-2):

$$\begin{cases} z_0 = x_0 \cdot y_0 + r_0 \\ z_1 = x_1 \cdot y_1 + r_0 + x_0 \cdot y_1 + x_1 \cdot y_0 \end{cases} \Rightarrow f(p) = 51p^2 + 754p^3 + 4827p^4 + \mathcal{O}(p^5)$$

3-share multiplication gadget from [8] (EC16-3):

$$\begin{cases} z_0 = x_0 \cdot y_0 + r_0 + x_0 \cdot y_2 + x_2 \cdot y_0 \\ z_1 = x_1 \cdot y_1 + r_1 + x_0 \cdot y_1 + x_1 \cdot y_0 \\ z_2 = x_2 \cdot y_2 + r_0 + r_1 + x_1 \cdot y_2 + x_2 \cdot y_1 \end{cases} \Rightarrow f(p) = 1116p^3 + 44909p^4 + \mathcal{O}(p^5)$$

3-share ISW multiplication gadget (ISW-3):

$$\begin{cases} z_0 = x_0 \cdot y_0 + r_0 + r_1 \\ z_1 = x_1 \cdot y_0 + (x_0 \cdot y_1 + r_0) + x_1 \cdot y_1 + r_2 \\ z_2 = x_2 \cdot y_0 + (x_0 \cdot y_2 + r_1) + \\ (x_2 \cdot y_1 + (x_1 \cdot y_2 + r_2)) + x_2 \cdot y_2 \end{cases} \Rightarrow f(p) = 1219p^3 + 55756p^4 + \mathcal{O}(p^5)$$

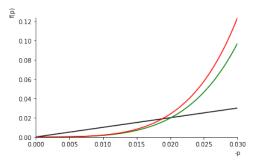

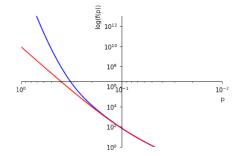

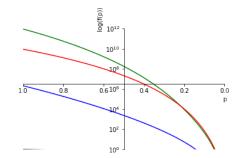

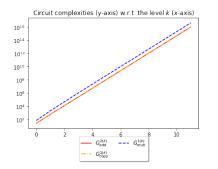

For our three examples, our verification tool (Algorithm 1) has been launched respectively with  $\beta = s = 21$  for ISW-2, with  $\beta = 9 < s = 57$  for ISW-3 and with  $\beta = 13 < s = 52$  for EC16-3. In the two later cases, the missing coefficients  $c_i$  with  $i > \beta$  have been either set to 0 or to  $\binom{s}{i}$ . This allowed us to define a lower bound  $f_{inf}$  and an upper bound  $f_{sup}$  for the functions f corresponding to ISW-3 and EC16-3. The behavior of these functions is plotted in Figures 1 to 3.

#### 4 Composition

This section aims to provide composition properties for random-probing secure gadgets. In a nutshell, we aim to show how to build random probing secure larger circuits from specific random probing secure building blocks.

#### 4.1 Random Probing Composability

We introduce hereafter the random probing composability notion for a gadget. In the following definition, for an *n*-share,  $\ell$ -to-*m* gadget, we denote by  $\mathbf{I}$  a collection of sets  $\mathbf{I} = (I_1, \ldots, I_\ell)$  with  $I_1 \subseteq [n], \ldots, I_\ell \subseteq [n]$  where  $n \in \mathbb{N}$  refers to the number of shares. For some  $\hat{\mathbf{x}} = (\hat{x}_1, \ldots, \hat{x}_\ell) \in (\mathbb{K}^n)^\ell$ , we then denote  $\hat{\mathbf{x}}|_{\mathbf{I}} = (\hat{x}_1|_{I_1}, \ldots, \hat{x}_\ell|_{I_\ell})$  where  $\hat{x}_i|_{I_i} \in \mathbb{K}^{|I_i|}$  is the tuple composed of the coordinates of the sharing  $\hat{x}_i$  of indexes included in  $I_i$ .

Fig. 1: Values taken by  $f_{inf}(p)$  for ISW-3 (red) and EC16-3 (green) compared to the function  $p \mapsto p$  (black).

Fig. 2: Values of  $\log(f_{inf}(p))$  (red) and  $\log(f_{sup}(p))$  (blue) for ISW-3.

Fig. 3: For values p ranging from 1 to 0, values of  $\log(f_{inf}(p))$  for ISW-3 (red) and EC16-3 (green) together with the values of  $\log(f(p))$  for ISW-2 (blue).

**Definition 6 (Random Probing Composability).** Let  $n, \ell, m \in \mathbb{N}$ . An *n*-share gadget G:  $(\mathbb{K}^n)^\ell \to (\mathbb{K}^n)^m$  is  $(t, p, \varepsilon)$ -random probing composable (RPC) for some  $t \in \mathbb{N}$  and  $p, \varepsilon \in [0, 1]$  if there exists a deterministic algorithm  $\operatorname{Sim}_1^G$  and a probabilistic algorithm  $\operatorname{Sim}_2^G$  such that for every input  $\widehat{x} \in (\mathbb{K}^n)^\ell$  and for every set collection  $J_1 \subseteq [n], \ldots, J_m \subseteq [n]$  of cardinals  $|J_1| \leq t, \ldots,$  $|J_m| \leq t$ , the random experiment

$$\mathcal{W} \leftarrow \text{LeakingWires}(G, p)$$

$$\boldsymbol{I} \leftarrow \text{Sim}_{1}^{G}(\mathcal{W}, \boldsymbol{J})$$

$$out \leftarrow \text{Sim}_{2}^{G}(\widehat{\boldsymbol{x}}|_{\boldsymbol{I}})$$

yields

$$\Pr\left(\left(|I_1| > t\right) \lor \ldots \lor \left(|I_\ell| > t\right)\right) \le \varepsilon \tag{7}$$

and

$$out \stackrel{id}{=} (AssignWires(G, W, \widehat{x}), \ \widehat{y}|_{J})$$

where  $\mathbf{J} = (J_1, \ldots, J_m)$  and  $\widehat{\mathbf{y}} = G(\widehat{\mathbf{x}})$ . Let  $f : \mathbb{R} \to \mathbb{R}$ . The gadget G is (t, f)-RPC if it is (t, p, f(p))-RPC for every  $p \in [0, 1]$ .

In the above definition, the first-pass simulator  $\mathsf{Sim}_1^G$  determines the necessary input shares (through the returned collection of sets I) for the second-pass simulator  $\mathsf{Sim}_2^G$  to produce a perfect simulation of the leaking wires defined by the set  $\mathcal{W}$  together with the output shares defined by the collection of sets J. Note that there always exists such a collection of sets I since  $I = ([n], \ldots, [n])$ trivially allows a perfect simulation whatever W and J. However, the goal of  $\text{Sim}_{1}^{G}$  is to return a collection of sets I with cardinals at most t. The idea behind this constraint is to keep the following composition invariant: for each gadget we can achieve a perfect simulation of the leaking wires plus t shares of each output sharing from t shares of each input sharing. We shall call *failure event* the event that at least one of the sets  $I_1, \ldots, I_{\ell}$  output of  $\text{Sim}_{1}^{G}$  has cardinality greater than t. When  $(t, p, \varepsilon)$ -RPC is achieved, the failure event probability is upper bounded by  $\varepsilon$  according to (7). A failure event occurs whenever  $\text{Sim}_{2}^{G}$  requires more than t shares of one input sharing to be able to produce a perfect simulation of the leaking wires (*i.e.* the wires with label in W) together with the output shares in  $\hat{y}|_{J}$ . Whenever such a failure occurs, the composition invariant is broken. In the absence of failure event, the RPC notion implies that a perfect simulation can be achieved for the full circuit composed of RPC gadgets. This is formally stated in the next theorem.

#### 4.2 Composition Security

**Theorem 1 (Composition).** Let  $t \in \mathbb{N}$ ,  $p, \varepsilon \in [0, 1]$ , and CC be a standard circuit compiler with  $(t, p, \varepsilon)$ -RPC base gadgets. For every (randomized) arithmetic circuit C composed of |C| gadgets, the compiled circuit CC(C) is  $(p, |C| \cdot \varepsilon)$ -random probing secure. Equivalently, the standard circuit compiler CC is  $(p, \varepsilon)$ -random probing secure.

*Proof.* Let  $\mathcal{W}$  denote the leaking wires of the randomized circuit  $\mathsf{CC}(C)$  with probability p for each wire. We now build a simulator Sim taking as inputs  $\mathsf{CC}(C)$  and  $\mathcal{W}$  and that perfectly simulates  $\mathcal{W}$  with probability at least  $(1 - |C| \cdot \varepsilon)$  from the simulators of the  $(t, p, \varepsilon)$ -RPC base gadgets.

We start with splitting set  $\mathcal{W}$  into |C| distinct subsets  $\mathcal{W}_i$  for  $i \in \{1, \ldots, |C|\}$  such that each  $\mathcal{W}_i$ stands for the output of LeakingWires when applied to the *i*'th gadget  $G_i$  of CC(C) with probability p. Then, we start from end gadgets whose outputs coincide with the circuit's outputs. We execute their  $Sim_1^{G_i}$  with  $\mathcal{W}_i$  and  $J = \emptyset$ , to get the sets I of required inputs. Then, we target their parents, that are gadgets whose outputs are inputs of end gadgets. For each such gadget  $G_i$ , we execute  $Sim_1^{G_i}$  with  $\mathcal{W}_i$  and J as defined by children sets I, to get the new sets I of required inputs. The simulation goes through the circuit from bottom to top by applying the  $Sim_1^G$  simulators to get the  $\mathcal{W}_i$  and I/J sets. The simulation fails if at least one set I is of cardinal greater than t. For |C|gadgets, this happens with probability  $1 - (1 - \varepsilon)^{|C|} \leq |C| \cdot \varepsilon$ . Otherwise, the simulation runs the  $Sim_2^G$  simulators from top to bottom by randomly picking the initial  $(x_i)_I$ , which completes the construction of our global simulator Sim.

#### 4.3 Relation with Standard Probing Composition Notions

We first reformulate the Strong Non-Interference notion introduced in [5] with the formalism used for our definition of the Random Probing Composability.

**Definition 7 (Strong Non-Interference (SNI)).** Let n,  $\ell$  and t be positive integers. An n-share gadget  $G : (\mathbb{K}^n)^\ell \to \mathbb{K}^n$  is t-SNI if there exists a deterministic algorithm  $\operatorname{Sim}_1^G$  and a probabilistic algorithm  $\operatorname{Sim}_2^G$  such that for every set  $J \subseteq [n]$  and subset  $\mathcal{W}$  of wire labels from G satisfying  $|\mathcal{W}| + |J| \leq t$ , the following random experiment with any  $\widehat{\mathbf{x}} \in (\mathbb{K}^n)^\ell$

$$I \leftarrow \mathsf{Sim}_1^G(\mathcal{W}, J)$$

out  $\leftarrow \mathsf{Sim}_2^G(\widehat{\boldsymbol{x}}|_{\boldsymbol{I}})$

yields

$$|I_1| \leqslant |\mathcal{W}|, \dots, |I_\ell| \leqslant |\mathcal{W}| \tag{8}$$

and

$$put \stackrel{id}{=} \left(\mathsf{AssignWires}(G, \mathcal{W}, \widehat{\boldsymbol{x}}), \ \widehat{\boldsymbol{y}}|_J\right) \tag{9}$$

where  $\mathbf{I} = (I_1, \ldots, I_\ell)$  and  $\widehat{\mathbf{y}} = G(\widehat{\mathbf{x}})$ .

Then, we demonstrate that gadgets satisfying the *t*-SNI notion are also random probing composable for specific values that we explicit in the following proposition, whose proof is available in Appendix A.

**Proposition 1.** Let n,  $\ell$  and t be positive integers and let G be a gadget from  $(\mathbb{K}^n)^{\ell}$  to  $\mathbb{K}^n$ . If G is t-SNI, then it is also  $(t/2, p, \varepsilon)$ -RPC for any probability p and  $\varepsilon$  satisfying:

$$\varepsilon = \sum_{i=\lfloor \frac{t}{2}+1 \rfloor}^{s} {\binom{s}{i}} p^{i} (1-p)^{s-i} \quad , \tag{10}$$

where s is the number of wires in G.

#### 4.4 Verification of Gadget Composability

Our random probing verification tool (Algorithm 1) can be easily extended to define a simulator for the  $(t, p, \varepsilon)$ -random probing composability of a gadget for some t and some p. This essentially amounts to extend Algorithm 1 inputs with a multi-set  $\mathcal{O}$  and to modify the failureTest procedure in order to test the simulation for each tuple in the input list  $\ell_n^p$  augmented with the outputs coordinates with indices in  $\mathcal{O}$ . Then, our extended algorithm is called for every set  $\mathcal{O}$  composed of at most t indices in each of the sets  $J_1, \ldots, J_m$ . The output for the call with input set  $\mathcal{O}$  is denoted by  $\mathbf{c}_{\mathcal{O}} = (c_1^{\mathcal{O}}, \ldots, c_{\beta}^{\mathcal{O}})$ . For our simulator construction, the probability  $\varepsilon$  satisfies

$$\varepsilon = \sum_{i=1}^{s} c_i \cdot p^i \cdot (1-p)^{s-i},$$

where s denotes the number of wires in the tested gadget. Moreover, the  $c_i$ 's satisfy  $c_i = \max_{\mathcal{O}} c_i^{\mathcal{O}}$ .

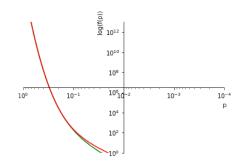

*Example.* As an illustration of the proposition, let us consider the well deployed 3-share ISW multiplication gadget  $G_{\text{ISW-3}} : (\mathbb{K}^3)^2 \to (\mathbb{K}^3)$  displayed in Section 3 and satisfying 2-SNI from [5]. Considering implicit copy gadgets that are mandatory in the circuit definition when a variable is reused, the corresponding circuit contains s = 57 wires. From Proposition 1, this gadget is also  $(1, p, \varepsilon_{\text{ISW}})$ -RPC for any probability p and  $\varepsilon_{\text{ISW}}$  such that

$$\varepsilon_{\rm ISW} = \sum_{i=2}^{57} {s \choose i} p^i (1-p)^{57-i}.$$

Figure 4 displays for  $p \in [0, 1]$  the values taken by  $\varepsilon_{\text{ISW}}$  (in red). It also displays (in green) the values  $\varepsilon'_{\text{ISW}}$  obtained by calling our verification tool on the same gadget  $G_{\text{ISW-3}}$  with  $\beta = 5$  (see Algorithm 1) and by replacing the missing coefficients  $c_i$  with  $i > \beta$  by their upper bound  $\binom{s}{i}$  (see (6)). It may be checked for small values of p the failure probability  $\varepsilon'_{\text{ISW}}$  is smaller than  $\varepsilon_{\text{ISW}}$  which directly implies that the simulation induced by our verification tool is tighter than that deduced from Proposition 1.

Fig. 4: Values taken by  $\varepsilon_{\text{ISW}}$  and  $\varepsilon'_{\text{ISW}}$  as a function of  $p \in [0, 1]$ .

#### 5 Expansion

Constructing random-probing-secure circuit compilers with a gadget expansion strategy has been proposed by Ananth, Ishai and Sahai in [2]. Such strategy was previously used in the field of multiparty computation (MPC) with different but close security goals [13, 19]. Note that such approach is called *composition* in [2] since it roughly consists in composing a base circuit compiler several times. We prefer the terminology of *expansion* here to avoid any confusion with the notion of composition for gadgets as considered in Section 4 and usual in the literature – see for instance [5, 9, 11].

We recall hereafter the general principle of the gadget expansion strategy and provide an asymptotic analysis of the so-called *expanding circuit compiler*. Then we propose an implementation of this strategy which relies on the new notion of *gadget expandability*. In contrast, the construction of [2] relies on a *t*-out-*n* secure MPC protocol in the passive security model. The advantage of our notion is that it can be achieved and/or verified by simple atomic gadgets leading to simple and efficient constructions. After introducing the gadget expandability notion, we show that it allows to achieve random-probing security with the expansion strategy. We finally explain how to adapt the verification tool described in Section 3 to this expandability notion.

#### 5.1 Expansion Strategy

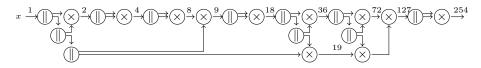

The basic principle of the gadget expansion strategy is as follows. Assume we have three *n*-share gadgets  $G_{\text{add}}$ ,  $G_{\text{mult}}$ ,  $G_{\text{copy}}$  and denote CC the standard circuit compiler for these base gadgets. We can derive three new  $n^2$ -share gadgets by simply applying CC to each gadget:  $G_{\text{add}}^{(2)} = \text{CC}(G_{\text{add}})$ ,  $G_{\text{mult}}^{(2)} = \text{CC}(G_{\text{mult}})$  and  $G_{\text{copy}}^{(2)} = \text{CC}(G_{\text{copy}})$ . Let us recall that this process simply consists in replacing each addition gate in the original gadget by  $G_{\text{add}}$ , each multiplication gate by  $G_{\text{mult}}$  and each copy gate by  $G_{\text{copy}}$ , and by replacing each wire by n wires carrying a sharing of the original wire. Doing so, we obtain  $n^2$ -share gadgets for the addition, multiplication and copy on K. This process can be iterated an arbitrary number of times, say k, to an input circuit C:

$$C \xrightarrow{\mathsf{CC}} \widehat{C}_1 \xrightarrow{\mathsf{CC}} \cdots \xrightarrow{\mathsf{CC}} \widehat{C}_k$$

The first output circuit  $\hat{C}_1$  is the original circuit in which each gate is replaced by a base gadget  $G_{\text{add}}$ ,  $G_{\text{mult}}$  or  $G_{\text{copy}}$ . The second output circuit  $\hat{C}_2$  is the original circuit C in which each gate is replaced by an  $n^2$ -share gadget  $G_{\text{add}}^{(2)}$ ,  $G_{\text{mult}}^{(2)}$  or  $G_{\text{copy}}^{(2)}$  as defined above. Equivalently,  $\hat{C}_2$  is the circuit  $\hat{C}_1$  in which each gate is replaced by a base gadget. In the end, the output circuit  $\hat{C}_k$  is hence

the original circuit C in which each gate has been replaced by a k-expanded gadget and each wire as been replaced by  $n^k$  wires carrying an  $(n^k)$ -linear sharing of the original wire. The underlying compiler is called *expanding circuit compiler* which is formally defined hereafter.

**Definition 8 (Expanding Circuit Compiler).** Let CC be the standard circuit compiler with sharing order n and base gadgets  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$ . The expanding circuit compiler with expansion level k and base compiler CC is the circuit compiler ( $CC^{(k)}, Enc^{(k)}, Dec^{(k)}$ ) satisfying the following:

- 1. The input encoding  $Enc^{(k)}$  is an  $(n^k)$ -linear encoding.

- 2. The output decoding Dec is the  $(n^k)$ -linear decoding mapping.

- 3. The circuit compilation is defined as

$$\mathsf{CC}^{(k)}(\cdot) = \underbrace{\mathsf{CC} \circ \mathsf{CC} \circ \cdots \circ \mathsf{CC}}_{k \text{ times}}(\cdot)$$

The goal of the expansion strategy in the context of random probing security is to replace the leakage probability p of a wire in the original circuit by the failure event probability  $\varepsilon$  in the subsequent gadget simulation. If this simulation fails then one needs the full input sharing for the gadget simulation, which corresponds to leaking the corresponding wire value in the base case. The security is thus amplified by replacing the probability p in the base case by the probability  $\varepsilon$ (assuming that we have  $\varepsilon < p$ ). If the failure event probability  $\varepsilon$  can be upper bounded by some function of the leakage probability:  $\varepsilon < f(p)$  for every leakage probability  $p \in [0, p_{\text{max}}]$  for some  $p_{\text{max}} < 1$ , then the expanding circuit compiler with expansion level k shall result in a security amplification as

$$p = \varepsilon_0 \xrightarrow{f} \varepsilon_1 \xrightarrow{f} \cdots \xrightarrow{f} \varepsilon_k = f^{(k)}(p) ,$$

which for an adequate function f (e.g.  $f : p \mapsto p^2$ ) provides exponential security. In order to get such a security expansion, the gadgets must satisfy a stronger notion than the composability notion introduced in Section 4 which we call random probing expandability; see Section 5.3 below.

#### 5.2 Asymptotic Analysis of the Expanding Compiler

In this section we show that the asymptotic complexity of a compiled circuit  $\widehat{C} = \mathsf{CC}^{(k)}(C)$  is  $|\widehat{C}| = \mathcal{O}(|C| \cdot \kappa^e)$  for security parameter  $\kappa$ , for some constant e that we make explicit.

Let us denote by  $\mathbf{N} = (N_a, N_c, N_m, N_r)^{\mathsf{T}}$  the column vector of gate counts for some base gadget G, where  $N_a, N_c, N_m, N_r$  stands for the number of addition gates, copy gates, multiplication gates and random gates respectively. We have three different such vectors

$$\begin{split} \boldsymbol{N}_{\text{add}} &\doteq (N_{\text{add},a}, N_{\text{add},c}, N_{\text{add},m}, N_{\text{add},r})^{\mathsf{T}} \\ \boldsymbol{N}_{\text{mult}} &\doteq (N_{\text{mult},a}, N_{\text{mult},c}, N_{\text{mult},m}, N_{\text{mult},r})^{\mathsf{T}} \\ \boldsymbol{N}_{\text{copy}} &\doteq (N_{\text{copy},a}, N_{\text{copy},c}, N_{\text{copy},m}, N_{\text{copy},r})^{\mathsf{T}} \end{split}$$

for the gate counts respectively in the base addition gadget  $G_{\text{add}}$ , in the base multiplication gadget  $G_{\text{mult}}$  and in the base copy gadgets  $G_{\text{copy}}$ . Let us define the  $4 \times 4$  square matrix M as

$$oldsymbol{M} = ig(oldsymbol{N}_{ ext{add}} \mid oldsymbol{N}_{ ext{copy}} \mid oldsymbol{N}_{ ext{mult}} \mid oldsymbol{N}_{ ext{rand}}ig) \quad ext{with} \quad oldsymbol{N}_{ ext{rand}} = (0,0,0,n)^{\mathsf{T}} \;,$$

where the definition  $N_{\text{rand}}$  holds from the fact that the standard circuit compiler replaces each random gate by n random gates.

It can be checked that applying the standard circuit compiler with base gadgets  $G_{\text{add}}$ ,  $G_{\text{mult}}$ and  $G_{\text{copy}}$  to some circuit C with gate-count vector  $N_C$  gives a circuit  $\hat{C}$  with gate-count vector  $N_{\hat{C}} = \boldsymbol{M} \cdot \boldsymbol{N}_C$ . It follows that the *k*th power of the matrix  $\boldsymbol{M}$  gives the gate counts for the level-*k* gadgets as:

$$oldsymbol{M}^k = \underbrace{oldsymbol{M} \cdot oldsymbol{M}}_{k ext{ times}} = ig(oldsymbol{N}_{ ext{add}}^{(k)} \mid oldsymbol{N}_{ ext{copy}}^{(k)} \mid oldsymbol{N}_{ ext{mult}}^{(k)} \mid oldsymbol{N}_{ ext{rand}}^{(k)}ig) \quad ext{with} \quad oldsymbol{N}_{ ext{rand}}^{(k)} = egin{pmatrix} 0 \\ 0 \\ 0 \\ n^k \end{pmatrix}$$

where  $N_{\text{add}}^{(k)}$ ,  $N_{\text{mult}}^{(k)}$  and  $N_{\text{copy}}^{(k)}$  are the gate-count vectors for the level-k gadgets  $G_{\text{add}}^{(k)}$ ,  $G_{\text{mult}}^{(k)}$  and  $G_{\text{copy}}^{(k)}$  respectively. Let us denote the eigen decomposition of M as  $M = Q \cdot \Lambda \cdot Q^{-1}$ , we get

$$oldsymbol{M}^k = oldsymbol{Q} \cdot oldsymbol{\Lambda}^k \cdot oldsymbol{Q}^{-1} ext{ with } oldsymbol{\Lambda}^k = egin{pmatrix} \lambda_1^k & & \ & \lambda_2^k & \ & & \lambda_3^k & \ & & & \lambda_4^k \end{pmatrix}$$

where  $\lambda_1, \lambda_2, \lambda_3, \lambda_4$  are the eigenvalues of **M**. We then obtain an asymptotic complexity of

$$|\widehat{C}| = \mathcal{O}(|C| \cdot (\lambda_1^k + \lambda_2^k + \lambda_3^k + \lambda_4^k)) = \mathcal{O}(|C| \cdot \max(\lambda_1, \lambda_2, \lambda_3, \lambda_4)^k)$$

for a compiled circuit  $\widehat{C} = \mathsf{C}\mathsf{C}^{(k)}(C)$  (where the constant in the  $\mathcal{O}(\cdot)$  depends on Q and shall be fairly small).

Interestingly, if multiplication gates are solely used in the multiplication gadget (*i.e.*  $N_{\text{add},m} = N_{\text{copy},m} = 0$ ) which is the case in the constructions we consider in this paper, it can be checked that (up to some permutation) the eigenvalues satisfy

$$(\lambda_1, \lambda_2) = \text{eigenvalues}(\boldsymbol{M}_{ac}) \ , \ \ \lambda_3 = N^k_{ ext{mult},m} \quad ext{and} \quad \lambda_4 = n^k$$

where  $M_{ac}$  is the top left  $2 \times 2$  block matrix of M *i.e.*

$$oldsymbol{M}_{ac} = egin{pmatrix} N_{\mathrm{add},a} & N_{\mathrm{copy},a} \ N_{\mathrm{add},c} & N_{\mathrm{copy},c} \end{pmatrix}$$

We finally get

$$|\hat{C}| = \mathcal{O}(|C| \cdot N_{\max}^k) \text{ with } N_{\max} = \max(\text{eigenvalues}(\boldsymbol{M}_{ac}), N_{\operatorname{mult},m}) .$$

(11)

In order to reach some security level  $\varepsilon = 2^{-\kappa}$  for some target security parameter  $\kappa$  and assuming that we have a security expansion  $p \to f^{(k)}(p)$ , the expansion level k must be chosen so that  $f^{(k)}(p) \leq 2^{-\kappa}$ . In practice, the function f is of the form

$$f: p \mapsto \sum_{i \ge d} c_i p^i \le (c_d + \mathcal{O}(p)) p^d$$

where  $\mathcal{O}(p)$  is to be interpred ed as p tends to 0. In the rest of this paper, we shall say that such a function has *amplification order d*.

The upper bound  $f(p) \leq c'_d p^d$  with  $c'_d = c_d + \mathcal{O}(p)$  implies  $f^{(k)}(p) < (c'_d p)^{d^k}$ . Hence, to satisfy the required security  $f^{(k)}(p) \leq 2^{-\kappa}$  while assuming  $c'_d p < 1$ , the number k of expansions must satisfy:

$$k \ge \log_d(\kappa) - \log_d(-\log_2(c'_d p))$$

We can then rewrite (11) as

$$|\widehat{C}| = \mathcal{O}(|C| \cdot \kappa^e) \quad \text{with} \quad e = \frac{\log N_{\max}}{\log d} .$$

(12)

#### 5.3 Random Probing Expandability

In the evaluation of random probing composability, let us recall that the failure event in the simulation of a gadget means that more that t shares from one of its inputs are necessary to complete a perfect simulation. For a gadget to be expandable we need slightly stronger notions than random probing composability. As first requirement, a two-input gadget should have a failure probability which is independent for each input. This is because in the base case, each wire as input of a gate leaks independently. On the other hand, in case of failure event in the child gadget, the overall simulator should be able to produce a perfect simulation of the full output (that is the full input for which the failure occurs). To do so, the overall simulator is given the clear output (which is obtained from the simulation of the base case) plus any set of n-1 output shares. This means that whenever the set J is of cardinal greater than t, the gadget simulator can replace it by any set J' of cardinal n-1.

**Definition 9 (Random Probing Expandability).** Let  $f : \mathbb{R} \to \mathbb{R}$ . An *n*-share gadget  $G : \mathbb{K}^n \times \mathbb{K}^n \to \mathbb{K}^n$  is (t, f)-random probing expandable (RPE) if there exists a deterministic algorithm  $\operatorname{Sim}_1^G$  and a probabilistic algorithm  $\operatorname{Sim}_2^G$  such that for every input  $(\hat{x}, \hat{y}) \in \mathbb{K}^n \times \mathbb{K}^n$ , for every set  $J \subseteq [n]$  and for every  $p \in [0, 1]$ , the random experiment

$$\mathcal{W} \leftarrow \text{LeakingWires}(G, p)$$

$$(I_1, I_2, J') \leftarrow \text{Sim}_1^G(\mathcal{W}, J)$$

$$out \leftarrow \text{Sim}_2^G(\mathcal{W}, J', \widehat{x}|_{I_1}, \widehat{y}|_{I_2})$$

ensures that

1. the failure events  $\mathcal{F}_1 \equiv (|I_1| > t)$  and  $\mathcal{F}_2 \equiv (|I_2| > t)$  verify

$$\Pr(\mathcal{F}_1) = \Pr(\mathcal{F}_2) = \varepsilon \quad and \quad \Pr(\mathcal{F}_1 \wedge \mathcal{F}_2) = \varepsilon^2$$

(13)

with  $\varepsilon = f(p)$  (in particular  $\mathcal{F}_1$  and  $\mathcal{F}_2$  are mutually independent), 2. J' is such that J' = J if  $|J| \leq t$  and  $J' \subseteq [n]$  with |J'| = n - 1 otherwise, 3. the output distribution satisfies

$$out \stackrel{id}{=} \left( \mathsf{AssignWires}(G, \mathcal{W}, (\widehat{x}, \widehat{y})), \, \widehat{z}|_{J'} \right)$$

(14)

where  $\widehat{z} = G(\widehat{x}, \widehat{y})$ .

The RPE notion can be simply extended to gadgets with 2 outputs: the  $\text{Sim}_1^G$  simulator takes two sets  $J_1 \subseteq [n]$  and  $J_2 \subseteq [n]$  as input and produces two sets  $J'_1$  and  $J'_2$  satisfying the same property as J' in the above definition (w.r.t.  $J_1$  and  $J_2$ ). The  $\text{Sim}_2^G$  simulator must then produce an output including  $\hat{z}_1|_{J'_1}$  and  $\hat{z}_2|_{J'_1}$  where  $\hat{z}_1$  and  $\hat{z}_2$  are the output sharings. The RPE notion can also be simply extended to gadgets with a single input: the  $\text{Sim}_1^G$  simulator produces a single set Iso that the failure event (|I| > t) occurs with probability lower than  $\varepsilon$  (and the  $\text{Sim}_2^G$  simulator is then simply given  $\hat{x}|_I$  where  $\hat{x}$  is the single input sharing). For the sake of completeness, and since we only focus in  $2 \to 1$  and  $1 \to 2$  gadgets in this paper, the RPE definition for the  $1 \to 2$  case is given in Appendix B.

It is not hard to check that the above expandability notion is stronger that the composability notion introduced in Section 4. Formally, we have the following reduction:

**Proposition 2.** Let  $f = \mathbb{R} \to \mathbb{R}$  and  $n \in \mathbb{N}$ . Let G be an n-share gadget. If G is (t, f)-RPE then G is (t, f')-RPC, with  $f'(\cdot) = 2 \cdot f(\cdot)$ .

*Proof.* We consider a (t, f)-RPE *n*-share gadget  $G : \mathbb{K}^n \times \mathbb{K}^n \to \mathbb{K}^n$ . The  $(t, 2 \cdot f)$ -random composability property is directly implied by the (t, f)-random probing expandability by making use of the exact same simulators and observing that

$$\Pr\left((|I_1| > t) \lor (|I_2| > t)\right) \le \Pr(|I_1| > t) + \Pr(|I_2| > t) = 2 \cdot \varepsilon.$$

The case of  $1 \rightarrow 2$  gadgets is even more direct.

#### 5.4 Expansion Security

Definition 9 of random probing expandability is valid for base gadgets. For level-k gadgets  $G^{(k)} = \mathsf{CC}^{(k-1)}(G)$  where  $G \in \{G_{\mathrm{add}}, G_{\mathrm{mult}}, G_{\mathrm{copy}}\}$  is a base gadget, we provide a generalized definition of random probing expandability.

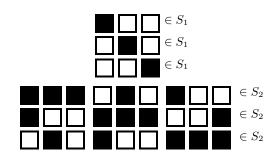

Adequate subsets of  $[n^k]$ . We first define the notion of "adequate" subsets of  $[n^k]$ , instead of only bounded subsets. For this we define recursively a family  $S_k \in \mathcal{P}([n^k])$ , where  $\mathcal{P}([n^k])$  denotes the set of all subsets of  $[n^k]$ , as follows:

$$S_1 = \{I \in [n], |I| \le t\}$$

$$S_k = \{(I_1, \dots, I_n) \in (S_{k-1} \cup [n^{k-1}])^n, I_j \in S_{k-1} \forall j \in [1, n] \text{ except at most } t\}$$

In other words, a subset I belongs to  $S_k$  if among the n subset parts of I, at most t of them are full, while the other ones recursively belong to  $S_{k-1}$ ; see Figure 9 in Appendix C.1 for an illustration with n = 3 and t = 1.

**Generalized definition of Random Probing Expandability.** We generalize Definition 9 as follows. At level k the input sets  $I_1$  and  $I_2$  must belong to  $S_k$ , otherwise we have a failure event. As in Definition 9, the simulation is performed for an output subset J' with J' = J if  $J \in S_k$ , otherwise  $J' = [n^k] \setminus \{j^*\}$  for some  $j^* \in [n^k]$ .

**Definition 10 (Random Probing Expandability with**  $\{S_k\}_{k\in\mathbb{N}}$ ). Let  $f : \mathbb{R} \to \mathbb{R}$  and  $k \in \mathbb{N}$ . An  $n^k$ -share gadget  $G : \mathbb{K}^{n^k} \times \mathbb{K}^{n^k} \to \mathbb{K}^{n^k}$  is  $(S_k, f)$ -random probing expandable (RPE) if there exists a deterministic algorithm  $\operatorname{Sim}_1^G$  and a probabilistic algorithm  $\operatorname{Sim}_2^G$  such that for every input  $(\hat{x}, \hat{y}) \in \mathbb{K}^{n^k} \times \mathbb{K}^{n^k}$ , for every set  $J \in S_k \cup [n^k]$  and for every  $p \in [0, 1]$ , the random experiment

$$\mathcal{W} \leftarrow \text{LeakingWires}(G, p)$$

$$(I_1, I_2, J') \leftarrow \text{Sim}_1^G(\mathcal{W}, J)$$

$$out \leftarrow \text{Sim}_2^G(\mathcal{W}, J', \hat{x}|_{I_1}, \hat{y}|_{I_2})$$

ensures that

1. the failure events  $\mathcal{F}_1 \equiv (I_1 \notin S_k)$  and  $\mathcal{F}_2 \equiv (I_2 \notin S_k)$  verify

$$\Pr(\mathcal{F}_1) = \Pr(\mathcal{F}_2) = \varepsilon \quad and \quad \Pr(\mathcal{F}_1 \wedge \mathcal{F}_2) = \varepsilon^2$$

(15)

with  $\varepsilon = f(p)$  (in particular  $\mathcal{F}_1$  and  $\mathcal{F}_2$  are mutually independent),

2. the set J' is such that J' = J if  $J \in S_k$ , and  $J' = [n^k] \setminus \{j^\star\}$  for some  $j^\star \in [n^k]$  otherwise,

3. the output distribution satisfies

$$out \stackrel{id}{=} \left( \mathsf{AssignWires}(G, \mathcal{W}, (\widehat{x}, \widehat{y})), \, \widehat{z}|_{J'} \right)$$

(16)

where  $\widehat{z} = G(\widehat{x}, \widehat{y})$ .

The notion of random probing expandability from Definition 10 naturally leads to the statement of our main theorem; the proof is given in Appendix C.1.

**Theorem 2.** Let  $n \in \mathbb{N}$  and  $f : \mathbb{R} \to \mathbb{R}$ . Let  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$  be n-share gadgets for the addition, multiplication and copy on  $\mathbb{K}$ . Let CC be the standard circuit compiler with sharing order n and base gadgets  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$ . Let CC<sup>(k)</sup> be the expanding circuit compiler with base compiler CC. If the base gadgets  $G_{add}$ ,  $G_{mult}$  and  $G_{copy}$  are (t, f)-RPE then,  $G_{add}^{(k)} = \mathsf{CC}^{(k-1)}(G_{add})$ ,  $G_{mult}^{(k)} = \mathsf{CC}^{(k-1)}(G_{mult})$ ,  $G_{copy}^{(k)} = \mathsf{CC}^{(k-1)}(G_{copy})$  are  $(S_k, f^{(k)})$ -RPE,  $n^k$ -share gadgets for the addition, multiplication and copy on  $\mathbb{K}$ .

The random probing security of the expanding circuit compiler can then be deduced as a corollary of the above theorem together with Proposition 2 (RPE  $\Rightarrow$  RPC reduction) and Theorem 1 (composition theorem).

**Corollary 1.** Let  $n \in \mathbb{N}$  and  $f : \mathbb{R} \to \mathbb{R}$ . Let  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$  be n-share gadgets for the addition, multiplication and copy on  $\mathbb{K}$ . Let CC be the standard circuit compiler with sharing order n and base gadgets  $G_{add}$ ,  $G_{mult}$ ,  $G_{copy}$ . Let  $CC^{(k)}$  be the expanding circuit compiler with base compiler CC. If the base gadgets  $G_{add}$ ,  $G_{mult}$  and  $G_{copy}$  are (t, f)-RPE then  $CC^{(k)}$  is  $(p, 2 \cdot f^{(k)}(p))$ -random probing secure.

#### 5.5 Relaxing the Expandability Notion

The requirement of the RPE property that the failure events  $\mathcal{F}_1$  and  $\mathcal{F}_2$  are mutually independent might seem too strong. In practice it might be easier to show or verify that some gadgets satisfy a weaker notion. We say that a gadget is (t, f)-weak random probing expandable (wRPE) if the failure events verify  $\Pr(\mathcal{F}_1) \leq \varepsilon$ ,  $\Pr(\mathcal{F}_2) \leq \varepsilon$  and  $\Pr(\mathcal{F}_1 \wedge \mathcal{F}_2) \leq \varepsilon^2$  instead of (22) in Definition 9. Although being easier to achieve and to verify this notion is actually not much weaker as the original RPE. We have the following reduction of RPE to wRPE; see Appendix C.3 for the proof. **Proposition 3.** Let  $f = \mathbb{R} \to [0, 0.14]$ . Let  $G : \mathbb{K}^n \times \mathbb{K}^n \to \mathbb{K}^n$  be an n-share gadget. If G is (t, f)-wRPE then G is (t, f')-RPE with  $f'(\cdot) = f(\cdot) + \frac{3}{2}f(\cdot)^2$ .

Assume that we can show or verify that a gadget is wRPE with the following failure event probabilities

$$\Pr(\mathcal{F}_1) = f_1(p)$$

,  $\Pr(\mathcal{F}_2) = f_2(p)$  and  $\Pr(\mathcal{F}_1 \land \mathcal{F}_2) = f_{12}(p)$ ,

for every  $p \in [0, 1]$ . Then the above proposition implies that the gadget is (p, f)-RPE with

$$f: p \mapsto f_{\max}(p) + \frac{3}{2} f_{\max}(p)^2$$

with  $f_{\max} = \max(f_1, f_2, \sqrt{f_{12}})$ .

We shall base our verification of the RPE property on the above equation as we describe hereafter.

#### 5.6 Verification of Gadget Expandability

We can easily adapt our automatic tool to verify the weak random probing expandability for base gadgets (Definition 9). Basically, the verification is split into two steps that we first describe for the case of addition and multiplication gadgets with fan-in 2 and fan-out 1.

In a first step, our tool computes the function f to check the (t, f)-wRPE property for output sets of shares of cardinal at most t. For 2-input gadgets, this step leads to the computation of coefficients  $c_i$  corresponding to three failure events  $\mathcal{F}_1$ ,  $\mathcal{F}_2$ , and  $\mathcal{F}_1 \wedge \mathcal{F}_2$  as defined above but restricted to output sets of shares of cardinal less than t. The process is very similar to the verification of random probing composability but requires to separate the failure events counter into failure events for the first input  $(|\mathcal{I}_1| > t)$ , for the second input  $(|\mathcal{I}_2| > t)$  or for both  $((|\mathcal{I}_1| > t) \wedge (|\mathcal{I}_2| > t))$ . In the following, we denote the three functions formed from the corresponding coefficients as  $f_1^{(1)}$ ,  $f_2^{(1)}$ , and  $f_{12}^{(1)}$ .

Then, in a second step, our tool verifies that there exists at least one set of n-1 shares for each output, such that the simulation failure is limited by f(p) for some probability  $p \in [0, 1]$ . In that case, it still loops on the possible output sets of shares (of cardinal n-1) but instead of computing the maximum coefficients, it determines whether the simulation succeeds for at least one of such sets. A failure event is recorded for a given tuple if no output sets of cardinal n-1 can be simulated together with this tuple from at most t shares of each input. As for the first verification step, we record the resulting coefficients for the three failure events to obtain functions  $f_1^{(2)}$ ,  $f_2^{(2)}$ , and  $f_{12}^{(2)}$ .

From these two steps, we can deduce f such that the gadget is (t, f)-wRPE:

$$\forall p \in [0, 1], f(p) = \max(f_1(p), f_2(p), \sqrt{f_{12}(p)})$$

with

$$f_{\alpha}(p) = \max(f_{\alpha}^{(1)}(p), f_{\alpha}^{(2)}(p)) \quad \text{for} \quad \alpha \in \{1, 2, 12\}$$

The computation of f for a gadget to satisfy (t, f)-weak random probing expandability is a bit trickier for copy gadgets which produce two outputs. Instead of two verification steps considering both possible ranges of cardinals for the output set of shares J, we need to consider four scenarios for the two possible features for output sets of shares  $J_1$  and  $J_2$ . In a nutshell, the idea is to follow the first verification step described above when both  $J_1$  and  $J_2$  have cardinal equal or less than t and to follow the second verification step described above when both  $J_1$  and  $J_2$  have greater cardinals. This leads to functions  $f^{(1)}$  and  $f^{(2)}$ . Then, two extra cases are to be considered, namely when  $(|J_1| \leq t)$  and  $(|J_2| > t)$  and the reverse when  $(|J_1| > t)$  and  $(|J_2| \leq t)$ . To handle these scenarios, our tool loops over the output sets of shares of cardinal equal or less than t for the first output, and it determines whether there exists a set of n-1 shares of the second output that a simulator can perfectly simulate with the leaking wires and the former set. This leads to function  $f^{(12)}$  and reversely to function  $f^{(21)}$ . From these four verification steps, we can deduce f such that the copy gadget is (t, f)-wRPE:

$$\forall p \in [0,1], f(p) = \max(f^{(1)}(p), f^{(2)}(p), f^{(12)}(p), f^{(21)}(p)).$$

Once gadgets have been proven (t, f)-weak RPE, they are also proven to be (t, f')-RPE from Proposition 3 with  $f': p \mapsto f(p) + \frac{3}{2}f(p)^2$ . Examples of such computations for 3-share gadgets are provided in Section 6.

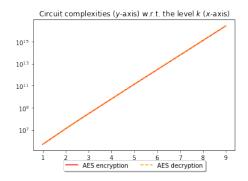

#### 6 New Constructions

In this section, we exhibit and analyze (1, f)-wRPE gadgets for the addition, multiplication, and copy (on any base field  $\mathbb{K}$ ) to instantiate the expanding circuit compiler. These gadgets are sound in the sense that their function f has amplification order strictly greater than one. As explained in previous sections, an amplification order strictly greater than one guarantees that there exists a probability  $p_{max} \in [0, 1]$  such that  $\forall p \leq p_{max}, f(p) \leq p$ , which is necessary to benefit from the expansion. For 2-input gadgets, f is defined as the maximum between  $f_1, f_2$ , and  $\sqrt{f_{12}}$ . Therefore, the constraint on the amplification order also applies to the functions  $f_1, f_2$ , and  $\sqrt{f_{12}}$ . For the function  $f_{12}$ , this means that the amplification order should be strictly greater than two.

We start hereafter with an impossibility result, namely there are no (2-share, 2-to-1) (1, f)-RPE gadgets such that f has an amplification order greater than one. Then, we provide concrete instantiations of addition, multiplication, and copy gadgets based on 3 shares which successfully achieve (1, f)-RPE for amplification order greater than one and can be used in the expansion compiler.

#### 6.1 About 2-Share Gadgets