## Surge Current Capability of Ultra-Wide-Bandgap Ga2O3 Schottky Diodes

Cyril Buttay, Hiu-Yung Wong, Boyan Wang, Ming Xiao, Christina Dimarino, Yuhao Zhang

### ▶ To cite this version:

Cyril Buttay, Hiu-Yung Wong, Boyan Wang, Ming Xiao, Christina Dimarino, et al.. Surge Current Capability of Ultra-Wide-Bandgap Ga2O3 Schottky Diodes. Microelectronics Reliability, in Press,  $10.1016/\mathrm{j.microrel.}$ 2020.113743 . hal-02968947

HAL Id: hal-02968947

https://hal.science/hal-02968947

Submitted on 16 Oct 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Surge Current Capability of Ultra-Wide-Bandgap Ga<sub>2</sub>O<sub>3</sub> Schottky Diodes

Cyril Buttaya,\*, Hiu-Yung Wongb, Boyan Wangc, Ming Xiaoc, Christina DiMarinoc, Yuhao Zhangc,\*

<sup>a</sup>Univ Lyon, INSA-Lyon, CNRS, Laboratoire Ampère UMR 5005, F-69621, LYON, France

<sup>b</sup>San Jose State University, San Jose, CA, USA

<sup>c</sup> Center for Power Electronics Systems, Virginia Tech, Blacksburg, VA, USA

### **Abstract**

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is an emerging ultra-wide-bandgap semiconductor material offering superior power material limits over Si, SiC, and GaN as well as the availability of large-diameter wafers growing from its own melt. However,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices performance may be limited by the relatively poor thermal conductivity of the material.

In this paper, we investigate the behavior of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diodes in the condition of forward current surge to explore their electro-thermal ruggedness and the related thermal management. An analytical electro-thermal device model is calibrated with experimental devices and TCAD simulations. Then this device model is incorporated into a SPICE electro-thermal network model, which is used to simulate the device temperature rise during the surge transient, considering various device and packaging configurations (i.e. various chip thicknesses and chip orientations).

It is found that provided heat is removed from the junction side, a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diode offers a robustness to surge current exceeding that of a SiC Schottky diode. The low thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is found to be overcome by the enhanced heat extraction from junction-side cooling, as well as by the intrinsically small temperature dependence of the on-resistance (and conduction loss) of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.

### 1. Introduction

From an electrical point-of-view,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is a very promising material. Its high critical electric field ( $\approx 8\,\mathrm{MV\,cm^{-1}}$ ) [1], in particular, makes it very attractive for power semiconductor devices. This can be summarized using the Baliga's Figure Of Merit (the product of a material permittivity, electron mobility, and critical field raised to the cubic power,  $\mu\epsilon E_c^3$ ). The BFOM of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is higher than that of the main wide-bangap semiconductor materials, at 3444 (vs. 340 and 870 for SiC and GaN, respectively) [2]. This means that devices made using  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can offer a lower on-state resistance for a given voltage rating than those made out of Si, SiC or GaN. Several high voltage, low resistance  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices have already been demonstrated, such as a 2 m $\Omega$  cm<sup>2</sup>, 1100 V diode [3]. High-voltage  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes operational at high temperatures up to 350 °C have also been demonstrated [4].

Another advantage of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is material growth: contrarily to SiC and GaN, bulk, mono-crystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates can be produced by a variety of melt-growth processes [5]. Substrates up to 100 mm in diameter are readily available, and 150 mm wafers are under development [1].

However,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> suffers from a major drawback: its thermal conductivity is very low (11 to 27 W m<sup>-1</sup> K<sup>-1</sup> depending on the crystal orientation [6]), approximately 10 to 20 times lower than that of GaN or SiC. This means that the semiconductor chip has a relatively high thermal resistance, making it much more difficult to remove heat from the semiconductor junction

to a heatsink. When dissipating the same power density as a SiC device, a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device will run much hotter (70 °C more in an example [7]). This may cause the device to exceed its safe operating temperature, which is limited by either the Schottky contact or the packaging materials. This also may reduce its long-term reliability due to wider thermal cycling temperature range.

A common application scenario that may cause the diode to exceed its maximum junction temperature is current surge. This may happen for example when the output of a diode rectifier is short-circuited. In this case, the diode must temporarily carry a current intensity noticeably higher than what it can sustain in steady state (nominal) conditions. This surge current value is listed in a diode's datasheet, and the corresponding tests are defined in JEDEC standards [8]. One particular test uses a half-sine current-pulse at the frequency of the ac electrical grid (here 50 Hz).

Current surges are transitory events, which result in the junction temperature of the diode rising dramatically: at one point during the current surge tests performed in [9], the junction temperature of a SiC Schottky diode was estimated to be more than 800 °C. This very high temperature transient is the result of two concomitant effects: first, the limited thermal inertia of the semiconductor chip; secondly, the positive temperature coefficient of the conduction losses, which causes the dissipated power to increase with the junction temperature, and may result in thermal runaway.

Several techniques have been developed to improve the current surge capability of semiconductor devices. Increasing the thermal inertia by clamping the semiconductor chip between

Preprint submitted to Elsevier July 2, 2020

<sup>\*</sup>Corresponding author

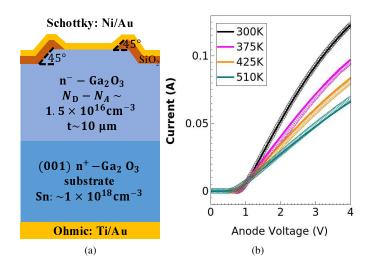

Figure 1: (a) Structure of the fabricated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes. (b) Calibration of the TCAD simulation model: experimental (lines) and TCAD simulated (markers) IV curves at different temperatures.

two thick metal shims, for example, may result in doubling of the current surge capability of a SiC diode, as compared with a more standard single-side cooling approach [10]. Another approach is to limit the increase in conduction losses with temperature. For SiC Schottky diodes, this is achieved by introducing bipolar junctions to form JBS (Junction Barrier Schottky) or MPS (Merged Pin Schottky) structures. This was found to noticeably improve the robustness of the diodes to thermal runaway [11].

Unfortunately, JBS or MPS structures require p-type doping and hole conduction, which are not available for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices [3]. Only unipolar diodes can be made using this material. Therefore, current surge capability of these diodes is based on the intrinsic properties of the material and on the thermal performance of the associated package.

In this paper, we investigate the evolution of the conduction losses of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes, based on experimental devices fabricated on commercial 2-inch  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers (section 2). Then we develop an electro-thermal model of the diodes and their packaging (section 3), and use this model to predict the surge current behavior of the diodes (section 4).

# 2. Effect of the Temperature on the Forward Characteristic of a β-Ga<sub>2</sub>O<sub>3</sub> Schottky Diode

To calibrate the electro-thermal simulation models,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power Schottky Barrier Diodes (SBDs) have been fabricated on 2-inch  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates. As shown in Fig. 1a, the epitaxial structure consists of a Si-doped n-Ga<sub>2</sub>O<sub>3</sub> layer ( $N_D \approx 1.5 \times 10^{16}$  cm<sup>3</sup>,  $\approx 10$  µm thick) grown by Hydride Vapour Phase Epitaxy (HVPE) on a commercial 2-inch n<sup>+</sup>-Ga<sub>2</sub>O<sub>3</sub> substrate. The detailed device fabrication and performance are reported in [4]. The device I-V and C-V characteristics were measured up to 510 K, and were then used to calibrate the TCAD electro-thermal simulation models (Fig. 1b). The net  $N_D$  extracted from C-V characteristics shows nearly no dependence

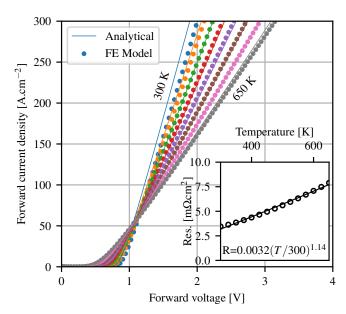

Figure 2: On-state characteristic of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as generated from finite element (TCAD) simulation, and corresponding analytical model, for temperatures ranging from 300 to 650 K. The inset graph presents the change in dynamic resistance as a function of temperature.

on temperature, indicating that Si is fully ionized in the drift region.

To understand the thermal limit of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power diodes, a 1.2 kV  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power SBD with an optimal drift region is designed. Here the breakdown voltage (BV) is designed as 1440 V to provide a 20 % safety margin for voltage rating and the maximum average electric field ( $E_m$ ) at the Schottky contact is designed as 4 MV cm<sup>-1</sup> based on the state-of-the-art experimental results [3, 12]. The thickness ( $t_D$ ) and donor concentration ( $N_D$ ) are designed based on the non-punch-through model, i.e.  $t_D = 2BV/E_m$  and  $N_D = qE_m^2/2qBV$ , to be 7.2  $\mu$ m and 3.07 × 10<sup>16</sup> cm<sup>3</sup>, respectively. The I-V characteristics of this optimized 1.2 kV  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power rectifier are then generated by the well-calibrated TCAD simulation up to 650 K.

With the objective of performing simple SPICE transient simulations, an analytical macro model is then fitted to this TCAD model (Fig. 2). This analytical model (forward conduction only) is comprised of two elements. The first is the Schottky junction, represented using a thermionic emission equation [24]:

$$I_F = S A^* T_j^2 e^{\frac{q\Phi_{BN}}{kT_j}} \left( e^{\frac{qV_D}{nkT_j}} - 1 \right)$$

(1)

where S is the junction area,  $A^*$  the effective Richardson constant,  $T_j$  the junction temperature, q the electronic charge,  $\Phi_{BN}$  the barrier height, n the ideality factor,  $V_D$  the voltage across the junction, k the Boltzmann's constant. The second element of the model corresponds to the electric resistance, mainly of the drift layer and substrate:

$$R_{on}(T_J) = R_{300} \left(\frac{T_J}{300}\right)^{\alpha}$$

(2)

with  $R_{300}$  the resistance at 300 K, and  $\alpha$  an exponent (in

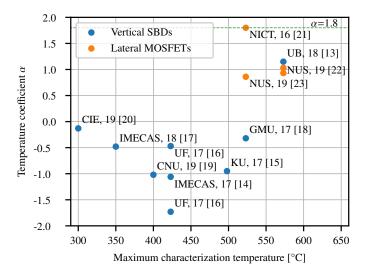

Figure 3: Value of the temperature-dependence coefficient  $\alpha$  for devices published in the literature, as a function of the maximum test temperature (with  $R_{on}(T) = R_{300} \left(\frac{T_0}{300}\right)^{\alpha}$ )

Fig. 2,  $\alpha = 1.14$ ). The value of  $\alpha$  appears to vary strongly from one device to another according to the literature. The relation between on-resistance  $(R_{on})$  and the temperature is vital to analyze the thermal stability of power devices [11, 25]. Following the commonly used power law in (2), we extracted the temperature coefficient  $\alpha$  in all experimental  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices with high-temperature performance we could find in the literature. As shown in Fig. 3, the highest  $\alpha$  is close to 1.8 in lightly doped lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin-film MOSFETs. This  $\alpha$  is mainly determined by the temperature dependence of β-Ga<sub>2</sub>O<sub>3</sub> mobility, which follows a  $T^{-1.5}$  power law as the result of phonon scattering [26, 27]. Much lower or even negative  $\alpha$  is found for many vertical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices. This is attributed to the increased donor ionization in the n<sup>+</sup>-Ga<sub>2</sub>O<sub>3</sub> substrate at high temperatures [4, 28]. These  $\alpha$  dependencies have also been validated by our TCAD simulation. To consider the worst case corresponding to the fastest  $R_{on}$  increase with temperature,  $\alpha$  is changed from 1.14, which provides the best fitting to our TCAD and experimental data (Fig. 2), to 1.8, with all other parameters in the analytical model remaining unchanged.

### 3. Electro-thermal Model of the Diode

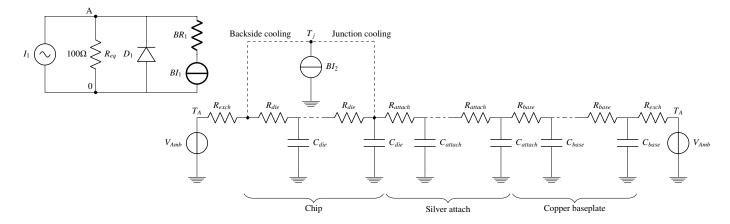

The electro-thermal model in Fig. 4 contains two parts. First, the electric circuit, with the sine current source  $I_1$ , resistor  $R_{eq}$  (for easier convergence of simulation), diode  $D_1$  (to carry negative currents), and the model of the diode under test. This diode model contains two elements, a behavioral current source  $BI_1$  (to implement (1)) and a behavioral resistance  $BR_1$  (to implement (2)). The second part of the circuit represents the thermal model in the form of a Cauer network.

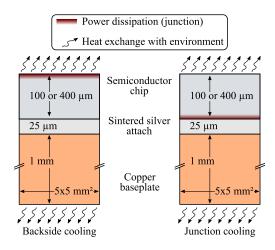

For the thermal model, two cases are considered (see Fig. 5): the chip is mounted either in the standard way (i.e with the Schottky junction on top), or it is mounted in the "flip-chip" configuration (with the Schottky junction at the bottom of the

| Table 1: Parameters used for the electrothermal simulations         |                     |                                                 |

|---------------------------------------------------------------------|---------------------|-------------------------------------------------|

| Parameter                                                           | Name                | Value                                           |

| Room temp.resistance (arbitrary)                                    | $R_{300}$           | 8 mΩ                                            |

| Temperature coefficient of resistance                               | $\alpha$            | 1.8                                             |

| Ther. cond. of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> on [001] [6] | $\lambda_{Ga_2O_3}$ | $14~{\rm W}~{\rm m}^{-1}~{\rm K}^{-1}$          |

| Thermal conductivity of Cu [29]                                     | $\lambda_{Cu}$      | 394 W m <sup>-1</sup> K <sup>-1</sup>           |

| Thermal cond. of Sintered Ag [30]                                   | $\lambda_{Cu}$      | $238 \text{ W m}^{-1} \text{ K}^{-1}$           |

| Specific heat of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> [31]       | $c_{p_{Ga2O3}}$     | $560 \mathrm{J}\mathrm{K}^{-1}\mathrm{kg}^{-1}$ |

| Specific heat of Cu [29]                                            | $c_{p_{Cu}}$        | $385 \mathrm{J}\mathrm{K}^{-1}\mathrm{kg}^{-1}$ |

| Specific heat of Sinterd Ag [30]                                    | $c_{p_{Cu}}$        | $233 \mathrm{J}\mathrm{K}^{-1}\mathrm{kg}^{-1}$ |

| Density of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> [1]              | $\rho_{Cu}$         | $5950  \mathrm{kg}  \mathrm{m}^{-3}$            |

| Density of Cu [29]                                                  | $\rho_{Cu}$         | $8960  \text{kg m}^{-3}$                        |

| Density of Sintered Ag [30]                                         | $\rho_{Cu}$         | $8580  \mathrm{kg}  \mathrm{m}^{-3}$            |

| Chip thickness (arbitrary)                                          | $t_{chip}$          | 100 or 400 μm                                   |

| Baseplate thickness (arbitrary)                                     | $t_{base}$          | 1 mm                                            |

| Chip area (arbitrary)                                               | S                   | $25\mathrm{mm}^2$                               |

| Ambient temperature (arbitrary)                                     | $T_A$               | 300 K                                           |

chip). In the first case, power is dissipated on top of the chip and heat must diffuse through the entire chip thickness before reaching the attach and the baseplate (this is referred to as "backside cooling"). In the second case, the heat dissipated at the Schottky junction has direct access to the attach and baseplate (this is referred to as "junction cooling"). In both cases, a uniform power dissipation is considered at the corresponding surface of the chip. The side surfaces are considered adiabatic. The bottom surface of the baseplate and the top surface of the chip are considered to exchange heat with the environment through a high thermal resistance ( $R_{exch} = 100 \text{ K W}^{-1}$ ). Note that due to the transient nature of the surge current, this thermal resistance has little effect on the results presented below.

For the sake of simplicity, the baseplate and the chip are considered to have the same surface area, so heat spreading effects can be neglected (1-D heat propagation condition). In this case, the chip and baseplates can be subdivided in a series of thermal resistance ( $R_{Th}$ ) and capacitance ( $C_{Th}$ ) cells:

$$R_{Th_a} = \frac{t_a}{N_a \lambda_b S} \tag{3}$$

$$C_{Th_a} = \frac{t_a}{N_a} S \rho_b C_{p_b} \tag{4}$$

where subscript a stands for either the baseplate, silver die attach, or chip and subscript b for the corresponding material ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, Ag or Cu);  $t_a$  is the thickness of the element;  $N_a$  the number of subdivisions;  $\lambda_b$  the thermal conductivity of the corresponding material;  $\rho_b$  its density and  $C_{p_b}$  its specific heat; S is the chip surface area. The numerical values of these parameters are listed in table 1.

In combination with the two cooling configurations, two chip thicknesses are considered (100 and 400  $\mu$ m) to investigate the effect of the semiconductor thickness on the surge current behavior. The model from Fig. 4 has been simulated using LTSpice. The same model is also simulated considering SiC instead of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, using the model parameters for a SiC Schottky diode presented in [11]. For the sake of comparison, both  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and SiC diodes are supposed to have a surface area of 0.25 cm<sup>2</sup> and a nominal resistance ( $R_{300}$ ) of 8 m $\Omega$ . The main

Figure 4: The electrothermal model used for SPICE simulation: the electrical circuit including the diode model comprised of behavioral elements  $BI_1$  and  $BR_1$  and the thermal network with the power source  $BI_2$  which can be connected to either the top or the bottom surface of the chip.

Figure 5: Packaging structures considered for the electro-thermal analysis.

difference is the temperature sensitivity of the resistance ( $\alpha$ ), which was found to be 2.95 for the SiC diode investigated in [11], while it is considered to be 1.8 for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> in the present article.

### 4. Simulation Results

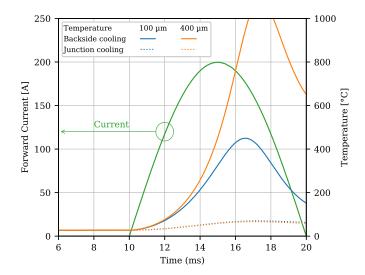

A transient simulation of  $\beta\text{-}Ga_2O_3$  devices (Fig.6) shows the calculated temperature rise for a 200 A peak, half-sine current pulse. This value was chosen as it is very close to the thermal runaway limit for the backside cooled, 400  $\mu\text{m}$ -thick chip (above this current level, the junction temperature becomes unrealistic, at several thousand degrees Celsius). It can be seen that while the temperature only rises moderately for both junction cooling cases, it increases much more for the backside cooling cases. For the junction cooling, the maximum temperature exceeds 400 °C and 1000 °C for the 100  $\mu\text{m}$  and 400  $\mu\text{m}$ -thick chip, respectively. This confirms that because of the poor thermal conductivity of  $\beta\text{-}Ga_2O_3$ , heat conduction through the chip is limited, and even the thermal resistance of a chip as thin as 100  $\mu\text{m}$  is large enough to cause a temperature rise of more than 300 °C compared to junction-cooled devices.

Figure 6: Simulated temperature transient during a current surge (200 A), for the 4 configuration considered (single or double-side cooling, 100 or 400  $\mu m$ -thick  $\beta\text{-}Ga_2O_3$  chip).

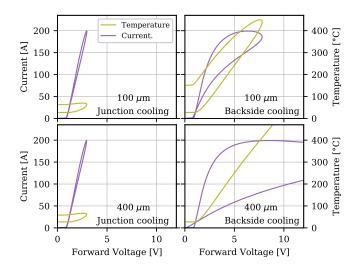

The same data are plotted in Fig. 7, this time as a function of the forward voltage rather than time. Such representation highlights the effects of the increase in forward voltage drop (as the diode heats up) on the power dissipation. As temperature increases, so does the forward voltage drop, due to the increase in dynamic resistance, as described by (2). As a result, the power dissipation (the product of forward current and voltage) also increases, causing the temperature to rise further. The rightmost graphs in Fig. 7, which correspond to the backside-cooled cases, illustrate this positive feedback: while the current pulse is identical in all cases, the resulting forward voltage is noticeably different (7 V max. for the 100 µm-thick chip vs. >12 V max. for the 400 µm-thick chip). This means that the elevated junction temperature reached in the backside-cooled, 400 µm-thick chip case (>1000 °C) is the result of both the higher thermal resistance of the thicker chip and of the higher power dissipation due to the positive temperature coefficient of the forward voltage drop.

Figure 7: Simulated temperature transient during a current surge (200 A peak), as a function of the instantaneous forward voltage drop for the 4 configuration considered (single or double-side cooling, 100 or 400  $\mu$ m-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> chip).

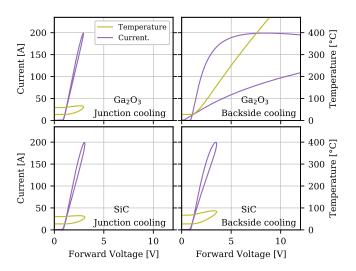

Regarding the comparison between SiC and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes, the results are summarized in Fig. 8, for 400 µm-thick chips and a surge current of 200 A. Contrarily to the backside-cooled  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diode (top right graph), the SiC diode can sustain the surge event with little temperature rise, even with backside-cooling (bottom graphs). This is due to the much better thermal conductivity of SiC (390 W m<sup>-1</sup> K<sup>-1</sup>, as opposed to 14 W m<sup>-1</sup> K<sup>-1</sup> for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>). When considering junction-cooling (leftmost graphs in Fig. 8), both the SiC and the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes show very similar behavior, with only small temperature rise (a few tens of degrees Celsius), as most of the dissipated heat can be absorbed by the chip attach and baseplate.

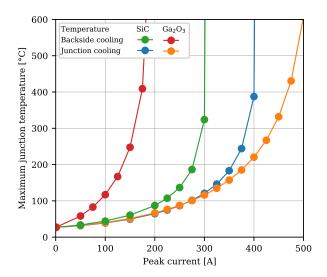

A more complete comparison between the behavior of SiC and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes is given in Fig. 9. For both materials, backside- and junction-cooled diodes are simulated, considering surge current values ranging from 1 to 500 A. In all cases, the chips are considered to be 400  $\mu$ m-thick and 25 mm<sup>2</sup> in surface. As expected, backside-cooled chips have the lower surge current capability, and their junction temperature is found to exceed 600 °C above 175 A and 300 A for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and SiC, respectively. Junction-cooled diodes have a higher capability, at 400 A and 500 A for SiC and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> respectively.

Moreover, it can be seen that the temperature of the junction-cooled  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diode (orange line in Fig. 9) is lower than that of its SiC counterpart for peak currents above 300 A. This is because of the lower  $\alpha$  value of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> in (2) compared to SiC (1.8 vs. 2.95): the on-state resistance of the SiC diode increases faster with temperature, causing the SiC diode to enter thermal runaway sooner. As can be seen in Fig. 9, the slope of the blue curve (junction-cooled, SiC diode) becomes vertical at a peak current of 400 A. This means that any small increase in peak current results in a dramatic increase in junction temperature, and corresponds to thermal runaway condition. On the contrary, even though its temperature becomes very high (600 °C for a peak current of 500 A), the junction-

Figure 8: Simulated temperature transient during a current surge (200 A peak), as a function of the instantaneous forward voltage drop for 400  $\mu$ m-thick chips with single or double-side cooling, and considering  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> or SiC semi-conductor material.

cooled  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diode (orange line in Fig. 9) has not reached thermal runaway yet.

### 5. Conclusion

The poor thermal conductivity of the material has a strong effect on the current carrying capability of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes in a conventional backside-cooled package. This is especially true regarding surge current reliability, when the diodes have to sustain a transient increase in current.

Reducing the chip thickness from  $400\,\mu m$  to  $100\,\mu m$  would reduce the thermal resistance of the chip, albeit not enough to achieve a surge current capability comparable to that of a SiC diode with the same chip size.

"Flipping" the chip, so that its junction would be in direct contact with the copper baseplate is found to be a much more efficient solution, as this removes the thermal resistance of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> chip entirely. For a peak surge current of 200 A (800 A cm<sup>-2</sup>), the behaviors of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and the SiC diodes are found to be very comparable. For higher peak surge current (above 300 A, or 1200 A cm<sup>-2</sup>), however, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diode exhibits a lower temperature rise and a much more stable behavior: while the SiC diode enters thermal-runaway above 400 A, no such phenomenon is observed for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diode up to 600 A. This can be explained by the lower temperature dependency of the on-state resistance ( $\alpha$ ) of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as compared to SiC. Note that in this article we considered a high value for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>  $\alpha$  (1.8, see Fig. 3). Lower values would result in an even greater advantage for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

It can be concluded that the poor thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is partly balanced by its low sensitivity to temperature.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can be used to build robust devices, with performances comparable to or exceeding those of SiC. However, this requires changing the way the devices are packaged, to provide cooling closer to the junction.

Figure 9: Simulated maximum temperature reached during a surge event as a function of the peak current, for  $400 \,\mu\text{m}$ -thick SiC and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes.

### References

- S. Stepanov, V. Nikolaev, V. Bougrov, and A. Romanov, "Gallium oxide: Properties and applications – a review," *Rev. Adv. Mater. Sci*, vol. 44, pp. 63–86, 2016.

- [2] M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, "Recent progress in Ga<sub>2</sub>O<sub>3</sub> power devices," *Semiconductor Science and Technology*, vol. 31, no. 3, p. 034001, Jan. 2016.

- [3] N. Allen, M. Xiao, X. Yan, K. Sasaki, M. J. Tadjer, J. Ma, R. Zhang, H. Wang, and Y. Zhang, "Vertical Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes with Small-Angle Beveled Field Plates: A Baliga's Figure-of-Merit of 0.6 GW/cm<sup>2</sup>," *IEEE Electron Device Letters*, vol. 40, no. 9, pp. 1399– 1402, Sep. 2019.

- [4] B. Wang, M. Xiao, X. Yan, H. Y. Wong, J. Ma, K. Sasaki, H. Wang, and Y. Zhang, "High-voltage vertical Ga<sub>2</sub>O<sub>3</sub> power rectifiers operational at high temperatures up to 600 K," *Applied Physics Letters*, vol. 115, no. 26, p. 263503, 2019.

- [5] J. D. Blevins, K. Stevens, A. Lindsey, G. Foundos, and L. Sande, "Development of Large Diameter Semi-Insulating Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>) substrates," *IEEE Transactions on Semiconductor Manufacturing*, vol. 32, no. 4, pp. 466–472, Nov 2019.

- [6] Z. Guo, A. Verma, X. Wu, F. Sun, A. Hickman, T. Masui, A. Kuramata, M. Higashiwaki, D. Jena, and T. Luo, "Anisotropic thermal conductivity in single crystal β-gallium oxide," *Applied Physics Letters*, vol. 106, no. 11, p. 111909, 2015.

- [7] L. Boteler, A. Lelis, M. Berman, and M. Fish, "Thermal Conductivity of Power Semiconductors—When Does It Matter?" in *Proceedings on the* 7<sup>th</sup> IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2019.

- [8] JEDEC, "Silicon Rectifier Diodes," Jedec solid state technology association, Tech. Rep., 2000.

- [9] V. Banu, P. Godignon, X. Jordá, M. Alexandru, and J. Millàn, "SiC Schottky Diode surge current analysis and application design using behavioral SPICE models," in CAS 2012 (International Semiconductor Conference), vol. 2, Oct 2012, pp. 359–362.

- [10] V. Banu, P. Godignon, X. Jordà, X. Perpiñà, and J. Millán, "Remarkable Increase in Surge Current Capability of SiC Schottky Diodes Using Press Pack Contacts," *Material Science Forum*, vol. 740 – 742, pp. 873 – 876, 2013.

- [11] C. Buttay, C. Raynaud, H. Morel, G. Civrac, M.-L. Locatelli, and F. Morel, "Thermal Stability of Silicon Carbide Power Diodes," *IEEE Transactions on Electron Devices*, vol. 59, no. 3, pp. 761–769, 2012.

- [12] X. Yan, I. S. Esqueda, J. Ma, J. Tice, and H. Wang, "High breakdown electric field in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/graphene vertical barristor heterostructure," *Applied Physics Letters*, vol. 112, no. 3, p. 032101, 2018.

- [13] A. Vaidya, K. Sasaki, A. Kuramata, T. Masui, and U. Singisetti, "Pt, Ni and Ti schottky barrier contacts to  $\beta$ -(Al0. 19Ga0. 81)<sub>2</sub>O<sub>3</sub> grown by molecular beam epitaxy on sn doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate," *arXiv preprint arXiv:1803.07504*, 2018.

- [14] Q. He, W. Mu, H. Dong, S. Long, Z. Jia, H. Lv, Q. Liu, M. Tang, X. Tao, and M. Liu, "Schottky barrier diode based on β-Ga<sub>2</sub>O<sub>3</sub> (100) single crystal substrate and its temperature-dependent electrical characteristics," *Applied Physics Letters*, vol. 110, no. 9, p. 093503, 2017.

- [15] S. Oh, G. Yang, and J. Kim, "Electrical characteristics of vertical Ni/β-Ga<sub>2</sub>O<sub>3</sub> schottky barrier diodes at high temperatures," ECS Journal of Solid State Science and Technology, vol. 6, no. 2, p. Q3022, 2016.

- [16] S. Ahn, F. Ren, L. Yuan, S. Pearton, and A. Kuramata, "Temperature-dependent characteristics of Ni/Au and Pt/Au Schottky diodes on β-Ga<sub>2</sub>O<sub>3</sub>," ECS Journal of Solid State Science and Technology, vol. 6, no. 1, pp. P68–P72, 2017.

- [17] G. Jian, Q. He, W. Mu, B. Fu, H. Dong, Y. Qin, Y. Zhang, H. Xue, S. Long, Z. Jia *et al.*, "Characterization of the inhomogeneous barrier distribution in a Pt/(100) β-Ga<sub>2</sub>O<sub>3</sub> schottky diode via its temperaturedependent electrical properties," *AIP Advances*, vol. 8, no. 1, p. 015316, 2018.

- [18] N. Moser, J. McCandless, A. Crespo, K. Leedy, A. Green, A. Neal, S. Mou, E. Ahmadi, J. Speck, K. Chabak, N. Peixoto, and G. Jessen, "Ge-doped β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Letters*, vol. 38, no. 6, pp. 775–778, 2017.

- [19] P. S. Reddy, V. Janardhanam, K.-H. Shim, V. R. Reddy, S.-N. Lee, S.-J. Park, and C.-J. Choi, "Temperature-dependent schottky barrier parameters of Ni/Au on n-type (001) β-Ga<sub>2</sub>O<sub>3</sub> schottky barrier diode," *Vacuum*, vol. 171, p. 109012, 2020.

- [20] T.-H. Yang, H. Fu, H. Chen, X. Huang, J. Montes, I. Baranowski, K. Fu, and Y. Zhao, "Temperature-dependent electrical properties of β-Ga<sub>2</sub>O<sub>3</sub> schottky barrier diodes on highly doped single-crystal substrates," *Journal of Semiconductors*, vol. 40, no. 1, p. 012801, 2019.

- [21] M. H. Wong, Y. Morikawa, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Characterization of channel temperature in Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors by electrical measurements and thermal modeling," *Applied Physics Letters*, vol. 109, no. 19, p. 193503, 2016.

- [22] D. Lei, K. Han, Y. Wu, Z. Liu, and X. Gong, "Investigation on temperature dependent dc characteristics of gallium oxide metal-oxide-semiconductor field-effect transistors from 25°C to 300°C," Applied Physics Express, vol. 12, no. 4, p. 041001, 2019.

- [23] ——, "High thermal performance Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistors," in 2019 Electron Devices Technology and Manufacturing Conference (EDTM). IEEE, 2019, pp. 23–25.

- [24] S. M. Sze and K. K. Ng, Physics of semiconductor devices. John Wiley & Sons, Ltd. 2006.

- [25] K. Sheng, "Maximum Junction Temperatures of SiC Power Devices," IEEE Transactions on Electron Devices, vol. 56, no. 2, pp. 337–342, Feb. 2009.

- [26] S. Pearton, J. Yang, P. H. Cary IV, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, "A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices," *Applied Physics Reviews*, vol. 5, no. 1, p. 011301, 2018.

- [27] A. Parisini and R. Fornari, "Analysis of the scattering mechanisms controlling electron mobility in β-Ga<sub>2</sub>O<sub>3</sub> crystals," *Semiconductor Science and Technology*, vol. 31, no. 3, p. 035023, 2016.

- [28] A. T. Neal, S. Mou, R. Lopez, J. V. Li, D. B. Thomson, K. D. Chabak, and G. H. Jessen, "Incomplete ionization of a 110 mev unintentional donor in β-Ga<sub>2</sub>O<sub>3</sub> and its effect on power devices," *Scientific reports*, vol. 7, no. 1, p. 13218, 2017.

- [29] T. Wetzel and P. v. Boeckh, Heat Transfer: Basics and Practice. Springer, 2012.

- [30] J. G. Bai, Z. Z. Zhang, J. N. Calata, and G. . Lu, "Low-temperature sintered nanoscale silver as a novel semiconductor device-metallized substrate interconnect material," *IEEE Transactions on Components and Packaging Technologies*, vol. 29, no. 3, pp. 589–593, Sept 2006.

- [31] Z. Galazka, K. Irmscher, R. Uecker, R. Bertram, M. Pietsch, A. Kwasniewski, M. Naumann, T. Schulz, R. Schewski, D. Klimm, and M. Bickermann, "On the bulk β-ga2o3 single crystals grown by the Czochralski method," *Journal of Crystal Growth*, vol. 404, pp. 184 191, 2014.