# Comparison of electrical properties of ohmic contact realized on p-type 4H-SiC

D M Nguyen, Christophe Raynaud, Mihai Lazar, H Vang, Dominique Planson

# ▶ To cite this version:

D M Nguyen, Christophe Raynaud, Mihai Lazar, H Vang, Dominique Planson. Comparison of electrical properties of ohmic contact realized on p-type 4H-SiC. ICSCRM'2007, Oct 2007, Otsu, Japan. hal-02961607

HAL Id: hal-02961607

https://hal.science/hal-02961607

Submitted on 8 Oct 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Comparison of electrical properties of ohmic contact realized on p-type 4H-SiC

D. M. Nguyen, C. Raynaud, M. Lazar, H. Vang, D. Planson AMPERE INSA Lyon, 21 Av. Jean-Capelle; 69621 Villeurbanne, France christophe.raynaud@insa-lyon.fr

#### 1. Introduction

Due to its wide bandgap, high breakdown field, and high thermal conductivity, silicon carbide is the semiconductor material that allows a spectacular reduction of the resistance of the active layers. These values are divided by a factor of 100 compared to silicon due to doping increasing and size reduction. Nevertheless this theoretical factor is shaded by the still higher contact resistances which are obtained on p-type SiC.

This paper compares the electrical resistivity of ohmic contacts formed on p-type 4H-SiC realized by Aluminum ion implantation followed by a thermal annealing to activate the dopants. The influence of the surface state after annealing is investigated. The annealing is realized at 1650° for 45min on one sample, and at 1700°C for 30 min on the second sample. When annealed at 1700°C, the sample is capped in a graphite layer to avoid Si evaporation [1].

# 2. Description of the devices

$N^+$  4H-SiC substrates with n-type epilayers purchased from CREE have been used to realize bipolar diodes and TLM structures. Doping level and thickness of the epilayer are  $8.5 \times 10^{14}$  cm<sup>-3</sup> and 55 µm. A thick epilayer was used in order to obtain a blocking voltage of 6 kV for these diodes (this aspect is not treated in this paper). The emitter of diodes are realized by multiple Aluminum implantations to achieve a box profile of impurities with a constant level at  $4 \times 10^{19}$  cm<sup>-3</sup> with a depth of 0.5 µm. The post-implantation anneal have been realized in two different ways. Sample A has been annealed at  $1650^{\circ}$ C during 45 min. Sample B has been annealed at  $1700^{\circ}$ C during 30 min. in the same furnace but capped with a graphite layer. Ohmic contacts were formed by deposing Ti/Ni and a Ni/Al on the topside and backside of the wafer for cathode and anode, respectively. An RTA annealing at  $1000^{\circ}$ C during 2 minutes was performed [2].

Current-Voltage (I-V) measurements have been realized using a Sourcemeter Keithley K2410.

## 3. Experimental results

## 3.1 Transmission Line Method (TLM)

TLM measurements have been performed on the two wafers with applied bias varying from -3 to 3 V. From the slope of the current-voltage measurement, the resistance is calculated. With varying the distance between the two ohmic contacts, it is possible to deduce the specific contact resistance  $\rho_c$ , and the sheet resistance  $R_{\square}$ . Results are summarised in **Table 1**. It appears that capping the sample during the annealing reduces considerably the specific contact resistance. The difference between the values of  $R_{\square}$  is a priori due to the difference in the temperature annealing. A higher temperature leads to a better activation of dopants and therefore to a lower resistivity or sheet resistance.

Table 1: Results of TLM measurements: each value is an average of 5 measurements for sample A and 7 measurements for sample B.

|                           | $\rho_{\rm c} \left(\Omega {\rm cm}^2\right)$ | $R_{\Box}\left( \mathrm{k}\Omega\right)$ |

|---------------------------|-----------------------------------------------|------------------------------------------|

| Sample A                  | 4.2×10 <sup>-3</sup>                          | 24.0                                     |

| Sample B (with C-capping) | 6.2×10 <sup>-4</sup>                          | 14.6                                     |

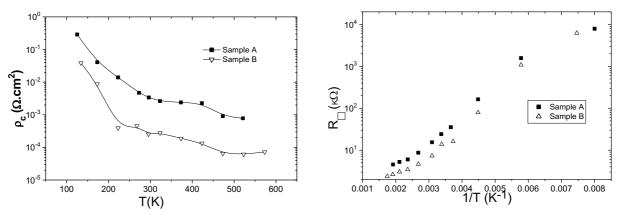

TLM measurements have also been performed as a function of temperature in order to verify the contact resistivity temperature dependence. From the For both samples, above room temperature,  $\rho_c$  is slowly decreasing with temperature: it is divided by 4-5. The surface state obtained after post-implantation annealing has a more significant impact on the contact resistances. The specific contact resistance is one decade lower for the capped sample B compared to the uncapped sample A. In contrast for the both samples closer values are obtained for the sheet resistance  $R_{\square}$ , decreasing with

temperature due to the ionization of the Aluminum dopants.

## 3.2 Characterization of diodes

In forward bias, the diodes have been tested up to 5 V to extract the series resistance  $R_S$ , and the specific on-resistance  $\rho_s = R_S \times S$ , where S is the diode area. In both samples,  $\rho_s$  depends on the diode area, which is probably due to the current spreading in the thinner metallization. However the average value of  $\rho_s$  is a little higher in sample A.

Table 2 : Results of I-V measurements on the diodes : each value of the specific on-resistance  $\rho_s$  is an average of 15-20 measurements for both samples A and B.

| $\rho_{\rm s} \left(\Omega {\rm cm}^2\right)$ | Ø 250 µm | Ø 400 μm |

|-----------------------------------------------|----------|----------|

| Sample A                                      | 1.0318   | 2.4383   |

| Sample B (with C-capping)                     | 0.9999   | 2.3551   |

Figure 1: Temperature dependence of specific contact resistance (left) and sheet resistance (right) obtained by TLM measurements on sample A.

Numerical calculations taking into account the incomplete ionization, the carrier mobility indicates that resistance of the emitter and of the substrate can be neglected in regards to the epilayer resistance,  $R_{epi} \sim 66~\Omega$  for  $\varnothing 250~\mu m$  diodes. Neglecting the contact resistance of the backside (due to the great surface of contact), we can estimated the specific contact resistance to be in the range  $7 \times 10^{-3} - 10^{-2}~\Omega.cm^2$  for sample A, which is considerably higher than values given by TLM measurements.

The final paper will discuss about this difference, and will also presents results on diodes realized with graphite capping. Moreover, the temperature dependence of forward characteristics will be also studied.

# 4. References

[1] E. Oliviero, M. Lazar, H. Vang, C. Dubois, P. Cremillieu, J.L. Leclercq, J. Dazord and D. Planson, Materials Science Forum **556-557**, 611 (2007)

[2] H. Vang, M. Lazar, P. Brosselard, C. Raynaud, P. Cremillieu, J.-L. Leclercq, J.-M. Bluet, S. Scharnholz, D. Planson, Superlattices and Microstructures 40, 626 (2006)