# Tornado: Automatic Generation of Probing-Secure Masked Bitsliced Implementations

Sonia Belaïd, Pierre-Evariste Dagand, Darius Mercadier, Matthieu Rivain, Raphaël Wintersdorff

## ▶ To cite this version:

Sonia Belaïd, Pierre-Evariste Dagand, Darius Mercadier, Matthieu Rivain, Raphaël Wintersdorff. Tornado: Automatic Generation of Probing-Secure Masked Bitsliced Implementations. Eurocrypt 2020 - 39th Annual International Conference on the Theory and Applications of Cryptographic Techniques, May 2020, Zagreb / Virtual, Croatia. pp.311-341, 10.1007/978-3-030-45727-3\_11. hal-02953167

HAL Id: hal-02953167

https://hal.science/hal-02953167

Submitted on 31 Oct 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Tornado: Automatic Generation of Probing-Secure Masked Bitsliced Implementations

Sonia Belaïd<sup>1</sup>, Pierre-Évariste Dagand<sup>2</sup>, Darius Mercadier<sup>2</sup>, Matthieu Rivain<sup>1</sup>, and Raphaël Wintersdorff

CryptoExperts, Paris, France

Sorbonne Université, Paris, France

{sonia.belaid,matthieu.rivain}@cryptoexperts.com {pierre-evariste.dagand,darius.mercadier}@lip6.fr raphaelwin@hotmail.com

Abstract. Cryptographic implementations deployed in real world devices often aim at (provable) security against the powerful class of side-channel attacks while keeping reasonable performances. Last year at Asiacrypt, a new formal verification tool named tightPROVE was put forward to exactly determine whether a masked implementation is secure in the well-deployed probing security model for any given security order t. Also recently, a compiler named Usuba was proposed to automatically generate bitsliced implementations of cryptographic primitives.

This paper goes one step further in the security and performances achievements with a new automatic tool named Tornado. In a nutshell, from the high-level description of a cryptographic primitive, Tornado produces a functionally equivalent bitsliced masked implementation at any desired order proven secure in the probing model, but additionally in the so-called register probing model which much better fits the reality of software implementations. This framework is obtained by the integration of Usuba with tightPROVE<sup>+</sup>, which extends tightPROVE with the ability to verify the security of implementations in the register probing model and to fix them with inserting refresh gadgets at carefully chosen locations accordingly.

We demonstrate Tornado on the lightweight cryptographic primitives selected to the second round of the NIST competition and which somehow claimed to be masking friendly. It advantageously displays performances of the resulting masked implementations for several masking orders and proves their security in the register probing model.

Keywords: Compiler, Masking, Automated verification, Bitslice

#### 1 Introduction

Cryptographic implementations susceptible to power and electromagnetic side-channel attacks are usually protected by *masking*. The general principle of masking is to apply some secret sharing scheme to the sensitive variables processed by the implementation in order to make the side-channel information either negligible or hard to exploit in practice. Many masked implementations rely on Boolean masking in which a variable x is represented as n random shares  $x_1, \ldots, x_n$  satisfying the completeness relation  $x_1 \oplus \cdots \oplus x_n = x$  (where  $\oplus$  denotes the bitwise addition).

The probing model is widely used to analyze the security of masked (software) implementations vs. side-channel attacks. This model was introduced by Ishai, Sahai and Wagner in [26] to construct circuits resistant to hardware probing attacks. It was latter shown that this model and the underlying construction were instrumental to the design of efficient practically-secure masked cryptographic implementations [32, 15, 18, 19]. A masking scheme secure against a t-probing adversary, i.e. who can probe t arbitrary variables in the computation, is indeed secure by design against the class of side-channel attacks of order t [17].

Most masking schemes consider the implementation to be protected as a Boolean or arithmetic circuit composed of gates of different natures. These gates are then replaced by gadgets processing masked variables. One of the important contributions of [26] was to propose a multiplication gadget secure against t-probing attacks for any t, based on a Boolean masking of order n = 2t+1. This was

reduced to the tight order n = t+1 in [32] by constraining the two input sharings to be independent, which could be ensured by the application of a mask-refreshing gadget when necessary. The design of secure refresh gadgets and, more generally, the secure composition of gadgets were subsequently subject to many works [18, 16, 5, 6]. Of particular interest, the notions of Non-Interference (NI) and Strong Non-Interference (SNI) introduced in [5] provide a practical framework for the secure composition of gadgets which yields tight probing-secure masked implementations. In a nutshell, such implementations are composed of ISW multiplication and refresh gadgets (from the names of their inventors Ishai, Sahai, and Wagner [26]) achieving the SNI property, and of sharewise addition gadgets. The main technical challenge in such a context is to identify the number of required refresh gadgets and their (optimal) placing in the implementation to obtain a provable t-probing security. Last year at Asiacrypt, a formal verification tool called tightPROVE was put forward by Belaïd, Goudarzi, and Rivain [8] which is able to clearly state whether a tight masked implementation is t-probing secure or not. Given a masked implementation composed of standard gadgets (sharewise addition, ISW multiplication and refresh), tightPROVE either produces a probing-security proof (valid at any order) or exhibits a security flaw that directly implies a probing attack at a given order. Although nicely answering a relevant open issue, tightPROVE still suffers two important limitations. First it only applies to Boolean circuits and does not straightforwardly generalize to software implementation processing  $\ell$ -bit registers (for  $\ell > 1$ ). Secondly, it does not provide a method to place the refresh whenever a probing attack is detected.

In parallel to these developments, many works have focused on the efficient implementation of masking schemes with possibly high orders. For software implementations, it was recently demonstrated in several works that the use of bitslicing makes it possible to achieve (very) aggressive performances. In the bitsliced higher-order masking paradigm, the ISW scheme is applied to secure bitwise and instructions which are significantly more efficient than their field-multiplication counterparts involved in the so-called polynomial schemes [25, 27]. Moreover, the bitslice strategy allows to compute several instances of a cryptographic primitive in parallel, or alternatively all the s-boxes in parallel within an instance of the primitive. The former setting is simply called (full) bitslice in the present paper while the latter setting is referred to as n-slice. In both settings, the high degree of parallelization inherited from the bitslice approach results in important efficiency gains. Verifying the probing security of full bitslice masked implementation is possible with tightPROVE since the different bit slots (corresponding to different instances of the cryptographic primitive) are mutually independent. Therefore, probing an  $\ell$ -bit register in the bitslice implementation is equivalent to probing the corresponding variable in  $\ell$  independent Boolean circuits, and hence tightPROVE straightforwardly applies. For n-slice implementations on the other hand, the different bit slots are mixed together at some point in the implementation which makes the verification beyond the scope of tightPROVE. In practice, for masked software implementations, the register probing model makes much more sense than the bit probing model because a software implementation works on  $\ell$ -bit registers containing several bits that leak all together.

Another limitation of tightPROVE is that it simply verifies an implementation under the form of an abstract circuit but it does not output a secure implementation, nor provide a sound placing of refresh gadgets to make the implementation secure. In practice one could hope for an integrated tool that takes an input circuit in a simple syntax, determine where to place the refresh gadgets and compile the augmented circuit into a masked implementation, for a given masking order on a given computing platform. Usuba, introduced by Mercadier and Dagand in [29], is a high-level programming language for specifying symmetric block ciphers. It provides an optimizing compiler that produces efficient bitsliced implementations. On high-end Intel platforms, Usuba has demonstrated performance on par with several, publicly available cipher implementations. As part of its compilation pipeline, Usuba features an intermediate representation, Usuba<sub>0</sub>, that shares many commonalities with the input language of tightPROVE.

It is therefore natural to consider integrating both tools in a single programming environment. We aim at enabling cryptographers to prototype their algorithms in Usuba, letting tightPROVE verify or repair its security and letting the Usuba back-end perform masked code generation.

Our Contributions. The contributions of our work are threefold:

Extended probing-security verification tool. We tackle the limitations of tightPROVE and propose an extended verification tool, that we shall call tightPROVE<sup>+</sup>. This tool can verify the security of any masked bitslice implementation in the register probing model (which makes more sense than the bit probing model w.r.t. masked software implementations). Given a masked bitslice/n-slice implementation composed of standard gadgets for bitwise operations, tightPROVE<sup>+</sup> either produces a probing-security proof or exhibits a probing attack.

New integrated compiler for masked bitslice implementations. We present (and report on the development of) a new compiler Tornado³ which integrates Usuba and tightPROVE⁺ in a global compiler producing masked bitsliced implementations proven secure in the bit/register probing model. This compiler takes as input a high-level, functional specification of a cryptographic primitive. If some probing attacks are detected by tightPROVE⁺, the Tornado compiler introduces refresh gadgets, following a sound heuristic, in order to thwart these attacks. Once a circuit has been identified as secure, Tornado produces bitsliced C code achieving register probing security at a given input order. To account for the limited resources available on embedded systems, Tornado exploits a generalization of bitslicing – implemented by Usuba – to reduce register pressure and implements several optimizations specifically tailored for Boolean masking code. The source code of Tornado is available at:

### https://github.com/CryptoExperts/Tornado

Benchmarks of NIST lightweight cryptography candidates. We evaluate Tornado on 11 cryptographic primitives from the second round of the ongoing NIST lightweight cryptography standardization process.<sup>4</sup> The choice of cryptographic primitives has been made on the basis that they were self-identified as being amenable to masking. These implementation results give a benchmark of these different candidates with respect to masked software implementation for a number of shares ranging between 1 and 128. The obtained performances are pretty satisfying. For instance, the *n*-slice implementations of the tested primitives masked with 128 shares takes from 1 to a few dozen megacycles on an Cortex-M4 processor.

## 2 Technical Background

## 2.1 Usuba

Usuba is a domain-specific language for describing bitsliced algorithms. It has been designed around the observation that a bitsliced algorithm is essentially a combinational circuit implemented in software. As a consequence, Usuba's design is inspired by high-level synthesis languages, following a dataflow specification style. For instance, the language offers the possibility to manipulate bit-level quantities as well as to apply bitwise transformations to compound quantities. A domain-specific compiler then synthesizes an efficient software implementation manipulating machine words.

Figure 1 shows the Usuba implementation of the ASCON cipher. To structure programs, we use node's (Figure 1b, 1c & 1d), of which table's (Figure 1a) are a special case of, specified through their truth table. A node specifies a set of input values, output values as well as a system of equations relating these variables. To streamline the definition of repeating systems (e.g., the 12 rounds of ASCON), Usuba offers bounded loops, which simply desugar into standalone equations. A static analysis ensures that the system of equations admits a solution. The semantics of an Usuba program is thus straightforward: it is the (unique) solution to the system of equations.

Aside from custom syntax, Usuba features a type system that documents and enforces parallelization strategies. Traditionally, bitslicing [12] consists in treating an m-word quantity as m variables, such that a combinational circuit can be straightforwardly implemented by applying the corresponding bitwise logical operations over the variables. On a 32-bit architecture, this means that 32 circuits are evaluated "in parallel": for example, a 32-bit and instruction is seen as 32

<sup>&</sup>lt;sup>3</sup> Tornado ambitions to be the work*horse* of those cryptographers that selflessly protect their ciphers through provably secure *mask*ing and precise bit*slicing*.

$<sup>^4\ \</sup>mathtt{https://csrc.nist.gov/Projects/lightweight-cryptography/round-2-candidates}$

```

table Sbox(x:v5) returns (y:v5) {

node AddConstant(state:u64x5,c:u64)

0x4,

0xb,

0x1f, 0x14, 0x1a, 0x15,

returns (stateR:u64x5)

0x1b, 0x5,

0x9.

0x2.

0x8,

0x12,

stateR = (state[0.1], state[2] ^ c.

0x1d. 0x3.

0x6.

0x1c.

0x1e, 0x13.

0x7.

0xe.

0x0.

0xd.

0x11. 0x18.

state[3,4]):

0x10, 0xc,

0x19, 0x16, 0xa,

tel

0x1,

Oxf,

0x17

(a) S-box specified by its truth table.

(b) Node manipulating a 5-uple

node LinearLayer(state:u64x5)

node ascon12(input:u64x5)

returns (stateR:u64x5)

returns (output:u64x5)

let

stateR[0] = state[0]

consts:u64[12]

(state[0] >>> 19)

state: u64x5[13]

(state[0] >>> 28);

stateR[1] = state[1]

consts = (0xf0, 0xe1, 0xd2, 0xc3,

(state[1] >>> 61)

0xb4, 0xa5, 0x96, 0x87

(state[1] >>> 39);

0x78, 0x69, 0x5a, 0x4b);

stateR[2] =

state[2]

(state[2] >>> 1)

state[0] = input;

forall i in [0, 11] {

(state[2] >>> 6):

stateR[3] =

state[3]

state[i+1] = LinearLayer

(state[3] >>> 10)

(Sbox

(state[3] >>> 17);

(AddConstant

stateR[4] = state[4]

(state[i],consts[i])))

(state[4] >>> 7)

output = state[12]

(state[4] >>> 41);

tel

```

Fig. 1: Ascon cipher in Usuba

(c) Node involving rotations and xors

Boolean and gates. To ensure that an algorithm admits an efficient bitsliced implementation, Usuba only allows bitwise operations and forbids stateful computations [30].

(d) Main node composing the 12 rounds

However, bitslicing can be generalized to n-slicing [29] (with n>1). Whereas bitslicing splits an m-word quantity into m individual bits, we can also treat it at a coarser granularity<sup>5</sup>, splitting it into k variables of n bits each (preserving the invariant that  $m=k\times n$ ). The register pressure is thus lowered, since we introduce k variables rather than m, and, provided some support from the underlying hardware or compiler, we may use arithmetic operations in addition to the usual Boolean operations. Conversely, certain operations become prohibitively expensive in this setting, such as permuting individual bits. The role of Usuba's type system is to document the parallelization strategy decided by the programmer (e.g., u64x5 means that we chose to treat a 320-bit block at the granularity of 64-bit atoms) and ensure that the programmer only used operations that can be efficiently implemented on a given architecture.

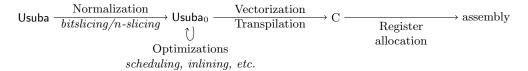

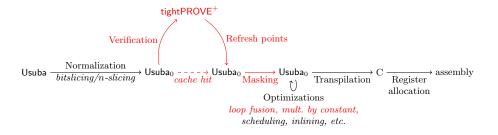

The overall architecture of the Usuba compiler is presented in Figure 2. It involves two essential steps. Firstly, normalization expands the high-level constructs of the language to a minimal core language called Usuba<sub>0</sub>. Usuba<sub>0</sub> is the software equivalent of a netlist: it represents the sliced implementation in a flattened form, erasing tuples altogether. Secondly, optimizations are applied at this level, taking Usuba<sub>0</sub> circuits to (functionally equivalent) Usuba<sub>0</sub> circuits. In particular, scheduling is responsible for ordering the system of equations in such a way as to enable sequential execution as well as maximize instruction-level parallelism. To obtain a C program from a scheduled Usuba<sub>0</sub> circuit, we merely have to replace the Boolean and arithmetic operations of the circuit with the corresponding C operations. The resulting C program is in static single assignment (SSA) form, involving only operations on integer types: we thus solely rely on the C compiler to perform register allocation and produce executable code.

<sup>&</sup>lt;sup>5</sup> The literature [29, Fig.2] distinguishes *vertical* from *horizontal n*-slicing: lacking the powerful SIMD instructions required by horizontal *n*-slicing, we focus here solely on vertical *n*-slicing, which we abbreviate unambiguously to "*n*-slicing".

Fig. 2: High-level view of the Usuba compiler

At compile-time, a specific node is designated as the cryptographic primitive of interest (here, ascon12): the Usuba compiler is then tasked to produce a C file exposing a function corresponding to the desired primitive. In this case, the bitsliced primitive would have type

```

void Ascon12 (uint32_t plain[320], uint32_t cipher[320])

whereas the 64-sliced primitive would have type

void Ascon12 (uint64_t plain[5], uint64_t cipher[5])

```

Usuba targets C so as to maximize portability: it has been successfully used to deploy cryptographic primitives on Intel, PowerPC, Arm and Sparc architectures. However, a significant amount of optimization is carried by the Usuba compiler: because this programming model is subject to stringent invariants, the compiler is able to perform far-reaching, whole program optimizations that a C compiler would shy away from. For example, it features a custom instruction scheduling algorithm, aimed at minimizing the register pressure of bitsliced code. On high-end Intel architectures featuring Single Instruction Multiple Data (SIMD) extensions, Usuba has demonstrated performance on par with hand-optimized reference implementations [29].

Usuba offers an ideal setting in which to automate Boolean masking. Indeed, ciphers specified in Usuba are presented at a suitable level of abstraction: they consist in combinational circuits, by construction. As a result, the Usuba compiler can perform a systematic source-to-source transformation, automating away the tedious introduction of masking gadgets and refreshes. Besides, the high-level nature of the language allows us to extract a model of an algorithm, analyzable by static analysis tools such as SAT solvers – to check program equivalence, which is used internally to validate the correctness of optimizations – or tightPROVE – to verify probing security.

## 2.2 tightPROVE

tightPROVE is a verification tool which aims to verify the probing security of a shared Boolean circuit. It takes as input a list of instructions that describes a shared circuit made of specific multiplication, addition and refresh gadgets and outputs either a probing security proof or a probing attack. To that end, a security reduction is made through a sequence of four equivalent games. In each of them, an adversary  $\mathcal A$  chooses a set of probes  $\mathcal P$  (indices pointing to wires in the shared circuit) in the target circuit C, and a simulator  $\mathcal S$  wins the game if it successfully simulates the distribution of the tuple of variables carried by the corresponding wires without knowledge of the secret inputs.

Game 0 corresponds to the t-probing security definition: the adversary can choose t probes in a t+1-shared circuit, on whichever wires she wishes. In Game 1, the adversary is restricted to only probe gadget inputs: one probe on an addition or refresh gadget becomes one probe on one input share, one probe on a multiplication gadget becomes one probe on each of the input sharings. In Game 2, the circuit C is replaced by another circuit C' that has a multiplicative depth of one, through a transformation called **Flatten**, illustrated in the original paper [8]. In a nutshell, each output of a multiplication or refresh gadget in the original circuit gives rise to a new input with a fresh sharing in C'. Finally, in Game 3, the adversary is only allowed to probe pairs of inputs of multiplication gadgets. The transition between these games is mainly made possible by an important property of the selected refresh and multiplication gadgets: in addition to being t-probing secure, they are t-strong non interfering (t-SNI for short) [5]. Satisfying the latter means that t probed variables in their circuit description can be simulated with less than  $t_1$  shares of

each input, where  $t_1 \leq t$  denotes the number of internal probes *i.e.* which are not placed on output shares

Game 3 can be interpreted as a linear algebra problem. In the flattened circuit, the inputs of multiplication gadgets are linear combinations of the circuit inputs. These can be modelled as Boolean vectors that we call operand vectors, with ones at indexes of involved inputs. From the definition of Game 3, the 2t probes made by the adversary all target these operand vectors for chosen shares. These probes can be distributed into t+1 matrices  $M_0, \ldots, M_t$ , where t+1 corresponds to the (tight) number of shares, such that for each probe targeting the share i of an operand vector  $\mathbf{v}$ , with i in  $\{0,\ldots,t\}$ ,  $\mathbf{v}$  is added as a row to matrix  $M_i$ . Deciding whether a circuit is t-probing secure can then be reduced to verifying whether  $\langle M_0^T \rangle \cap \cdots \cap \langle M_t^T \rangle = \emptyset$  (where  $\langle \cdot \rangle$  denotes the column space of a matrix). The latter can be solved algorithmically with the following high-level algorithm for a circuit with m multiplications:

For each operand vector  $\mathbf{w}$ ,

- 1. Create a set  $\mathcal{G}_1$  with all the multiplications for which  $\mathbf{w}$  is one of the operand vectors.

- 2. Create a set  $\mathcal{O}_1$  with the co-operand vectors of  $\mathbf{w}$  in the multiplications in  $\mathcal{G}_1$ .

- 3. Stop if  $\mathbf{w} \in \langle \mathcal{O}_1 \rangle$  ( $\mathcal{O}_1$ 's linear span), that is if  $\mathbf{w}$  can be written as a linear combination of Boolean vectors from  $\mathcal{O}_1$ .

- 4. For i from 2 to m, create new sets  $\mathcal{G}_i$  and  $\mathcal{O}_i$  by adding to  $\mathcal{G}_{i-1}$  multiplications that involve an operand  $\mathbf{w}'$  verifying  $\mathbf{w}' \in (\mathbf{w} \oplus \langle \mathcal{O}_{i-1} \rangle)$ , and adding to  $\mathcal{O}_{i-1}$  the other operand vectors of these multiplications. Stop whenever i = m or  $\mathcal{G}_i = \mathcal{G}_{i-1}$  or  $\mathbf{w} \in \langle \mathcal{O}_i \rangle$ .

If this algorithm stops when  $\mathbf{w} \in \langle \mathcal{O}_i \rangle$  for some i, then there is a probing attack on  $\mathbf{w}$ , i.e., for a certain t, the attacker can recover information on  $\mathbf{x} \cdot \mathbf{w}$  (where  $\mathbf{x}$  denote the vector of plain inputs), with only t probes on the (t+1)-shared circuit. In the other two scenarios, the circuit is proven to be t-probing secure for any value of t.

## 3 Extending tightPROVE to the Register-Probing Model

## 3.1 Model of Computation

**Notations.** In this paper, we denote by  $\mathbb{K} = \mathbb{F}_2$  the field with two elements and by  $\mathcal{V} = \mathbb{K}^s$  the vector space of dimension s over  $\mathbb{K}$ , for some given integer s (which will be used to denote the register size). Vectors, in any vector space, are written in bold. [i,j] denotes the integer interval  $\mathbb{Z} \cap [i,j]$  for any two integers i and j. For a finite set  $\mathcal{X}$ , we denote by  $|\mathcal{X}|$  the cardinality of  $\mathcal{X}$  and by  $x \leftarrow \mathcal{X}$  the action of picking x from  $\mathcal{X}$  independently and uniformly at random. For some (probabilistic) algorithm  $\mathcal{A}$ , we further denote  $x \leftarrow \mathcal{A}(in)$  the action of running algorithm  $\mathcal{A}$  on some inputs in (with fresh uniform random tape) and setting x to the value returned by  $\mathcal{A}$ .

**Basic Notions.** We call *register-based circuit* any directed acyclic graph, whose vertices either correspond to an input gate, a constant gate outputting an element of  $\mathcal{V}$  or a gate processing one of the following functions:

- XOR and AND, the coordinate-wise Boolean addition and multiplication over  $\mathbb{K}^s$ , respectively. For the sake of intelligibility, we write  $\mathbf{a} + \mathbf{b}$  and  $\mathbf{a} \cdot \mathbf{b}$  instead of  $\mathsf{XOR}(\mathbf{a}, \mathbf{b})$  and  $\mathsf{AND}(\mathbf{a}, \mathbf{b})$  respectively when it is clear from the context that we are performing bitwise operations between elements of  $\mathcal{V}$ .

- $(\mathsf{ROTL}_r)_{r \in \llbracket 1, s-1 \rrbracket}$ , the family of vector Boolean rotations. For all  $r \in \llbracket 1, s-1 \rrbracket$ ,

$$\mathsf{ROTL}_r \colon \mathcal{V} \to \mathcal{V}$$

$(v_1, \dots, v_s) \mapsto (v_{r+1}, \dots, v_s, v_1, \dots, v_r)$

-  $(\mathsf{SHIFTL}_r)_{r \in \llbracket 1, s-1 \rrbracket}$  and  $(\mathsf{SHIFTR}_r)_{r \in \llbracket 1, s-1 \rrbracket}$ , the families of vector Boolean left and right shifts. For all  $r \in \llbracket 1, s-1 \rrbracket$ ,

$$\begin{aligned} \mathsf{SHIFTL}_r \colon \mathcal{V} \to \mathcal{V} \\ (v_1, \dots, v_s) \mapsto (v_{r+1}, \dots, v_s, 0, \dots, 0) \end{aligned} \qquad \begin{aligned} \mathsf{SHIFTR}_r \colon \mathcal{V} \to \mathcal{V} \\ (v_1, \dots, v_s) \mapsto (0, \dots, 0, v_1, \dots, v_{s-r}) \end{aligned}$$

A randomized circuit is a register-based circuit augmented with gates of fan-in 0 that output elements of  $\mathcal{V}$  chosen uniformly at random.

Translation to the Masking World. A d-sharing of  $\mathbf{x} \in \mathcal{V}$  refers to any random tuple  $[\mathbf{x}]_d =$  $(\mathbf{x}_0, \mathbf{x}_1, \dots, \mathbf{x}_{d-1}) \in \mathcal{V}^d$  that satisfies  $\mathbf{x} = \mathbf{x}_0 + \mathbf{x}_1 + \dots + \mathbf{x}_{d-1}$ . A *d*-sharing  $[\mathbf{x}]_d$  is uniform if it is uniformly distributed over the subspace of tuples satisfying this condition, meaning that for any k < d, any k-tuple of the shares of **x** is uniformly distributed over  $\mathcal{V}^k$ . In the following, we omit the sharing order d when it is clear from the context, so a d-sharing of  $\mathbf{x}$  is denoted by  $[\mathbf{x}]$ . We further denote by **Enc** a probabilistic *encoding* algorithm that maps  $\mathbf{x} \in \mathcal{V}$  to a fresh uniform sharing  $[\mathbf{x}]$ .

In this paper, we call a d-shared register-based circuit a randomized register-based circuit working on d-shared variables as elements of  $\mathcal{V}$  that takes as inputs some d-sharings  $[\mathbf{x}_1], \dots, [\mathbf{x}_n]$ and performs operations on their shares with the functions described above. Assuming that we associate an index to each edge in the circuit, a probe refers to a specific edge index. For such a circuit C, we denote by  $C([\mathbf{x}_1], \dots, [\mathbf{x}_n])_{\mathcal{P}}$  the distribution of the tuple of values carried by the wires of C of indexes in  $\mathcal{P}$  when the circuit is evaluated on  $[\mathbf{x}_1], \ldots, [\mathbf{x}_n]$ .

We consider circuits composed of subcircuits called qadqets. Gadgets are d-shared circuits performing a specific operation. They can be seen as building blocks of a more complex circuit. We furthermore say that a gadget is sharewise if each output share of this gadget can be expressed as a deterministic function of its input shares of the same sharing index. In this paper, we specifically consider the following gadgets:

- The ISW-multiplication gadget  $[\otimes]$  takes two d-sharings  $[\mathbf{a}]$  and  $[\mathbf{b}]$  as inputs and outputs a d-sharing [c] such that  $\mathbf{c} = \mathbf{a} \cdot \mathbf{b}$  as follows:

- 1. for every  $0 \le i < j \le d-1$ ,  $\mathbf{r}_{i,j} \leftarrow \mathcal{V}$ ;

- 2. for every  $0 \le i < j \le d-1$ , compute  $\mathbf{r}_{j,i} \leftarrow (\mathbf{r}_{i,j} + \mathbf{a}_i \cdot \mathbf{b}_j) + \mathbf{a}_j \cdot \mathbf{b}_i$ ; 3. for every  $0 \le i \le d-1$ , compute  $\mathbf{c}_i \leftarrow \mathbf{a}_i \cdot \mathbf{b}_i + \sum_{j \ne i} \mathbf{r}_{i,j}$ .

- The ISW-refresh gadget [R] is the ISW-multiplication gadget in which the second operand [b] is set to the constant sharing  $(1,0,\ldots,0)$ , where  $0\in\mathcal{V}$  and  $1\in\mathcal{V}$  denote the all 0 and all 1 vector respectively.

- The sharewise addition gadget  $[\oplus]$  computes a d-sharing  $[\mathbf{c}]$  from sharings  $[\mathbf{a}]$  and  $[\mathbf{b}]$  such that  $\mathbf{c} = \mathbf{a} + \mathbf{b}$  by letting  $\mathbf{c}_i = \mathbf{a}_i + \mathbf{b}_i$  for  $i \in [0, d-1]$ .

- The sharewise left shift, right shift and rotation gadgets ( $[\ll_n]$ ,  $[\gg_n]$  and  $[\ll_n]$  respectively) take a sharing [a] as input and output a sharing [c] such that  $\mathbf{c} = f(\mathbf{a})$  by letting  $\mathbf{c}_i = f(\mathbf{a}_i)$ for  $i \in [0, d-1]$ , f being the corresponding function described in the section above.

- The sharewise multiplication by a constant  $[\otimes_k]$  takes a sharing  $[\mathbf{a}]$  and a constant  $\mathbf{k} \in \mathcal{V}$  as inputs and outputs a sharing [c] such that  $\mathbf{c} = \mathbf{k} \cdot \mathbf{a}$  by letting  $\mathbf{c}_i = \mathbf{k} \cdot \mathbf{a}_i$  for  $i \in [0, d-1]$ .

- The sharewise addition with a constant  $[\oplus_k]$  takes a sharing  $[\mathbf{a}]$  and a constant  $\mathbf{k} \in \mathcal{V}$  as input and outputs a sharing [c] such that  $\mathbf{c} = \mathbf{a} + \mathbf{k}$  by letting  $\mathbf{c}_i = \mathbf{a}_i$  for  $i \in [0, d-1]$  and  $\mathbf{c}_0 = \mathbf{a}_0 + \mathbf{k}$ . The coordinate-wise logical complement NOT is captured by this definition with  $\mathbf{k} = (1, \dots, 1).$

#### 3.2Security Notions

In this section, we recall the t-probing security originally introduced in [26] as formalized through a concrete security game in [8]. It is based on two experiments described in Figure 3 from [8] in which an adversary A, modelled as a probabilistic algorithm, outputs of set of t probes  $\mathcal{P}$ and n inputs  $x_1, \ldots, x_n$  in a set K. In the first experiment, ExpReal, the inputs are encoded and given as inputs to the shared circuit C. The experiment then outputs a random evaluation of the chosen probes  $(v_1, \ldots, v_t)$ . In the second experiment, ExpSim, the simulator outputs a simulation of the evaluation  $C([x_1], \ldots, [x_n])_{\mathcal{P}}$  without the input sharings. It wins the game if and only if the distributions of both experiments are identical.

**Definition 1** ([8]). A shared circuit C is t-probing secure if and only if for every adversary A. there exists a simulator S that wins the t-probing security game defined in Figure 3, i.e. the random experiments  $\mathsf{ExpReal}(\mathcal{A}, C)$  and  $\mathsf{ExpSim}(\mathcal{A}, \mathcal{S}, C)$  output identical distributions.

Fig. 3: t-probing security game from [8].

In [8], the notion of t-probing security was defined for a Boolean circuit, with  $\mathbb{K} = \mathbb{F}_2$ , that is with  $x_1, \ldots, x_n \in \mathbb{F}_2$  and  $v_1, \ldots, v_t \in \mathbb{F}_2$ . We further refer to this specialized notion as t-bit probing security.

While the notion of t-bit probing security is relevant in a hardware scenario, in the reality of masked software embedded devices, variables are manipulated in registers which contain several bits that leak all together. To capture this model, in this paper, we extend the verification to what we call the t-register probing model in which the targeted circuit manipulates variables on registers of size s for some  $s \in \mathbb{N}^+$  and the adversary is able to choose t probes as registers containing values in  $\mathcal{V} = \mathbb{F}_2^s$ . Notice that the t-bit probing model can be seen as a specialization of the t-register probing model with s = 1.

Cautionary note. In software implementations, we may also face transition leakages, modeled as functions of two  $\ell$ -bit variables when they are successively stored in the same register. In that scenario, the masking order t might be halved [2, 31]. While specific techniques can be settled to detect and handle such leakages, we leave it for future work and focus on simple register probing model in this paper, in which one observation reveals the content of a single register.

#### 3.3 Security Reductions in the Register Probing Model

Just like for the bit-probing version of tightPROVE, the security notions are formalized through games. Similar notions are used which only differ in the fact that the probes in the new model now point to wires of register-based circuits, which carry vectors of  $\mathcal{V}$ . In this section, we present the differences between the security games in the bit-probing model and the register-probing model. The games are still equivalent to one another, and we give a sketch of proof for each transition (as well as a full proof in the appendix). We then give a description of the linear algebra problem induced by the last game.

**Sequence of Games.** Similarly to the bit-probing case, Game 0 corresponds to the probing security definition for a register-based circuit, and still features an adversary  $\mathcal{A}$  that chooses a set of probes  $\mathcal{P}$  in a circuit C, and a simulator  $\mathcal{S}$  that wins the game if it successfully simulates  $C([\mathbf{x}_1], \ldots, [\mathbf{x}_n])_{\mathcal{P}}$ , for inputs  $x_1, \ldots, x_n \in \mathcal{V}$ .

Game 1. In Game 1, the adversary returns a set of probes  $\mathcal{P}' = \mathcal{P}'_r \cup \mathcal{P}'_m \cup \mathcal{P}'_{sw}$ , where  $|\mathcal{P}'| = t$  and the sets  $\mathcal{P}'_r$ ,  $\mathcal{P}'_m$  and  $\mathcal{P}'_{sw}$  contain probes pointing to refresh gadgets' inputs, pairs of probes pointing to multiplication gadgets' inputs and probes pointing to sharewise gadgets' inputs or outputs respectively.  $C([\mathbf{x}_1], \dots, [\mathbf{x}_n])_{\mathcal{P}'}$  is then a q-tuple for  $q = 2|\mathcal{P}'_m| + |\mathcal{P}'_r \cup \mathcal{P}'_{sw}|$ . Besides the definition set of variables, the only difference with the bit-probing case stands in the fact that the sharewise gadgets are not restricted to addition gadgets.

Game 2. In Game 2, the circuit C is replaced by an equivalent circuit C' of multiplicative depth 1, just like in the bit-probing case. The **Flatten** operation can be trivially adapted to register-based circuits, as the outputs of refresh and multiplication gadgets can still be considered as uniform sharings.

Game 3. In this last game, the adversary is restricted to only position its t probes on multiplication gadgets, i.e.  $\mathcal{A}$  returns a set of probes  $\mathcal{P}'' = \mathcal{P}'_r \cup \mathcal{P}'_m \cup \mathcal{P}'_s w$  such that  $\mathcal{P}'_{sw} = \mathcal{P}'_r = \emptyset$  and  $\mathcal{P}'' = P'_m \cup \mathcal{P}'_s \cup \mathcal{P}'_s w$  such that  $\mathcal{P}'_{sw} = \mathcal{P}'_r = \emptyset$  and  $\mathcal{P}'' = \mathcal{P}'_m \cup \mathcal{P}'_s \cup \mathcal{P}'_s w$  such that  $\mathcal{P}'_s \cup \mathcal{P}'_s \cup \mathcal{$

**Theorem 1.** Let C be a shared circuit. We have the following equivalences:

$$\forall \mathcal{A}_0, \exists \mathcal{S}_0, \mathcal{S}_0 \text{ wins } Game \ 0. \iff \forall \mathcal{A}_1, \exists \mathcal{S}_1, \mathcal{S}_1 \text{ wins } Game \ 1.$$

$$\iff \forall \mathcal{A}_2, \exists \mathcal{S}_2, \mathcal{S}_2 \text{ wins } Game \ 2.$$

$$\iff \forall \mathcal{A}_3, \exists \mathcal{S}_3, \mathcal{S}_3 \text{ wins } Game \ 3.$$

For the sake of clarity, we define one lemma per game transition. The corresponding proofs are available in Appendix A, but an informal reasoning that supports these ideas is given in the following, as well as the differences with the proofs established in [8].

**Lemma 1.**

$$\forall A_0, \exists S_0, S_0 \text{ wins } Game \ 0. \iff \forall A_1, \exists S_1, S_1 \text{ wins } Game \ 1.$$

Proof (sketch). The proof for the first game transition is based on the fact that multiplication and refresh gadgets are t-SNI gadgets, and that each probe on such gadgets can be replaced by at most one probe on each input sharing. The reason why this still works in the new model is that the ISW multiplication and refresh gadgets are still SNI for register-based circuits performing bitwise operations on  $\mathcal{V}$ . This transition can thus be reduced to the original transition.

**Lemma 2.**

$$\forall A_1, \exists S_1, S_1 \text{ wins } Game 1. \iff \forall A_2, \exists S_2, S_2 \text{ wins } Game 2.$$

Proof (sketch). The proof for the second game transition relies on the fact that just as the output of a Boolean multiplication gadget is a random uniform Boolean sharing, independent of its input sharings, the outputs of the multiplication gadgets we consider can be treated as new, fresh input encodings. Thus, a circuit C is t-probing secure if and only if the circuit C' = Flatten(C) is t-probing secure.

**Lemma 3.**

$$\forall A_2, \exists S_2, S_2 \text{ wins Game 2.} \iff \forall A_3, \exists S_3, S_3 \text{ wins Game 3.}$$

Proof (sketch). A cross product of shares  $\mathbf{a}_i \cdot \mathbf{b}_j$  carries informations on both shares  $\mathbf{a}_i$  and  $\mathbf{b}_j$ , as each of the s slots in the cross product carries information about each share. Thus, placing probes on multiplication gadgets only is optimal from the attacker point of view. The complete proof for Lemma 3 makes use of formal notions which are introduced in the next paragraph.

**Translation to Linear Algebra.** From now on, the column space of a matrix M is denoted by  $\langle M \rangle$  and the column space of the concatenation of all the matrices in a set E is denoted by  $\langle E \rangle$ .

From Lemma 1 and Lemma 2, checking the t-probing security of a shared circuit C has been reduced to verifying the t-probing security of a shared circuit  $C' = \mathbf{Flatten}(C)$ , for which the attacker is restricted to use probes on its multiplication and refresh gadgets' inputs. We can translate this problem into a linear algebra problem that we can solve algorithmically. In the following, let us denote by  $\mathbf{x}_{i,j} \in \mathcal{V}$  the  $j^{th}$  share of the  $i^{th}$  input sharing  $[\mathbf{x}_i]$ , so that

$$\forall i \in [1, N], [\mathbf{x}_i] = (\mathbf{x}_{i,0}, \mathbf{x}_{i,1}, \dots, \mathbf{x}_{i,t}) \in \mathcal{V}^{t+1}$$

We also denote by  $\mathbf{x}_{||j}$  the concatenation of the  $j^{th}$  shares of the input sharings:

$$\forall j \in [0, t], \mathbf{x}_{||j} = \mathbf{x}_{1,j} || \mathbf{x}_{2,j} || \dots || \mathbf{x}_{N,j} \in \mathbb{K}^{sN}$$

The probed variables in the flattened circuit C' form a q-tuple  $(\mathbf{v}_1, \dots, \mathbf{v}_q) = C'([\mathbf{x}_1], \dots, [\mathbf{x}_N])_{\mathcal{P}'}$ . It can be checked that all these variables are linear combinations of inputs shares' coordinates since (1) the circuit C' has a multiplicative depth of one, (2) the adversary can only place probes on inputs for multiplication and refresh gadgets, and (3) other types of gadgets are linear. Since the gadgets other than multiplication and refresh are sharewise, we can assert that for every  $k \in [1, q]$ , there exists a single share index j for which  $\mathbf{v}_k$  only depends on the  $j^{th}$  share of the input sharings

and thus only depends on  $\mathbf{x}_{||j}$ . Therefore there exists a Boolean matrix  $A_k \in \mathbb{K}^{sN \times s}$ , that we refer to as a block from now on, such that

$$\mathbf{v}_k = \mathbf{x}_{||j} \cdot A_k \in \mathcal{V}.$$

Let us denote by  $\mathbf{v}_{||j}$  the concatenation of all  $n_j$  probed variables  $\mathbf{v}_i$  with  $i \in [1, q]$  such that  $\mathbf{v}_i$  only depends on share j. Similarly, we denote by  $M_j \in \mathbb{K}^{sN \times sn_j}$  the matrix obtained from the concatenation of all the corresponding blocks  $A_i$  (in the same order). We can now write

$$\mathbf{v}_{||0} = \mathbf{x}_{||0} \cdot M_0$$

,  $\mathbf{v}_{||1} = \mathbf{x}_{||1} \cdot M_1$ , ...,  $\mathbf{v}_{||t} = \mathbf{x}_{||t} \cdot M_t$

which leads us to the following proposition.

**Proposition 1.** For any  $(\mathbf{x}_1, \dots, \mathbf{x}_N) \in \mathcal{V}^N$ , the q-tuple of probed variables  $(\mathbf{v}_1, \dots, \mathbf{v}_q) = C([\mathbf{x}_1], [\mathbf{x}_2], \dots, [\mathbf{x}_N])_{\mathcal{P}'}$  can be perfectly simulated if and only if the  $M_j$  matrices satisfy

$$\langle M_0 \rangle \cap \langle M_1 \rangle \cap \cdots \cap \langle M_t \rangle = \emptyset$$

.

Proof. Let us denote by  $\mathbf{x} = (\mathbf{x}_1 \| \mathbf{x}_2 \| \dots \| \mathbf{x}_N)$  the concatenation of all the inputs. We split the proof into two parts to handle both implications.

From left to right. Let us assume that there exist a non-null vector  $\mathbf{w} \in \mathbb{K}^{sN}$  and vectors  $\mathbf{u}_0 \in \mathbb{K}^{sn_0}, \ldots, \mathbf{u}_t \in \mathbb{K}^{sn_t}$  that verify  $\mathbf{w} = M_0 \cdot \mathbf{u}_0 = \cdots = M_t \cdot \mathbf{u}_t$ . This implies the following sequence of equalities:

$$\sum_{j=0}^{t} \mathbf{v}_{||j} \cdot \mathbf{u}_{j} = \sum_{j=0}^{t} \mathbf{x}_{||j} \cdot M_{j} \cdot \mathbf{u}_{j} = \sum_{j=0}^{t} \mathbf{x}_{||j} \cdot \mathbf{w} = \mathbf{x} \cdot \mathbf{w}$$

which implies that the distribution of  $(\mathbf{v}_1, \dots, \mathbf{v}_q)$  depends on  $\mathbf{x}$ , and thus cannot be perfectly simulated.

From right to left. Since the sharings  $[\mathbf{x}_1], \ldots, [\mathbf{x}_N]$  are uniform and independent, the vectors  $\mathbf{x}_{||1}, \ldots, \mathbf{x}_{||t}$  are independent uniform random vectors in  $\mathbb{K}^{sN}$ , and can thus be perfectly simulated without the knowledge of any secret value. As a direct consequence, the distribution of  $(\mathbf{v}_{||1}, \ldots, \mathbf{v}_{||t})$  can be simulated. From the definition  $\mathbf{v}_{||0} = \mathbf{x}_{||0} \cdot M_0$ , each coordinate of  $\mathbf{v}_{||0}$  is the result of a product  $\mathbf{x}_{||0} \cdot \mathbf{c}$  where  $\mathbf{c}$  is a column of  $M_0$ . By assumption, there exists  $j \in \{1, \ldots, t\}$  such that  $\mathbf{c} \notin \langle M_j \rangle$ . Since  $\mathbf{x}_{||1}, \ldots, \mathbf{x}_{||t}$  are mutually independent,  $\mathbf{x}_{||j} \cdot \mathbf{c}$  is a random uniform bit independent of  $\mathbf{x}_{||1} \cdot M_1, \ldots, \mathbf{x}_{||j-1} \cdot M_{j-1}, \mathbf{x}_{||j+1} \cdot M_{j+1}, \ldots, \mathbf{x}_{||t} \cdot M_t$ , and since  $\mathbf{c} \notin \langle M_j \rangle$ , it is also independent of  $\mathbf{x}_{||j} \cdot M_j$ . This means that  $\mathbf{x}_{||j} \cdot \mathbf{c}$  is a random uniform bit independent of  $\mathbf{v}_{||1}, \ldots, \mathbf{v}_{||t}$ , and so is  $\mathbf{x}_{||0} \cdot \mathbf{c}$ , as  $\mathbf{x}_{||0} \cdot \mathbf{c} = \mathbf{x}_{||j} \cdot \mathbf{c} + (\mathbf{x}_{||1} \cdot \mathbf{c} + \cdots + \mathbf{x}_{||j-1} \cdot \mathbf{c} + \mathbf{x}_{||j+1} \cdot \mathbf{c} + \cdots + \mathbf{x}_{||t} \cdot \mathbf{c} + \mathbf{x} \cdot \mathbf{c})$ . Since  $\mathbf{v}_{||0} = \mathbf{x}_{||0} \cdot M_0$ , we can then perfectly simulate  $\mathbf{v}_{||0}$ . As a result,  $(\mathbf{v}_1, \ldots, \mathbf{v}_q)$  can be perfectly simulated.

## 3.4 Verification in the Register Probing Model

In this section, we present a method based on Proposition 1 that checks whether a (t+1)-shared circuit C achieves t-register probing security for every  $t \in \mathbb{N}^*$ . We start by introducing some notations and formalizing the problem, then we give a description of the aforementioned method, along with a pseudocode of the algorithm. The method is finally illustrated with some examples.

**Formal Definitions.** Now that the equivalence between the t-register probing security game was proven to be equivalent to Game 3, in which the adversary can only probe variables that are inputs of multiplication gadgets in a flattened circuit C', we formally express the verification of the t-register probing security as a linear algebra problem. For a given multiplication gadget of index g, let us denote by  $[\mathbf{a}_g]$  and  $[\mathbf{b}_g]$  its input sharings, i.e.

$$[\mathbf{a}_g] = (\mathbf{x}_{||0} \cdot A_g , \dots, \mathbf{x}_{||t} \cdot A_g) \text{ and } [\mathbf{b}_g] = (\mathbf{x}_{||0} \cdot B_g , \dots, \mathbf{x}_{||t} \cdot B_g)$$

for some constant blocks  $A_g$  and  $B_g$  that we now call *operand blocks*. The adversary outputs a set of t pairs of probes  $\mathcal{P} = \{(p_1^1, p_2^1), (p_1^2, p_2^2), \dots, (p_1^t, p_2^t)\}$ , where for i in  $\{1, \dots, t\}$ ,  $p_1^i$  and  $p_2^i$  are wire indices corresponding to one element of each input sharings of the same multiplication. For all  $j \in [0, t]$ , we define the matrix  $M_j$  as the concatenation of all the blocks corresponding to probed shares of share index j.

By Proposition 1, there is a register probing attack on C if and only if  $\bigcap_{i=0}^t \langle M_j \rangle \neq \emptyset$ . For an attack to exist, the matrices must be non-empty, and since these matrices contain 2t blocks, at least one of them is made of a single block D that belongs to the set of operand blocks  $\{A_g, B_g\}_g$ . We can now say that there exists a register probing attack on C if and only if there exists a non-empty subspace S of  $\mathbb{K}^{sN}$  such that  $S = \bigcap_{i=0}^t \langle M_j \rangle \subseteq \langle D \rangle$ . In that case, there is an attack on the subset S that we now refer to as the  $attack \ span$ .

**tightPROVE**<sup>+</sup>. When s=1 (i.e., in the t-bit probing model case), the dimension of  $S=\bigcap_{i=0}^t \langle M_j \rangle$  is at most 1, so checking whether an operand block W leads to an attack or not reduces to verifying whether there exists a set of probes for which  $S=\langle W \rangle$ . However, for s>1, there can be many possible subspaces of  $\langle W \rangle$  for an operand block W, so that any non-null subspace of  $\langle W \rangle \cap S$  leads to an attack. That is why the new method not only has to determine whether there is an attack, but also which subsets of  $\langle W \rangle$  could possibly intersect with the attack span S.

Our method loops over all the operand blocks  $W \in \{A_g, B_g\}_g$  of multiplication gadgets and checks whether there is a probing attack on a subset of  $\langle W \rangle$ . For each  $W \in \{A_g, B_g\}_g$ , we create a layered directed acyclic graph  $\mathcal{G}_W$  for which each node is associated with a permissible attack span that represents the subspace of  $\langle W \rangle$  in which an attack could possibly be found. The permissible attack span in a node is a subset of the permissible attack span in its parent node. Each node is indexed by a layer number i and a unique index b. Besides, the permissible attack span denoted  $S_{i,b}$ , the node contains some information in the form of three additional sets  $\mathcal{G}_{i,b}$ ,  $\mathcal{O}_{i,b}$  and  $\mathcal{Q}_{i,b}$ .  $\mathcal{G}_{i,b}$  is a list of multiplication gadgets which could be used to find an attack.  $\mathcal{Q}_{i,b}$  contains the operand blocks of the multiplications in  $\mathcal{G}_{i,b}$  that can be combined with other operands to obtain elements of  $\langle W \rangle$ . And then  $\mathcal{O}_{i,b}$ , called the set of free operand blocks, contains the other operand blocks of  $\mathcal{G}_{i,b}$ . If there is a way to combine free operands to obtain an element of  $\langle W \rangle$ , then a probing attack is found.

We start with the first node *root*. We assign to  $S_{1,root}$  the span  $\langle W \rangle$ , to  $\mathcal{G}_{1,root}$  the set of multiplications for which W is an operand and to  $\mathcal{Q}_{1,root}$  the operand W.  $\mathcal{O}_{1,root}$  can then be deduced from  $\mathcal{G}_{1,root}$  and  $\mathcal{Q}_{1,root}$ :

$$\begin{cases} S_{1,root} = \langle W \rangle \\ \mathcal{G}_{1,root} = \{g \mid A_g = W\} \cup \{g \mid B_g = W\} \\ \mathcal{O}_{1,root} = \{B_g \mid A_g = W\} \cup \{A_g \mid B_g = W\} \\ \mathcal{Q}_{1,root} = \{W\} \end{cases}$$

At each step i (from i=1) of the algorithm, for each node b in the  $i^{th}$  layer, if  $S_{i,b} \cap \langle \mathcal{O}_{i,b} \rangle \neq \emptyset$ , the method stops and returns False: the circuit is not tight t-register probing secure for any t. If not, for each node b in the  $i^{th}$  layer, for each operand block  $A \in \{A_g, B_g\}_g \setminus \mathcal{Q}_{i,b}$ , if  $S_{i,b} \cap (\langle A \rangle + \langle \mathcal{O}_{i,b} \rangle) \neq \emptyset$  (where  $\langle A \rangle + \langle \mathcal{O}_{i,b} \rangle$  denotes the Minkowski sum of  $\langle A \rangle$  and  $\langle \mathcal{O}_{i,b} \rangle$ ), then we connect b to a new node b' in the next layer i+1, containing the following information:

$$\begin{cases} S_{i+1,b'} = S_{i,b} \cap (\langle A \rangle + \langle \mathcal{O}_{i,b} \rangle) \\ \mathcal{G}_{i+1,b'} = \mathcal{G}_{i,b} \cup \{g \mid A \text{ is an operand block of the multiplication gadget } g\} \\ \mathcal{O}_{i+1,b'} = \mathcal{O}_{i,b} \cup \{B \mid A \text{ is a co-operand block of } B \text{ in a multiplication gadget}} \\ \mathcal{Q}_{i+1,b'} = \mathcal{Q}_{i,b} \cup \{A\} \end{cases}$$

If no new node is created at step i, then the algorithm stops and returns True: the circuit is tight t-register probing secure for any t. The method eventually stops, as the number of nodes we can create for each graph is finite. Indeed, at each step i, each node b can only produce  $|\{A_g, B_g\}_g| - |\mathcal{Q}_{i,b}|$  new nodes, and for each of them the set  $\mathcal{Q}$  grows by one. In total, each graph can contain up to  $(|\{A_g, B_g\}_g| - 1)!$  nodes.

The pseudocode of Algorithm 1 gives a high-level description of our method. In this algorithm, each edge on the graph corresponds to adding an operand in Q. Multiple operands can be added

at once if the corresponding permissible attack span is the same for all of those operands. For the sake of simplicity, we decide to omit this optimization in the algorithm.

```

Algorithm 1: tightPROVE+

input: A description of a circuit C

output: True or False, along with a proof (and possibly a list of attacks)

foreach operand W do

/* create root for the new graph \mathcal{G}_W */

S_{1,root} = \langle W \rangle

\mathcal{G}_{1,root} = \{g \mid A_g = W\} \cup \{g \mid B_g = W\}

\mathcal{O}_{1,root} = \{B_g \mid A_g = W\} \cup \{A_g \mid B_g = W\}

Q_{1,root} = \{W\}

foreach step i do

foreach branch b in layer i do

if S_{i,b} \cap \langle \mathcal{O}_{i,b} \rangle \neq \emptyset then return False;

foreach branch b in layer i do

foreach operand A \notin \mathcal{Q}_{i,b} do

if S_{i,b} \cap (\langle A \rangle + \langle \mathcal{O}_{i,b} \rangle) \neq \emptyset then

/* add new branch b' */

S_{i+1,b'} = S_{i,b} \cap (\langle A \rangle + \langle \mathcal{O}_{i,b} \rangle)

\mathcal{G}_{i+1,b'} = \mathcal{G}_{i,b} \cup \{g \mid A \text{ is an operand of the mult. gadget } g\}

\mathcal{O}_{i+1,b'} = \mathcal{O}_{i,b} \cup \{B \mid A \text{ is an operand of a mult. gadget}\}

Q_{i+1,b'} = Q_{i,b} \cup \{A\}

end

end

end

end

end

return True

```

## Proposition 2. Algorithm 1 is correct.

Proof (sketch). The proof is organized in two parts. First, we show that there are no false negatives: if the algorithm returns False, then there is a probing attack on the input circuit C. This is done with a constructive proof. Assuming that the algorithm returns False, we construct from the graph a set of matrices (as defined in section 3.3) such that the intersection of their images is non-empty. Then we prove that there are no false positives by showing that if there is a probing attack on a circuit C, then the algorithm cannot stop as long as no attack is found. Since the algorithm has been proven to terminate, it must return False.

The complete proof is provided in Appendix B.

Complete Characterization. The verification algorithm can be slightly modified to output all the existing t-register probing attack paths on the input circuit. This extension mostly amounts to continuing to add new nodes to the graph even when an attack has been detected until no new node can be added, and slightly changing the condition to add a node. The new condition can be written  $S_{i,b} \cap (\langle A \rangle^* + \langle \mathcal{O}_{i,b} \rangle) \neq \emptyset$ , where  $\langle A \rangle^*$  denotes the set of non-null vectors of the column space of A. And with this, it is possible to determine the least attack order, which is the least amount of probes  $t_{min}$  that can be used to recover a secret value in a  $(t_{min} + 1)$ -shared circuit.

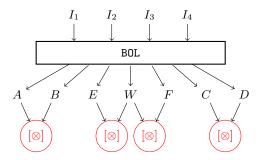

Toy example. We illustrate tightPROVE<sup>+</sup> on a toy example. The flattened circuit is displayed on Figure 4 (the extended inputs are omitted for clarity as they do not have any impact on the circuit). It uses 3-bit registers and it is made of a bitwise operation layer (BOL) that takes 4 inputs

$x_1, x_2, x_3, x_4$  and produces 7 vectors  $a, b, e, w, f, c, d \in \mathcal{V}$ , plus a single layer of multiplications. In the figure, the aforementioned variables are denoted by  $I_1, I_2, I_3, I_4$  and A, B, E, W, F, C, D, their corresponding blocks. The values we chose for those blocks are:

Fig. 4: Graph representation of the example circuit C.

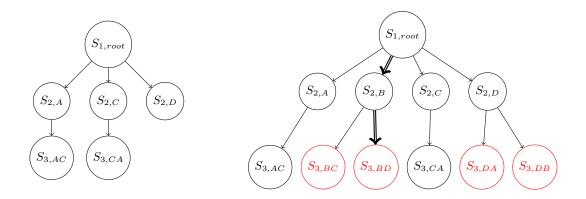

Two graphs are displayed in Figure 5 to illustrate our algorithm working on operands W and F.

Fig. 5: Examples of graphs  $\mathscr{G}_F$  (left) and  $\mathscr{G}_W$  (right) created during the algorithm.

Operand F. The algorithm starts by creating the node root. Without any constraint yet, the permissible attack span  $S_{1,root}$  is initialized to  $\langle F \rangle$ .  $\mathcal{G}_{1,root}$  contains the only multiplication for which F is a block operand: (F,W). The set of used operands  $\mathcal{Q}_{1,root}$  contains F, and thus the set of free operands  $\mathcal{O}_{1,root}$  only contains one operand block, W. All in one, the root node is built as follows:

$$\begin{cases} S_{1,root} = \langle F \rangle \\ \mathcal{G}_{1,root} = \{(F,W)\} \\ \mathcal{O}_{1,root} = \{W\} \\ \mathcal{Q}_{1,root} = \{F\} \end{cases}$$

Since  $\langle F \rangle \cap \langle W \rangle = \emptyset$ , and the current permissible attack span is not empty, new nodes are investigated to be added to the graph. Denoting by  $\mathbf{a}_1, \mathbf{a}_2, \mathbf{a}_3$  the 3 column vectors of  $A, \mathbf{b}_1, \mathbf{b}_2, \mathbf{b}_3$  the 3 column vectors of B and so on, we have

$$\langle F \rangle \cap (\langle A \rangle + \langle W \rangle) = \langle \mathbf{f}_3 \rangle \neq \emptyset$$

because  $\mathbf{f}_3 = \mathbf{a}_2$  and it is clear that we cannot obtain  $\mathbf{f}_1$  or  $\mathbf{f}_2$  from column vectors of W and A. We also have

$$\langle F \rangle \cap (\langle C \rangle + \langle W \rangle) = \langle \mathbf{f}_3 \rangle \neq \emptyset \qquad (\mathbf{f}_3 = \mathbf{c}_2)$$

and  $\langle F \rangle \cap (\langle D \rangle + \langle W \rangle) = \langle \mathbf{f}_1 \rangle \neq \emptyset \qquad (\mathbf{f}_1 = \mathbf{d}_1 + \mathbf{w}_1 + \mathbf{w}_2).$

The other intersections being empty, 3 new nodes are connected to the root one:

$$\begin{cases} S_{2,A} = \langle \mathbf{f}_3 \rangle \\ \mathcal{G}_{2,A} = \{(F,W),(A,B)\} \\ \mathcal{O}_{2,A} = \{W,B\} \\ \mathcal{Q}_{2,A} = \{F,A\} \end{cases} \begin{cases} S_{2,C} = \langle \mathbf{f}_3 \rangle \\ \mathcal{G}_{2,C} = \{(F,W),(C,D)\} \\ \mathcal{O}_{2,C} = \{W,D\} \\ \mathcal{Q}_{2,C} = \{F,C\} \end{cases} \begin{cases} S_{2,D} = \langle \mathbf{f}_1 \rangle \\ \mathcal{G}_{2,D} = \{(F,W),(D,C)\} \\ \mathcal{O}_{2,D} = \{W,C\} \\ \mathcal{Q}_{2,D} = \{F,D\} \end{cases}$$

None of the permissible attack spans in this new layer intersects with their set of free block operands, and none are empty, so the algorithm tries to find new nodes to add to each of them. No new node can be found for the last one, as  $\mathbf{f}_1$  cannot be obtained with column vectors of blocks of  $\mathcal{O}_{2,D}$  and other block operands that are not in  $\mathcal{Q}_{2,D}$ . For the first two nodes, however, we have

$$S_{2,A} \cap (\langle C \rangle + \langle \mathcal{O}_{2,A} \rangle) = \langle \mathbf{f}_3 \rangle \neq \emptyset$$

and  $S_{2,C} \cap (\langle A \rangle + \langle \mathcal{O}_{2,C} \rangle) = \langle \mathbf{f}_3 \rangle \neq \emptyset$ ,

so new nodes are created:

$$\begin{cases} S_{3,AC} = \langle \mathbf{f}_3 \rangle \\ \mathcal{G}_{3,AC} = \{ (F,W), (A,B), (C,D) \} \\ \mathcal{O}_{3,AC} = \{ W,B,D \} \\ \mathcal{Q}_{3,AC} = \{ F,A,C \} \end{cases} \begin{cases} S_{3,CA} = \langle \mathbf{f}_3 \rangle \\ \mathcal{G}_{3,CA} = \{ (F,W), (C,D), (A,B) \} \\ \mathcal{O}_{3,CA} = \{ W,D,B \} \\ \mathcal{Q}_{3,CA} = \{ F,C,A \} \end{cases}$$

None of the permissible attack spans in this last layer intersects with their corresponding set of free block operands, and none leads to the creation of new nodes, which is why the algorithm ends the creation of this graph and goes on to the next one.

Operand W. Since the first steps are similar to the previous example, only the steps that lead to an attack are detailed hereafter. The full graph can be found in Figure 5 in which red circles denote nodes where an attack is found. We detail the construction of the nodes on the path displayed with a double arrow.

The algorithm starts by creating the *root* node:

$$\begin{cases} S_{1,root} = \langle W \rangle \\ \mathcal{G}_{1,root} = \{(W,E),(W,F)\} \\ \mathcal{O}_{1,root} = \{E,F\} \\ \mathcal{Q}_{1,root} = \{W\} \end{cases}$$

As  $\langle W \rangle \cap \langle \{E, F\} \rangle = \emptyset$ , the algorithm searches for new nodes to add. Since

$$\langle W \rangle \cap (\langle B \rangle + \langle \{E, F\} \rangle) = \langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \neq \emptyset \qquad (\mathbf{w}_1 + \mathbf{w}_2 = \mathbf{b}_1 + \mathbf{b}_3 + \mathbf{e}_1),$$

the following node is created:

$$\begin{cases} S_{2,B} = \langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \\ \mathcal{G}_{2,B} = \{ (W, E), (W, F), (B, A) \} \\ \mathcal{O}_{2,B} = \{ E, F, A \} \\ \mathcal{Q}_{2,B} = \{ W, B \} \end{cases}$$

There is still no attack at this point, as  $\langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \notin \langle \{E, F, A\} \rangle$ . However,

$$\langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \cap (\langle D \rangle + \langle \{E, F, A\} \rangle) = \langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \neq \emptyset$$

$(\mathbf{w}_1 + \mathbf{w}_2 = \mathbf{d}_1 + \mathbf{f}_1),$

so the following node is created:

$$\begin{cases} S_{3,BD} = \langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \\ \mathcal{G}_{3,BD} = \{(W, E), (W, F), (B, A), (D, C)\} \\ \mathcal{O}_{3,BD} = \{E, F, A, C\} \\ \mathcal{Q}_{3,BD} = \{W, B, D\} \end{cases}$$

This time, we have  $\langle \mathbf{w}_1 + \mathbf{w}_2 \rangle \in \langle \{E, F, A, C\} \rangle$ , as  $\mathbf{w}_1 + \mathbf{w}_2 = \mathbf{a}_1 + \mathbf{c}_1$ . Thus there exists a register probing attack, and the algorithm returns False.

Let us now go one step further by showing that this circuit is not tight t-register probing secure for any  $t \geq 4$ . We assume that the circuit is d-shared with  $d \geq 5$ , and denote by  $w_{i,j}$  the  $i^{th}$  coordinate of the  $j^{th}$  share of  $[\mathbf{w}]$ , by  $a_{i,j}$  the  $i^{th}$  coordinate of the  $j^{th}$  share of  $[\mathbf{a}]$  and so on. By probing the multiplications (A, B), (C, D), (W, E) and (W, F), an attacker can get the values of

- $-a_{1,0}, b_{1,1}, b_{3,1}$  with a probe on (A, B) targeting shares 0 for A and 1 for B,

- $-c_{1,0}, d_{1,2}$  with a probe on (C, D) targeting shares 0 for C and 2 for D,

- $-w_{1,3}, w_{2,3}, e_{1,1}$  with a probe on (W, E) targeting shares 3 for W and 1 for E,

- $-w_{1,4}, w_{2,4}, f_{1,2}$  with a probe on (W, F) targeting shares 4 for W and 2 for F.

With those values, one can compute:

$$\begin{aligned} w_{1,0} + w_{2,0} &= a_{1,0} + c_{1,0} \\ w_{1,1} + w_{2,1} &= b_{1,1} + b_{3,1} + e_{1,1} \\ w_{1,2} + w_{2,2} &= d_{1,2} + f_{1,2} \\ w_{1,3} + w_{2,3} \\ w_{1,4} + w_{2,4} \end{aligned}$$

With 4 probes, an attacker can thus get the sum of the first two coordinates of 5 shares of  $\mathbf{w}$ , i.e., the circuit is not tight t-register probing secure for  $t \ge 4$ .

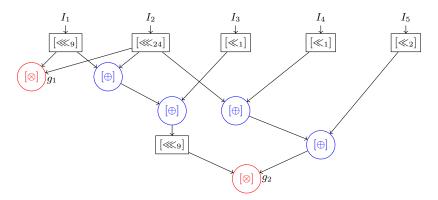

Concrete Example. We now present an example that shows how tightPROVE<sup>+</sup> applies to reallife implementations of cryptographic primitives. We take as example an Usuba implementation of the Gimli [10] cipher, a 384-bit permutation, with 32-bit registers. When applying tightPROVE<sup>+</sup> on this circuit, register probing attacks are identified. Let us describe one of them and display the subgraph of the circuit it is based on in Figure 6.

The subcircuit uses 5 input blocks  $I_1, I_2, I_3, I_4, I_5$ . We denote by [x] the sharing obtained after the rotation of  $I_2$  and [y] the one after the rotation of  $I_1$ . By probing the multiplication  $g_1$ , one can get the values  $x_{32,0}$  and  $y_{32,1}$  (the first index denotes the bit slot in the register and the second one denotes the share). Due to the left shifts, one can get the values  $x_{32,2}$  and  $x_{32,1} + y_{32,1}$  by probing  $g_2$ . The following values can thus be obtained:  $x_{32,0}, x_{32,1} = (x_{32,1} + y_{32,1}) + y_{32,1}$ , and  $x_{32,2}$ . This implies that  $x_{32}$ , the last slot of the secret value x, can be retrieved with t probes when the circuit is (t+1)-shared for any  $t \geq 2$ .

### 4 Tornado: Automating Slicing & Masking

Given a high-level description of a cryptographic primitive, Tornado synthesizes a masked implementation using the ISW-based multiplication and refresh gadgets. The gadgets are provided as C functions, presented in Figure 7 and where the macro MASKING\_ORDER is instantiated at compile time to the desired masking order. The key role of Usuba is to automate the generation of a sliced implementation, upon which tightPROVE<sup>+</sup> is then able to verify either the bit probing or register probing security, or identify the necessary refreshes. By integrating both tools, we derive a masked implementation from the sliced one. This is done by mapping linear operations over all shares, by using isw\_mult for bitwise and operations and by calling isw\_refresh where necessary.

Fig. 6: Graph representation of a sub-circuit of Gimli.

```

static void isw_mult(uint32_t *res,

static void isw_refresh(uint32_t *res,

const uint32_t *op1,

const uint32_t *in) {

const uint32_t *op2)

for (int i=0; i<=MASKING_ORDER; i++)</pre>

for (int i=0; i<=MASKING_ORDER; i++)</pre>

res[i] = in[i];

res[i] = 0;

for (int i=0: i<=MASKING ORDER: i++) {

for (int j=i+1; j<=MASKING_URDER; j++) {

for (int j=i+1; j<=MASKING_ORDER; j++) {

uint32_t rnd = get_random();

res[i] ^= rnd;

res[j] ^= rnd;</pre>

for (int i=0; i<=MASKING_ORDER; i++) {</pre>

res[i] ^= op1[i] & op2[i];

for (int j=i+1; j<=MASKING_ORDER; j++) {</pre>

uint32_t rnd = get_random();

res[i] ^= rnd;

}

^= (rnd ^ (op1[i] & op2[j]))

res[i]

(op1[j] & op2[i]);

}

```

Fig. 7: ISW gadgets.

The overall architecture of the Tornado compiler is shown in Figure 8. It consists essentially in the integration of Usuba and tightPROVE<sup>+</sup> within a single, unified framework. This integration is reasonably simple since the Usuba<sub>0</sub> intermediate representation amounts essentially to a register-based circuit extended with a notion of function node (for code reuse), whereas the input language of tightPROVE<sup>+</sup> consists in unrolled inlined register-based circuits. We therefore easily obtain an input suitable for tightPROVE<sup>+</sup> by inlining all the nodes within the Usuba<sub>0</sub> generated by Usuba. We also need to specify the probing model to use when carrying the analysis in tightPROVE<sup>+</sup>: this corresponds exactly to the typing information specified in Usuba, whether we are considering a bitsliced implementation (in which case we select the bit probing model), or an *n*-sliced implementation (in which case we select the register probing model, registers whose size is *m*).

Fig. 8: High-level view of the Tornado compiler.

Having sent a register-based circuit to the extended tool tightPROVE<sup>+</sup>, it may either be accepted as-is or tightPROVE<sup>+</sup> may have identified necessary refresh points to achieve bit or register probing security. In the latter case, Tornado maps these refresh points back into the initial, non-inlined Usuba<sub>0</sub> code: each refresh point is turned into a custom refresh operator that is treated specifically by the Tornado backend (in particular, it cannot be optimized out). Upon emitting C code, this operator turns into a call to the isw\_refresh gadget of Figure 7.

#### 4.1 Addition of Refresh Gadgets

In order to make the generation of secure masked implementations fully automatic, we use heuristic methods to determine a set of operands to be refreshed in order to make the resulting circuit secure in the considered probing model.

When a circuit is built from the combination of several instances of the same subcircuit, the description of the subcircuit is analyzed first, assuming that it has random, uniform and independent inputs. If probing attacks are found, an exhaustive search of the placement of refresh gadgets can be done if the size of the subcircuit is not too big. The same placement of refresh is then applied every time this subcircuit appears. Doing so is relevant, as any attack that can be done on a subfunction alone also exists when that subfunction is part of a wider circuit.

Then, tightPROVE<sup>+</sup> verifies that the resulting circuit is secure. If probing attacks are still found, then tightPROVE<sup>+</sup> is called in full characterization mode which yields the complete list of multiplications involved in each attack. We then select an operand of the multiplication that appears the most in that list, and apply a refresh to this operand. This step is repeated until no more attacks can be found. This method is bound to stop and yield a secure circuit since, as proven in the original paper describing tightPROVE, refreshing one input per multiplication guarantees that the resulting circuit is secure.

We stress that this method is not optimal in the sense that it does not always find the minimal number of refresh gadgets needed to make a circuit secure, but it provides a sound heuristic. Finding an optimal and efficient method to place refresh gadgets is left open for future research.

#### 4.2 Optimizations

Whereas this compilation scheme is functionally sufficient to guarantee security, further optimizations are beneficial to make it scale to large masking orders on a typical embedded platform. Tornado therefore integrates a modicum of optimizations to optimize stack usage (especially for bitsliced implementations), to reduce the overhead of repeatedly iterating over shares and to minimize the number of masked multiplications. Note that the objective of the present work is not to demonstrate best-in-class performance results: we are instead interested in 1. the asymptotic performance of a given primitive across a sizable choice of masking orders; and 2. the comparative performance of sizable number primitives at a given masking order.

To this end, Tornado has proved to be a valuable tool. We enable the first point by minimizing the impact that the C compiler can have on the quality (or lack thereof) of the resulting code. For example and as the masking order grows, the compiler tends to shy away from certain loop-related optimizations that are beneficial. We therefore systematically carry these optimizations in Tornado. We enable the second point by subjecting all the primitives to the same, predictable (even if imperfect) compilation process tailored to the platform of interest.

We have therefore identified two optimizations that are necessary to scale to large masking orders: aggressive constant propagation for multiplications and loop fusion. Masked multiplication being expensive, we strive to spot the case where the operand of a multiplication is in fact a constant value. We do so through a constant propagation analysis in  $Usuba_0$  followed by a specific compilation rule in this case: we directly multiply all the shares with the constant.

To mask a sequence of instructions, Tornado replaces each of them with a masked gadget. Gadgets for linear operations consist in a loop applying iteratively a basic operation over each share, such as

```

for (int i=0; i<=MASKING_ORDER; i++) A(i);

for (int i=0; i<=MASKING_ORDER; i++) B(i);

for (int i=0; i<=MASKING_ORDER; i++) C(i);</pre>

```

where A, B and C are linear operations storing their results in a number of variables linear with MASKING\_ORDER. As a result, stack usage increases linearly with the masking order, which means that, when considering implementations as register-hungry as bitslicing ones, even small masking orders can be too heavy. Besides, operating each loop (increment, comparison, branching) impedes an overhead that the C compiler is something heuristically willing to optimize out at small orders, leading to confusing threshold effects when benchmarking. To address both issues, we systematically perform loop fusion, thus obtaining

```

for (int i=0; i<=MASKING_ORDER; i++) {

A(i); B(i); C(i);

}</pre>

```

on the above example, followed by instruction scheduling, which will strive to reduce the live range [29] (and thus the number of temporaries) of, for example, the variables set in A and used in B.

This optimization allows us to reduce stack usage of our bitsliced implementations by 11kB on average whereas this saves us, on average, 3kB of stack for our n-sliced implementations (recall that our platform offers a measly 96kB of SRAM). It also positively impacts performance, with a 16% average speedup for bitslicing and a 21% average speedup for n-slicing.

## 5 Evaluation

We evaluated Tornado on 11 cryptographic primitives from the second round of the NIST lightweight cryptography competition<sup>6</sup>. The choice of cryptographic primitives was made on the basis that they were self-identified as being amenable to masking. We stress that we do not focus on the full authenticated encryption, message authentication, or hash protocols but on the underlying primitives, mostly block ciphers and permutations.

Table 1 provides an overview of these primitives. Whenever possible, we generate both a bit-sliced and an n-sliced implementation for each primitive, which allows us to exercise the bit-probing and the register-probing models of tightPROVE<sup>+</sup>. However, 4 primitives do not admit a straightforward n-sliced implementation. The Subterranean permutation involves a significant amount of bit-twiddling across its 257-bit state, which makes it a resolutely bitsliced primitive (as confirmed by its reference implementation). Photon, Skinny, Spongent rely on lookup tables that would be too expansive to emulate in n-sliced mode. In bitslicing, these tables are simply implemented by their Boolean circuit, either provided by the authors (Photon, Skinny) or generated through SAT [34] with the objective of minimizing multiplicative complexity (Spongent, with 4 ANDs and 28 XORs). Spook and Elephant respectively rely on the Clyde and Spongent primitives, which we therefore include in our evaluation.

Note that the *n*-sliced implementations, when they exist, are either 32-sliced or 64-sliced. This means in particular that, unlike bitslicing that processes multiple blocks in parallel, these implementations process a single block at once on our 32-bit Cortex M4.

In Subsection 5.1, we present the results of tightPROVE<sup>+</sup> on the considered primitives using the refresh placement strategy explained in Subsection 4.1. Finally, we benchmark our unmasked implementations against reference implementations in Subsection 5.2, and compare their masked versions in Subsection 5.3.

## 5.1 tightPROVE+

Table 2 contains the results of tightPROVE<sup>+</sup> for the aforementioned primitives. We display the output of our algorithm for each circuit, along with the size of the registers used and the time it takes for tightPROVE<sup>+</sup> to output the results. Table 3 provides additional information about the implementations that are not secure in the register probing model. This includes the size of the registers, the time it takes to find the first attack, the time it takes to find all the operands that

<sup>&</sup>lt;sup>6</sup> See https://csrc.nist.gov/Projects/lightweight-cryptography/round-2-candidates for the list of candidates together with specifications and reference implementations.

Table 1: Overview of the selected cryptographic primitives.

| ,.                | state size | multip  | lications | mult            | ./bits   | 1: 1.1              | slice |

|-------------------|------------|---------|-----------|-----------------|----------|---------------------|-------|

| primitive         | (bits)     | n-slice | bitslice  | <i>n</i> -slice | bitslice | <i>n</i> -sliceable | size  |

| Ace [1]           | 320        | 384     | 12288     | 1.2             | 38       | <b>√</b>            | 32    |

| Ascon [23]        | 320        | 60      | 3840      | 0.19            | 12       | ✓                   | 64    |

| Clyde [9]         | 128        | 48      | 1536      | 0.37            | 12       | ✓                   | 32    |

| Gift [3]          | 128        | 160     | 5120      | 1.25            | 40       | ✓                   | 32    |

| Gimli [11]        | 384        | 288     | 9216      | 0.75            | 24       | ✓                   | 32    |

| Рнотом [4]        | 256        | -       | 3072      | -               | 12       | X                   | -     |

| Pyjamask [24]     | 128        | 56      | 1792      | 0.44            | 14       | ✓                   | 32    |

| SKINNY [7]        | 128        | -       | 6144      | -               | 48       | X                   | -     |

| SPONGENT [13, 14] | 160        | -       | 12800     | -               | 80       | X                   | -     |

| Subterranean [22] | 257        | -       | 2056      | -               | 8        | X                   | -     |

| Xoodoo [21, 20]   | 384        | 144     | 4608      | 0.37            | 12       | ✓                   | 32    |

can be retrieved, then the least attack order, the optimal number of refresh gadgets needed to make the implementation secure in the register probing model, and finally the time tightPROVE<sup>+</sup> takes to verify that the refreshed implementation is indeed secure. All calculations were made on an iMac with an intel Core i7 processor (4 GHz) and 16 GB of DDR3 RAM (1600 MHz), with parallel computing on its 8 CPUs.

Following the method described in Section 4.1, tightPROVE<sup>+</sup> places refresh gadgets for the considered implementations of ACE, Clyde and Gimli. For the two first primitives, there is exactly one subcircuit which is responsible for the identified register probing attacks, which can be fixed by adding only one refresh gadget. This gives us a lower bound for the optimal number of refresh gadgets, and since tightPROVE<sup>+</sup> does not find any further attack after the addition of refresh gadgets, it is also an upper bound. Gimli, however, is made of 6 subsequent identical subcircuits that are subject to register probing attacks, but the method uses 20 refresh gadgets per subcircuits to make the implementation secure. We can thus only conclude that we have an upper bound of 120 for the optimal number of gadgets, and that it is a multiple of 6, but in the current method, we cannot ascertain that it is optimal without setting up an exhaustive search.

## 5.2 Baseline Performance Evaluation

In the following, we benchmark our implementations – in Usuba and compiled with Tornado – of the NIST submissions against the reference implementation provided by the contestants. This allows us to establish a performance baseline (without masking), thus providing a common frame of reference for the performance of these primitives based on their implementation synthesized from Usuba. In doing so, we have to bear in mind that the reference implementations provided by the NIST contestants are of varying quality: some appear to have been finely tuned for performance while others focus on simplicity, acting as an executable specification.