## Conducted EMI reduction in a 100kW 1.2kV Dual Active Bridge converter

Hadiseh Geramirad, Florent Morel, Piotr Dworakowski, Bruno Lefebvre, Thomas Lagier, Philippe Camail, Christian Vollaire, Arnaud Bréard

## ▶ To cite this version:

Hadiseh Geramirad, Florent Morel, Piotr Dworakowski, Bruno Lefebvre, Thomas Lagier, et al.. Conducted EMI reduction in a 100kW 1.2kV Dual Active Bridge converter. PCIM Europe digital days 2020, Jul 2020, Virtual, Germany. hal-02942284v2

## HAL Id: hal-02942284 https://hal.science/hal-02942284v2

Submitted on 17 Apr 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Conducted EMI reduction in a 100kW 1.2kV Dual Active Bridge converter

Hadiseh GERAMIRAD<sup>1,2</sup>, Florent MOREL<sup>1</sup>, Piotr DWORAKOWSKI<sup>1</sup>, Bruno LEFEBVRE<sup>1</sup>, Thomas LAGIER<sup>1</sup>, Philippe CAMAIL<sup>1</sup>, Christian VOLLAIRE<sup>1,2</sup>, Arnaud BREARD<sup>2</sup>

Corresponding author: Hadiseh GERAMIRAD, hadiseh.geramirad@supergrid-institute.com

### **Abstract**

Medium-frequency transformer is one of the key components of isolated power electronic converters. The parasitic capacitances of the transformer provide paths for the common-mode current inside the converter. The electromagnetic interferences due to fast switching are among the main concerns for the design of SiC MOSFET based power converters. The conducted emissions of the converter are directly linked to its physical layout. In this work, the main loops of the common-mode current in the presence of a 3-phase medium-frequency transformer are discussed. The experimental studies show the effects of the transformer construction and vector group (star/delta) on the common-mode currents through the gate drivers of SiC MOSFETs in a 100kW 1.2kV three-phase dual active bridge converter.

#### 1 Introduction

The maturity of commercial high-voltage highcurrent semiconductors such as 1.7kV SiC MOSFETs allows converter designers to improve power converters density and efficiency [1]. Using SiC MOSFET results in fast rising and falling of the voltage and current which creates unwanted currents due to the parasitic inductances and capacitances in the layout of the converter [2]-[4]. Therefore, using SiC MOSFETs as switching element of power converters increases the electromagnetic interferences (EMI). For this reason, implementing SiC MOSFETs and dealing with the generated EMI added a new dimension to the design of power converters. To solve an aforementioned EMI problem in a converter, it should be considered that the parasitic elements change over their frequency band, the topology of the converter changes from one design to another one, the switching speed can vary based on the converter, etc. Therefore, there is not a well-defined design methodology. It is then difficult to have a general attitude to solve the problem [5]. In addition, the size and cost of the electromagnetic filter to reduce the EMI become an important factor in high

power-density converters [6]–[8]. So reducing the common-mode (CM) noise of the power converter can help to simplify the filter design and to reduce the total size.

In isolated DC/DC converters, there are plenty of coupling capacitances which provide paths for CM current [9]-[12]. In most of the cases, a CM electromagnetic disturbance issue is due to the circulation of the CM current into the layout of the converter [13]. It is always a challenge to ensure that the CM current of a converter is well-controlled in order to not disturb its critical elements like gate drivers and controllers. In the converter, a gate driver has to provide at least two functions, the signal transmission and the power supply for switching [14]. The signal transmission includes signals for switching orders and protection of the device. The power supply design is challenging since this part of the circuit should provide a high isolation with a low coupling capacitance. The gate driver is one of the EMI victims in the converter due to the parasitic capacitances in its isolation stages [15]. Since gate drivers provide an interface between the controller and the switches, the CM current can disturb the controller [16]. A limited

<sup>&</sup>lt;sup>1</sup> SAS SuperGrid Institute, ITE, France

<sup>&</sup>lt;sup>2</sup> Ecole centrale de Lyon, Ampère lab, CNRS 5005, France

CM current passing through the gate driver is required in order to guarantee proper operation of the converter. For a commercial gate driver, the isolation is defined and cannot be change. However, a proper design of the converter can change the CM current. Hence, identification and investigation on the CM current in an isolated DC/DC converter is the objective of this work.

Understanding the effect of the parasitic elements in the converter layout provides a basis for applying the EMI reduction techniques. There are several studies focused on EMI modelling and analysis of dual active bridge (DAB) converters [17]-[21]. There are some experimental works for flyback converters [22]-[25] but there are not a lot of researches focused on experimental EMI behaviour of a 3-phase DAB (DAB3) using SiC MOSFETs. The uncontrolled CM currents pass through gate drivers (input CM current) and disturb the proper turn-on and turn-off of the switches. This is the problematic case in this prototype above 800V, 100kW. This phenomenon is called here "self-disturbance". It was encountered as an obstacle to achieve the nominal operation of the converter. Changing the parasitic elements, once the design completed, is costly and time consuming, therefore, here with comparative experimental study, it is targeted to show the effect of the MFT design on the input CM current of gate drivers and highlight the effect of the transformer design on the self-disturbance phenomenon. So as, this paper analyses the CM current behaviour of the DAB3 based on different transformer structures with the following organisation. Section 2 describes the DAB3 used as a test-platform in this study. Section 3 presents the paths of the CM current in the converter. In section 4, the proposed model is experimentally validated and the influence of different transformer designs on the CM current is analysed. Section 5 concludes the article.

#### 2 Considered converter

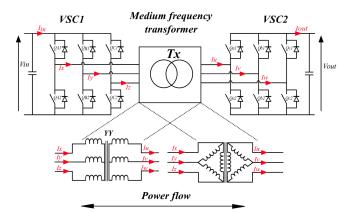

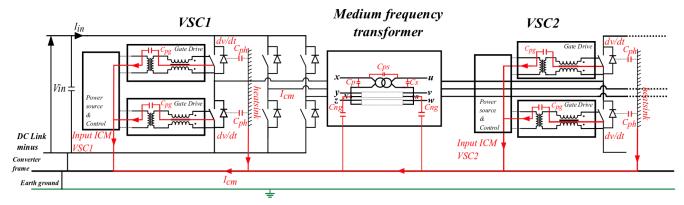

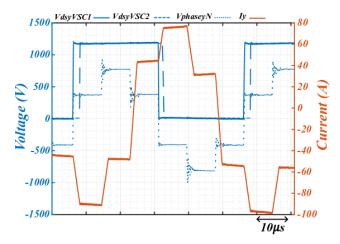

A 3-phase DAB is made of two voltage source converters (VSC) connected through a 3-phase medium frequency transformer (MFT). Both VSCs are composed of three legs of half-bridge power semiconductors which are controlled by half-bridge

gate drivers (see Fig. 1). In the operation of the DAB, each VSC generates a square waveform. A controlled phase shift  $\delta$  between the primary and secondary voltages can control the power flow through the MFT. Thus the power can be transmitted from VSC1 to VSC2 or vice versa (the direction from VSC1 to VSC2 is called here as +P and opposite direction as -P).

Fig. 1: Dual active bridge schematic.

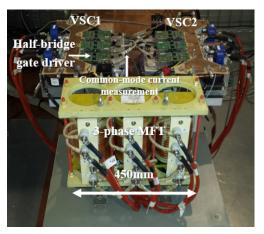

Fig. 2: 100kW, 1200V, DAB3 prototype.

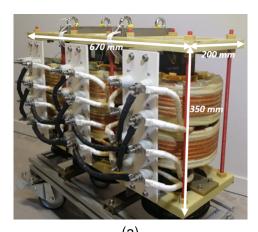

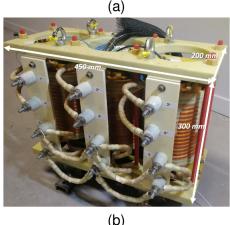

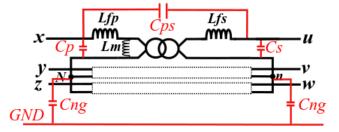

The investigation has been carried out in this work on a new 3-phase 100kW 1.2kV dual active bridge converter prototype (see Fig. 2) [26], [27]. The considered DAB3 is sized for 100kW power transfer at 20kHz switching frequency, 11kV/ $\mu$ s switching speed and benefits from soft switching capabilities in both VSCs with identical gate drivers. The novelty of this DAB3 is the 3-phase MFT design which is focused to establish a power flow between 1.2kV DC-links [28] (see Fig. 3). In the structure of the transformer, there are three types of parasitic capacitances. The parasitic capacitance between winding layers ( $C_p$  and  $C_s$  in Fig. 4), the inter-winding capacitance between primary winding

and secondary winding ( $C_{ps}$  in Fig. 4) and the parasitic capacitance between neutral point to the ground in YY configuration ( $C_{ng}$  in Fig. 4). The model parameters of the transformers (see Fig. 4) are presented in table 1. The transformer T1 can operate in  $\Delta\Delta$  or YY configurations while T2 can operate only in YY configuration.

**Fig. 3:** Medium frequency transformer (a) T1 prototype (b) T2 prototype.

**Fig. 4:** Transformer model in *YY* configuration.

## 3 Common-mode current paths

The noise source in each leg of the VSC is the voltage variation across MOSFETs/diodes. The propagation paths are provided by coupling

**Tab. 1:** Parameters of the transformers based on impedance measurement in YY configuration.

| Parameter | Unit    | <b>T</b> 1 | <b>T2</b> |

|-----------|---------|------------|-----------|

| $L_{fp}$  | $\mu H$ | 17         | 8         |

| $L_{fs}$  | $\mu H$ | 17         | 8         |

| $L_m$     | mH      | 1          | 1         |

| $C_p$     | pF      | 30         | 65        |

| $C_S$     | pF      | 30         | 60        |

| $C_{ps}$  | pF      | 80         | 85        |

| $C_{ng}$  | pF      | 30         | 50        |

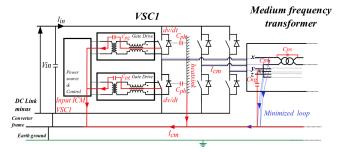

capacitances in the layout of the converter which experience high  $\frac{dv}{dt}$ . The main coupling capacitors that are subject to fast variations of the voltage are shown in figure 5. During a fast voltage variation across a switch, the parasitic capacitances in the isolation stages of its gate driver provide coupling paths for CM currents to pass through the gate drivers and consequently to the converter controller [10] ( $C_{pq}$  in Fig. 5). The voltage variation along the windings of the transformer makes the parasitic capacitances of the transformer as other paths in which the current can circulate [29] from one VSC to the another and also shunt the CM current to the ground ( $C_s$ ,  $C_p$ ,  $C_{ng}$  and  $C_{ps}$  in Fig. 5) [23]. Parasitic capacitance between the device and the heat-sink [18], provide another path for the CM current to the ground ( $C_{ph}$  in Fig. 5). The existence of these parasitic paths in the layout of the converter is unavoidable and also changing the value of the related capacitances can not be done after design phase. In practice, due to physical limitations, it is very difficult to measure all the CM currents which makes the analysis even more difficult. Then, the amplitude of the time domain waveform of the input CM current through gate drivers is the EMI criteria of this study. A comparative study has been done to illustrate the effect of the MFT design on the input CM current through gate drivers.

## 4 Experimental results and analysis

The experimental study has been done by conducting continuous-mode tests on the converter

Fig. 5: CM current paths in an isolated dual active bridge converter.

prototype (Fig. 2) at 800V, 100kW with T1 and T2 and it has been completed in nominal operation of the converter at 1200V, 100kW with T2 only. The investigation has been focused on the phase B (y for VSC1 and v for VSC2) of the converter considering that the analysis can be applied for the rest of the system. The input CM current of the half-bridge gate driver of the phase B has been measured with different transformer configurations and with both MFT designs.

#### 4.1 Common-mode current circulation

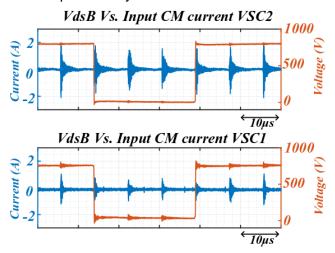

As each leg of VSCs switches at  $20 \mathrm{kHz}$ , each switch creates a CM current each  $25 \mu \mathrm{s}$ . The experimental results shown in figures 6 and 7 revealed that the generated CM current passing through a gate driver is not dominated only by the voltage variation across the corresponding switch but also due to the voltage variation in other legs of the same VSC and even the complementary VSC.

**Fig. 6:** Experimental measurement of Vds and input CM current in 800V, 0kW, T1 in *YY* configuration.

**Fig. 7:** Experimental measurement of Vds and input CM current in 800V, +100kW, T1 in *YY* configuration.

It can be seen that due to the physical electrical connection, the CM current passing through the gate driver of one switch is changed based on the phase shift variation in the converter. When the converter operates at zero power, there is no phase shift between the VSCs while by increasing the phase shift, the CM current changed based on the voltage phase shift in both VSCs.

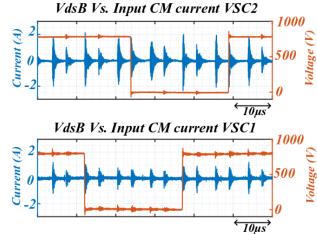

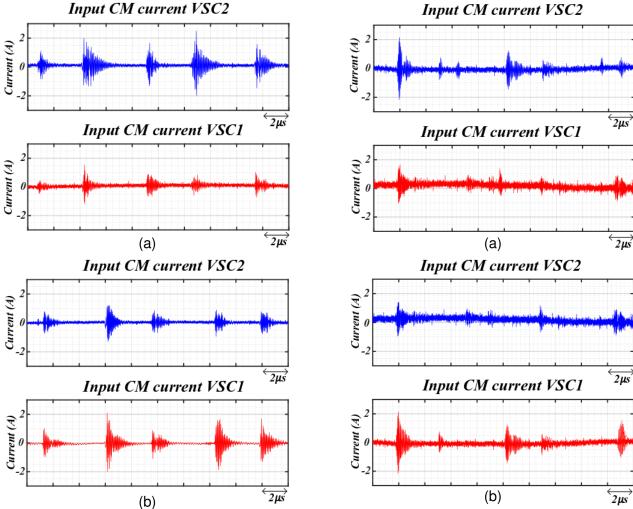

To show the circulation of the CM current from one VSC to another, the CM current of the gate driver has been measured in both power flow directions. Experimental results (see Fig. 8) reveal the difference between the magnitude of the two input CM currents.

By repeating the same measurement but in opposite power flow (from VSC2 to VSC1 indicated as -P), it is shown that the input CM current of VSC2 is similar to input CM current of VSC1 in +P. Due to the phase shift between VSC1 and VSC2 controls, these converters do not switch the

Fig. 8: Experimental comparison of input CM current, 800V, MFT1 in YY configuration (a) +100kW (b) -100kW.

Fig. 9: Experimental measurement of input CM current, 800V, MFT1 in  $\Delta\Delta$  configuration (a) +100kW (b) -100kW.

same current amplitudes. That is why the input CM current amplitudes differs by inverting the power flow. The phase shift is reverted in -P and the phenomena observed in VSC2 in P has been occurred in VSC1 in -p [30]. The inter-winding capacitance of the transformer provides a path for the CM to transfer from one VSC to the other (see Fig. 4) which changes the amplitude of the CM current. The performance of the converter with T1 in  $\Delta\Delta$  configuration has been tested. It changed the waveforms of the input CM current but its amplitude has not been changed by changing vector group (see Fig. 9).

#### 4.2 Common-mode current reduction

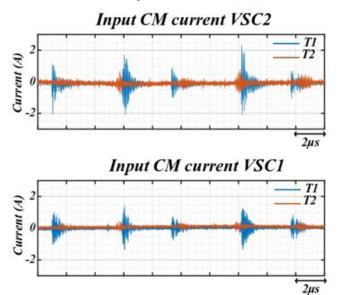

CM current is always passing through the coupling path with less impedance. If the transformer

parasitic capacitances are bigger than the parasitic capacitances of the gate driver isolation, then the CM current will pass more through the transformer than through the gate driver. These capacitances (see Fig.4) can change based on the transformer design. In this section, to show the effects of these capacitances on CM current through the gate driver, the CM current has been measured with two different designs of the transformers in YY configuration. Note that with these designs, values of  $C_{ps}$  are almost the same while values of  $C_{ng}$  are quite different (see Table. 1).

Due to the more compact design of T2 (dimension and size of the windings [28]), the neutral point to ground capacitance ( $C_{ng}$ ) provides an almost two times smaller impedance path to the ground compared to T1. The bigger capacitance leads

to a smaller impedance, which is preferred to pass through by the CM current. The parasitic capacitances shunt a significant amount of CM current to the ground, and since, the CM current through gate driver is reduced. The minimized loop is shown in figure 10.

**Fig. 10:** Minimized loop of the CM current due to a different design of the MFT2.

**Fig. 11:** Experimental result of input CM current of gate driver, comparison between two transformers design in 800V, 100kW.

The input CM current has been measured in the same configuration by changing the transformer. The experimental results validate how parasitic capacitances of T2 shorten the CM current path then reduce the CM current through gate drivers (see Fig. 11). Not only the CM current due to switching in phase B, but also the generated CM current due to the other phases found a shorter impedance to flow. This reduces the CM current of the gate driver significantly. Thanks to the optimised design of the transformer, the nominal operation of the converter has been achieved at 1200V, 100kW (see Fig. 12).

**Fig. 12:** Experimental converter waveform, isolation with T2 in 1200V, 100kW.

## 5 Conclusion

In the design of isolated converters, medium-frequency transformers provide a galvanic isolation while introducing, at high frequencies, a low impedance path for common-mode current between primary and secondary. The provided path allows the circulation of current through gate drivers. This paper compared experimentally two different designs of the transformer in the same layout of the converter to show the effects of the transformer design on the common-mode current through the gate drivers. The nominal operation of the converter has been achieved thanks to an improved design of the medium-frequency transformer since it reduces the input common-mode current of the gate driver and solve the self-disturbance phenomenon.

Adopting a filter connected to the transformer starpoint in order to reduce the impedance of the CM current from neutral point to ground to minimize the CM current loop and introducing a screen between primary and secondary windings and connecting this screen to ground are possible perspectives for this work.

## **Acknowledgement**

This work was supported by a grant overseen by the French National Research Agency (ANR) as part of the "Investissements d'Avenir" Program (ANE-ITE-002-01).

## References

- [1] J. Palmour, L Cheng, V Pala, E. Brunt, D. Lichtenwalner, et al., "Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), IEEE, 2014, pp. 79–82.

- [2] D. Pavel and K. Vaclav, "EMC issues of power electronic converters," in 2009 IEEE International Symposium on Electromagnetic Compatibility, IEEE, 2009, pp. 296–301.

- [3] F. Costa and D. Magnon, "Graphical analysis of the spectra of EMI sources in power electronics," *IEEE Transactions on Power Electronics*, vol. 20, no. 6, pp. 1491–1498, 2005.

- [4] E. Rondon, F. Morel, C. Vollaire, and J. Schanen, "Impact of SiC components on the EMC behaviour of a power electronics converter," in 2012 IEEE Energy Conversion Congress and Exposition (ECCE), 2012, pp. 4411–4417.

- [5] M. R. Yazdani, H. Farzanehfard, and J. Faiz, "Classification and comparison of EMI mitigation techniques in switching power converters-A review," *Journal of Power Electronics*, vol. 11, no. 5, pp. 767–777, 2011.

- [6] J. Le Lesle, R. Caillaud, F. Morel, N. Degrenne, C. Buttay, et al., "Optimisation of an Integrated Bidirectional Interleaved Single-Phase Power Factor Corrector," in PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2018, pp. 1–8.

- [7] J. Le Leslé, R. Caillaud, F. Morel, N. Degrenne, C. Buttay, et al., "Optimum design of a single-phase Power Pulsating Buffer (PPB) with PCB-integrated inductor technologies," in 2018 IEEE International Conference on Industrial Technology (ICIT), 2018, pp. 782–787.

- [8] J. Le Leslé, R. Caillaud, F. Morel, N. Degrenne, C. Buttay, and R. Mrad, "Multi-objective optimisation of a bidirectional single-phase grid connected AC/DC converter (PFC)

- with two different modulation principles," in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), 2017, pp. 5298–5305.

- [9] H. Zhang, S. Wang, Y. Li, Q. Wang, and D. Fu, "Two-capacitor transformer winding capacitance models for common-mode EMI noise analysis in isolated DC–DC converters," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8458–8469, 2017.

- [10] A. Anurag, S. Acharya, Y. Prabowo, G. Gohil, and S. Bhattacharya, "Design Considerations and Development of an Innovative Gate Driver for Medium-Voltage Power Devices With High dv/dt," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5256–5267, 2018.

- [11] P. Zdenek and D. Pavel, "Electromagnetic compatibility issues of variable speed drives," in 2002 IEEE International Symposium on Electromagnetic Compatibility, IEEE, vol. 1, 2002, pp. 308–313.

- [12] R. Naayagi, "Electromagnetic compatibility issues of dual active bridge DC-DC converter," in 2013 International Conference on Energy Efficient Technologies for Sustainability, IEEE, 2013, pp. 699–703.

- [13] S. Gulur, V. M. Iyer, and S. Bhattacharya, "Improved Common Mode Noise Models for Three Level T-Type Neutral Point Clamped Converters," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, 2018, pp. 6398–6403.

- [14] L. Ghossein, F. Morel, H. Morel, and P. Dworakowski, "State of the Art of Gate-Drive Power Supplies for Medium and High Voltage Applications," in PCIM Europe 2016; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2016, pp. 1–8.

- [15] F Costa, E Labouré, F Wilmot, F Forest, F Reby, and C. Rombaut, "An innovative gate drive to control electromagnetic perturbations emitted by a MOSFET chopper," *EPE '99, Lausanne*, 1999.

- [16] H. Geramirad, F. Morel, B. Lefebvre, A. Bréard, and C. Vollaire, "Experiemental study of the self-disturbance phenomena in a half-bridge configuration of SiIGBT and SiC MOSFET switches, PCIM 2020 (in press)," 2020.

- [17] M. A. Saket, N. Shafiei, and M. Ordonez, "Planar transformer winding technique for reduced capacitance in LLC power converters," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, 2016, pp. 1–6.

- [18] S. Kumar, S. K. Voruganti, and G. Gohil, "Common-mode Current Analysis and Cancellation Technique for Dual Active Bridge Converter based DC System," in 2019 IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, pp. 6949–6956.

- [19] D. Hamza and P. K. Jain, "Conducted EMI noise mitigation in DC-DC converters using active filtering method," in 2008 IEEE Power Electronics Specialists Conference, IEEE, 2008, pp. 188–194.

- [20] M. Vilathgamuwa, J Deng, and K. Tseng, "EMI suppression with switching frequency modulated DC-DC converters," *IEEE Industry Applications Magazine*, vol. 5, no. 6, pp. 27– 33, 1999.

- [21] E. Rondon, F. Morel, C. Vollaire, M. Ferber, and J. Schanen, "Conducted EMC prediction for a power converter with SiC components," in 2012 Asia-Pacific Symposium on Electromagnetic Compatibility, 2012, pp. 281–284.

- [22] M. Kheraluwala, R. W. Gascoigne, D. M. Divan, and E. D. Baumann, "Performance characterization of a high-power dual active bridge DC-to-DC converter," *IEEE Transactions on industry applications*, vol. 28, no. 6, pp. 1294–1301, 1992.

- [23] Y. Bai, X. Yang, X. Li, D. Zhang, and W. Chen, "A novel balanced winding topology to mitigate EMI without the need for a Y-capacitor," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), IEEE, 2016, pp. 3623–3628.

- [24] P. Kong and F. C. Lee, "Transformer structure and its effects on common mode EMI noise in isolated power converters," in 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), IEEE, 2010, pp. 1424–1429.

- [25] E. Rondon-Pinilla, F. Morel, C. Vollaire, and J. Schanen, "Modeling of a Buck Converter With a SiC JFET to Predict EMC Conducted Emissions," 5, vol. 29, 2014, pp. 2246–2260.

- [26] T. Lagier, L. Chédot, F. W. L. Ghossein, B. Lefebvre, P. Dworakowski, et al., "A 100 kW 1.2 kV 20 kHz DC-DC converter prototype based on the Dual Active Bridge topology," in 2018 IEEE International Conference on Industrial Technology (ICIT), IEEE, 2018, pp. 559–564.

- [27] T. Lagier and P. Ladoux, "Theoretical and experimental analysis of the soft switching process for SiC MOSFETs based Dual Active Bridge converters," in 2018 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), IEEE, 2018, pp. 262–267.

- [28] P. Dworakowski, A. Wilk, M. Michna, B. Lefebvre, and T. Lagier, "3-phase medium frequency transformer for a 100kW 1.2 kV 20kHz Dual Active Bridge converter," in IECON 2019-45th Annual Conference of the IEEE Industrial Electronics Society, IEEE, vol. 1, 2019, pp. 4071–4076.

- [29] G. Lan, S. Zhang, and X. Wu, "Analysis and reduction of common mode current of the transformer in a full-bridge LLC battery charger," in 2017 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), IEEE, 2017, pp. 1–5.

- [30] H. Geramirad, B. Lefebvre, F. Morel, A. Bréard, and C. Vollaire, "Etude experimentale de la CEM des drivers d'un demi-pont avec MOSFET SIC et IGBT (in press), 20ème Colloque International et Exposition sur la Compatibilité Electromagnétique (CEM 2020)," 2020.