# CSME: A novel cycle-sensing margin enhancement scheme for high yield STT-MRAM

H. Cai, M. Liu, Y. Zhou, B. Liu, Lirida Naviner

#### ▶ To cite this version:

H. Cai, M. Liu, Y. Zhou, B. Liu, Lirida Naviner. CSME: A novel cycle-sensing margin enhancement scheme for high yield STT-MRAM. Microelectronics Reliability, 2020, pp.113732. 10.1016/j.microrel.2020.113732. hal-02941338

### HAL Id: hal-02941338 https://hal.science/hal-02941338v1

Submitted on 21 Nov 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## CSME: A Novel Cycle-Sensing Margin Enhancement Scheme for High Yield STT-MRAM

H. Cai<sup>a,b,\*</sup>, M. Liu<sup>a</sup>, Y.Zhou<sup>a</sup>, B. Liu<sup>a</sup>, L.A.B. Naviner<sup>b</sup>

<sup>a</sup> National ASIC System Engineering Center, Southeast University, Nanjing, 210096

<sup>b</sup> Télécom Paris, 19 place Marguerite Perey Palaiseau, France, 91120

Abstract – Spin-transfer torque (STT)-magnetic random access memory (MRAM) requires yield-aware design for hybrid magnetic-CMOS integration. In this paper, a novel cycle-sensing margin enhancement (CSME) scheme with pMOS assisted voltage-type sense amplifier (p-VSA) is proposed to alleviate imperfect process induced performance fluctuations. With iterated charging-discharging through non-volatile data path and reference path, read margin can be significantly improved thanks to the enlarged sensing window. Simulation is performed using MTJ compact model and an industrial 28-nm CMOS process. Results show that with 0.6V supply voltage ~14.1% read yield improvement can be realized at 50% tunnel magnetoresistance (TMR) ratio comparing to conventional VSA.

#### 1. Introduction

Spin-transfer torque (STT)-MRAM demonstrates excellent endurance, retention, fast access speed, and low power switching characteristics [1-3]. It has been used in last-level cache [4-5], embedded systems [6-8], microcontroller unit (MCU) [9] and so on. Non-volatile magnetic RAM (MRAM) design shows high yield requirement due to sub-28-nm CMOS process and sub-100-nm magnetic tunnel junction (MTJ) device applied to hybrid integration [10].

For read operation, STT-MRAM suffers from several read reliability problems caused by physical parameter fluctuations in MTJ and CMOS devices, especially at low supply voltage ( $V_{dd}$ ) and high temperature scenario. Previous works mainly focused on robust sense amplifier (SA) [11-15] design in order to alleviate variability induced failure.

High- $V_{dd}$  strategy is the most direct and effective method to achieve yield enhancement. Related to MRAM read operation, using above nominal voltage for reading leads to extra power dissipation, the incremental sensing current generates reliability concerns such as read disturbance. Additionally, variability-aware transistor sizing strategy in SA could accordingly suppress the influence of imperfect process. However, increasing the size of SA is also an inappropriate solution in nanoscale technology node because of the serious random dopant fluctuation (RDF) [16-17]. Another solution is to cancel the SA offset voltage ( $V_{OS}$ ). But many offset cancellation schemes could not effectively cancel  $V_{OS}$  and require sensing latency overhead [11].

For energy efficient and fast MRAM read operations, the 2T-2M (two access transistors and two MTJs) bit-cell structure [18-19] is a proper choice. Its differential bit-lines (BL and BLB) enable an enlarged sensing margin. However, 2T-2M STT-MRAM read operations still face the read reliability challenges.

In this paper, we proposed a novel <u>Cycle-Sensing Margin Enhancement</u> scheme named CSME to provide an extended sensing margin window, as well as higher input bit-line voltage difference  $(V_{in})$ . The main contributions of this work include:

- Read reliability challenges of STT-MRAM have been surveyed. Previous VSAs in MRAM have been reviewed, including sensing margin/window and bit-line voltage ( $V_{BL}$ ) swing.

- The CSME scheme using pMOS assisted voltage-type sense amplifier (p-VSA) with dual-transistor sensing is

proposed to overcome imperfect MTJ/CMOS hybrid process induced performance fluctuations.

• The enhanced sensing margin and  $V_{BL}$  driving ability benefit read yield improvement, ~14.1% at  $V_{dd}$ =0.6V and TMR=50% with CSME scheme.

The rest of this paper is organized as follows: Section 2 reviews reliability challenges during read operation in STT-MRAM. Section 3 presents the proposed CSME scheme with circuit-level implementation. In section 4, we simulate the proposed scheme and circuits using 28-nm CMOS and MTJ behavioral model. Results are compared with previous VSA. Section 5 concludes this paper.

#### 2. Preliminaries

#### 2.1. STT-MRAM read reliability challenges

Table I lists main reliability concerns during read and write operations of STT-MRAM [20-22]. According to their key causes, the write reliability type can be divided into three categories: transition faults, coupling faults and write polarization asymmetry. The read reliability challenge includes decision fault, read disturb, incorrect read fault and retention failures.

Table I - Writing/reading failure mechanisms and key causes

| Affect | Mechanisms                   | Key cause                                                                                          |

|--------|------------------------------|----------------------------------------------------------------------------------------------------|

| Read   | Decision<br>Fault            | *Process variations *Limited TMR *Low supply voltage                                               |

|        | Read<br>Disturb              | *Read and write share the same path *Growing with technology scaling                               |

|        | Incorrect<br>Read Fault      | *Opposite Temp. dependence resistance<br>*Parasitic effects<br>*Short sensing margin window of VSA |

|        | Retention<br>failures        | * Intrinsic thermal instability * Thermal noise                                                    |

| Write  | Transition faults            | *Stochastic nature of write operation<br>*Thermal Fluctuations                                     |

|        | Coupling faults              | *Neighboring cells switching                                                                       |

|        | Write polarization asymmetry | *P to AP needs higher switching current *The writing time required varies                          |

In this work, we concentrate on read operation. Table II shows the main physical parameters affecting the read reliability of MRAM [20]. Among them, the finite TMR is a key macroscopic parameter which determines the margin during sensing. The limited TMR generates similar parallel resistance ( $R_P$ ) and antiparallel resistance ( $R_{AP}$ ) value, which causes an overlapped  $R_P/R_{AP}$  distribution in their tail regions. Even if MRAM sensing block is implemented with an ideal reference cells, SA cannot distinguish high and low states of MTJ.

Table II – Key parameters affecting the reliability of STT-MRAM

| MTJ parameters                             | Transistor parameters                                |  |

|--------------------------------------------|------------------------------------------------------|--|

| The magnetic anisotropy (H <sub>K</sub> )  | Threshold voltage of the                             |  |

| Saturation magnetization (M <sub>S</sub> ) | access transistor (V <sub>T</sub> )                  |  |

| Tunnel Magneto-resistance Ratio            | Length and width variations of the access transistor |  |

| (TMR)                                      |                                                      |  |

| Oxide thickness of MgO layer (tox)         |                                                      |  |

| Planar dimensions of the MTJ               |                                                      |  |

#### 2.1.1. Read disturb

MRAM  $V_{dd}$  scaling is the most efficient method to reduce power consumption [23]. Both writing and reading  $V_{dd}$  can be reduced below 1V. Near threshold (near- $V_T$ ) configuration can be used for energy efficient sensing.

Writing operation in STT-MRAM is executed with the bipolar switching current. Notice that read and write operations share the same current flow path. Therefore, path overlap becomes an important concern. Along with bit-cell dimension shrinking and switching energy reduction, MRAM write current is continuously decreasing to get close to current range during read. Therefore, the sensing current has probability to switch the resistance state. This issue becomes an obvious trend with technology scaling of MTJ because of the reduced thermal stability factor and critical write current [24-25].

#### 2.1.2. Incorrect read fault

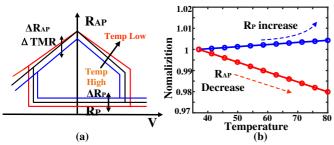

Fig. 1. (a) MTJ resistance versus bias voltage under different temperature, (b) temperature dependence of resistance of parallel and anti-parallel state, normalization at room temperature

As illustrated in Fig. 1, temperature fluctuations show significant impact on resistance of MTJ, whereas  $R_P$  and  $R_{AP}$  have the opposite trend of temperature dependence [24]. When the temperature increases,  $R_P$  gradually increases and  $R_{AP}$  gradually decreases, which leads to a reduced TMR and limited read margin. The antiparallel state is sensitive to the bias voltage of MTJ as shown in Fig. 1(a). That is, the TMR decreases with the increase of the bias on MTJ until its state switched, which inevitably leads to loss of sensing margin.

Several previous works announced that embedded MRAM

places MTJ in the lower metal layers for better routing ability at chip level [25]. Compared with high-level metals, the low-level solution shows serious parasitic effects. Besides, the lower layer should be optimized for a tight routing pitch and compatibility with logic platform due to its thin-layer characteristic. Parasitic resistance and capacitance of different bit-line (BL), source-line (SL) and their variations degrade the read margin.

#### 2.1.3. Retention failures

MRAM is with intrinsic thermal instability, which results to bit-flip of cell resistance state, denoted as retention failure [22]. If the data stored in MRAM bit-cell suffers data corruption before read operation, it is impossible to read the correct data during a successive read process. This issue is limited by the technological level of MRAM, and can be improved for the exploration of thermal stability facture at MTJ device level.

#### 2.2 Conventional VSA

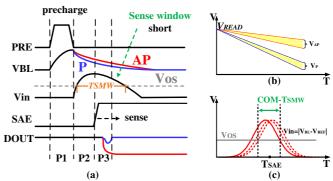

Fig. 2(a) shows the working waveforms of conventional latch-type VSA in STT-MRAM [15], whose circuit is shown in Fig. 3(c). A read cycle starts with a precharge phase, BL and reference line (BLB) firstly precharge to read voltage. In the next phase, the word-line (WL) is on and BL begins to discharge, the resistance state of MTJ determines the discharge current. Finally, the latch-type VSA compares the  $V_{\rm BL}$  with reference voltage ( $V_{\rm BLB}$ ) and outputs a digital result.

SAs have input offset caused by transistors mismatch [28]. The mismatch comes from transistors parameter variations (seen Table II). As  $V_{BL}$  and  $V_{BLB}$  both drop from read voltage to 0 quickly, the sensing margin window is short, as shown in Fig. 2(a). Theoretically, the maximum read yield acquired when sensing at the highest point of  $V_{in}$ .  $V_{in}$  is denoted as  $|V_{BL}|$  MTJ process variations cause the maximum  $V_{in}$  occurs at different times for different cells as shown in Fig. 2(b) and 2(c). Replica bit-line technique is a proper timing scheme for suppressing timing variation and tracking MRAM process fluctuations [29]. Additionally,  $V_{BL}$  and  $V_{BLB}$  drop to a low level at sensing time, which produces a weak driving ability for NMOS sampling transistors.

Fig. 2. (a) Waveforms of conventional VSA for STT-MRAM, (b) variations in V<sub>BL</sub> and V<sub>BLB</sub> swing during read operations, (c) Sensing margin window is limited by BL voltage variations

Therefore, a larger  $V_{in}$  is required to provide tolerance against above challenges. In this work, CSME scheme by charging and discharging bit-line along time has been proposed to improve read reliability at limited TMR and low supply

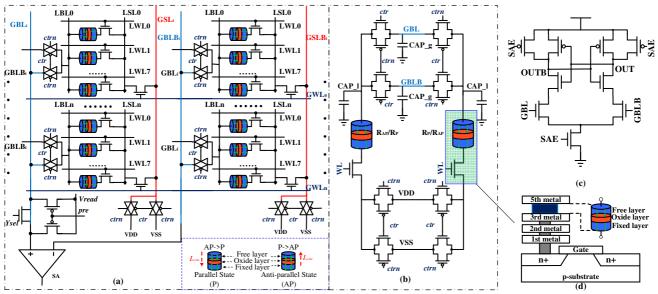

Fig. 3. (a) MRAM array (256 × 256) with the proposed CSME structure, (b) The schematic of CSME voltage difference optimization circuit, (c) The schematic of latch-type VSA, (d) The cross section view of 1T-1M bit-cell and MTJ device.

voltage.

#### 3. Proposed read reliability enhancement scheme

#### 3.1. CSME circuit implementation

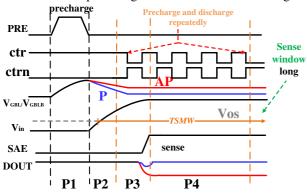

The proposed cycle-sensing margin enhancement circuit with hierarchical bit-line technique is shown in Fig. 3(a). A hierarchical bit-line technique is necessary to ameliorate read disturbance [5] and reduce the height of memory bank [30]. 8 local columns are connected to global bit-line (GBL/GBLB) to reduce parasitic resistance of read paths for read margin enhancement. This scheme can also reduce write power consumption because the local bit-line (LBL) capacitance is reduced, the charging time is short, and thus the cell current can be suppressed. Fig. 3 (b) shows the CSME input voltage difference optimization conception diagram. Two transmission gates are used to isolate global and local bit-lines. In read operation, LBL can be alternately connected to GBL and GBLB. Another two transmission gates are used to control the charge and discharge operation of capacitance in global bitlines. Fig. 3 (d) shows the cross section view of a 1T-1M (half of 2T-2M) MRAM bit-cell. Fig. 4 shows the detailed CSME timing sequence. ctr signal (ctrn is reversed ctr) is the switch of transmission gates. It is enabled only when current sub-array is selected. In the first phase (pre-charge), the capacitances of global bit-lines are pre-charged to the level of read voltage.

Fig. 4. The working waveforms of proposed CSME.

In the second phase (BL develop), the capacitance of GBL and GBLB begin to discharge and form an input voltage difference. The discharge current is depended on the resistance of accessed cell. When the resistance state of the accessed cell is  $R_{AP}$ , the cell read current is smaller than reference cell. Thus, the discharge speed of GBLB capacitance is faster than GBL, causing GBL voltage  $(V_{GBL})$  larger than reference voltage  $(V_{GBLB})$ . Latency of this phase is similar with conventional VSA in order to acquire maximum value of  $\left|V_{GBL}-V_{GBLB}\right|$ .

In the third phase (sensing margin enhancement), the ctr signal changes to cycle pulse, and the charge/discharge operation of bit-cell alternately appears to further improve sensing margin. When ctr=1 (ctrn=0), the GBL capacitance discharges through the cell path and GBLB capacitance discharges through the reference path. Assume that the data stored in accessed cell is '1', so that the cell resistance is larger than reference resistance. The discharge current of data path is smaller than reference current, consequently causing the  $V_{GBL}$  larger than  $V_{GBLB}$ . When ctr=0 (ctrn=1), GBLB capacitance is connected to accessed cell and GBL capacitance attaches to reference cell. The charge current of data path is smaller than reference path. Therefore, the charging speed of the GBL capacitance is faster than the charging speed of the GBLB capacitance, and also causing  $V_{GBL}$  larger than  $V_{GBLB}$ .

It is obvious that both charge and discharge processes enlarge  $V_{\rm in}$ . After several cycles, the global capacitances charge and discharge capacity reach equilibrium.  $V_{\rm GBL}/V_{\rm GBLB}$  tends to be stable and the input voltage difference remains unchanged. In the final phase, the SA enable signal (SAE) is activated. VSA senses the voltage difference and generates a digital output.

The main difference between the proposed CSME and conventional VSA is the application of cycle pulse. The alternating occurrence of the charging and discharging process stabilizes and improves the input sensing margin.

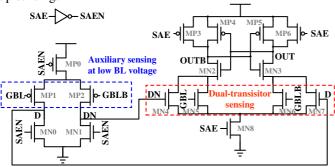

#### 3.2. p-VSA circuit implementation

In addition to the short duration of the sensing margin window, STT-MRAM suffers insufficient driving ability of the bit-line voltage to the NMOS sampling transistor (MN5/MN6

in Fig. 5), which is caused by low read voltage and the fast discharge speed. In order to overcome this issue, p-VSA with dual transistors enhanced sensing is proposed as shown in Fig. 5.

The p-VSA circuit is composed of two parts, the voltage difference conversion circuit and dual-transistors enhanced sensing circuit. A voltage difference conversion circuit is added on the basis of conventional VSA to auxoliary sense at low V<sub>BL</sub>. This circuit can convert lower bit-line voltage to higher input voltage. When the input bit-line voltage is high enough to drive NMOS transitors, MN5 and MN6 complete sensing operation. When the V<sub>GBL</sub>/V<sub>GBLB</sub> is low, which cannot activate MN5 and MN6. But low input read voltage activates transistor MP1 and MP2, then the left circuit transforms the low input read voltage to high voltage, which increases the driving ability of NMOS transistor. SAE is the SA enable signal and SAEN is reverse SAE. Firstly, SAE is set to low, SAEN is high, D/DN will be discharged to GND and OUT/OUTB is precharged to V<sub>dd</sub>. When V<sub>GBL</sub> is higher than V<sub>GBLB</sub>, the charging current flows through MP2 is larger than MP1. Thus, the voltage of DN becomes larger than D. Dual-NMOS sensing scheme works well despite the existence of bitline voltage discrepancy of different cells during read operation. Dual-transistors sensing increases sense sensitivity and speeds up sensing.

Fig. 5. The proposed p-VSA circuit with pMOS transistor auxiliary sensing at low BL voltage

#### 4. Simulation Results

Table III. Physical parameters of STT-MTJ compact model used in this work [31].

| Parameters                      | Description                   | Default Value |  |

|---------------------------------|-------------------------------|---------------|--|

| α                               | Gilbert Damping Coefficient   | 0.027         |  |

| g                               | GyroMagnetic Constant         | 1.76e7        |  |

| Ms                              | Saturation Field              | 15800         |  |

| t <sub>ox</sub>                 | Oxide thickness               | 0.85nm        |  |

| $t_{sl}$                        | MTJ free layer thickness      | 1.3nm         |  |

| RA                              | Resistance area product       | 5             |  |

| TMR                             | Tunnel magnetoresistance      | 10%-100%      |  |

|                                 | ratio                         |               |  |

| R <sub>P</sub> /R <sub>AP</sub> | Parallel and anti-parallel    | 5 kΩ/10 kΩ    |  |

|                                 | resistance                    | (Initial)     |  |

| Area                            | MTJ layout surface            | 40nm×40nm     |  |

| $V_{BL}$                        | Bit-line voltage (traditional | 150 mV/300 mV |  |

|                                 | sensing/this work)            |               |  |

The proposed CSME scheme was evaluated with an MTJ Verilog-A compact model and a commercial 28-nm CMOS process. Minimum transistor dimension (W/L = 80nm/30nm) is used to realize p-VSA circuit (see Fig. 5). A 256×256 MRAM cell array is simulated for sensing operation. Table III shows

the parameters of the used MTJ compact model.

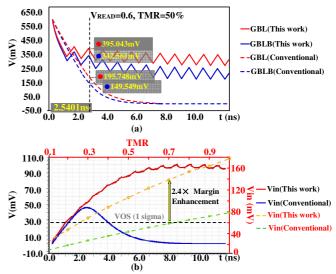

Fig. 6(a) illustrates the input bit-line voltage and voltage difference during transient read operation of conventional VSA and this work. As conventional and our proposed scheme perform identical discharge, initially their voltage differences show same trend. As shown in Fig. 6(a), the sensing margin window lasts about 2.5ns in conventional scheme. Whereas in the proposed CSME scheme, the input voltage difference is continuously enlarged until it stabilizes at a relatively high value, e.g., 95mV when  $V_{read} = 0.6V$  and TMR=50%. 1,000 runs Monte Carlo simulation are performed considering TMR fluctuations. Results show that CSME achieves ~2.4× larger margin than previous work (see Fig. 6(b)).

Fig. 6. Simulation results of (a) bit-line voltage and (b) $V_{in}$  of conventional VSA scheme and this work

As the capacitance in GBL/GBLB is supplementary charged,  $V_{BL}$  in CSME scheme is about 200mV higher than previous VSAs. Thus, the ability of NMOS sensing transistor (MN5 & MN6) is enhanced.

Fig. 7. 1000 times Monte Carlo Simulation results for read error rate estimation, with conventional VSA, p-VSA only and this work at (a) TMR fluctuation, (b) wide range supply voltage.

Our proposed scheme shows a significant read reliability

improvement. Fig. 7 (a) shows the simulation results of read error rate at TMR from 10% to 100%, the supply voltage and read voltage is set to 0.6 V. Comparing to conventional VSA, this work gets max 29.1% read error rate reduction. The read with p-VSA only also obtains max 15.9% read error rate reduction. The read yield improvement of CSME benefits from the high sensing margin and extended sensing margin window. These advantages make it robust for the intrinsic offset voltage of SA latch. Moreover, the increased sense sensitivity of dual transistors also contributes to the yield improvement.

Fig. 7 (b) shows the simulation results with wide range  $V_{\rm dd}$ , this work obtains effective read yield improvement especially when  $V_{\rm dd}$  is less than 0.7 V. The CSME scheme strengths read reliability at wide operation range. The p-VSA only method is well-behaved at low voltage.

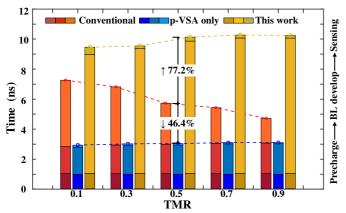

Fig. 8. Simulation results of latency for conventional VSA, p-VSA and this work at different TMR

Table IV – Performance comparison of the VSAs in 28nm CMOS with the same transistor size (V<sub>dd</sub>=0.6V, TMR=50%)

|                    | Conventional VSA | p-VSA<br>only | This<br>work | CRE-<br>VSA[15] |

|--------------------|------------------|---------------|--------------|-----------------|

| Power (µW)         | 9.51             | 17.58         | 20.77        | 9.03            |

| Latency (ns)       | 5.68             | 3.04          | 10.06        | 3.71            |

| Normalized latency | 1                | 0.54          | 1.77         | 0.65            |

| Energy(fJ)         | 54               | 53.53         | 208.94       | 33.5            |

| Normalized energy  | 1                | 0.99          | 3.85         | 0.62            |

| Yield              | 0.879            | 0.99          | 0.995        | 0.958           |

| Normalized yield   | 1                | 1.126         | 1.132        | 1.09            |

The improved yield of the proposed scheme comes at the expense of power consumption and latency. Fig. 8 demonstrates the simulation results of latency for conventional VSA, working with p-VSA only and this work at different TMR. The three methods have similar precharge time. Working with CSME has a longer BL develop time because it needs more time to stabilize  $V_{\rm in}$ , which is 4 times longer than conventional VSA and p-VSA only. However, CSME has a short latch time, which benefits from the increased read margin, extended sensing margin window, high input bit-line voltage and the dual-transistors enhancement sensing. Overall, working with p-VSA only has the fastest access speed and CSME has the longest latency.

Table IV shows the performance comparison of the VSAs during the transient simulations. CRE-VSA is added for comparison. Simulation results indicate that CRE-VSA can only work well when the variations of CRE circuit is small enough. CRE-VSA achieves a fast access time and a reduced read power. The proposed CSME has the best read yield improvement among them.

#### 5. Conclusion

A novel CSME scheme with p-VSA implementation was proposed to improve the read reliability of MRAM at low voltage and limited TMR scenario. The proposed scheme can demonstrate high-tolerance to MTJ/CMOS variations. Comparing to conventional VSA, an extended sensing margin window and higher SA input voltage were realized. The proposed scheme was evaluated with 28-nm CMOS and 40-nm MTJ compact model. Simulation results indicated a minimum  $2.4\times$  margin improvement and 14.1% read error rate reduction, which successfully benefits low TMR rate (50%) and low  $V_{dd}$  (0.6V) MRAM sensing scenario.

#### Acknowledgment

This work is supported in part by National Key R&D Program of China under Grant 2018YFB2202800 and National Natural Science Foundation of China under Grant 61904028.

#### References

- [1] H. Yu et al., Cycling endurance optimization scheme for 1Mb STT-MRAM in 40nm technology, ISSCC Digest of Technical Papers, 2013, pp. 224-225, https://doi.org/10.1109/ISSCC.2013.6487710

- [2] K. Tsuchida et al., A 64Mb MRAM with clamped-reference and adequate-reference schemes, 2010 IEEE International Solid-State Circuits Conference - (ISSCC), 2010, pp. 258-259, https://doi.org/10.1109/ISSCC.2010.5433948

- [3] Y. K. Lee et al., Embedded STT-MRAM in 28-nm FDSOI Logic Process for Industrial MCU/IoT Application, 2018 IEEE Symposium on VLSI Technology, 2018, pp. 181-182, https://doi.org/10.1109/VLSIT.2018.8510623

- [4] H. Noguchi et al., 7.2 4Mb STT-MRAM-based cache with memory-access-aware power optimization and write-verify-write / read-modify-write scheme, ISSCC, 2016, pp. 132-133, https://doi.org/10.1109/ISSCC.2016.7417942

- [5] H. Noguchi et al., 7.5 A 3.3ns-access-time 71.2μW/MHz 1Mb embedded STT-MRAM using physically eliminated read-disturb scheme and normally-off memory architecture, 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, 2015, pp. 1-3, https://doi.org/10.1109/ISSCC.2015.7062963

- [6] K. Lee et al., 1Gbit High Density Embedded STT-MRAM in 28nm FDSOI Technology, 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 2.2.1-2.2.4, https://doi.org/10.1109/IEDM19573.2019.8993551

- [7] Y. Shih et al., Logic Process Compatible 40-nm 16-Mb, Embedded Perpendicular-MRAM With Hybrid-Resistance Reference, SubuA Sensing Resolution, and 17.5-nS Read Access Time, in IEEE Journal of Solid-State Circuits, vol. 54, no. 4, pp. 1029-1038, April 2019, https://doi.org/10.1109/JSSC.2018.2889106

- [8] M.Shih et al., Reliability study of perpendicular STT-MRAM as emerging embedded memory qualified for reflow soldering at 260°C, 2016 IEEE Symposium on VLSI Technology, 2016, pp. 1-2, https://doi.org/10.1109/VLSIT.2016.7573411

- [9] M. Natsui et al., A 47.14- uW 200-MHz MOS/MTJ-Hybrid Nonvolatile Microcontroller Unit Embedding STT-MRAM and

- FPGA for IoT Applications, in IEEE Journal of Solid-State Circuits, vol. 54, no. 11, pp. 2991-3004, Nov. 2019, https://doi.org/10.1109/JSSC.2019.2930910

- [10] K. C. Chun et al., A Scaling Roadmap and Performance Evaluation of In-Plane and Perpendicular MTJ Based STT-MRAMs for High-Density Cache Memory, in IEEE Journal of Solid-State Circuits, vol. 48, no. 2, pp. 598-610, Feb. 2013, https://doi.org/10.1109/JSSC.2012.2224256

- [11] B. Song, T. Na, J. Kim, J. P. Kim, S. H. Kang and S. Jung, Latch Offset Cancellation Sense Amplifier for Deep Submicrometer STT-RAM, in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 7, pp. 1776-1784, July 2015, https://doi.org/10.1109/TCSI.2015.2427931

- [12] Q. Dong et al., A 1-Mb 28-nm 1T1MTJ STT-MRAM With Single-Cap Offset-Cancelled Sense Amplifier and In Situ Self-Write-Termination, in IEEE Journal of Solid-State Circuits, vol. 54, no. 1, pp. 231-239, Jan. 2019, https://doi.org/10.1109/JSSC.2018.2872584

- [13] L. Wei et al., 13.3 A 7Mb STT-MRAM in 22FFL FinFET Technology with 4ns Read Sensing Time at 0.9V Using Write-Verify-Write Scheme and Offset-Cancellation Sensing Technique, 2019 IEEE International Solid- State Circuits Conference -(ISSCC), 2019, pp. 214-216, https://doi.org/10.1109/ISSCC.2019.8662444

- [14] T. Yang, K. Li, Y. Chiang, W. Lin, H. Lin and M. Chang, A 28nm 32Kb embedded 2T2MTJ STT-MRAM macro with 1.3ns read-access time for fast and reliable read applications," 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 482-484, https://doi.org/10.1109/ISSCC.2018.8310394

- [15] Y. Zhou et al., A Self-Timed Voltage-Mode Sensing Scheme With Successive Sensing and Checking for STT-MRAM, in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 67, no. 5, pp. 1602-1614, May 2020, https://doi.org/10.1109/TCSI.2019.2960028

- [16] H. Mahmoodi, S. Mukhopadhyay and K. Roy, Estimation of delay variations due to random-dopant fluctuations in nanoscale CMOS circuits, in IEEE Journal of Solid-State Circuits, vol. 40, no. 9, pp. 1787-1796, Sept. 2005, https://doi.org/10.1109/JSSC.2005.852164

- [17] A. J. Bhavnagarwala, Xinghai Tang and J. D. Meindl, The impact of intrinsic device fluctuations on CMOS SRAM cell stability, in IEEE Journal of Solid-State Circuits, vol. 36, no. 4, pp. 658-665, April 2001, https://doi.org/10.1109/4.913744

- [18] H. Noguchi, K. Ikegami, N. Shimomura, T. Tetsufumi, J. Ito and S. Fujita, Highly reliable and low-power nonvolatile cache memory with advanced perpendicular STT-MRAM for highperformance CPU," 2014 Symposium on VLSI Circuits Digest of Technical Papers, 2014, pp. 1-2, https://doi.org/10.1109/VLSIC.2014.6858403

- [19] H. Noguchi et al., A 250-MHz 256b-I/O 1-Mb STT-MRAM with advanced perpendicular MTJ based dual cell for nonvolatile magnetic caches to reduce active power of processors, 2013 Symposium on VLSI Circuits, 2013, pp. C108-C109.

- [20] A. Chintaluri, H. Naeimi, S. Natarajan and A. Raychowdhury, Analysis of Defects and Variations in Embedded Spin Transfer Torque (STT) MRAM Arrays, in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 6, no. 3, pp. 319-329, Sept. 2016, https://doi.org/10.1109/JETCAS.2016.2547779

- [21]E. Eken, Y. Zhang, W. Wen, R. Joshi, H. Li and Y. Chen, "A Novel Self-Reference Technique for STT-RAM Read and Write Reliability Enhancement," in IEEE Transactions on Magnetics, vol. 50, no. 11, pp. 1-4, Nov. 2014, Art no. 3401404, https://doi.org/10.1109/TMAG.2014.2323196

- [22] Soheil Salehi et al., Survey of STT-MRAM Cell Design Strategies: Taxonomy and Sense Amplifier Tradeoffs for Resiliency, ACM Journal on Emerging Technologies in Computing Systems, Vol. 13, No. 3, Article 48, Publication date: April 2017. http://dx.doi.org/10.1145/2997650

- [23] M. Alioto, E. Consoli, and G. Palumbo, General strategies to design nanometer flip-flops in the energy-delay space, IEEE Trans.

- Circuits Syst. I, Reg. Papers, vol. 57, no. 7, pp. 1583–1596, Jul. 2010. https://doi.org/10.1109/TCSI.2009.2033538

- [24] T. Na, J. Kim, J. P. Kim, S. H. Kang and S. Jung, Reference-Scheme Study and Novel Reference Scheme for Deep Submicrometer STT-RAM, in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 12, pp. 3376-3385, Dec. 2014, https://doi.org/10.1109/TCSI.2014.2327337

- [25] E. Eken, Y. Zhang, W. Wen, R. Joshi, H. Li and Y. Chen, A Novel Self-Reference Technique for STT-RAM Read and Write Reliability Enhancement, in IEEE Transactions on Magnetics, vol. 50, no. 11, pp. 1-4, Nov. 2014, Art no. 3401404, https://doi.org/10.1109/TMAG.2014.2323196

- [26] R. Takemura et al., A 32-Mb SPRAM With 2T1R Memory Cell, Localized Bi-Directional Write Driver and `1'/`0' Dual-Array Equalized Reference Scheme, in IEEE Journal of Solid-State Circuits, vol. 45, no. 4, pp. 869-879, April 2010, https://doi.org/10.1109/JSSC.2010.2040120

- [27] O. Golonzka et al., MRAM as Embedded Non-Volatile Memory Solution for 22FFL FinFET Technology, 2018 IEEE International Electron Devices Meeting (IEDM), 2018, pp. 18.1.1-18.1.4, https://doi.org/10.1109/IEDM.2018.8614620

- [28] M. Chang et al., An Offset-Tolerant Fast-Random-Read Current-Sampling-Based Sense Amplifier for Small-Cell-Current Nonvolatile Memory, in IEEE Journal of Solid-State Circuits, vol. 48, no. 3, pp. 864-877, March 2013, https://doi.org/10.1109/JSSC.2012.2235013

- [29] Y. Zhou, H. Cai, B. Liu, W. Zhao and J. Yang, MTJ-LRB: Proposal of MTJ-based Loop Replica Bitline as MRAM Device-Circuit Interaction for PVT-Robust Sensing, in IEEE Transactions on Circuits and Systems II: Express Briefs, https://doi.org/10.1109/TCSII.2020.2980331

- [30] K. Rho et al., 23.5 A 4Gb LPDDR2 STT-MRAM with compact 9F2 1T1MTJ cell and hierarchical bitline architecture, 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2017, pp. 396-397, https://doi.org/10.1109/ISSCC.2017.7870428

- [31] You Wang et al., [Online]. http://www.spinlib.com/STT\_PMA\_MTJ.html