### Versatile Three-Level FC-NPC Converter With High Fault-Tolerance Capabilities: Switch Fault Detection and Isolation and Safe Postfault Operation

Afef Bennani-Ben Abdelghani, Hafedh Ben Abdelghani, Frédéric Richardeau, Jean-Marc Blaquière, Franck Mosser, Ilhem Slama-Belkhodja

### ▶ To cite this version:

Afef Bennani-Ben Abdelghani, Hafedh Ben Abdelghani, Frédéric Richardeau, Jean-Marc Blaquière, Franck Mosser, et al.. Versatile Three-Level FC-NPC Converter With High Fault-Tolerance Capabilities: Switch Fault Detection and Isolation and Safe Postfault Operation. IEEE Transactions on Industrial Electronics, 2017, 64 (8), pp.6453-6464. 10.1109/TIE.2017.2682009. hal-02920315

### HAL Id: hal-02920315 https://hal.science/hal-02920315v1

Submitted on 22 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Versatile three-level FC-NPC converter with high fault-tolerance capabilities: switch fault detection and isolation and safe post-fault operation

Afef Bennani Ben Abdelghani<sup>1,2,\*</sup>, Hafedh Ben Abdelghani<sup>1,3</sup>, Frédéric Richardeau<sup>3</sup>, Jean-Marc Blaquière<sup>3</sup>, Franck Mosser<sup>3</sup>, Ilhem Slama-Belkhodja<sup>1</sup>

<sup>1</sup>Université de Tunis El Manar, Ecole Nationale d'Ingénieurs de Tunis, LR11ES15 Laboratoire des Systèmes Electriques LSE, 1002, Tunis, Tunisia.

<sup>2</sup> Université de Carthage, Institut National des Sciences Appliquées et de Technologie, Centre Urbain Nord, BP 676; Tunis, Tunisia.

<sup>3</sup> University of Toulouse-LAPLACE-CNRS-INPT-UPS, ENSEEIHT, 2 rue Camichel, 31071 Toulouse Cedex 7, France.

*Abstract*—This paper deals with a hybrid fault-tolerant converter topology. It is performed through the connection of a classical three-phase three-level Neutral Point Clamped (3L-NPC) converter with a fourth three-level Flying Capacitor (3L-FC) leg. The 3L-FC leg actively balances the 3L-NPC neutral point voltage. For normal operation mode, this paper proposes a mathematical design of the filter needed to connect these two different topologies. Experimentally, and thanks to the already existing decoupling capacitors of the 3L-NPC converter, this filter requires the addition of only one low size inductance.

When one fault of the power switch of the 3L-NPC occurs, the paper proposes hardware reconfiguration technique based on only two fuses and one thyristor per leg allows a safe post-fault operation recovery. This is achieved thanks to a simple faultdetection method and a new technique that combines fault leg isolation and corresponding phase post-fault connection to the neutral point. Also, a dedicated FPGA-based control of the reconfigured converter is synthetized to ensure power system availability under fault operation mode.

The converter fault-tolerant capabilities are addressed through simulation results and original overall experimental validations of the fault detection and isolation and the post-fault operation steps, carried out on a 15 kW prototype converter.

*Index Terms*—Multilevel converter, Hybrid converter, Fault detection, Fault isolation, Fault tolerance.

#### I. INTRODUCTION

During the last decades, multilevel converters have been one of the more worthwhile challenges in power electronic fields. They have enabled power systems to meet increasingly stringent grid and load requirements [1]–[8]. Nowadays, many industrial applications, especially for medium- and high-voltage systems, use multilevel topologies, particularly the Neutral Point Clamped (NPC) one, thanks to its inherent advantages such as high DC-bus voltage, reduced output voltage harmonics, low voltage stress on power switches, and low dV/dt ratings [9]–[13].

Recently, the reliability of power converters has become an important issue. In fact, for many applications using standalone converters or on-board systems, fault tolerance is crucial. This is the case in the transportation field (electric vehicles, hybrid electric vehicles, rail, and aerospace), where the power system redundancy has a financial cost and volume limitations and may be technically inappropriate [14]–[16]. In addition, in present-day renewable energy applications, fault tolerance considerations are mandatory since maintenance can be difficult and expensive as in offshore wind farms. Moreover, a large-scale energy production shutdown may cause serious network stability problems and lead to a risk of blackout [17],[18].

Fault tolerance considerations have to be introduced from the converter design step in order to synthesize robust, secure, and fault-tolerant systems that provide operation availability after failure occurrence[19],[20]. Furthermore, the state of the art of power system reliability shows the predominance of the power converter and, in particular, power devices as the origin of the overall system failures [21]-[25]. Several model-based Fault Detection and Isolation (FDI) methods were proposed in literature for linear [26] and nonlinear systems [27]. These methods generally assume that, the control would be able to preserve operation at the nominal equilibrium point until the post-fault mode is reached. This issue is crucial for practical cases such as power converter applications. To overcome this issue, a safe-parking framework was proposed for nonlinear systems [28] and more recently for switched nonlinear ones [29]. Although the distinction between sensor and actuator faults for nonlinear systems was considered [30], the needed FDI time is the main concern of such techniques when applied for power converters, especially for short circuit switch faults. Moreover, a global power converter fault tolerance has to consider technological aspects when dealing with the electric isolation of the faulty power switch and the reconfiguration of the post-fault system issues.

This paper focuses on a hybrid fault-tolerant converter able to detect a power switch fault, isolate the corresponding faulty leg, and recover safe post-fault operation.

In [31]–[33], the authors proposed a fault-tolerant hybrid three-level converter based on the connection of a three-level Flying Capacitor (FC) leg to a three-phase three-level NPC (3L-NPC) converter. Transition from normal mode to faulty mode was ensured by fuses and an additional semi-conductor. This post-fault reconfiguration depends on the faulty NPC IGBT and the fault type (open-circuit or short-circuit). However, fault detection and the method of blowing up fuses were not discussed and the practical implementation issues were not detailed. In [34], the authors show the FC IGBT's dead time effect on the FC output voltage for this fault tolerant hybrid topology and claim to add an LC filter to overcome this issue.

In this paper, this fault-tolerant topology is sensitively improved. Four new features are proposed: First, a detailed mathematical design of the LC filter is performed. Second, a new and simple PWM control reconfiguration is developed. Third, a novel hardware reconfiguration technique based on fuses and one thyristor is experimentally tested. This new technique is based on an interesting NPC-intrinsic topology feature in order to adapt and simplify the set-up proposed by [33], where two different circuits are needed for a classical two-level converter reconfiguration. Finally, the whole of the fault-tolerance process, including fault detection, fault isolation, and post-fault hardware and control reconfiguration, is experimentally handled and validated.

The second section is dedicated to the hybrid feature of the proposed converter topology. The role of the FC leg is described and a detailed design methodology for the NPC-FC decoupling filter is presented. In the third section, the fault-tolerant FPGA-based PWM strategy is addressed. In the fourth section, a novel high-performance converter-reconfiguration technique is proposed. A comparison between two different fuse technologies is experimentally addressed. Then, the experimental results of post-fault operation mode are discussed. These results are obtained with an FPGA control board and a 15 kW laboratory test-bench. The fault-tolerant reconfiguration process improves the converter reliability and allows power system post-fault operation after the occurrence of an NPC switch fault.

## II. HYBRID NPC-FC CONVERTER: ISSUES AND PROPOSED SOLUTIONS

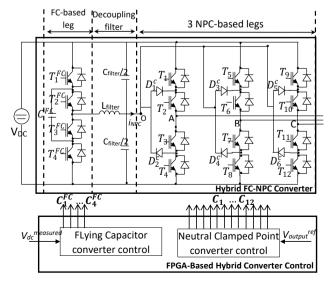

The considered power converter solution consists of a classical three-phase 3L-NPC topology with an added fourth FC leg connected at the neutral point "O", as shown in Fig.1. Note that the proposed topology is equivalent to the connection at the neutral point of two power converters: a three-level FC-based DC/DC converter and a three-level NPC DC/AC converter. Moreover, the hybrid converter is open loop controlled since the close loop control would not affect the hybrid feature of the converter or its fault tolerant capabilities.

Fig.1. Hybrid FC-NPC converter: topology and control

### A. Role of the FC Leg

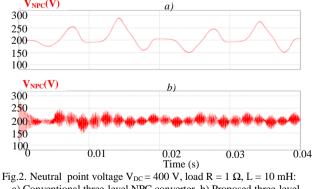

Under normal operation, the FC leg's main function is to provide the NPC converter with an active neutral point. In fact, a two-cell/three-level FC leg with a 50% ratio leads to an output voltage equal to half of the DC bus value, theoretically with a zero-voltage ripple at the output [35]. This voltage can constitute an efficient active neutral point for the NPC legs. Active neutral point regulation techniques proposed in the literature [36] are interesting because they offer a considerable volume reduction and electrolytic capacitors are replaced by lower size and more reliable and safer film capacitors. However, they involve dedicated control strategies and consequently limit the degrees of freedom of the NPC converter. Fig.2 shows a comparison of the neutral point voltage when the FC leg is controlled with the active balance strategy described above (Fig. 2.b) and the case of a conventional NPC converter with two 600-µF DC bus capacitors s (Fig. 2.a). It proves the effectiveness of the proposed active balance. Furthermore, unlike NPC converters, the proposed hybrid converter allows a very low frequency operation (as for machine start-up cases) and even a multilevel DC/DC chopper operation may be possible by interlacing the NPC legs.

#### B. Connecting the FC leg to the NPC ones

For a practical implementation and because of mandatory dead-times, the duty cycle of the FC leg will never be precisely equal to 50%, and a low-size high-frequency filter, denoted ( $L_{filter}$ ,  $C_{filter}$ ) must be included, as shown in Fig.1. Qualitatively, this filter has two main functions, which are developed below:

- From the NPC leg mid-point to the FC leg: Only the NPC mid-point low-frequency current at three times the modulation frequency has to flow between the two converter parts. Indeed, the high frequency components of this current affect the FC voltage balance especially in the case of identical (or an integer multiple/sub-multiple) switching frequencies of the NPC and FC legs.

- From the FC leg to the NPC leg mid-point: this secondorder filter acts on the residual pulse-width voltages of the FC output voltage that are caused by the IGBTs' dead-times.

The hybrid topology converter needs a precise sizing of the LC filter elements, which is developed in the next paragraph.

a) Conventional three-level NPC converter, b) Proposed three-level hybrid converter with active neutral point balance

### C. Sizing Methodology of the Proposed Filter

Three criteria families are fundamental for the LC filter sizing: spectral properties, state variables' ripples, and system behaviour after sudden load disconnection. i) Spectral constraints: The filter cut-off frequency,  $F_{\rm filter}$ , must be chosen to properly filter the residual pulse-width voltages at the FC leg output. The filter cut-off frequency maximum value, denoted  $F_{\rm filter\_max}$ , has to be equal to the minimum of the NPC leg's frequency, denoted  $F_{\rm sw\_PC}$ , and the FC leg's apparent frequency, denoted  $F_{\rm sw\_FC}$ . Besides, the minimum value of the filter cut-off frequency, denoted  $F_{\rm filter\_min}$ , is equal to one decade lower than  $F_{\rm filter\_max}$ , as expressed by Eqs. (1) and (2).

$$F_{filter\_min} = \frac{1}{2.\pi.\sqrt{\left(L_{filter}.C_{filter}\right)_{max}}}$$

$$F_{filter\_min} = \frac{Min(F_{SW\_NPC},F_{SW\_FC})}{10}$$

(1)

$$F_{filter\_max} = \frac{1}{2.\pi.\sqrt{\left(L_{filter}.C_{filter}\right)_{min}}}$$

$$F_{filter\_max} = Min(F_{SW\_NPC},F_{SW\_FC})$$

(2)

ii) NPC neutral point voltage and FC output current ripples. First, the neutral point voltage ripple, denoted  $\delta V_{NPC}$ , is generated by the I<sub>NPC</sub> current (see Fig. 1) and particularly its high frequency components (@ F<sub>sw\_NPC</sub>) when it flows through C<sub>filter</sub>. Second, the dead-times of the FC leg lead to glitches in its output voltage. These glitches excite the inductance and cause L<sub>filter</sub> current ripple, which corresponds to the FC output current ripple, denoted  $\delta I_{FC}$ .

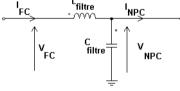

The NPC mid-point voltage ripple and the FC output current ripple must be set to admissible values through a smart choice of  $C_{filter}$  and  $L_{filter}$  values. To perform a precise calculation of  $\delta V_{NPC}$  and  $\delta I_{FC}$ , an analysis of the filter operation is detailed below. In fact, Fig.3 gives a simplified scheme of the principle of the filter.

Fig.3. Simplified scheme of the LC filter

The high-frequency component of  $V_{NPC}$ , denoted $(V_{NPC})_{HF}$ , can be expressed by:

$$(V_{NPC})_{HF} = (I_{NPC})_{HF} \cdot Z_{C_{filter}}$$

(3)

where:

$(I_{NPC})_{HF}$  is the high frequency component at  $F_{sw\_NPC}$  of current  $I_{NPC},$

and  $Z_{C_{filtre}}$  is the  $C_{filter}$  impedance, expressed by:

$$Z_{C_{filter}} = \frac{1}{2.\pi.F_{sw_NPC}.C_{filter}}$$

(4)

Consequently,

$$(V_{NPC})_{HF}$$

can be expressed by:

$$(V_{NPC})_{HF} = \frac{(T_{NPC})_{HF}}{2.\pi.F_{sw_NPC}.C_{filter}}$$

(5)

and the maximum admissible ripple of  $V_{NPC}$  is then:

$$\delta V_{NPC\_max} = \frac{(I_{NPC})_{HF}}{2.\pi.F_{sw\_NPC}.C_{filter\_min}}$$

(6)

where  $C_{filter\_min}$  is the  $C_{filter}$  minimum value corresponding to the maximum ripple of  $V_{NPC}$ . The expression for  $C_{filter\_min}$  is then given by (7):

$$C_{filter\_min} = \frac{(I_{NPC})_{HF}}{2.\pi.F_{sw\_NPC}.\delta V_{NPC\_max}}$$

(7)

The FC output current ripple depends on the voltage across  $L_{filter}$ , denoted  $V_{L_{filter}}$  as expressed by Eq. (8).

$$V_{L_{filter}} = L_{filter} \cdot \frac{dI_{FC}}{dt}$$

(8)

Since the amplitude and duration of  $V_{L_{filter}}$  ripple are respectively  $V_{DC}/2$  and  $T_d$ , where  $T_d$  is the dead time of the FC leg IGBTs,  $\delta I_{FC}$  can be deduced by (9).

$$\delta I_{FC} = T_d \cdot \frac{V_{DC}}{2 \cdot L_{filter}} \tag{9}$$

The minimal value of  $L_{\text{filter}}$  that enables the  $I_{\text{FC}}$  ripple to be within its admissible interval is expressed by (10).

$$L_{filter\_min} = T_d \cdot \frac{V_{DC}}{2 \cdot \delta I_{FC\_max}}$$

(10)

iii) Finally, the inductance and capacitance have to be in a range that guarantees protection against NPC mid-point overvoltages caused by an instantaneous load disconnection or the turning-off of all power devices.

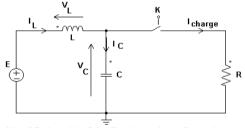

Fig.4 gives a simplified scheme to analyse the  $V_{NPC}$  ripple in the case of a brutal load disconnection. L and C do model the LC filter components, E models the  $V_{FC}$  voltage, and switch K is used to instantaneously disconnect the load modelled by R. The capacitor voltage  $V_c$ , which emulates the neutral point voltage, is constant as long as the load is connected. Once switch K is off, emulating a sudden load disconnection, the system becomes oscillatory and the  $V_c$ voltage undergoes an unavoidable over-voltage. This overvoltage depends on the values of L and C. In fact, initially, the system is described by Eq. (11), and when switch K is turned off, it verifies Eqs. (12) and (13).

Fig.4. Simplified model of the filter behaviour after an instantaneous load disconnection

$$V_C(t=0) = E, V_L(t=0) = 0, i_L(t=0) = \frac{E}{R}$$

(11)

$$V_C(t) = E - V_L(t) \tag{12}$$

$$V_L(t) = L \cdot \frac{di_L}{dt} \tag{13}$$

The current  $i_L$  can be written as in Eq. (14):

$$i_L(t) = \frac{E}{R} \cdot \cos(\omega t) \tag{14}$$

where :

$$\omega = \frac{1}{\sqrt{L.C}} \tag{15}$$

Consequently the over-voltage of the capacitor, C, is equal to that of the inductor, L; it is easily derived from (12)–(14) and is given by Eq. (16).

$$\delta V_C = \sqrt{\frac{L}{C} \cdot \frac{E}{R}}$$

(16)

Analogously, for the case of instantaneous load disconnection from the proposed hybrid converter, the load current can be approximated by its RMS value and the neutral point voltage,  $V_{NPC}$ , would be subject to an over-voltage given by (17).

$$\delta V_{NPC} = \sqrt{\frac{L_{filter}}{C_{filter}}} \cdot I_{load} \tag{17}$$

Imposing a maximum admissible ripple of  $V_{NPC}$  in the case of instantaneous load disconnection can be performed if the LC filter components are chosen with respect to Eq. (18).

$$L_{filter\_max} = \frac{(\delta V_{NPC})^2}{(I_{load})^2} \cdot C_{filter}$$

(18)

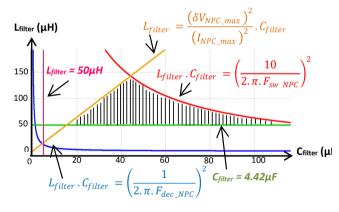

Fig.5, which has a two-dimensional coordinate system, describes the considered LC filter sizing criteria and summarizes graphically the proposed design methodology.

The hatched zone corresponds to the values of  $L_{\rm filter}$  and  $C_{\rm filter}$  that satisfy Eqs. (1), (2), (7), (10), and (18) and can consequently cope with the three above-mentioned requirements.

Fig.5. NPC filter sizing methodology: Application for the proposed converter: The hatched zone correspond to values  $L_{filter}$  and  $C_{filter}$  that meet the three considered criteria @ $V_{DC} = 600 V$ ,  $I_{load} = 10 A$ ,  $F_{sw_NPC} = 10 V_{sw_NPC} =$

$F_{sw_FC} = 20 \text{ kHz}$ ,  $\delta V_{NPC_max} = 6\%$ ,  $\delta I_{FC_max} = 6A$ ,  $T_d = 1 \mu s$ . It should be mentioned that C<sub>filter</sub> is "naturally" available in the power converter. It is composed of the already existing decoupling capacitors (taken as equal to 3.3  $\mu$ F in the experimental setup) in parallel with each half leg of the NPC inverter. This leads to C<sub>filter</sub> = 19.8  $\mu$ F. L<sub>filter</sub> has been chosen as 50  $\mu$ H regarding the above described methodology.

### C. Experimental Validation of the Hybrid Converter Operation under Normal Condition Mode

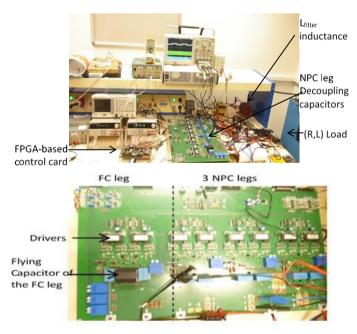

In order to verify the effectiveness of the proposed filter, it was tested experimentally as shown in Fig.6. The developed power converter uses INFINEON<sup>TM</sup> F3L150R07W2E3\_B11 three-level IGBT modules for the NPC legs and two IXYS<sup>TM</sup> FII40-06D modules for the commutation cells of the FC leg. Under normal conditions, the proposed FC-NPC power converter was tested with a three-phase RL load and an open-

loop FPGA-based control. Under this healthy mode, called (3,3,3) mode, the control board generates three-level PWM signals for the 12 IGBT modules of the three NPC legs. The FC leg, which acts as a DC/DC converter with a constant duty cycle equal to 50%, is controlled to generate an output voltage equal to  $V_{DC}/2$ . The flying capacitor is actively balanced by using the algorithm proposed in [35].

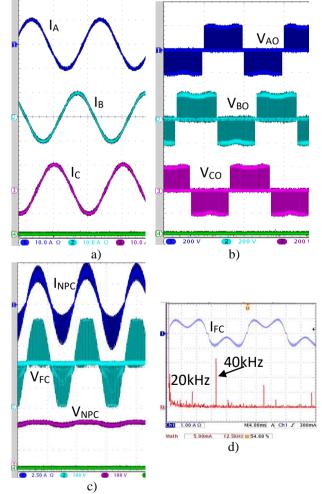

Fig.7 gives the experimental validation of the proposed converter topology and control, that is, the three-phase NPC converter connected through the LC filter to the FC leg, feeding a three-phase 10-A RL load. The obtained output voltages and currents prove the efficient global operation as shown on Fig.7.a and Fig.7.b. It should be mentioned that the neutral point voltage ripple does not exceed 10% without using any capacitor bank (Fig7.c.). This is achieved thanks to the active neutral point control and the FC filter described above. As expected, the FC leg output current  $I_{FC}$  low frequency component (150 Hz) is three times the reference frequency (50 Hz). This low frequency component, which is also observable on the neutral point voltage, is due to nonnegligible impedance of the LC filter inductance. The three output voltages,  $V_{AO}$ ,  $V_{BO}$ , and  $V_{CO}$ , are quasi-perfectly threelevel modulated (0,  $+V_{DC}/2$ , and  $-V_{DC}/2$ ). The dead time clearly affects the  $V_{FC}$  voltage involving  $2*F_{sw}$  FC frequency glitches. These glitches, which also affect the  $V_{NPC}$  voltage, are completely filtered by L<sub>filter</sub>. As expected, the spectral analysis of I<sub>NPC</sub> current flowing between the two converter parts given in Fig.7.d shows the two first frequency components at  $F_{sw_NPC}$  (20 kHz) and  $2*F_{sw_FC}$  (40 kHz). Moreover, the  $V_{NPC}$  voltage ripple and the  $I_{FC}$  current one have their values inside the expected ranges.

Fig.6. Experimental test bed for LC filter validation: The FC leg is connected to one NPC leg through a 50  $\mu$ H filter inductance (L<sub>filter</sub>.)

### III. SIMPLE FAULT-TOLERANT PWM STRATEGY FOR THE HYBRID FC-NPC CONVERTER

As described in Section II.D, during normal mode, an open-loop FPGA-based three-level PWM strategy is used to control NPC legs. When an NPC IGBT breaks down, the corresponding leg is partially isolated and the phase is connected to the FC leg output. In this section, a fault-tolerant PWM strategy is described. It consists of developing a PWM reference system for the degraded mode. Fault detection, leg isolation, and post-fault connection are detailed in the next section. It should be noted that in the following, phase A refers to the damaged converter leg. Analogous analyses are obviously valid if the failure occurs in phase B or phase C.

### A. Description of the proposed FPGA-based PWM scheme under faulty conditions

During faulty mode, the FC leg continues feeding the active midpoint voltage to the neutral point of the two healthy NPC legs. Thus, phase A permanently has just one level " $V_{DC}/2$ ", while the two other phases have three levels ( $V_{DC}$ ,  $V_{DC}/2$ , and 0), as in normal mode operation. This faulty mode is then referred to as (1,3,3) mode. Only phases B and C are modulated and their power switches have to be controlled. It should be mentioned that, under fault condition (1,3,3) mode, the power converter delivers only eight active voltage vectors and one zero voltage vector and that its maximum modulation depth  $(M_{max})$  is reduced by 50% when compared to normal conditions. Even if this limitation affects the power delivered to the converter load, it avoids system breakdown and corresponds to a transient operation mode before corrective maintenance. The fault tolerant SVM-based strategy described in [35] involves complicated mathematical development and is not compatible with rapid and highperformance FPGA-based controls.

Fig.7. Proposed FC-NPC converter topology and control under normal conditions. Experimental validation @  $V_{DC} = 100 - V / 10 - A$  RL load,  $F_{sw_{-}FC} = 20 kHz$ ,  $F_{sw_{-}NPC} = 20 kHz$ , dead time  $T_d = 1 \mu s$ : a) Phase currents  $I_A$ ,  $I_B$ ,

and *I<sub>C</sub>* (10 ms/div, 10 A/div); b) Output voltages *V<sub>AO</sub>*, *V<sub>BO</sub>*, and *V<sub>CO</sub>* (10 ms/div, 200 V/div); c) NPC input current *I<sub>NPC</sub>* (4 ms/div, 2.5 A/div), FC output voltage *V<sub>FC</sub>* (4 ms/div, 100 V/div), and NPC neutral point voltage *V<sub>NPC</sub>* (4 ms/div, 100 V/div); d) Time (4ms/div, 1A/div) and spectral (12.5 kHz/div, 5 mA/div) analysis of FC output current *I<sub>FC</sub>*

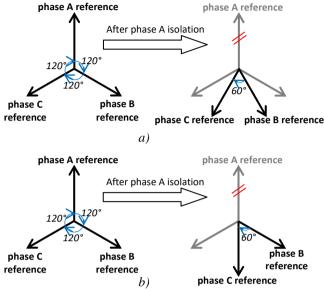

This post-fault reconfiguration implies a modification of the PWM reference system. In fact, in [37], it has been demonstrated that when one of the converter phases is not modulated, shifting the two remaining ones by  $30^{\circ}$  as depicted in Fig.8.a leads to a system that is able to operate in a balanced way regarding the phase-to-phase voltages.

Fig.8. Voltage reference system modification after the loss of phase *A* leg: a) Classical modification [37]; b) Proposed modification

In this paper, this solution is improved. In order to simplify the control reconfiguration from the normal mode to the faulty one, the PWM reference system presented in Fig.8.b is proposed. With this technique, the phase B reference is not changed during faulty mode, and the phase C reference can be easily deduced from the phase A one. In fact, after the occurrence of a fault, the phase C reference is the opposite of the phase A one during normal mode.

### B. Experimental Results

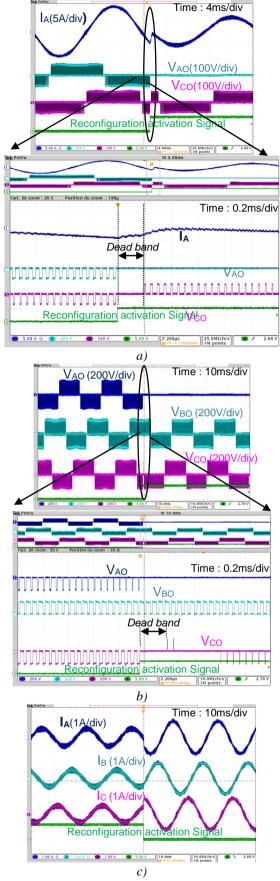

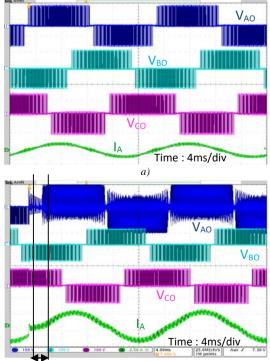

Validation tests of the proposed control reconfiguration were carried out on the experimental test bench described above. Fig.9 gives some of the experimental results obtained with various DC bus voltage and RL-load current configurations. Under normal conditions, the three NPC converter phases deliver three-level voltage outputs. When a fault occurs, the power converter reconfiguration ensures the connection of the faulty leg (taken as phase A under the current tests) output to the NPC neutral point and the  $V_{AO}$ voltage is then null (Fig.9.a). During faulty mode, and according to the proposed reconfiguration scheme described in the previous paragraph, the  $V_{CO}$  voltage is equal to the opposite of the  $V_{AO}$  one if the fault wouldn't have occurred; as illustrated in Fig.9.a. The  $V_{BO}$  and  $V_{CO}$  voltages continue to be three-level modulated after the occurrence of the fault (Fig. 9.b): They are shifted by  $60^{\circ}$ , enabling the load currents to form a balanced three-phase system with a 50% amplitude reduction: Fig. 9.c emulates the converter recovery since the power system switches from the (1,3,3) mode to normal mode operation.

Fig.9. Fault-tolerant hybrid FC-NPC converter and control validation: Transition between normal condition mode and (1,3,3) post-fault mode with a security dead-band and a 50% reduction in output current @ 20 kHz switching frequency, and 1  $\mu$ s dead time: a) phase A current,  $I_A$  and Output voltages  $V_{AO}$ ,  $V_{CO}$ ; b) Output voltages  $V_{AO}$ ,  $V_{BO}$  and  $V_{CO}$ ; c) Load currents  $I_A$ ,  $I_B$ , and  $I_C$

It is to be noted that for safe transition from normal mode to faulty mode, a 200us dead band is introduced between these two modes: During this dead band, phase C control signal is OFF and its output voltage is then null. The magnified Fig. 9.a and Fig.9.b prove that the transition from normal condition mode to post-fault mode does not involve any transient or undesirable system interruption.

### IV. NOVEL FAULT ISOLATION AND POST- FAULT RECONFIGURATION TECHNIQUES FOR THE HYBRID FC-NPC CONVERTER

In order to reach fault tolerant capabilities, three steps are mandatory for the considered FC-NPC converter: first, the converter has to detect the fault that would affect the power switch, second, isolate it, and third, enable the reconfiguration of the post-fault topology. In the following, an interesting technique combining both isolation and postfault reconfiguration is proposed.

### A. Fault Detection

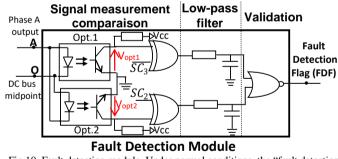

NPC IGBT faults lead to discordance between the control signal delivered by the PWM module and the corresponding leg output voltage. The developed fault-detection principle is to compare an adaptation of the control signals with the voltages across the converter IGBTs. Under normal conditions, they comply; otherwise, the fault detection module indicates an error.Fig.10 shows the adopted fault detection for the 3L-NPC converter. The output *Vopt1* of optocoupler *Opt. 1* is:

- "ON" if the converter output *Voutput1* is equal to  $V_{DC}/2$ , - "OFF" otherwise.

The output Vopt2 of opto-coupler Opt. 2 is:

- "ON" if *Voutput1* is equal to  $-V_{DC}/2$ ,

- "OFF" otherwise.

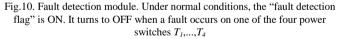

It should be mentioned that the two RC-based low-pass filters aim to filter the output comparison signal and avoid inadvertent activation caused by an imperfect compensation of the dead time and driver's propagation delays. Typically, the optimal compensation of the delays is tuned at the nominal operation. To validate the fault detection step, experimental tests on one NPC converter leg were carried out. An FPGA-based control board delivers the power switch control signals. The NPC leg is connected to a *100-V* DC bus and the neutral point "0" is passively balanced. The fault is created through an external push button that inhibits the four control signals of phase by means of a blocking signal, named BLS. An open-circuit fault is then emulated. Fig.11 gives the

power switch blocking signal BLS, the IGBT  $T_1$  output voltage ( $V_{CE}(T_1)$ ), and the fault detection flag (FDF) after the occurrence of a fault.

The power switch fault is effectively detected only  $33 \ \mu s$  after it begins to occur, which is less than the switching period of the NPC part. This delay is due to the two RC-based lowpass filters and has to be taken into account in order to propose adapted fault isolation and power converter reconfiguration procedures.

Fig. 11. Power switch fault detection: a) Blocking Signal BLS (0, 3V/div), IGBT  $T_1$  output voltage  $V_{CE}(T_1)$  (50V/div), and Fault Detection Flag, FDF (20V/div), Time : 2ms/div; b) zoom: 20µs/div

### B. Fault Isolation and Power Converter Reconfiguration

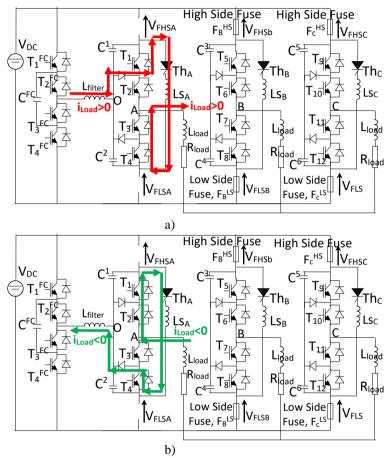

In [38], the authors proposed an interesting fault isolation and hardware reconfiguration technique for two-level converters and [35] adopted it for multilevel applications. Since it requires the addition of only one power switch (thyristor) and two fast fuses per phase, its principle is now integrated in the studied power converter topology. The proposed symmetrical isolation technique consists of "high-side" and "low-side" fuse-blowing through the DC bus short circuit using thyristor  $Th_x$  in series with snubber inductance  $Ls_x$ . The post-fault connection between the damaged phase and the active neutral point is also ensured by this thyristor, and no additional semiconductors are necessary for this connection; as depicted. In fact, phase current flows from the load to the FC leg output (or vice versa) through the parallel diodes of the fault leg IGBT modules and the thyristor  $Th_x$  as shown in Fig.12. In this figure, the fault-tolerant three-level hybrid power converter reconfiguration after the occurrence of a fault on the phase A leg is presented. This new technique has two main advantages. First, isolation and post-fault reconfiguration are ensured by the same additional component, that is, the thyristor  $Th_x$ . Second, this technique is applicable regardless of the faulty IGBT and the fault type (open circuit or short circuit). Parallel diodes are connected within the transistor chips.

The power converter reconfiguration needs a fast fuse reaction during pre-arc phase (low  $I^2Tp$  value), low di/dt value during post-arc phase, a low leakage current and short operation time in order to prevent converter power switch damage and to ensure acceptable post-blowing isolation performance. Many experimental tests are carried out in order to indicate the recommended fuse technology and PCB compatible technology for the considered application.Fig.13 shows the system topology used for the isolation

Fig.12. Hybrid FC-NPC converter: power switch fault-tolerance capability thanks to a simple reconfiguration control and an effective addition of three thyristors ( $Th_{ax}Th_{bx}$  and  $Th_{c}$ ) and six fast fuses ( $F_X^{HS}$  and  $F_X^{LS}$ , where X = A, B, and C). a)Case of positive load current b) Case of negative load current

technique test. The two fuse technologies presented in Fig.15 are tested: Surface Mounted Devices (SMD, 125 V / 10 A,  $2 \times 2 matrix$ ) and a classical cartridge one (250 V / 32 A) screwed on the bus bar power PCB. Three parameters are considered to compare the two fuse types:

- the time needed by the thyristor current,  $I_{TH}$ , to reach the value that blows up the High Side and Low side fuses;

- the time needed by  $I_{TH}$  to fall down to zero after fuses blowing up. In fact, in the considered fault-tolerant power converter application, the discharge time of the snubber inductance is an important issue: the converter reconfiguration step cannot begin before the post-arc phase ends definitively. The choice of isolation fuse influences the waiting time that the converter control board has to have between normal and fault operation modes. - and voltages across the two fuses V<sub>FHS</sub> and V<sub>FLS</sub>. In fact, once the fault leg is isolated, it is important to consider the voltages across the high- and low-side fuses. Theoretically, these two voltages are balanced and equal to  $V_{DC}/2$ . Otherwise, the converter output voltage *Voutput* would be floating and would lead to additional and undesirable load current components caused by the fuse leakage current.

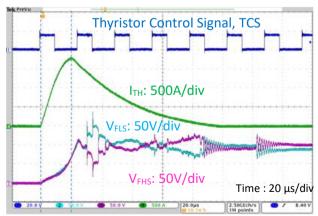

Fig.16 shows the experimental results during the fault leg isolation. As expected, the first phase during the fault isolation operation corresponds to the snubber inductance charging with  $I_{TH}$  current. Once the fuse  $I^2T_p$  rating value is reached, the fuses blow and the *Ls* current discharges through the power switch freewheeling diodes: this is the second phase of the isolation process. During this phase, after the post-arc phenomena, fuses become high impedance, allowing isolation of the fault leg.

Fig.13. Fault isolation technique test setup: Two fuses ( $F_{HS}$  and  $F_{LS}$ ), one thyristor (*Th*), and a snubber inductance *Ls* are added to the original 3L-NPC leg Fig.14.

As shown in Fig.16, the two fuse types have approximately the same speed: For the cartridge type, the current  $I_{TH}$  reaches 2500A after 25  $\mu$ s and for the SMD one, the current  $I_{TH}$ reaches 1800A after 20  $\mu$ s. The two fuse types have approximately the same performances considering this first criteria. However, the post-arc phase requires 60% more time when using the cartridge fuses (80  $\mu$ s) compared to the SMD ones (50  $\mu$ s). Then, the second fuse technology leads a lower overvoltage at the DC bus than the first one, and it clearly provides a better safe isolation process regarding all parallel components.

Fig.15. Fuses used for experimental tests: a) SMD fuses: Schurter 125 V / 10 A; b) Cartridge fuses: Mersen BS88 32 A / 250 V

Moreover, Fig.16.a shows that with the cartridge fuses, the unbalance between the voltages at the "high-side" and "low-side" fuses reaches 250 V ( $V_{HFS}$ \_max=250V and  $V_{FLS}$ \_min=0V), that is, 150%, whereas it does not exceed 150V with SMD technology, as shown in Fig.16.b.

Fig.16. Comparison of the behaviour of two fuses of different technologies during power converter fault leg isolation,  $V_{DC} = 200$  V: a) Classical cartridge; b) surface mounted devices: high- and low-side fuse voltages  $V_{FHS}$  (50 V/div),  $V_{FLS}$  (50 V/div), fuse current  $I_{TH}$  (500 A/div)

The above described isolation technique tests led to the conclusion that the SMD fuses are, today, the most suitable ones for the fault-tolerant power converter studied. It should be mentioned that, during the arc phase, a very low energy is generated, which corresponds only to the energy stored in the "DC bus-NPC leg" mesh and does not involve the energy stored in the load phase that spontaneously flows through the clamp diodes and the FC leg.. Moreover, the energy stored in the snubber inductance is not considered because this inductance is freewheeling. All these properties are important because fuses that have low break energy (and consequently low cost and volume) are able to meet the considered application requirements. However, these fuses must have undergone very low manufacturing dispersion in order to have quasi-similar behaviour during the fault isolation process. Consequently, this effective fault isolation solution does not entail a significant converter efficiency, price and volume increase.

#### C. Experimental Validation

In this paragraph, the whole of the fault-tolerance process, including fault creation, fault detection, leg isolation, and control reconfiguration, is experimentally validated. The fault is created using an external switch, which produces an open circuit of one of the NPC power switches.

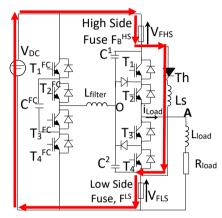

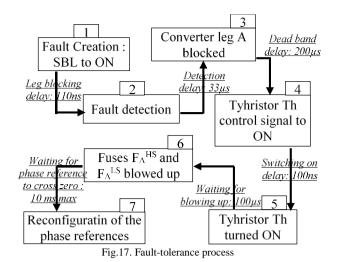

For safe transition from normal mode to faulty mode, two actions are taken. First, a dead band is considered after fault detection and before thyristor activation. Second, control reconfiguration is done when the phase *A* reference is equal to zero, in order to avoid the risk of over-current. Fig.17 shows all the delays included in the fault-tolerance process.In this test, the focus is given to the transition from normal to faulty operation. In order to dissociate the numerous issues of the designed hybrid converter (neutral point regulation, filter behaviour, post-fault operation, hardware reconfiguration), the midpoint of the NPC legs is connected to a capacitive neutral point voltage composed of two electrolytic capacitors. During faulty mode, the FC leg replaces the faulty NPC one. Fig.18 demonstrates the effectiveness of the proposed fault-tolerance process.

Blanking: Transition from normal to post-fault mode operation b)

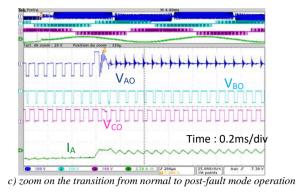

Fig.18. Experimental validation of the fault-tolerance process: NPC leg output voltages  $V_{AO}$ ,  $V_{BO}$ , and  $V_{CO}(100V/div)$  and NPC leg A output current I<sub>A</sub> (2.5A/div). a) normal mode operation, b) post-fault mode operation, c) zoom on the transition from normal to post-fault mode operation

Indeed, the availability of the converter after an NPC IGBT breakdown is ensured. In this test, the open-circuit failure occurs when the phase A reference is close to zero, which results in reduced blanking time (2 ms) before the FC leg starts to modulate. During this blanking time, phase A is isolated from the DC bus, connected to the inactive FC leg and its load current is cancelled, while phases B and C remain active with a 120° phase shift. Voltages  $V_{BO}$  and  $V_{CO}$  do not undergo any degradation during faulty mode. However, due to the resonance between the flying capacitor C<sup>FC</sup> and filter inductance L<sub>filter</sub> (already mounted on the test bench), the midlevel of voltage  $V_{AO}$  is not perfectly null. Phase current  $I_A$  is still perfectly sinusoidal in faulty mode with the same amplitude. Fig.19 shows the fuses' voltage and snubber current during the isolation process. The triggering of the thyristor causes the charge of  $L_{snubber}$  inductance, resulting in a strong current surge with a peak at 1800 A: it is the first isolation phase. When i<sup>2</sup>t is reached, the fuses blow up and the snubber current flows in the freewheeling diode until it is cancelled. The voltage across each fuse increases gradually, because of the plasma fluctuation and then fuse's internal resistance. This internal resistance is first constant and then suddenly increases during the arc phase. The DC voltage is divided between the two fuses: It confirms the effectiveness of the leg isolation.

Fig.19. Experimental validation of the fault-tolerance process: Thyristor control signal, L<sub>snubber</sub> current I<sub>TH</sub>(500A/div), fuse voltages V<sub>FHS</sub> (50V/div) and V<sub>FLS</sub> (50V/div)

### V. CONCLUSION

This paper investigates a three-level fault-tolerant hybrid converter that hat combines two main topologies: three identical three-level NPC-based legs and a three-level FCbased one. The aim of this FC leg is to provide an actively balanced neutral point to the NPC ones and to replace the conventional high-capacitance electrochemical capacitors by simple polypropylene ones.

Connection of the FC leg to the three NPC ones needs an LC filter design to ensure decoupling of the mandatory two topologies. The precise filter sizing is described in detail. It [9] takes into account three criteria: spectral constraints, admissible neutral point voltage and current ripples, and protection against NPC neutral point overvoltage in the case of instantaneous load disconnection.

Under fault conditions, a post-fault mode named (1,3,3) is analysed: the damaged leg is disconnected and the corresponding phase is connected to the active midpoint generated by the FC leg. Converter availability is ensured, but with an output power penalty of 50%. A simple FPGA-based reconfiguration control for post-fault (1,3,3) mode was proposed and experimentally validated.In order to tolerate power switch faults, in both open- and short-circuit modes, the authors enhanced the hybrid FC-NPC topology by adding the required fault-tolerance features needed to detect the switch fault, isolate the corresponding damaged leg, reconfigure the converter, and ensure its safe post-fault operation. For each of the three NPC legs, dual-fuses and one thyristor are added to isolate the switch fault. This thyristor also ensures an original reconfiguration of the hybrid converter after the occurrence of the fault. Two fuse technologies were tested and their performances were shown, proving that the SMD one is currently more suitable for faulttolerant converter applications.

This paper is a novel research investigation in the field of fault-tolerant multilevel converters since all the needed faulttolerance functionalities were simultaneously tested and validated. The experimental results were carried out with a 15 kW converter test-bench that the authors designed according to the abovementioned considerations. The proposed functionalities imply increases in converter cost and volume, but they remain relatively low. Indeed, the designed converter has attractive solutions considering the fault-tolerance improvement it offers. The developed test-bench could be used as an original experimental benchmark to evaluate the whole of the fault-tolerance process and to verify the effectiveness of the dependable capabilities of the power system when a switch failure occurs.

#### REFERENCES

- A. Laka, J. Andoni Barrena, J. Chivite-Zabalza, M.A. Rodriguez Vidal, and P. Izurza-Moreno, "New hexagonal three-phase voltage-source converter topology for high-power," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 30–39, May 2015.

- [2] C.R. Baier, J.R. Espinoza, M. Rivera, J.A. Munoz, W. Bin, P.E. Melin, and V. Yaramasu, "Improving power quality in cascade multilevel converters based on single-phase nonregenerative power cells," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4498–4509, November 2014.

- [3] L. Tarisciotti, P. Zanchetta, A. Watson, S. Bifaretti, J.C. Clare, and P.W. Wheeler, "Active DC voltage balancing PWM technique for high-power cascaded multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 61, no. 11, pp. 6157–6167, February 2014.

- [4] F. Dengand and Z. Chen, "Voltage-balancing method for modular multilevel converters switched at grid frequency," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 2835–2847, October 2015.

- [5] A. Ruderman, "About voltage total harmonic distortion for single- and three-phase multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1548–1551, July 2015.

- [6] A.S. Aneesh Kumar, G. Poddar, and P. Ganesan, "Control strategy to naturally balance hybrid converter for variable-speed medium-voltage drive applications," *IEEE Trans. Ind. Electron.*, vol. 62, no. 23, pp. 866– 876, July 2015.

- [7] S.K. Chattopadhyay and C. Chakraborty, "A new multilevel inverter topology with self-balancing level doubling network," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4622–4631, November 2014.

- [8] A. Antonopoulos, L. Angquist, L. Harnefors, K. Ilves, and H.-P. Nee, "Global asymptotic stability of modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 61, no. 2, pp. 603–612, March 2014.

- [9] W. Kui, Z. Zedong, L. Yongdong, L. Kean, and S. Jing, "Neutral-point potential balancing of a five-level active neutral-point-clamped inverter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1907–1918, Nov. 2013.

- [10]Z. Zhe, O.C. Thomsen, and M.A.E. Andersen, "Discontinuous PWM modulation strategy with circuit-level decoupling concept of three-level neutral-point-clamped (NPC) inverter," *IEEE Trans. Ind. Electron.*, vol. 60, no.5, pp. 1897–1906, November 2013.

- [11] R. Stala, "A natural DC-link voltage balancing of diode-clamped inverters in parallel systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 11, pp. 5008– 5018, September 2013.

- [12] J.D. Barros, J.F.A. Silva and E.G.A. Jesus, "Fast-predictive optimal control of NPC multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 619–627, July 2013.

- [13] P.F. Acuna, L.A. Moran, M.E. Rivera, R. Aguilera, R. Burgos and V.G. Agelidis, "A single-objective predictive control method for a multivariable single-phase three-level NPC converter-based active power filter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 11, pp. 5008–5018, January 2015.

- [14]S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchandand, and C. Patel, "Multilevel inverters for low-power application," *IET Power Electron.*, vol. 4, no. 4, pp. 384–392, April 2011.

- [15] R. Mecke, "Multilevel NPC inverter for low-voltage applications", Proc. EPE, Birmingham, UK, 2011, pp. 1–10.

- [16] M.R. Islam, Y. Guo, and J.G. Zhu., "Performance and cost comparison of NPC, FC and SCHB multilevel converter topologies for high-voltage applications," *Proc. ICEMS*, Beijing, China, 2011, pp. 1–6.

- [17] S. Kouro, K. Asfaw, R. Goldman, R. Snow, B. Wu, and J. Rodríguez, "NPC multilevel multistring topology for large scale grid connected photovoltaic systems," *Proc. PEDG*, Hefei, China, 2010, pp. 400–405.

- [18] F. Kieferndorf, M. Basler, L.A. Serpa, J.-H. Fabian, A. Coccia, and G.A. Scheuer, "ANPC-5L technology applied to medium voltage variable speed drives applications," *Proc. SPEEDAM*, Pisa, Italy, 2010, pp. 1718–1725.

- [19] Y. Shen, L. Hao, and S.X. Ding, "Real-time implementation of faulttolerant control systems with performance optimization," *IEEE Trans. Ind. Electron.*, vol. 61, no. 5, Jul. 2014, pp. 2402–2411.

- [20]B. Mirafzal, "Survey of fault-tolerance techniques for three-phase voltage source inverters," *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5192–5202, January 2014.

- [21] L.M.A. Caseiro and A.M.S. Mendes, "Real-time IGBT open-circuit fault diagnosis in three-level neutral-point-clamped voltage-source rectifiers based on instant voltage error," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1669–1678, July 2015.

- [22] H. Wang, K. Ma, and B. Blaabjerg, "Design for reliability of power electronic systems," *Proc. IECON*, IEEE Industrial Electronics Society, Montreal, QC, 2012, pp. 33–44.

- [23] M. Arifujjaman and L. Chang, "Reliability comparison of power electronic converters used in grid-connected wind energy conversion system," *Proc. PEDG*, Aalborg, Danemark, 2012, pp. 323–329.

- [24] R. Grinberg, G. Riedel, A. Korn, P. Steimer, and E. Bjornstad, "On reliability of medium voltage multilevel converters," *Proc. ECCE*, Denver, CO, 2013, pp. 4047–4052.

- [25] Y. Song and B. Wang, "Survey on reliability of power electronic systems," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 591–604, January 2013.

- [26] V. Venkatasubramanian, R. Rengaswamy, K. Yin, and S. N. Kavuri, "A review of process fault detection and diagnosis Part I: Quantitative model-based methods," Comp. & Chem. Eng., vol. 27, pp. 293–311, 2003

- [27] P. Mhaskar, C. McFall, A. Gani, P. D. Christofides, and J. F. Davis, "Isolation and handling of actuator faults in nonlinear systems," Automatica, vol. 44, pp. 53–62, 2008.

- [28] R. Gandhi and P. Mhaskar, "Safe-parking of nonlinear process systems," Comp. & Chem. Eng., vol. 32, pp. 2113–2122, 2008

- [29] M. Du and P. Mhaskar, "Uniting Safe-Parking and Reconfiguration-Based Approaches for Fault-Tolerant Control of Switched Nonlinear

Systems" Proc. American Control Conference (ACC), Baltimore, USA, 2010, pp. 2829-2834

- [30] H. Shahnazari and P. Mhaskar "Simultaneous actuator and sensor fault isolation of nonlinear systems subject to uncertainty" Proc. American Control Conference (ACC), Boston, USA, 2016, pp. 6857 - 6862.

- [31] S. Ceballos, J. Pou, E. Robles, I. Gabiola, J. Zaragoza, J.L. Vilatte, and D. Boroyevich, "Three-level converter topologies with switch breakdown fault-tolerance capability," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 982–995, March 2008.

- [32]S. Ceballos, J. Pou, E. Robles, J. Zaragoza, and J.-L. Matin, "Fault tolerant neutral-point-clamped converter solutions based on including a fourth resonant leg," *IEEE. Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2293–2303, June 2011.

- [33] S. Ceballos, J. Pou, E. Robles, J. Zaragoza and J.-L. Matin, "Three-leg fault-tolerant neutral-point-clamped converter", *Proc. ISIE*, Vigo, Spain, 2007, pp. 3180–3185.

- [34] H. Ben Abdelghani, A. Bennani Ben Abdelghani, F Richardeau, J.-M. Blaquiere and F. Mosser, "Post-fault reconfiguration for a versatile and hybrid 4 leg NPC-flying capacitor topology", *Proc. ISIE*, Istanbul, Turkey, 2014, pp. 1502–1507.

- [35] H. Ben Abdelghani, A. Bennani Ben Abdelghani, F. Richardeau, J.-M. Blaquiere and F. Mosser, "Fault tolerant control for hybrid 4 leg NPCflying capacitors topology," *Proc. ELECTRIMACS*, Valencia, Spain, 2014, pp. 1–6.

- [36] N. Celanovic and D. Boroyevich, "A comprehensive study of neutralpoint voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters", *IEEE Trans. Power Electron.*, vol. 15, no. 2, pp. 242–249, March 2000.

- [37] G.T. Park, T.J. Kim, D.W. Kang, and D.S. Hyun, "Control method of NPC inverter for continuous operation under one phase fault condition", *IEEE Conf. Industry Applications Society (IAS)*, vol. 4, October 2004, pp. 2188–2193.

- [38] Z. Dou, F. Richardeau, E. Sarraute, V. Bley, J.-M. Blaquiere, C. Vella, and G. Gonthier, "PCB dual-switch fuse with energetic materials embedded. Application for new fail-safe and fault-tolerant converters," *Microelectron. Reliab.*, vol. 52, no. 9/10, pp. 1919–1926, October 2012